Fault Ride-Through Method for Interline Power Flow Controller Based on DC Current Limiter

Abstract

:1. Introduction

- A DC-side fault current limitation method for the IPFC is proposed for the first time, which can assist with the DC-side fault ride-through of the IPFC and effectively limit the fault current.

- The proposed current limiter can limit the fault current below the MMC blocking current and enable IPFC non-blocking fault ride-through, thereby improving the survival capability of the IPFC. After the circuit breaker cuts off the fault, the IPFC can resume normal operation in a short period of time.

- The proposed IPFC limiter exhibits low-impedance characteristics in the steady state and low on-state loss, ensuring that the normal operation of the IPFC is not affected.

- The proposed current limiter only requires the use of thyristors without the need for expensive fully controlled devices. At the same time, the fault current is limited to a lower level, which can greatly reduce the energy consumption of the lightning arrester in the DC circuit breaker. This will reduce the overall cost.

2. Current Limiter Topology and Current-Limiting Process Suitable for IPFC DC Side

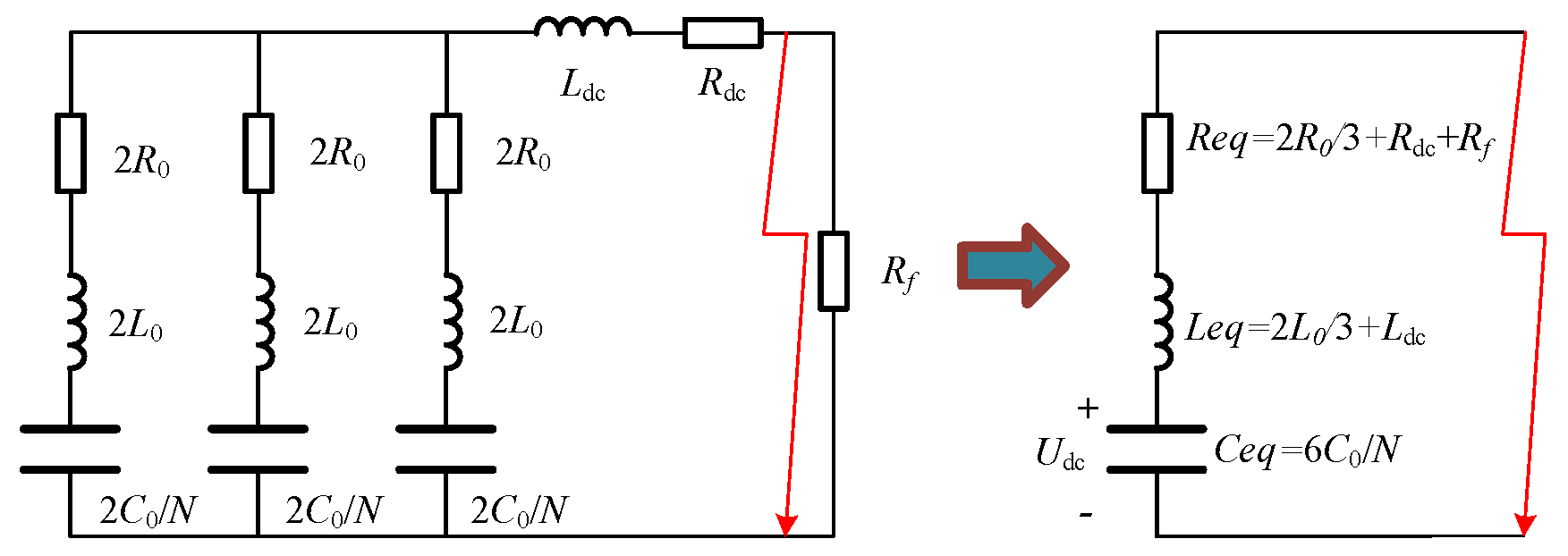

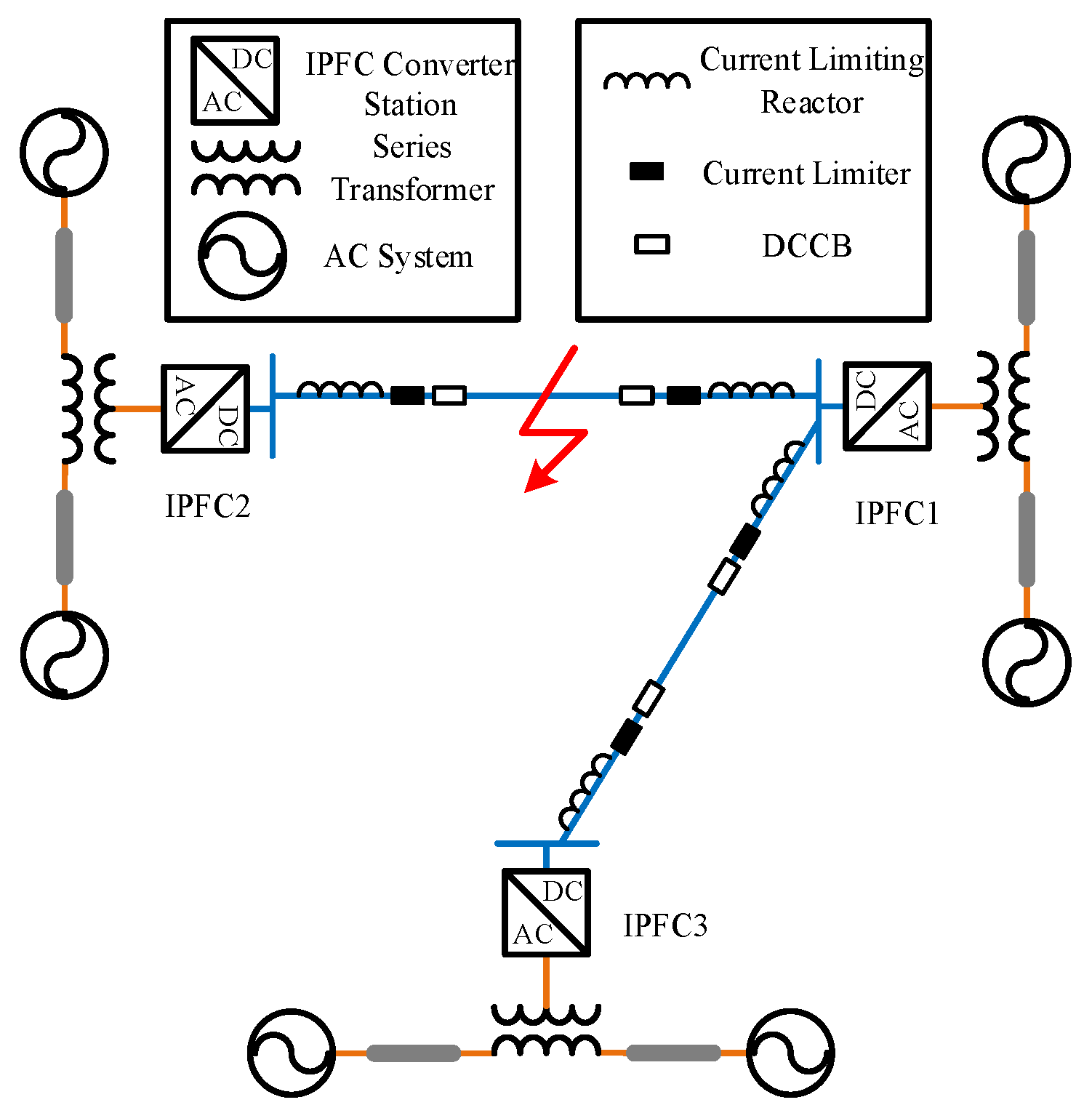

2.1. Topology of IPFC

2.2. DC Fault Vulnerability Analysis

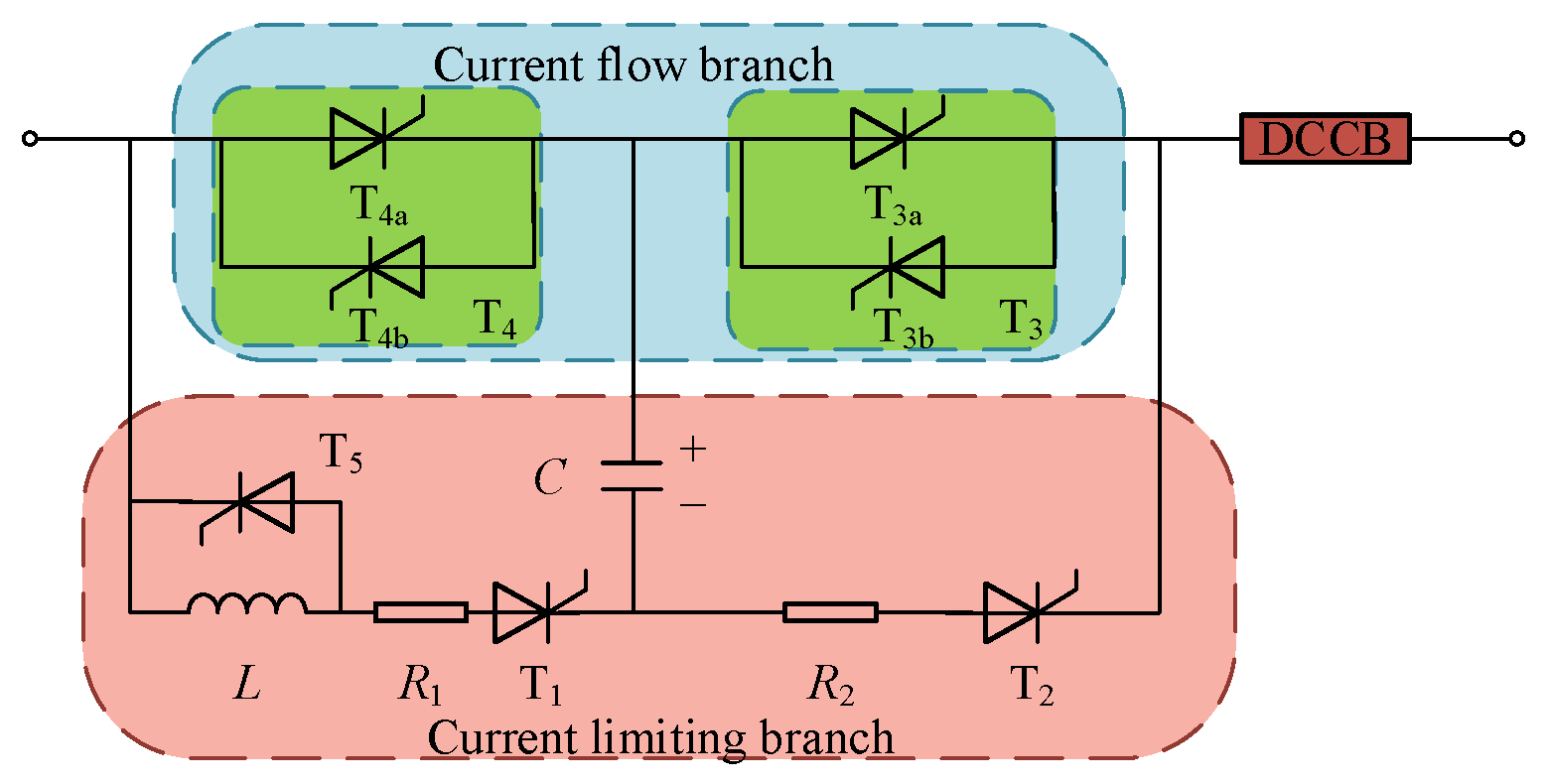

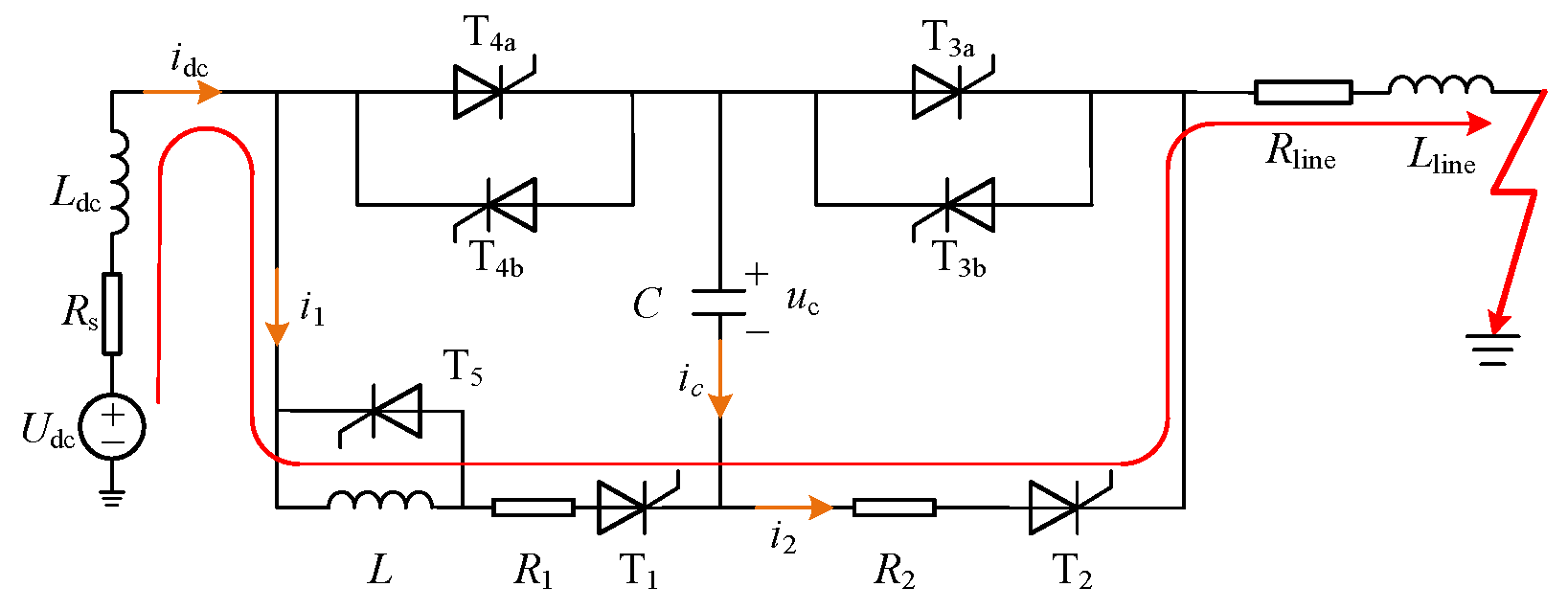

2.3. IPFC Fault Current Limiter Topology

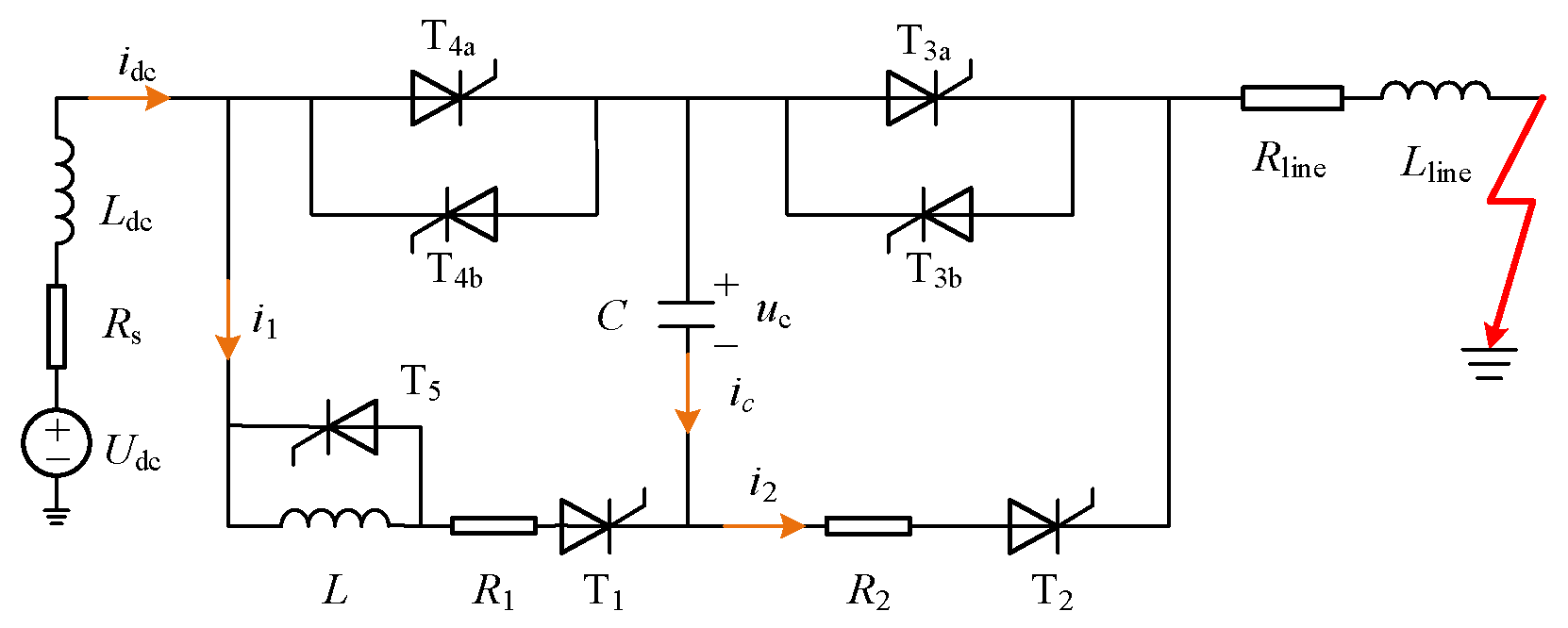

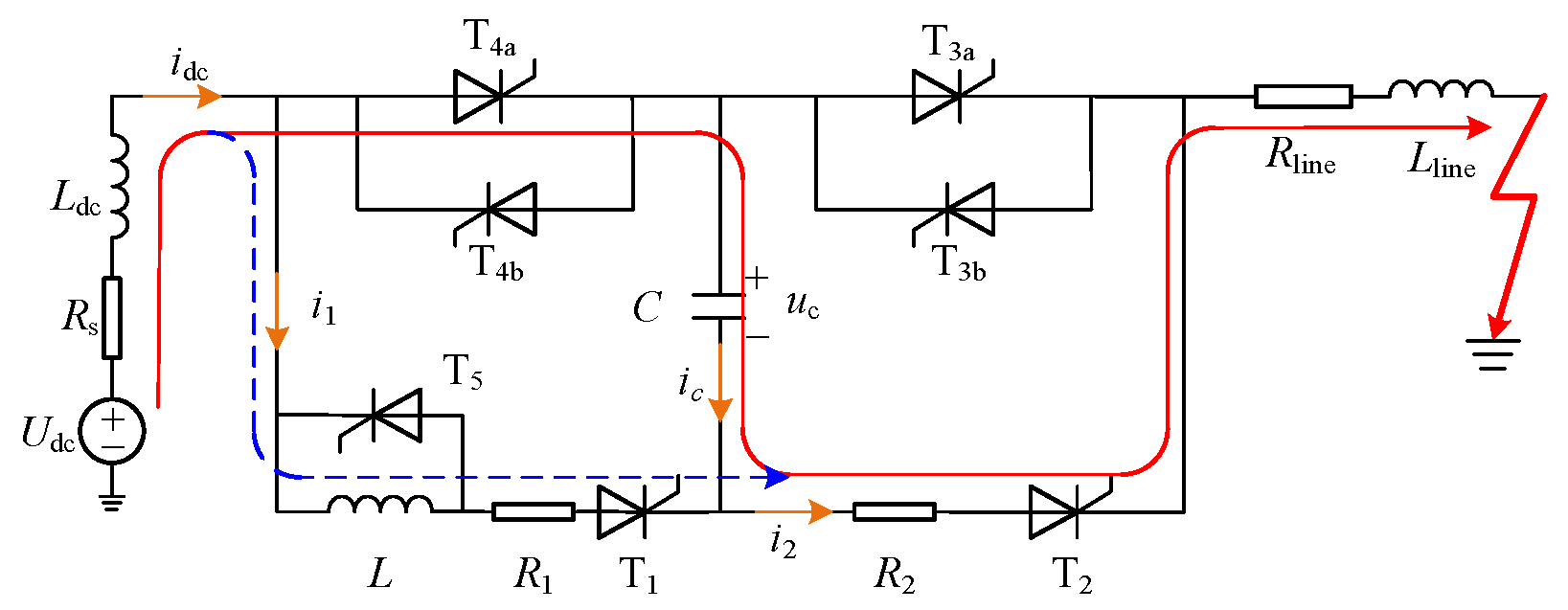

2.4. Action Process and Theoretical Analysis of Current Limiter

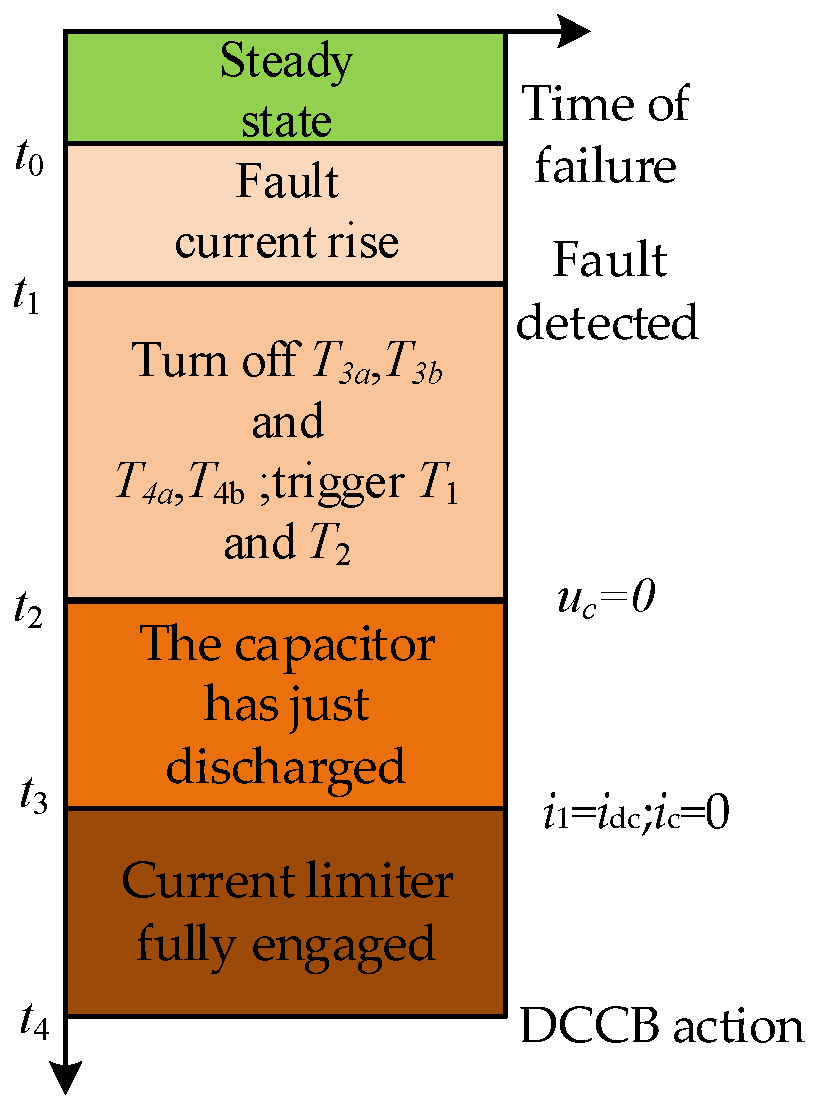

2.4.1. Current Limiter Action Process

- During normal operation, the thyristors T3 and T4 are in a normal trigger state, and the current flows through the current branch as usual.

- When a fault occurs, the current rapidly increases. When the current reaches the fault detection condition, T3 and T4 are turned off, and T2 and T1 are turned on. Thyristor T2 conducts under the forward voltage of the capacitor C, and the current is quickly transferred to the auxiliary commutation branch. After the current of thyristor T3a decreases to zero, capacitor C is not discharged completely, and T3a withstands the reverse voltage of capacitor C for a reliable shutdown.

- As the voltage of capacitor C drops to zero, the current continues to charge it and thyristor T1 turns on due to the forward voltage, putting the main current-limiting branch into operation. As the current increases, when the sum of the capacitor voltage and resistor R1 voltage exceeds the system voltage, the line current begins to decrease. After T4a current drops to zero, the thyristor is turned off; the voltage across C reaches its maximum value, and the fault current is transferred to the current-limiting branch.

2.4.2. Theoretical Analysis of Current-Limiting Process

- (1)

- t0–t1 fault detection stage

- (2)

- t1–t2 current transfer stage

- (3)

- t2–t3 capacitor commutation stage

- (4)

- t3–t4 main current-limiting stage

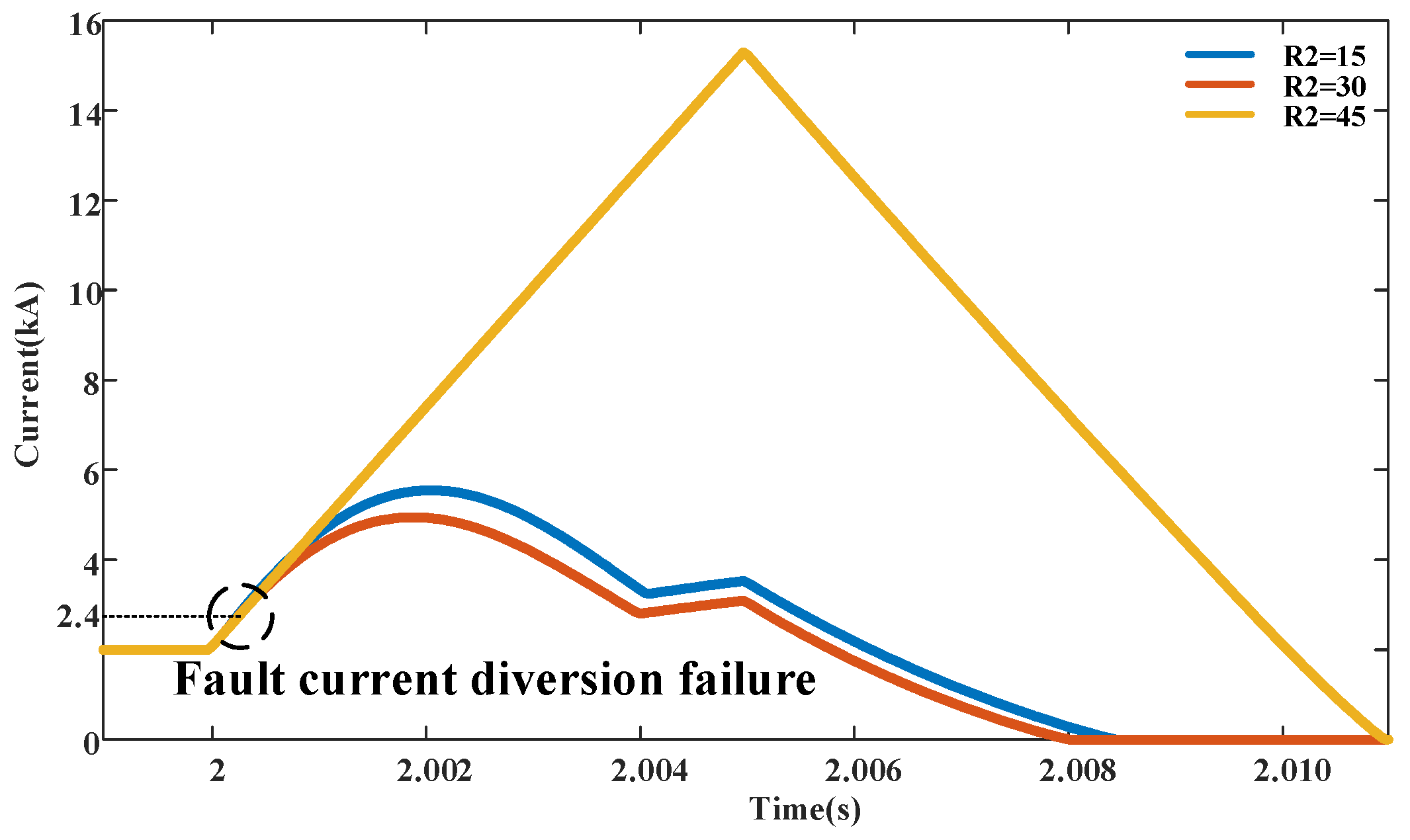

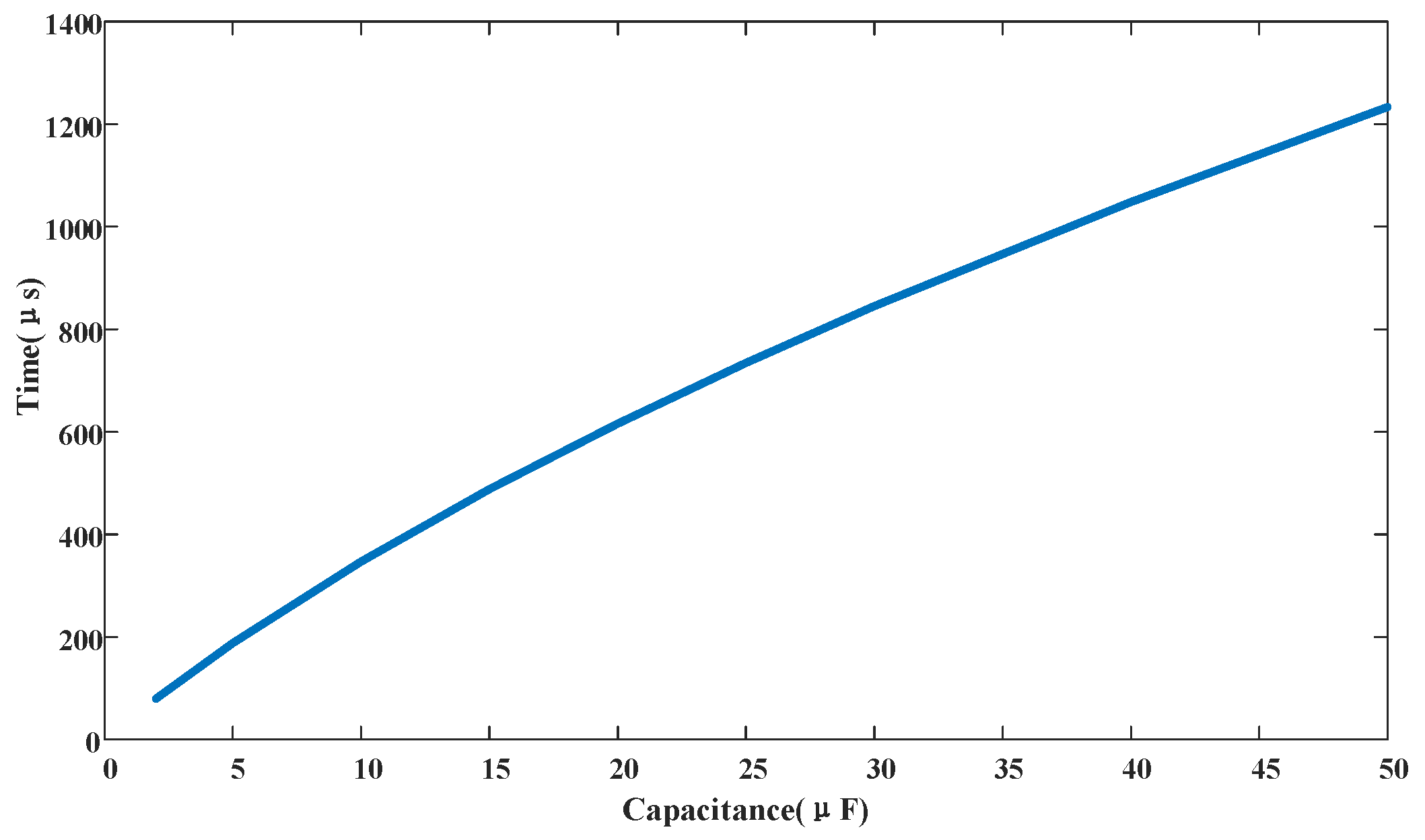

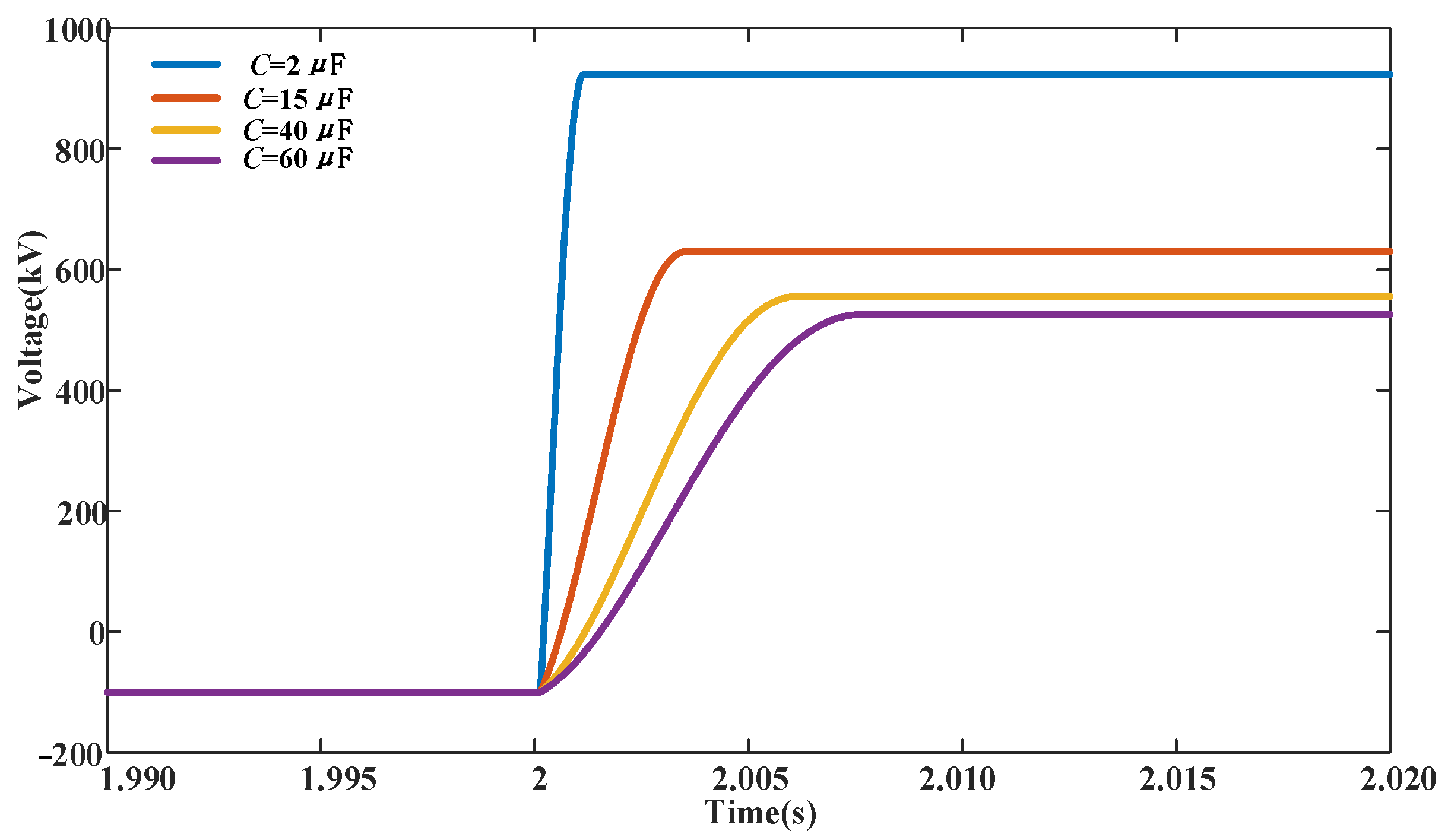

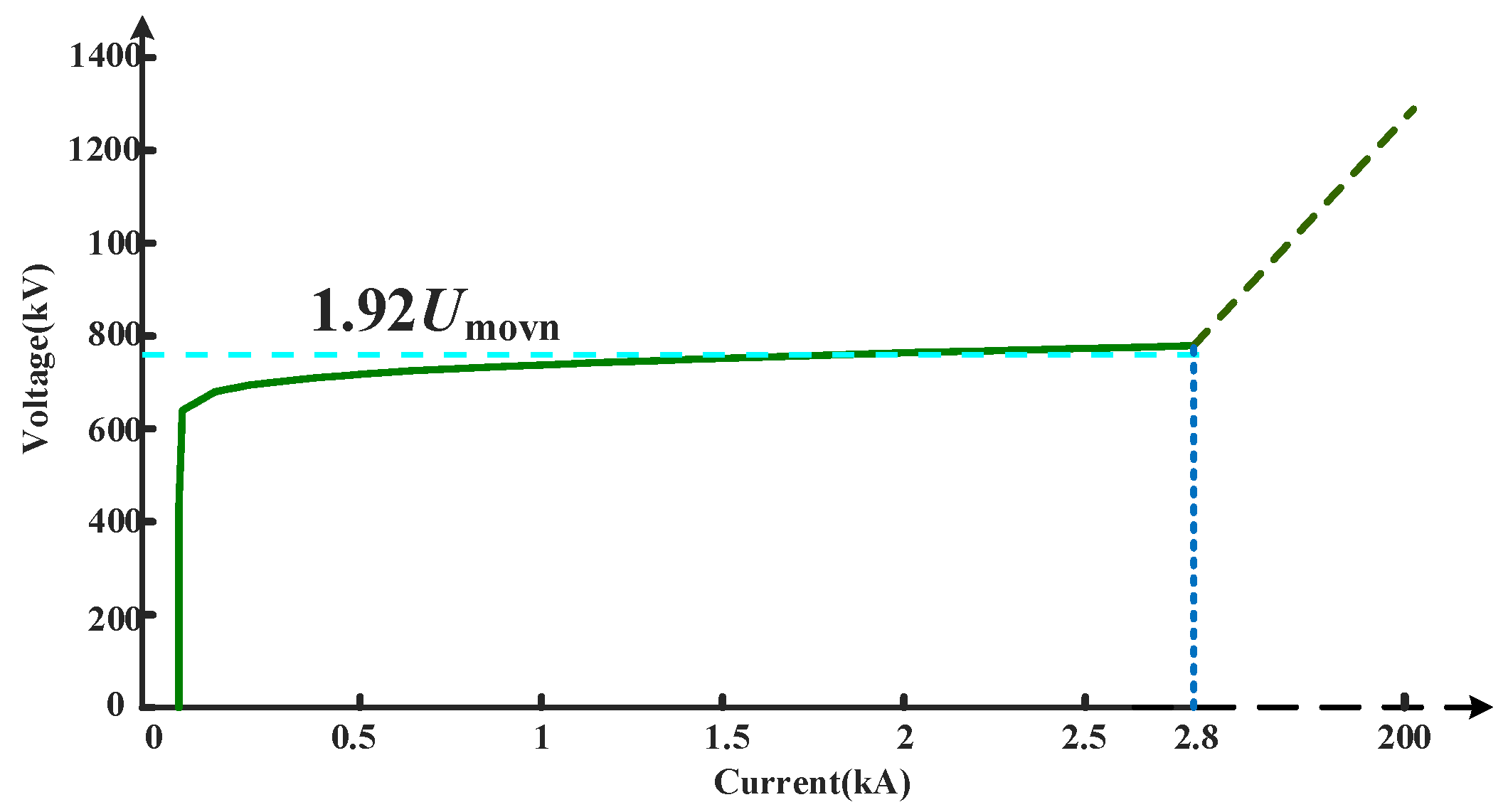

3. Parameter Design of Current Limiter

4. Pre-Charge Capacitor Charging Scheme and Current-Limiting Inductor Fast Bypass Technology

4.1. Pre-Charging Capacitor Charging Scheme

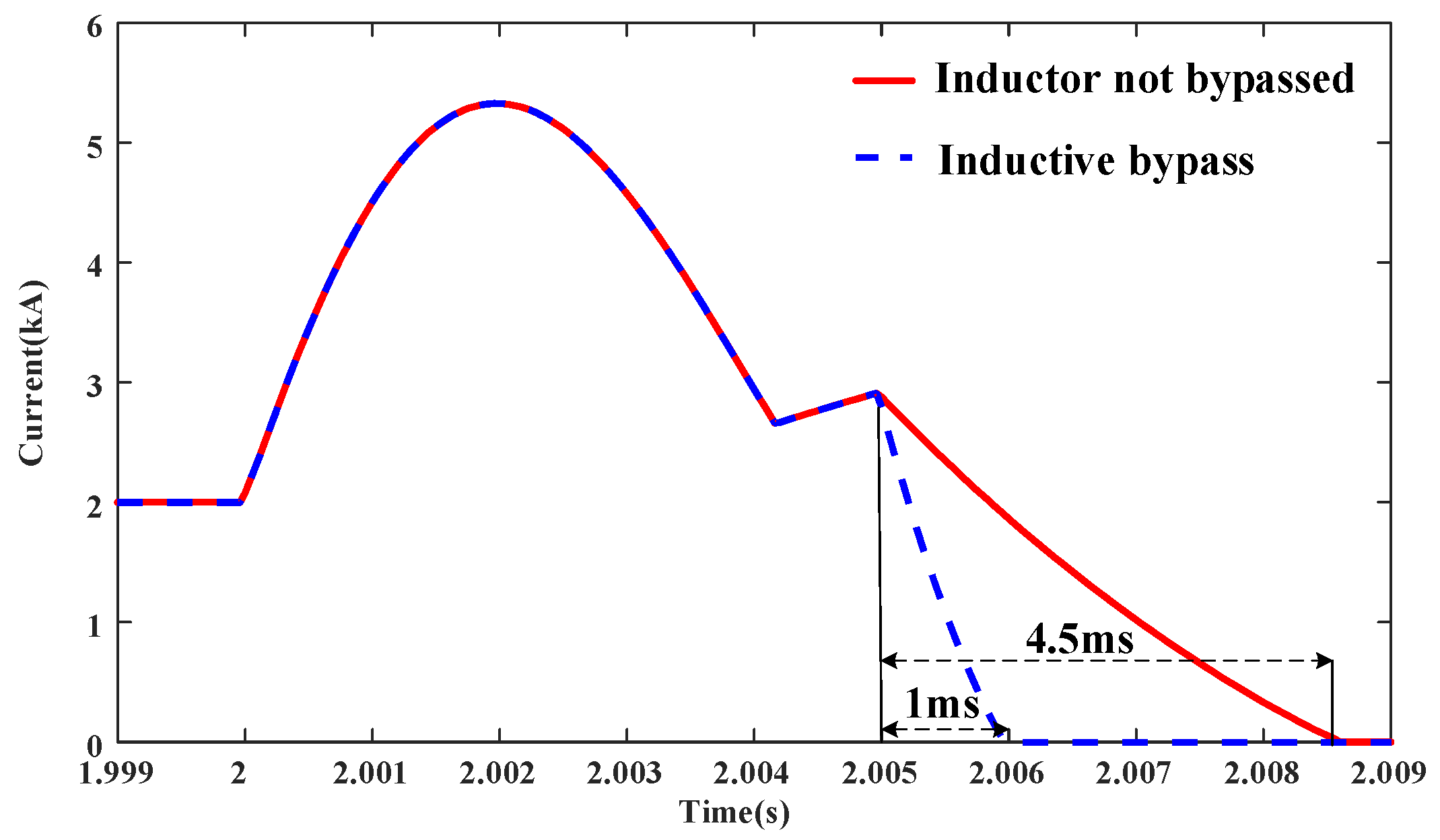

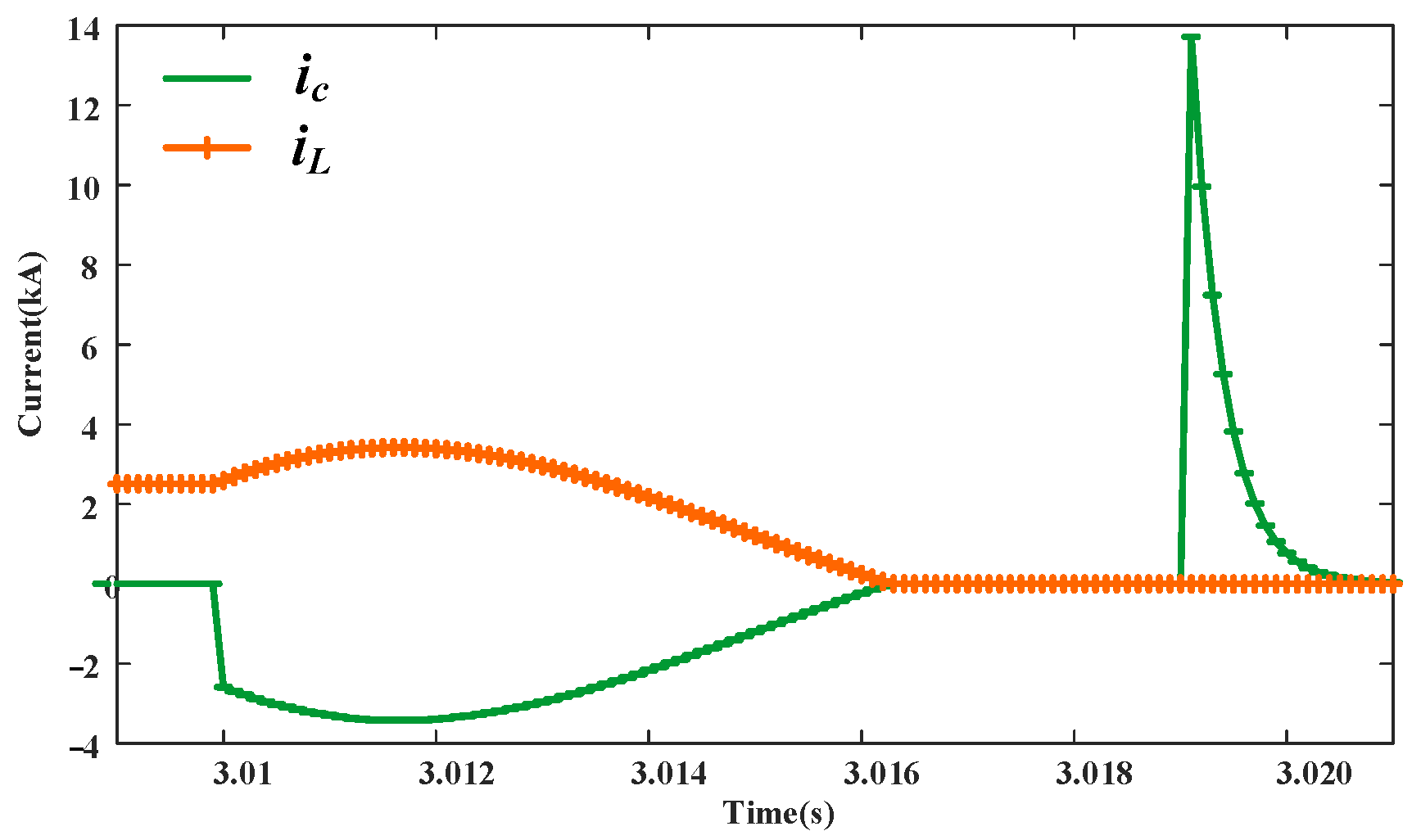

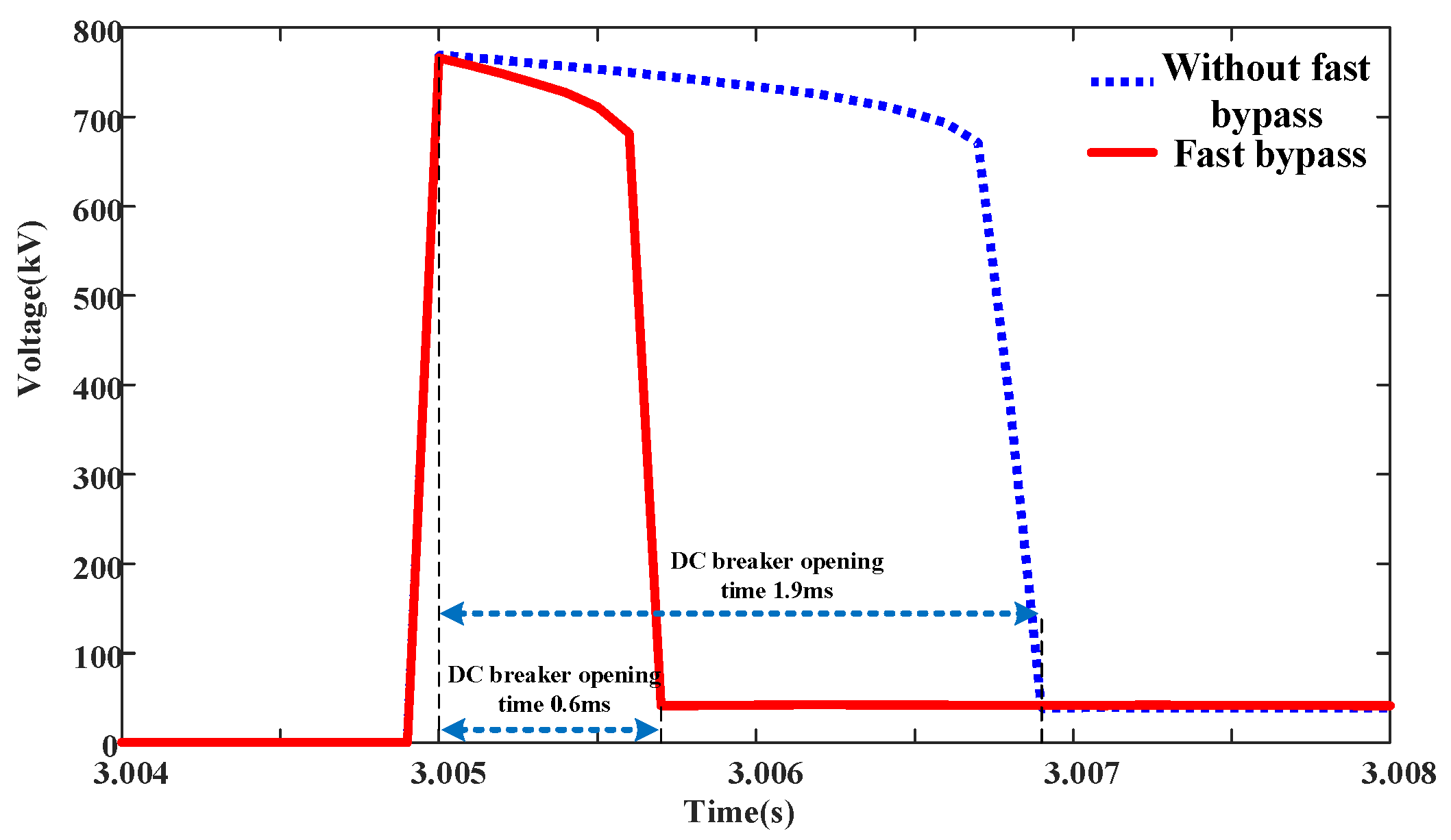

4.2. Current-Limiting Inductor Fast Bypass Technology

4.2.1. Inductive Fast Bypass Method

- (1)

- Once the system experiences failure, the current limiter is activated in the fault circuit using the sequence of actions outlined in the previous section. This is repeated until the capacitor commutation current limiter was completely operational. Further refinement of the system may be required to ensure optimal performance in the event of future failure.

- (2)

- Fast bypass of current-limiting inductor.

- (3)

- Energy consumption of current-limiting inductor.

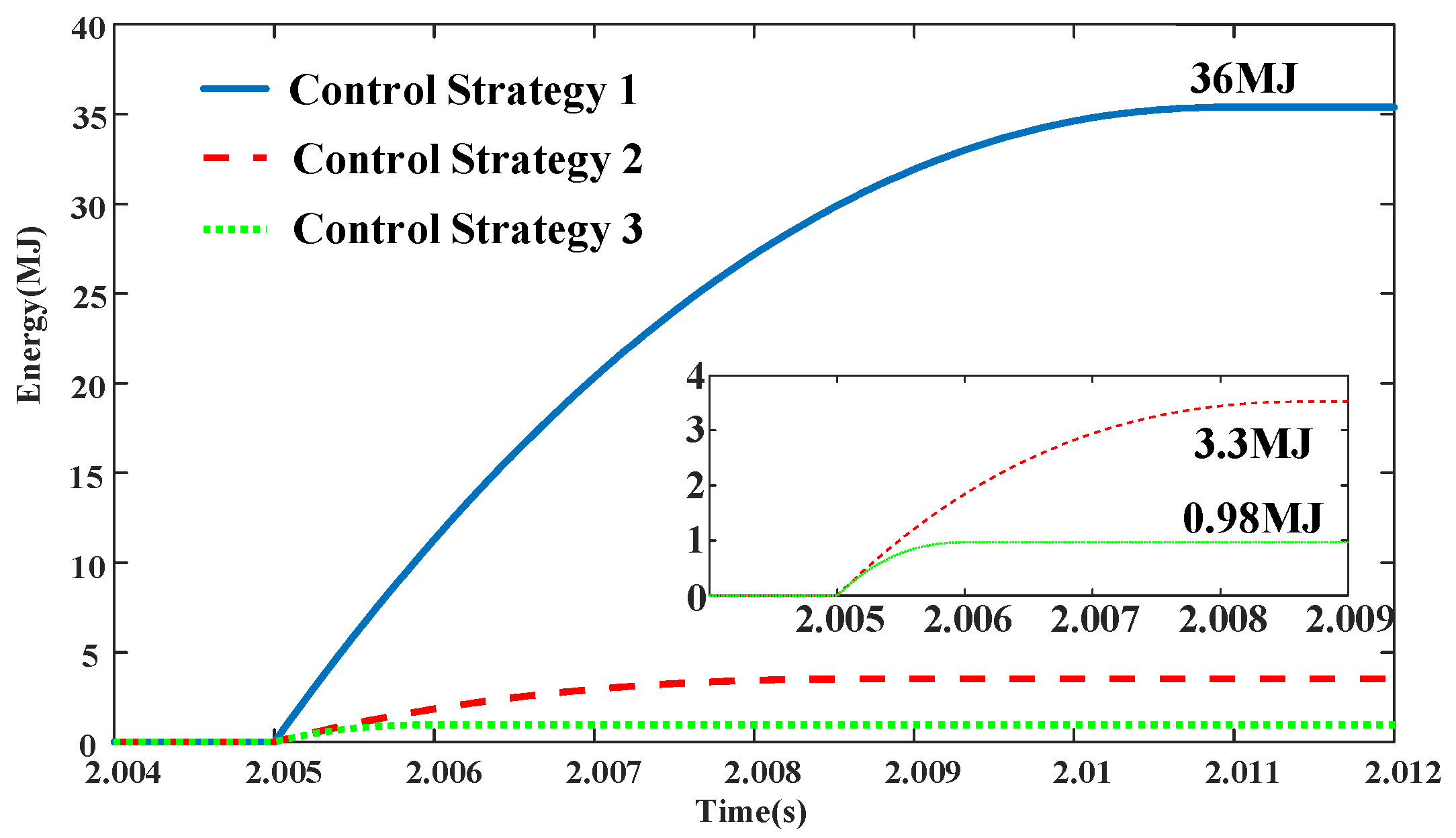

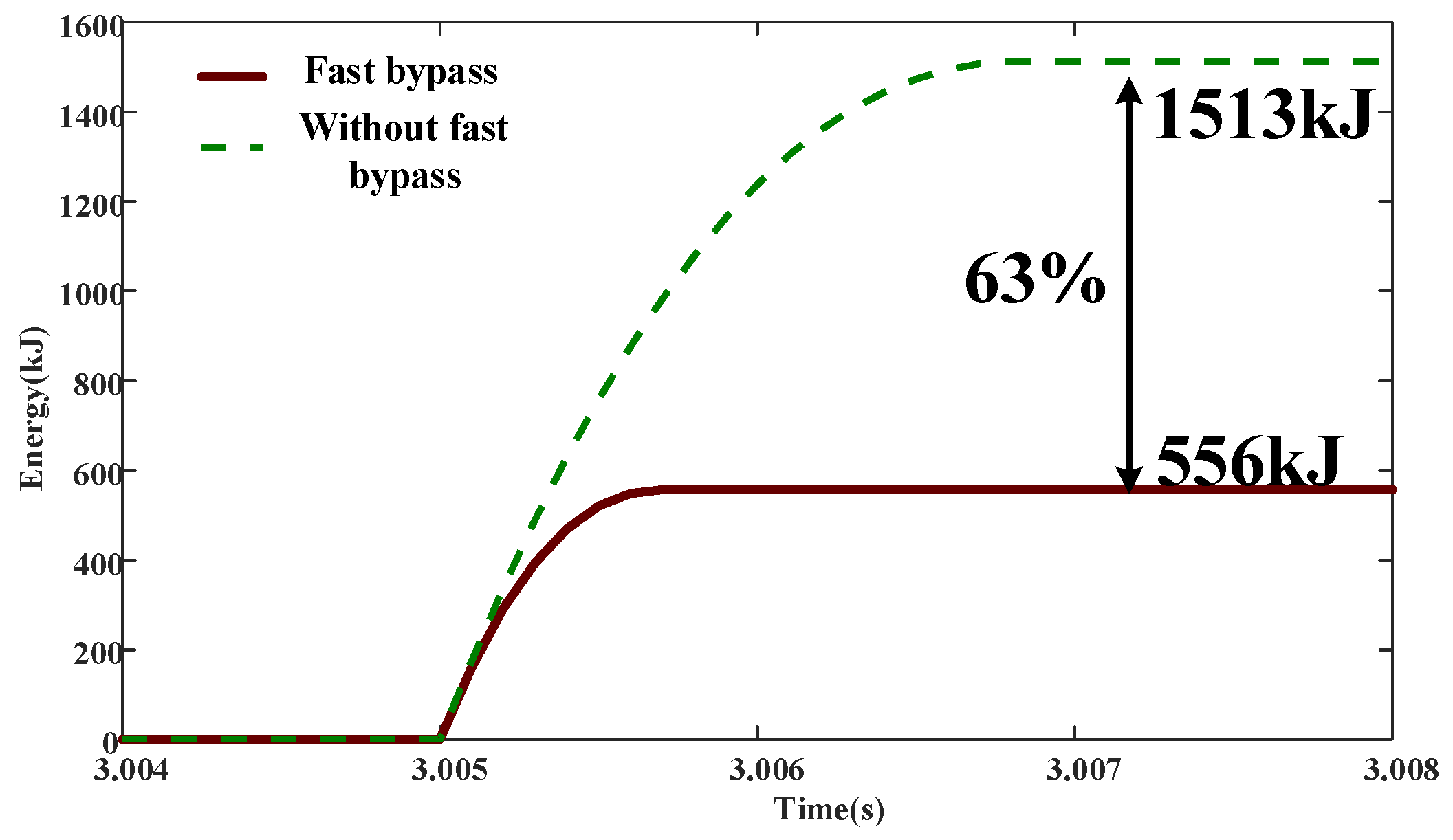

4.2.2. Approximate Calculation of Arrester Energy Consumption Reduction

5. Model Validation

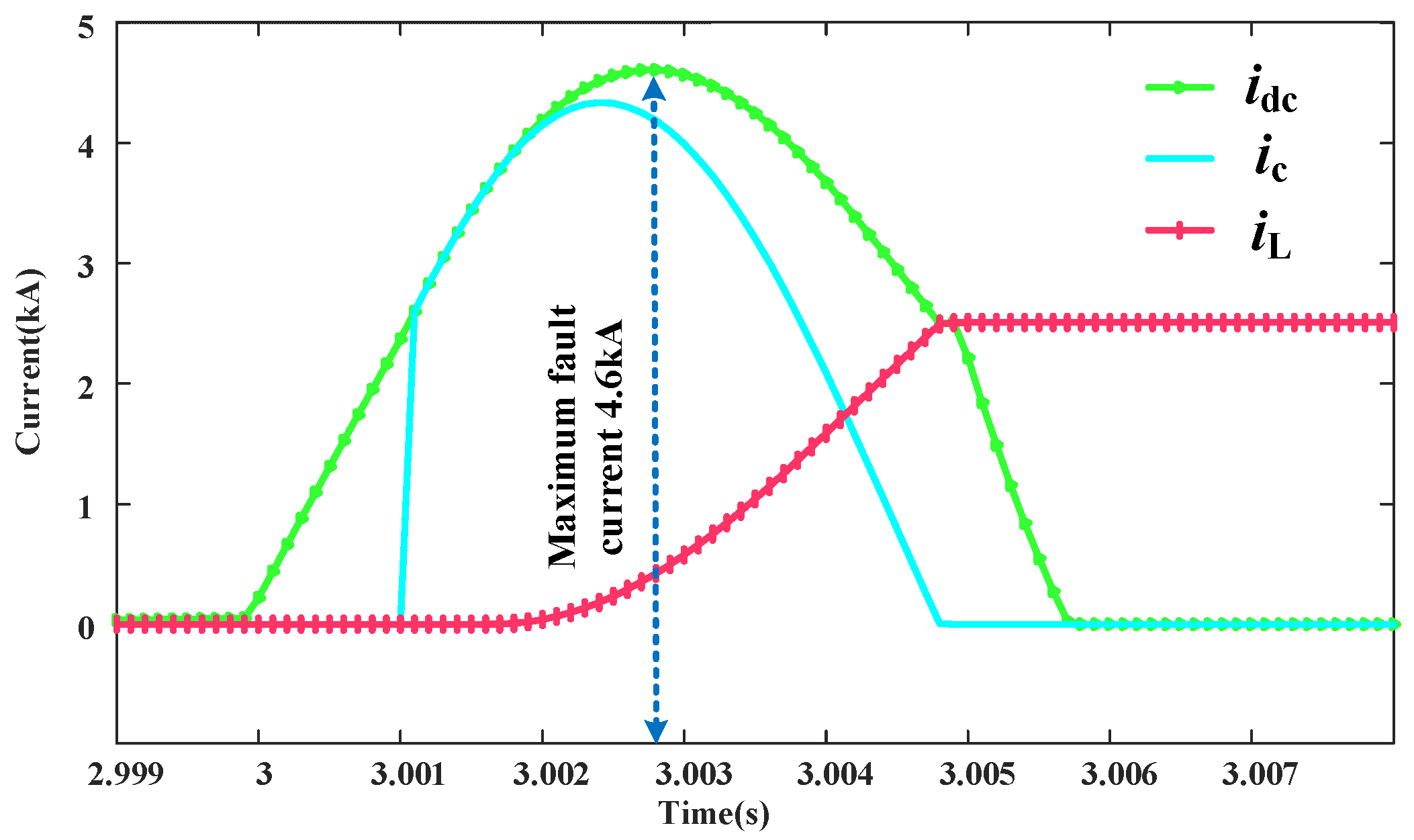

5.1. DC System Verification

5.2. Three-Terminal IPFC DC Side Simulation Verification

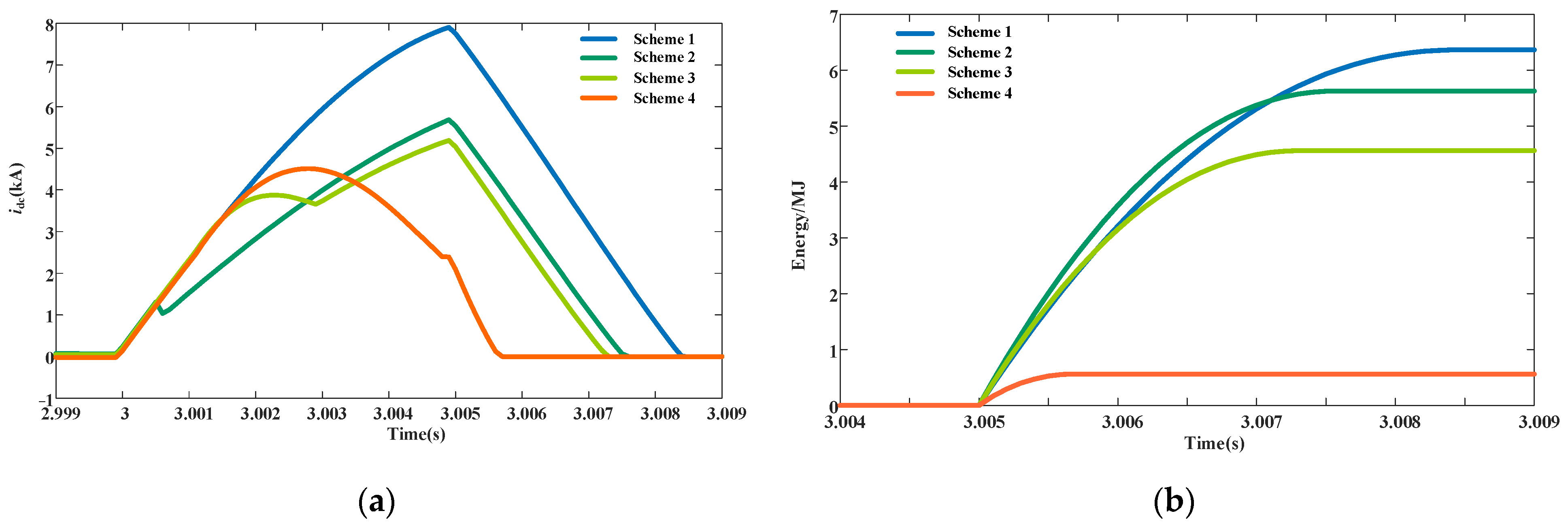

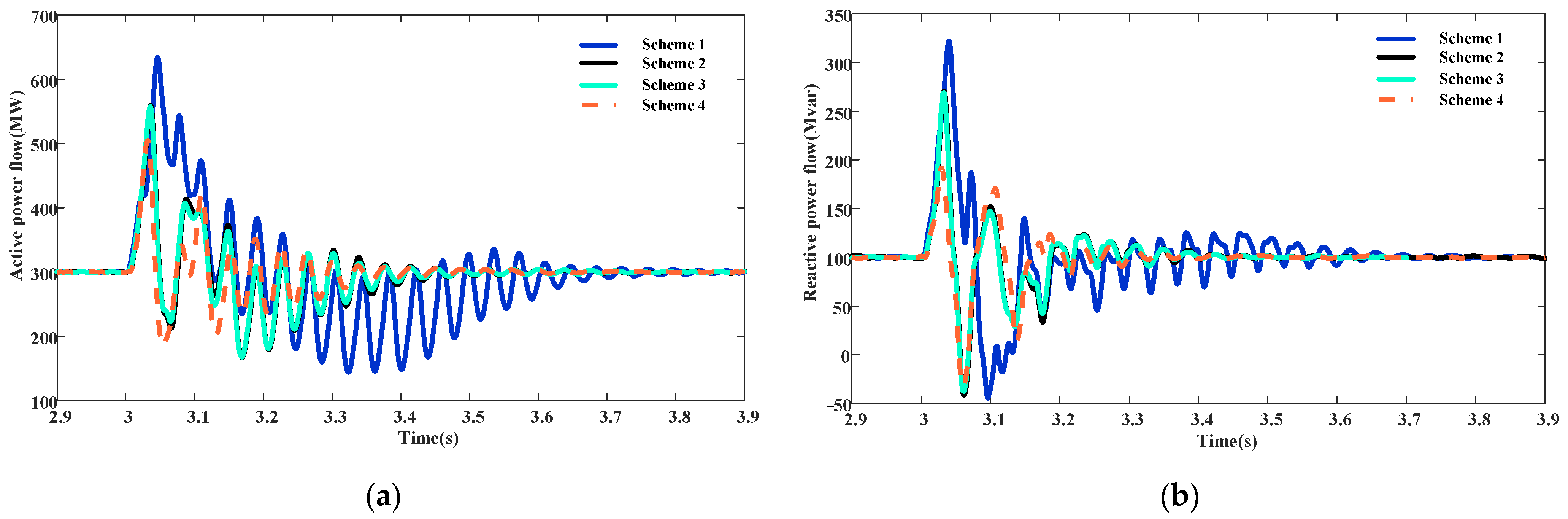

5.3. Comparison and Verification with Other Fault Current Limiters

6. Conclusions

- (1)

- The proposed IPFC current limiter can limit the DC-side short-circuit current below the blocking protection threshold such that a non-blocking fault ride-through can be realized. This improves the survivability of the IPFC under fault conditions.

- (2)

- The operation loss of the current limiter proposed in this study is low. Compared to other current limiters that use fully controlled devices, the current limiter proposed in this article only uses thyristors, greatly reducing the cost.

- (3)

- By adopting the thyristor fast bypass scheme proposed in this study, the current limiter can further reduce the energy consumption of the arrester during the circuit breaker operation, which further reduces the investment cost of the circuit breaker.

- (4)

- After the circuit breaker operates, the IPFC using the proposed strategy can restore the DC voltage stability and control ability in a short time.

- (5)

- In this paper, we propose and validate an FCL for the IPFC. However, post-fault reclosing and the corresponding control strategies were not studied. Future research should focus on post-fault reclosing and control strategies to enhance the post-fault survivability of the IPFC.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Wang, Z.; Mu, L. Microgrid Fault Detection Method Coordinated with a Sequence Component Current-Based Fault Control Strategy. Prot. Control Mod. Power Syst. 2024, 9, 81–93. [Google Scholar] [CrossRef]

- Simatupang, D.P.; Choi, J. Integrated Photovoltaic Inverters Based on Unified Power Quality Conditioner with Voltage Compensation for Submarine Distribution System. Energies 2018, 11, 2927. [Google Scholar] [CrossRef]

- Simatupang, D.P.; Choi, J. PV Source Inverter with Voltage Compensation for Weak Grid Based on UPQC Configuration. In Proceedings of the 2018 IEEE 18th International Power Electronics and Motion Control Conference (PEMC), Budapest, Hungary, 26–30 August 2018; pp. 421–427. [Google Scholar]

- Xie, B.; Li, Z.; An, Y.; Zhao, J. The Coordinated Droop Control Strategy for Interline Power Flow Controller. In Proceedings of the 2022 IEEE 6th Conference on Energy Internet and Energy System Integration (EI2), Chengdu, China, 11–13 November 2022; pp. 849–852. [Google Scholar]

- Sau-Bassols, J.; Zhao, Q.; García-González, J.; Prieto-Araujo, E.; Gomis-Bellmunt, O. Optimal Power Flow Operation of an Interline Current Flow Controller in an Hybrid AC/DC Meshed Grid. Electr. Power Syst. Res. 2019, 177, 105935. [Google Scholar] [CrossRef]

- Ebeed, M.; Kamel, S.; Jurado, F. Determination of IPFC Operating Constraints in Power Flow Analysis. Int. J. Electr. Power Energy Syst. 2016, 81, 299–307. [Google Scholar] [CrossRef]

- Ghorbani, A.; Soleymani, S.; Mozafari, B. A PMU-Based LOE Protection of Synchronous Generator in the Presence of GIPFC. IEEE Trans. Power Deliv. 2016, 31, 551–558. [Google Scholar] [CrossRef]

- Yanfang, F.; Yuehua, L.; Long, M.; Zhijun, C. Research on Specific Fault Analysis and Protection Countermeasures of AC/DC Hybrid System. In Proceedings of the 16th IET International Conference on AC and DC Power Transmission (ACDC 2020), Online, 2–3 July 2020; Volume 2020, pp. 1910–1915. [Google Scholar]

- Liu, G.; Xu, F.; Xu, Z.; Zhang, Z.; Tang, G. Assembly HVDC Breaker for HVDC Grids With Modular Multilevel Converters. IEEE Trans. Power Electron. 2017, 32, 931–941. [Google Scholar] [CrossRef]

- Taherzadeh, E.; Radmanesh, H.; Javadi, S.; Gharehpetian, G.B. Circuit Breakers in HVDC Systems: State-of-the-Art Review and Future Trends. Prot. Control Mod. Power Syst. 2023, 8, 38. [Google Scholar] [CrossRef]

- Wang, Y.; Yuan, Z.; Wen, W.; Ji, Y.; Fu, J.; Li, Y.; Zhao, Y. Generalised Protection Strategy for HB-MMC-MTDC Systems with RL-FCL under DC Faults. IET Gener. Transm. Distrib. 2018, 12, 1231–1239. [Google Scholar] [CrossRef]

- Lin, W.; Jovcic, D.; Nguefeu, S.; Saad, H. Protection of Full Bridge MMC DC Grid Employing Mechanical DC Circuit Breakers. In Proceedings of the 2017 IEEE Power & Energy Society General Meeting, Chicago, IL, USA, 16–20 July 2017; pp. 1–5. [Google Scholar]

- Wang, T.; Chu, X.; Hussain, K.S.T.; Gao, J. Fault Control and Line Protection Strategy for LVDC Microgrids Based on Modified High-Frequency-Link DC Solid State Transformer. Int. J. Electr. Power Energy Syst. 2022, 140, 108052. [Google Scholar] [CrossRef]

- Xu, J.; Wu, D.; Li, J.; Zhao, X.; Jia, X. The Voltage Clamping Based DC Circuit Breaker With Decoupled Fault Isolation and Energy Dissipation Processes. IEEE Trans. Power Deliv. 2021, 36, 64–73. [Google Scholar] [CrossRef]

- Pan, Y.; Chen, L.; Yuan, Z.; Xu, M.; Liu, L.; Li, G. Research on Current Limiting and Energy Limiting Technology for DC Power Grid Fault. Proc. CSEE 2020, 40, 2006–2015. [Google Scholar] [CrossRef]

- Zhu, J.; Zeng, Q.; Guo, X.; Jia, H.; Cui, B.; Wei, T. Multiport Current Injection Hybrid DC Circuit Breaker With Simple Bridge Arm Circuit. IEEE Trans. Ind. Electron. 2023, 70, 9882–9892. [Google Scholar] [CrossRef]

- Wang, W.; Barnes, M.; Marjanovic, O.; Cwikowski, O. Impact of DC Breaker Systems on Multiterminal VSC-HVDC Stability. IEEE Trans. Power Deliv. 2016, 31, 769–779. [Google Scholar] [CrossRef]

- Beerten, J.; D’Arco, S.; Suul, J.A. Identification and Small-Signal Analysis of Interaction Modes in VSC MTDC Systems. IEEE Trans. Power Deliv. 2016, 31, 888–897. [Google Scholar] [CrossRef]

- Xia, D.; Qiu, Q.; Zhang, Z.; Liu, S.; Xia, Z. Magnetic Field and Characteristic Analysis of the Superconducting Fault Current Limiter for DC Applications. IEEE Trans. Appl. Supercond. 2018, 28, 5601405. [Google Scholar] [CrossRef]

- Steurer, M.; Frohlich, K.; Holaus, W.; Kaltenegger, K. A Novel Hybrid Current-Limiting Circuit Breaker for Medium Voltage: Principle and Test Results. IEEE Trans. Power Deliv. 2003, 18, 460–467. [Google Scholar] [CrossRef]

- Ma, T.; Dai, S.; Song, M.; Li, C. Electromagnetic Design of High-Temperature Superconducting DC Bias Winding for Single-Phase 500 kV Saturated Iron-Core Fault Current Limiter. IEEE Trans. Appl. Supercond. 2018, 28, 5200805. [Google Scholar] [CrossRef]

- Fereidouni, A.R.; Vahidi, B.; Hosseini Mehr, T. The Impact of Solid State Fault Current Limiter on Power Network With Wind-Turbine Power Generation. IEEE Trans. Smart Grid 2013, 4, 1188–1196. [Google Scholar] [CrossRef]

- Radmanesh, H.; Fathi, S.H.; Gharehpetian, G.B.; Heidary, A. Bridge-Type Solid-State Fault Current Limiter Based on AC/DC Reactor. IEEE Trans. Power Deliv. 2016, 31, 200–209. [Google Scholar] [CrossRef]

- Jeong, J.-S.; Choi, H.-S. A Study on Increasing the Capacity of Transformer-Type Superconducting DC Circuit Breaker. IEEE Trans. Appl. Supercond. 2023, 33, 5500405. [Google Scholar] [CrossRef]

- Yang, S.; Xiang, W.; Lu, X.; Zuo, W.; Wen, J. An Adaptive Reclosing Strategy for MMC-HVDC Systems With Hybrid DC Circuit Breakers. IEEE Trans. Power Deliv. 2020, 35, 1111–1123. [Google Scholar] [CrossRef]

- Tao, C.; Wang, W.; Li, T.; Zhang, J. Current Limiting Hybrid DC Circuit Breaker Based on Capacitor Commutation. Dianwang JishuPower Syst. Technol. 2023, 47, 5138–5146. [Google Scholar] [CrossRef]

- Bucher, M.K.; Wiget, R.; Andersson, G.; Franck, C.M. Multiterminal HVDC Networks—What Is the Preferred Topology? IEEE Trans. Power Deliv. 2014, 29, 406–413. [Google Scholar] [CrossRef]

- Zhang, C.; Wu, D.; Chen, K.; Li, J.; Xu, J.; Zhao, C. DC Fault Current Limiter Based on Precharge Commutation Capacitor. Zhongguo Dianji Gongcheng Xuebao Proc. Chin. Soc. Electr. Eng. 2019, 39, 54–62. [Google Scholar] [CrossRef]

| Time Frame | Node Features |

|---|---|

| t0 | Time of failure |

| t1 | Fault detected |

| t2 | uc = 0; the capacitor has just discharged |

| t3 | i1 = idc; ic = 0; the current limiter is fully engaged |

| t4 | DCCB action |

| Converter Station | Number of Bridge Arm Submodules | Submodule Capacitance/μF | Bridge Arm Reactance/mH | Control Strategy |

|---|---|---|---|---|

| IPFC1 | 200 | 3000 | 100 | Udc = 400 kV Q = 0 MVar |

| IPFC2 | 200 | 3000 | 100 | P = 400 MW Q = 200 MVar |

| IPFC3 | 200 | 3000 | 100 | P = 300 MW Q = 100 MVar |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, J.; Shi, H.; Li, B.; Jiang, Q.; Yin, Y.; Zhang, Y.; Liu, T.; Nie, C. Fault Ride-Through Method for Interline Power Flow Controller Based on DC Current Limiter. Electronics 2024, 13, 1038. https://doi.org/10.3390/electronics13061038

Li J, Shi H, Li B, Jiang Q, Yin Y, Zhang Y, Liu T, Nie C. Fault Ride-Through Method for Interline Power Flow Controller Based on DC Current Limiter. Electronics. 2024; 13(6):1038. https://doi.org/10.3390/electronics13061038

Chicago/Turabian StyleLi, Jiajun, Huabo Shi, Baohong Li, Qin Jiang, Yue Yin, Yingmin Zhang, Tianqi Liu, and Chang Nie. 2024. "Fault Ride-Through Method for Interline Power Flow Controller Based on DC Current Limiter" Electronics 13, no. 6: 1038. https://doi.org/10.3390/electronics13061038