A Modified SVPWM Strategy for Reducing PWM Voltage Noise and Balancing Neutral Point Potential

Abstract

1. Introduction

2. Introduction of the NPB–RSVPWM Strategy

2.1. Introduction of the Random Switching Frequency

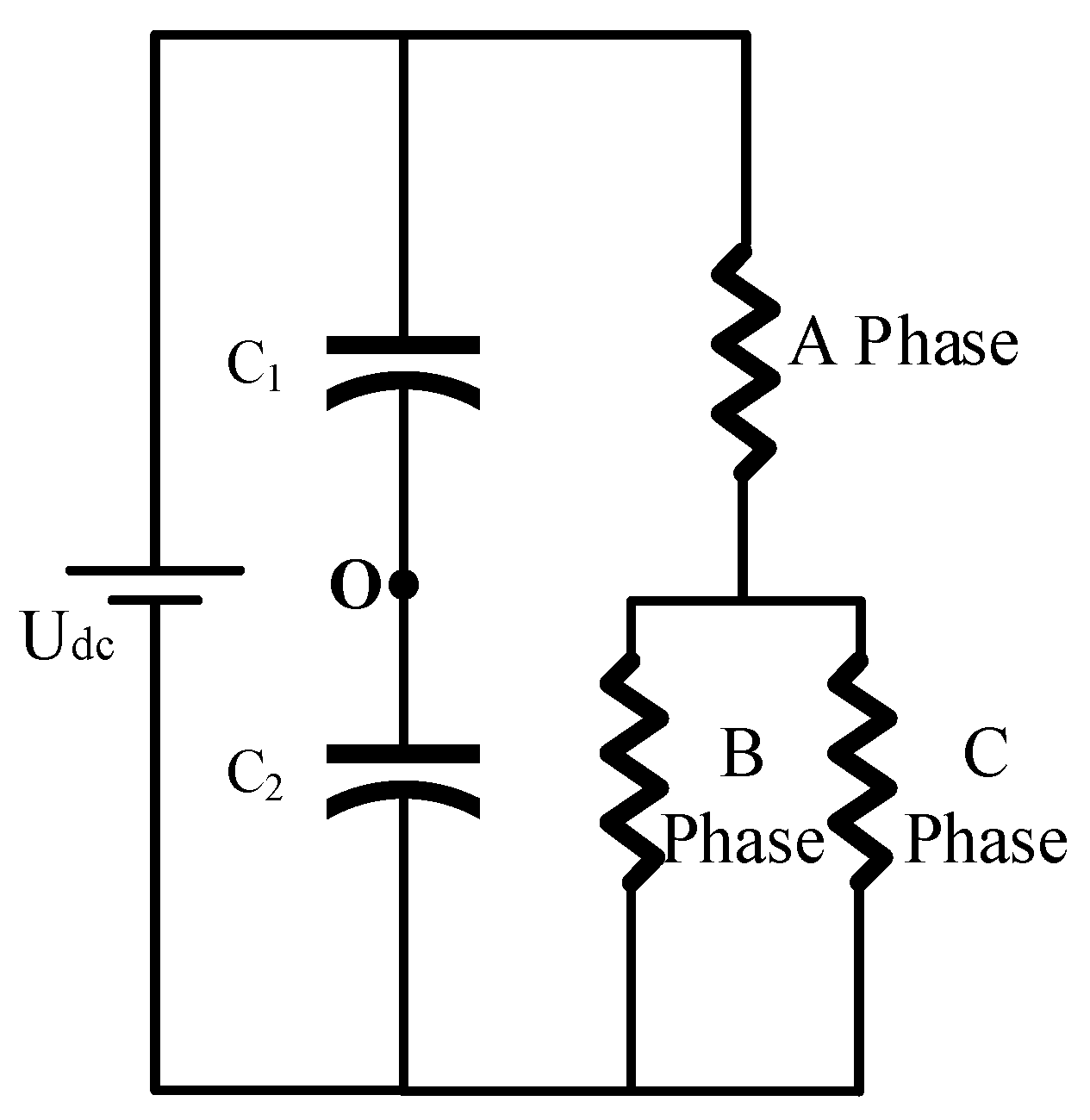

2.2. Analysis of Neutral-Point Potential Imbalance

2.3. The Method of Balancing Midpoint Potential

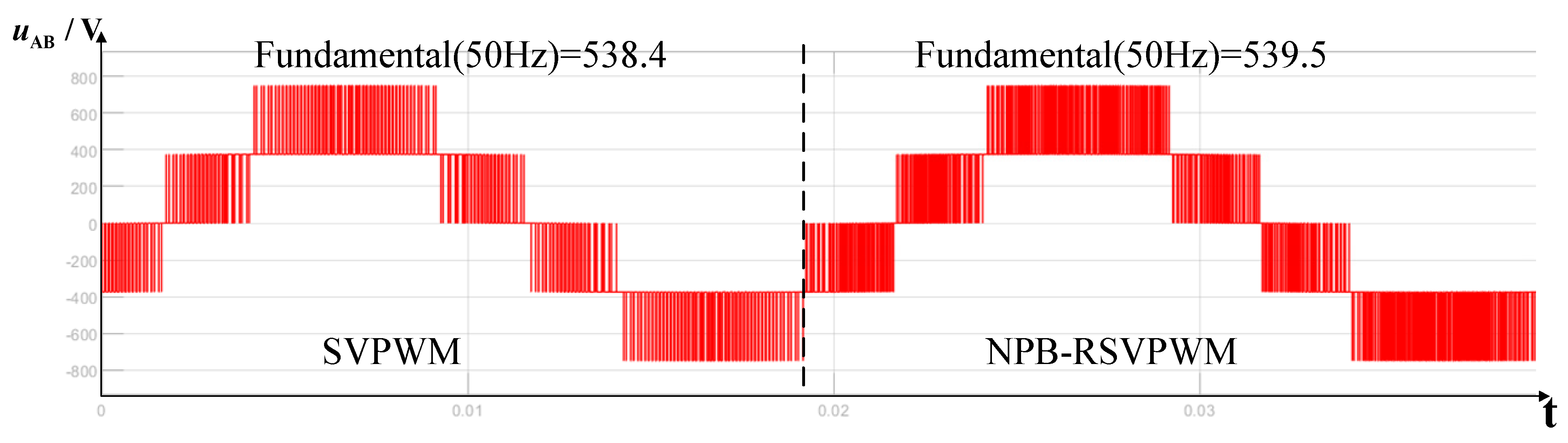

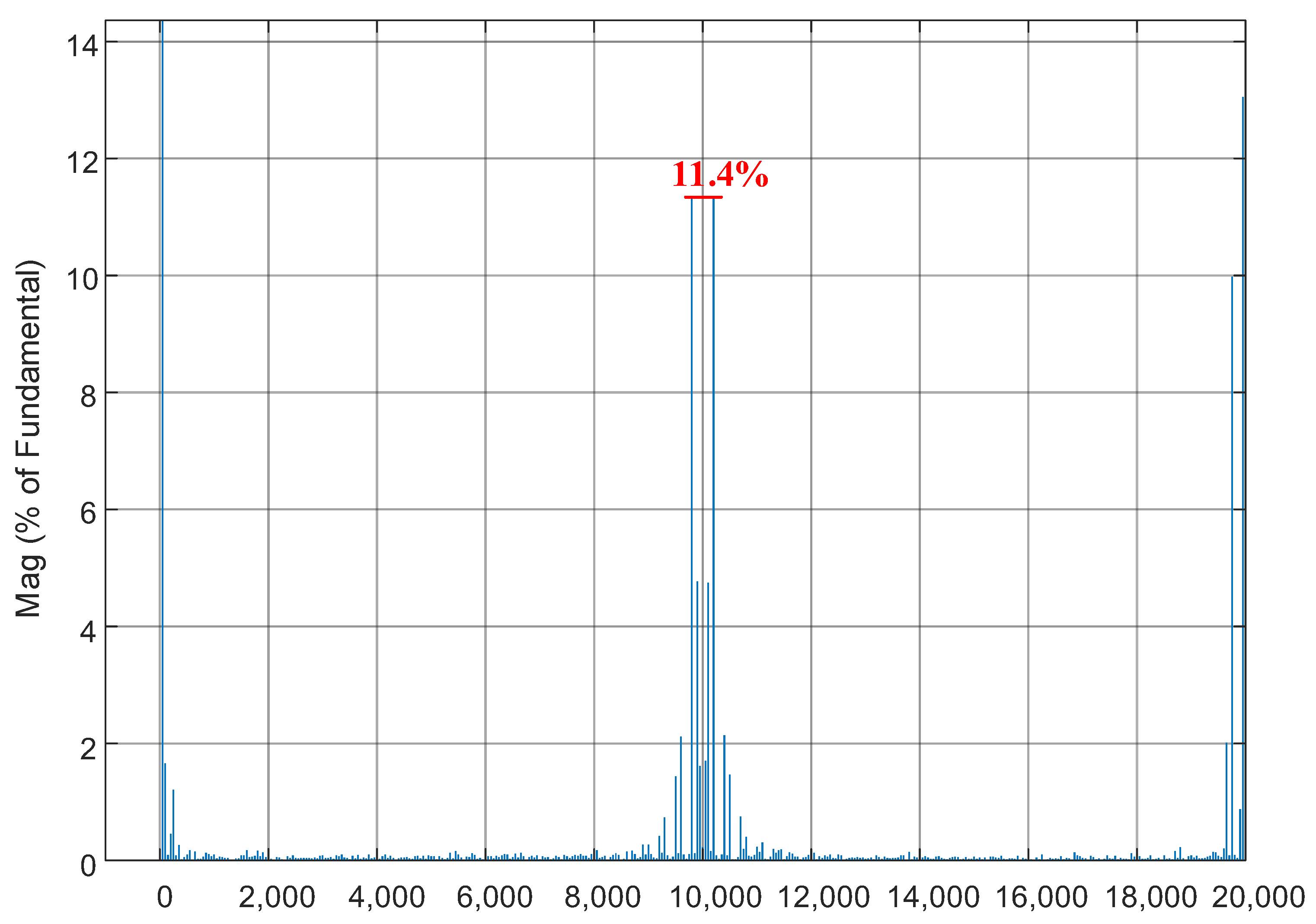

3. Simulation Verification

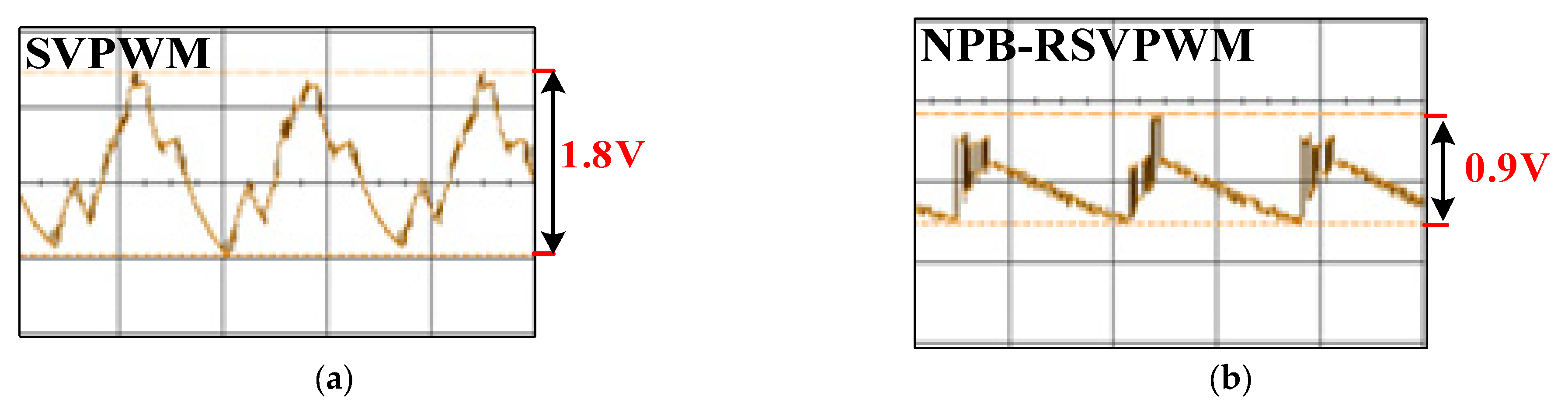

4. Experimental Verification

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Wen, H.; Xiao, W.; Wen, X.; Armstrong, P. Analysis and Evaluation of DC-Link Capacitors for High-Power-Density Electric Vehicle Drive Systems. IEEE Trans. Veh. Technol. 2012, 61, 2950–2964. [Google Scholar]

- Binojkumar, A.C.; Saritha, B.; Narayanan, G. Acoustic Noise Characterization of Space Vector Modulated Induction Motor Drives—An Experimental Approach. IEEE Trans. Ind. Electron. 2014, 62, 3362–3371. [Google Scholar] [CrossRef]

- Le Besnerais, J.; Lanfranchi, V.; Hecquet, M.; Brochet, P. Characterization and Reduction of Audible Magnetic Noise Due to PWM Supply in Induction Machines. IEEE Trans. Ind. Electron. 2010, 57, 1288–1295. [Google Scholar] [CrossRef]

- Liang, W.; Luk, P.C.-K.; Fei, W. Analytical Investigation of Sideband Electromagnetic Vibration in Integral-Slot PMSM Drive With SVPWM Technique. IEEE Trans. Power Electron. 2017, 32, 4785–4795. [Google Scholar] [CrossRef]

- Liang, W.; Wang, J.; Luk, P.C.-K.; Fang, W.; Fei, W. Analytical Modeling of Current Harmonic Components in PMSM Drive With Voltage-Source Inverter by SVPWM Technique. IEEE Trans. Energy Convers. 2014, 29, 673–680. [Google Scholar] [CrossRef]

- Sekhar, K.R.; Srinivas, S. Torque ripple reduction PWMs for a single DC source powered dual-inverter fed open-end winding induction motor drive. IET Power Electron. 2018, 11, 43–51. [Google Scholar] [CrossRef]

- von Jouanne, A.; Rendusara, D.; Enjeti, P.; Gray, J. Filtering techniques to minimize the effect of long motor leads on PWM inverter-fed AC motor drive systems. IEEE Trans. Ind. Appl. 1996, 32, 919–926. [Google Scholar] [CrossRef]

- Liu, S.; Liu, C. Virtual-vector-based robust predictive current control for dual three-phase PMSM. IEEE Trans. Ind. Electron. 2021, 68, 2048–2058. [Google Scholar] [CrossRef]

- Lee, K.; Shen, G.; Yao, W.; Lu, Z. Performance characterization of random pulse width modulation algorithms in industrial and commercial adjustable-speed drives. IEEE Trans. Ind. Appl. 2017, 53, 1078–1108. [Google Scholar] [CrossRef]

- Kumar, A.B.C.; Narayanan, G. Variable-switching frequency PWM technique for induction motor drive to spread acoustic noise spectrum with reduced current ripple. IEEE Trans. Ind. Appl. 2016, 52, 3927–3938. [Google Scholar] [CrossRef]

- Jia, Y.; Wang, X.; Mao, L.; Yang, S.; Zhang, H. Application and simulation of SVM in three phase inverter. In Proceedings of the 2011 6th International Forum on Strategic Technology (IFOST), Harbin, China, 22–24 August 2011; Volume 1, pp. 541–544. [Google Scholar]

- Huang, Y.; Xu, Y.; Li, Y.; Yang, G.; Zou, J. PWM frequency voltage noise cancellation in three-phase VSI using the novel SVPWM strategy. IEEE Trans. Power Electron. 2018, 33, 8596–8606. [Google Scholar] [CrossRef]

- Peyghambari, A.; Dastfan, A.; Ahmadyfard, A. Selective voltage noise cancellation in three-phase inverter using random SVPWM. IEEE Trans. Power Electron. 2016, 31, 4604–4610. [Google Scholar] [CrossRef]

- Huang, Y.; Xu, Y.; Zhang, W.; Zou, J. Hybrid RPWM technique based on modified SVPWM to reduce the PWM acoustic noise. IEEE Trans. Power Electron. 2019, 34, 5667–5674. [Google Scholar] [CrossRef]

- Davis, T.T.; Gajare, P.M.; Dey, A. A novel floating capacitor voltage control technique for 9-level T-type inverter with reduced device count. In Proceedings of the IECON 2019—45th Annual Conference of the IEEE Industrial Electronics Society, Lisbon, Portugal, 14–17 October 2019; pp. 1526–1531. [Google Scholar]

- Muduli, U.R.; Behera, R.K. A Modified High Gain Boost TNPC Inverter with Neutral Point Balancing for Three-phase Induction Motor Driven Electric Vehicle. In Proceedings of the 2020 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Jaipur, India, 16–19 December 2020; pp. 1–6. [Google Scholar]

- Man, Y.K.; Bian, C.Y.; Xu, N.; Zhu, Z.Q. Influence of zero space vector and PWM switching frequency on acoustic noise induction motors. J. Northeast. Univ. (Nat. Sci.) 2002, 23, 738–741. [Google Scholar]

- Peng, H.; Yuan, Z.; Narayanasamy, B.; Zhao, X.; Deshpande, A.; Luo, F. Comprehensive analysis of three-phase three-level T-type neutral-point clamped inverter with hybrid switch combination. In Proceedings of the IEEE 10th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Xi’an, China, 3–6 June 2019; pp. 816–821. [Google Scholar]

- Liu, J.; Zhang, J.; Li, H. A T-type NPC three-level three-phase four-arm midpoint potential control strategy. J. Electr. Power Sources 2016, 14, 68–73. [Google Scholar]

- Li, W.; Feng, J.; Wang, C. Dead zone-free carrier cascade PWM control of TNPC inverter. J. Syst. Simul. 2016, 28, 1628–1636. [Google Scholar]

- Wang, S.; Yang, S.; Li, Y.; Xie, Z. Inverter common mode voltage suppression method based on virtual space vector overmodulation strategy. Electr. Power Autom. Equip. 2022, 42, 76–81+96. [Google Scholar]

- Siwakoti, Y.P.; Peng, F.Z.; Blaabjerg, F.; Loh, P.C.; Town, G.E. Impedance-Source Networks for Electric Power Conversion Part I: A Topological Review. IEEE Trans. Power Electron. 2015, 30, 699–716. [Google Scholar] [CrossRef]

- Stankovic, A.M.; Verghese, G.E.; Perreault, D.J. Analysis and synthesis of randomized modulation schemes for power converters. IEEE Trans. Power Electron. 1995, 10, 680–693. [Google Scholar] [CrossRef]

- Boudouda, A.; Boudjerda, N.; Melit, M.; Nekhoul, B.; El Khamlichi Drissi, K.; Kerroum, K. Optimized RPWM technique for a Variable Speed Drive using induction motor. In Proceedings of the International Symposium on Electromagnetic Compatibility—EMC EUROPE, Rome, Italy, 17–21 September 2012; pp. 1–6. [Google Scholar]

- Paramasivan, M.; Paulraj, M.M.; Balasubramanian, S. Assorted carrier-variable frequency-random PWM scheme for voltage source inverter. IET Power Electron. 2017, 10, 444–460. [Google Scholar] [CrossRef]

| Vector Vertex | Coordinate |

|---|---|

| O | (0, 0) |

| A | , 0) |

| B | ) |

| C | , 0) |

| D | ) |

| E | ) |

| Region | Order of the Vector State |

|---|---|

| 1 | ONN OON OOO POO OOO OON ONN |

| 2 | OON OOO POO PPO POO OOO OON |

| 3 | ONN OON PON POO PON OON ONN |

| 4 | OON PON POO PPO POO PON OON |

| 5 | ONN PNN PON POO PON PNN ONN |

| 6 | OON PON PPN PPO PPN PON OON |

| Small Vector | Small Vector | Middle Vector | |||

|---|---|---|---|---|---|

| OON | POO | PON | |||

| PPO | OON | OPN | |||

| NON | OPO | NPO | |||

| OPP | NOO | NOP | |||

| NNO | OOP | ONP | |||

| POP | ONO | PNO |

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| DC voltage | 600 V | Carrier frequency | 7.5–10 kHz |

| Capacitance value | 5 µF | Sampling frequency | 20 kHz |

| Modulation ratio | 0.9 | Three-phase load | 10 Ω |

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| DC voltage | 24 V | Carrier frequency | 7.5–10 kHz |

| Capacitance value | 5 µF | Sampling frequency | 20 kHz |

| Modulation ratio | 0.9 | Three-phase load | 10 Ω |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gong, R.; Wu, H.; Tang, J.; Wan, X. A Modified SVPWM Strategy for Reducing PWM Voltage Noise and Balancing Neutral Point Potential. Electronics 2024, 13, 1656. https://doi.org/10.3390/electronics13091656

Gong R, Wu H, Tang J, Wan X. A Modified SVPWM Strategy for Reducing PWM Voltage Noise and Balancing Neutral Point Potential. Electronics. 2024; 13(9):1656. https://doi.org/10.3390/electronics13091656

Chicago/Turabian StyleGong, Renxi, Hao Wu, Jing Tang, and Xingyuan Wan. 2024. "A Modified SVPWM Strategy for Reducing PWM Voltage Noise and Balancing Neutral Point Potential" Electronics 13, no. 9: 1656. https://doi.org/10.3390/electronics13091656

APA StyleGong, R., Wu, H., Tang, J., & Wan, X. (2024). A Modified SVPWM Strategy for Reducing PWM Voltage Noise and Balancing Neutral Point Potential. Electronics, 13(9), 1656. https://doi.org/10.3390/electronics13091656