A Review of Circuits and Systems for Advanced Sub-THz Transceivers in Wireless Communication

Abstract

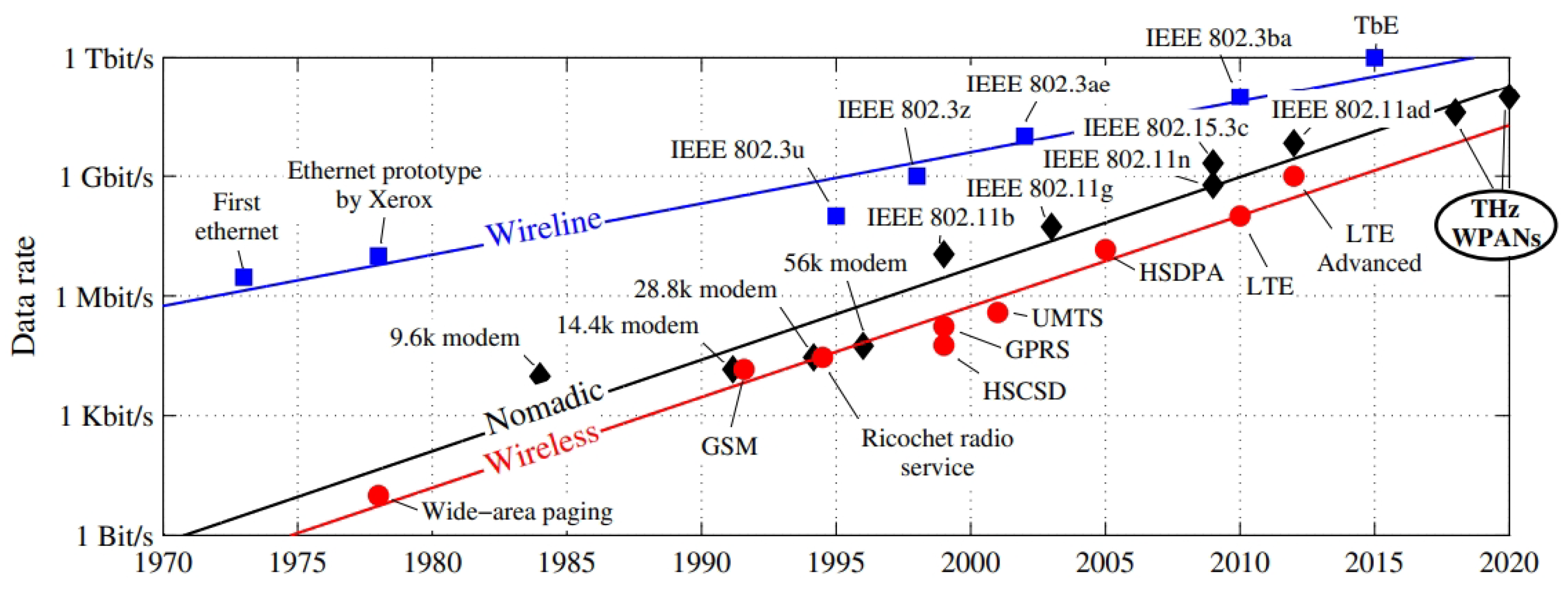

1. Introduction

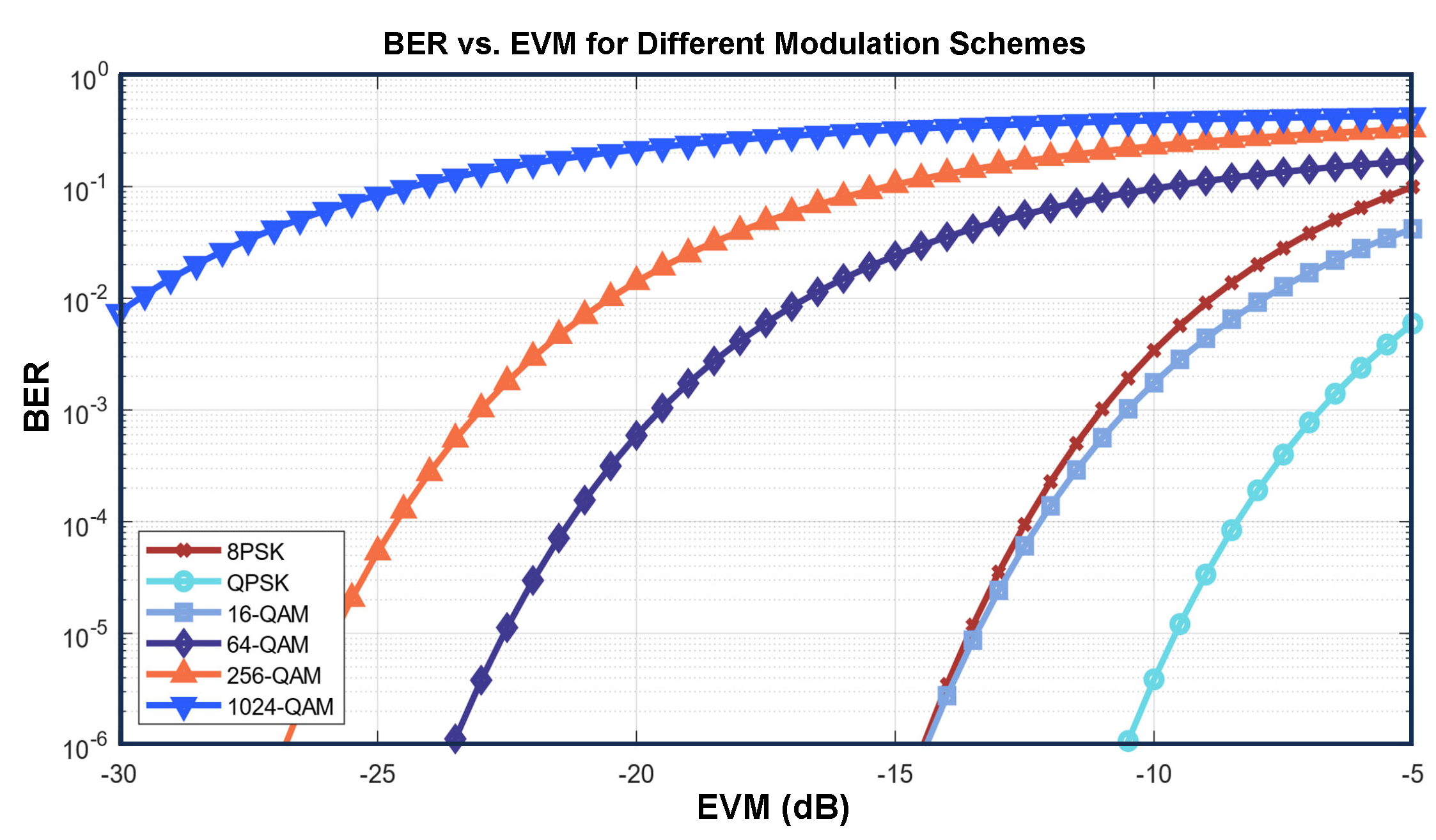

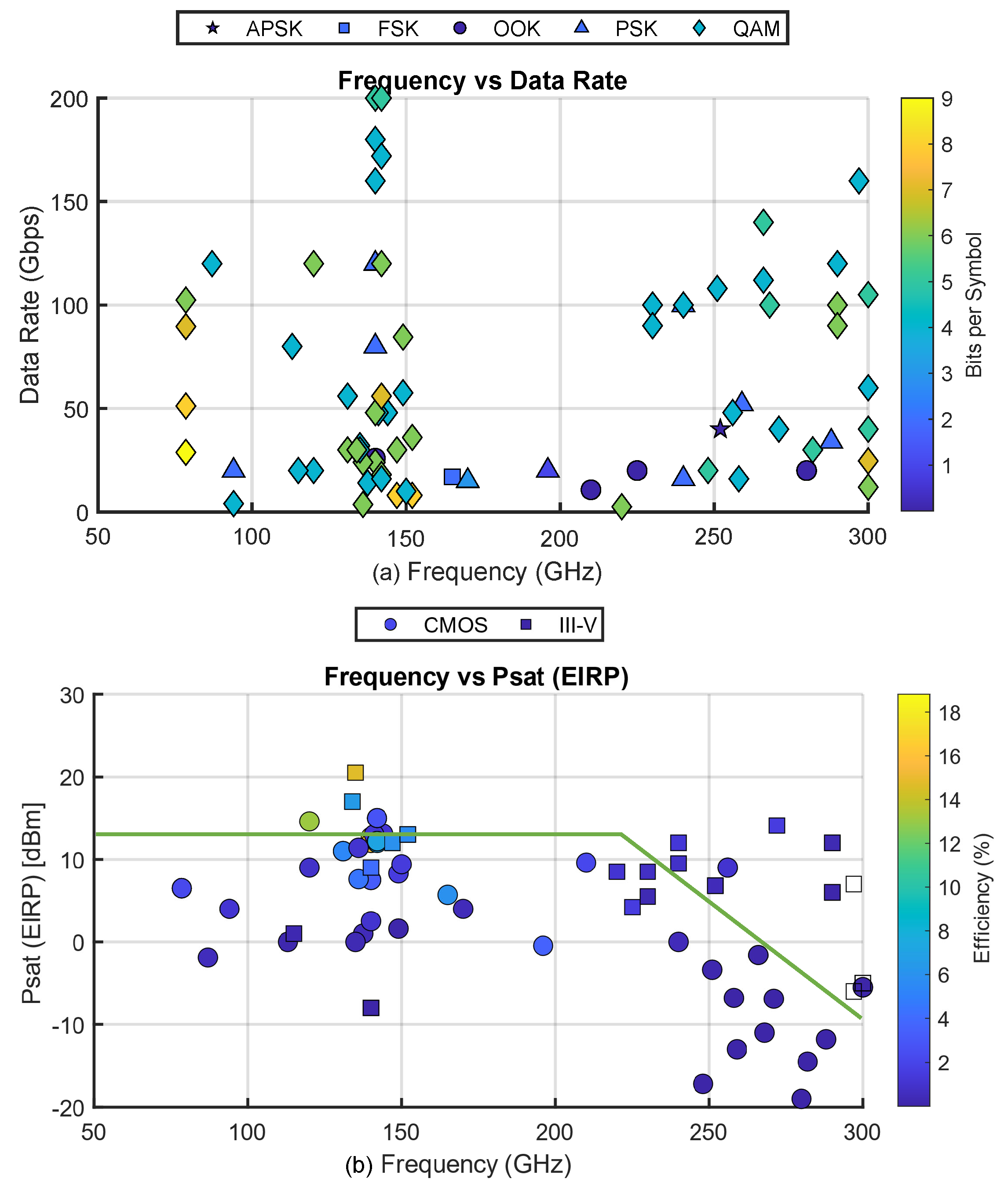

2. Transmitter System and Component Design Considerations

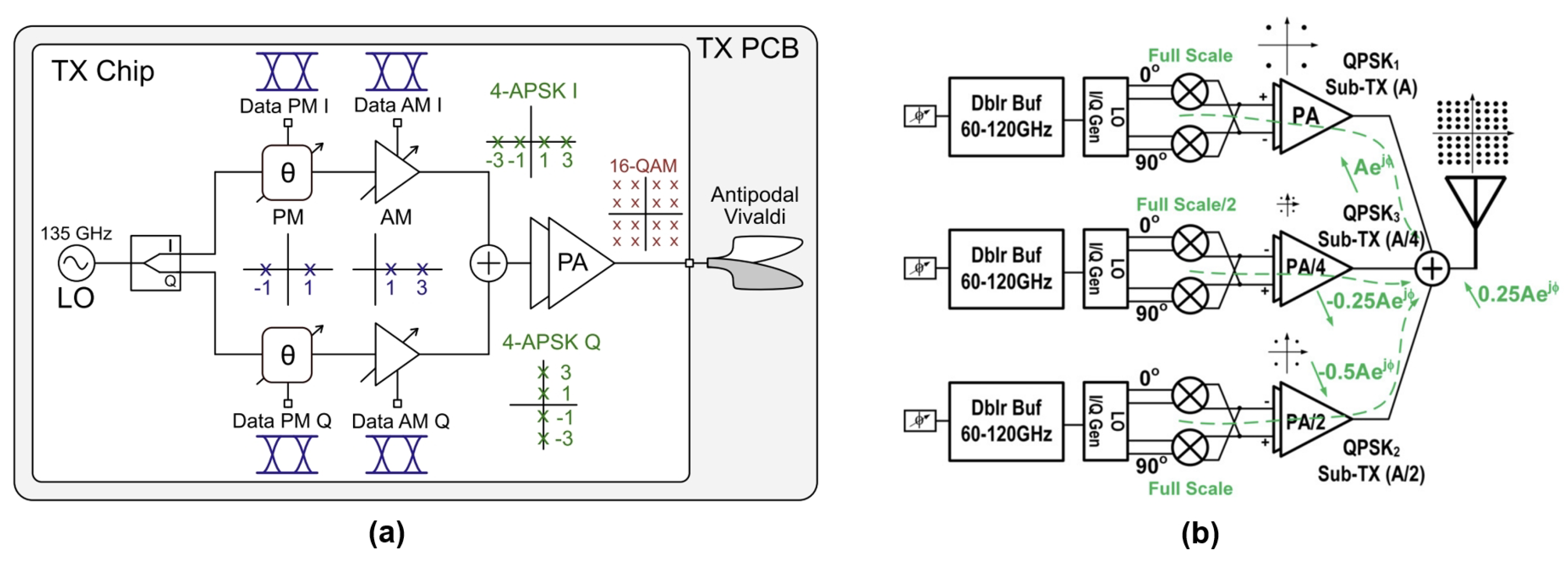

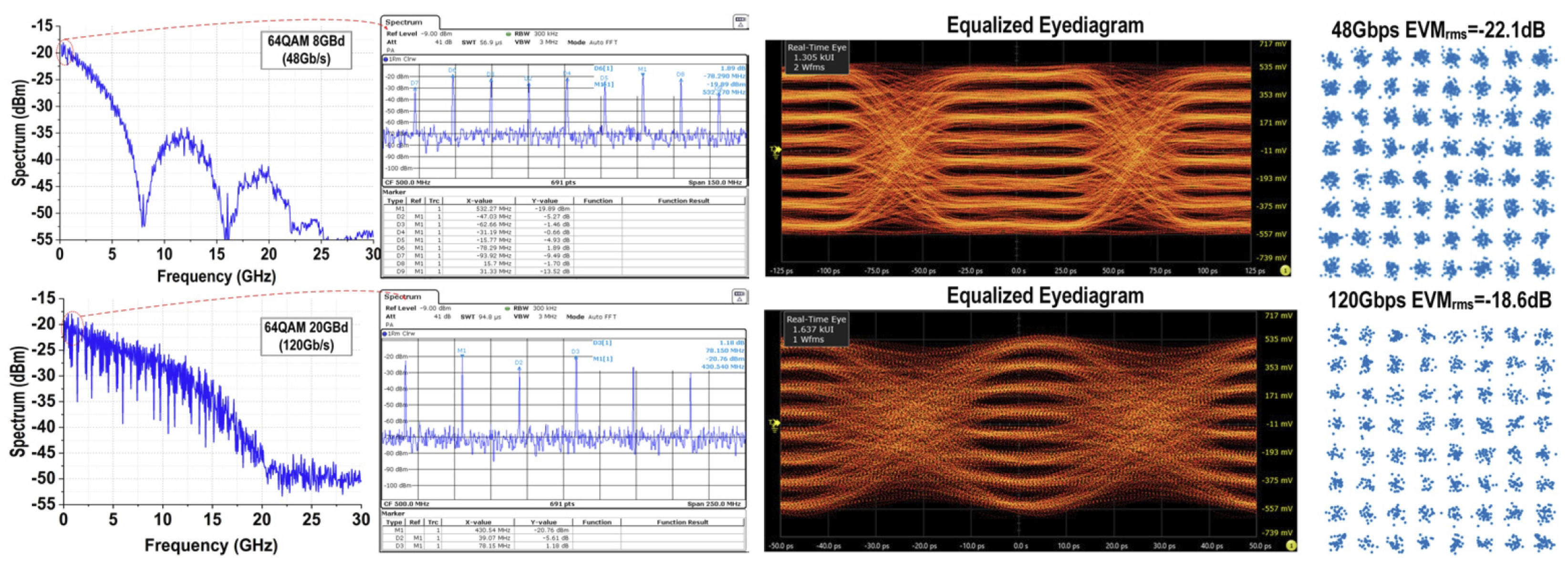

2.1. Heterodyne, Direct-Conversion, and Direct-Digital Modulation Transmitter

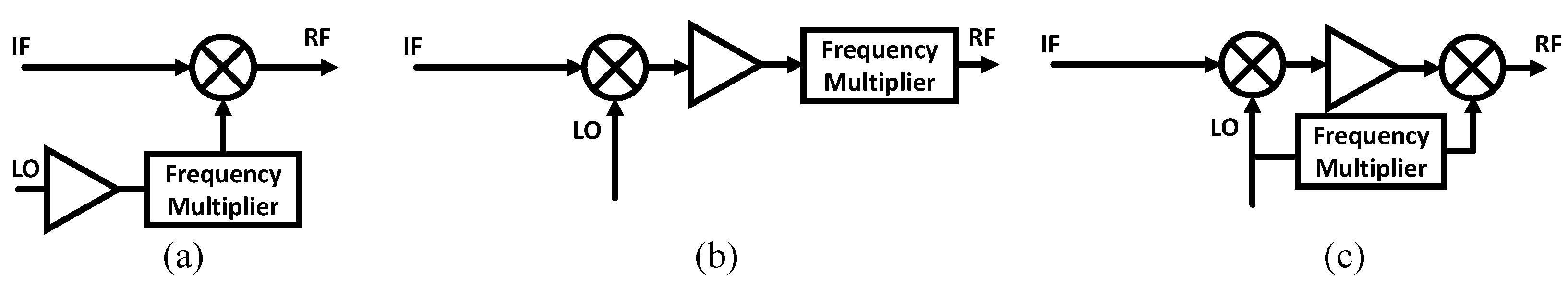

2.2. Signal Generation: VCO vs. Frequency Multiplier

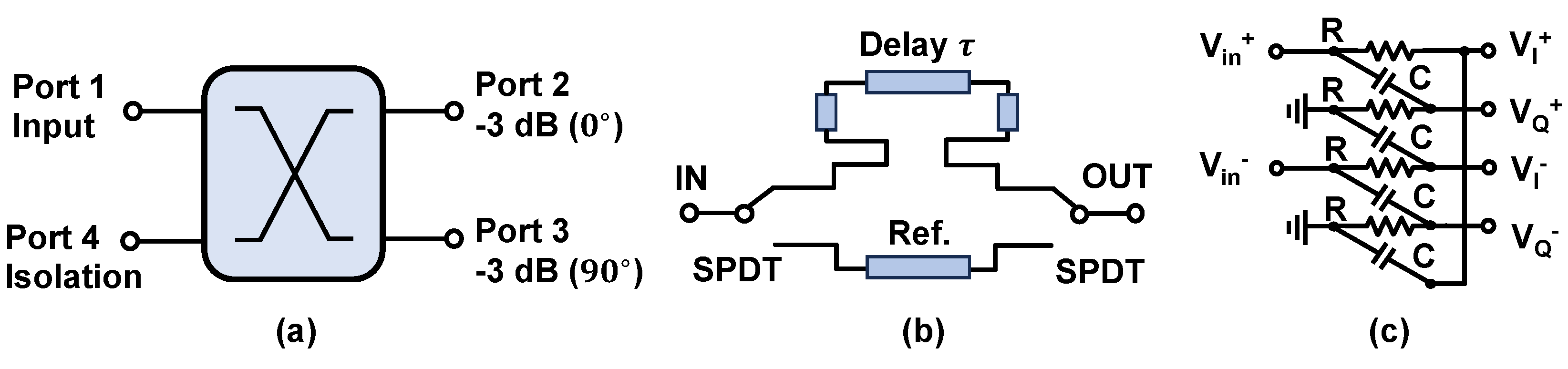

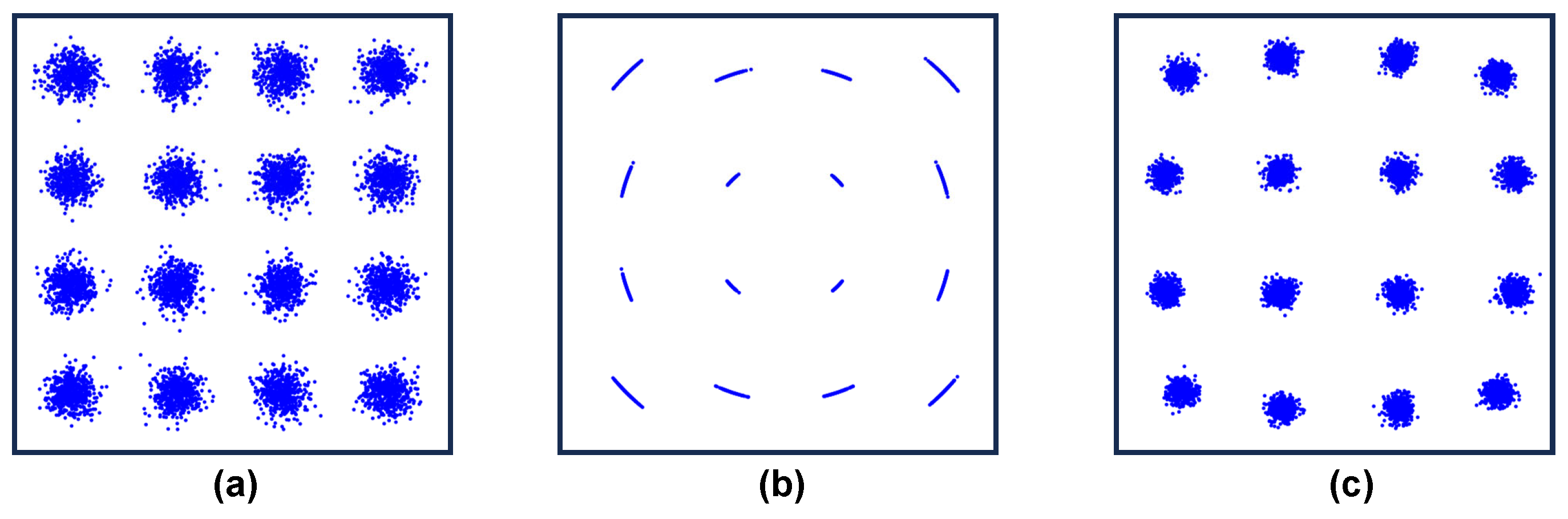

2.3. Phase Shifter

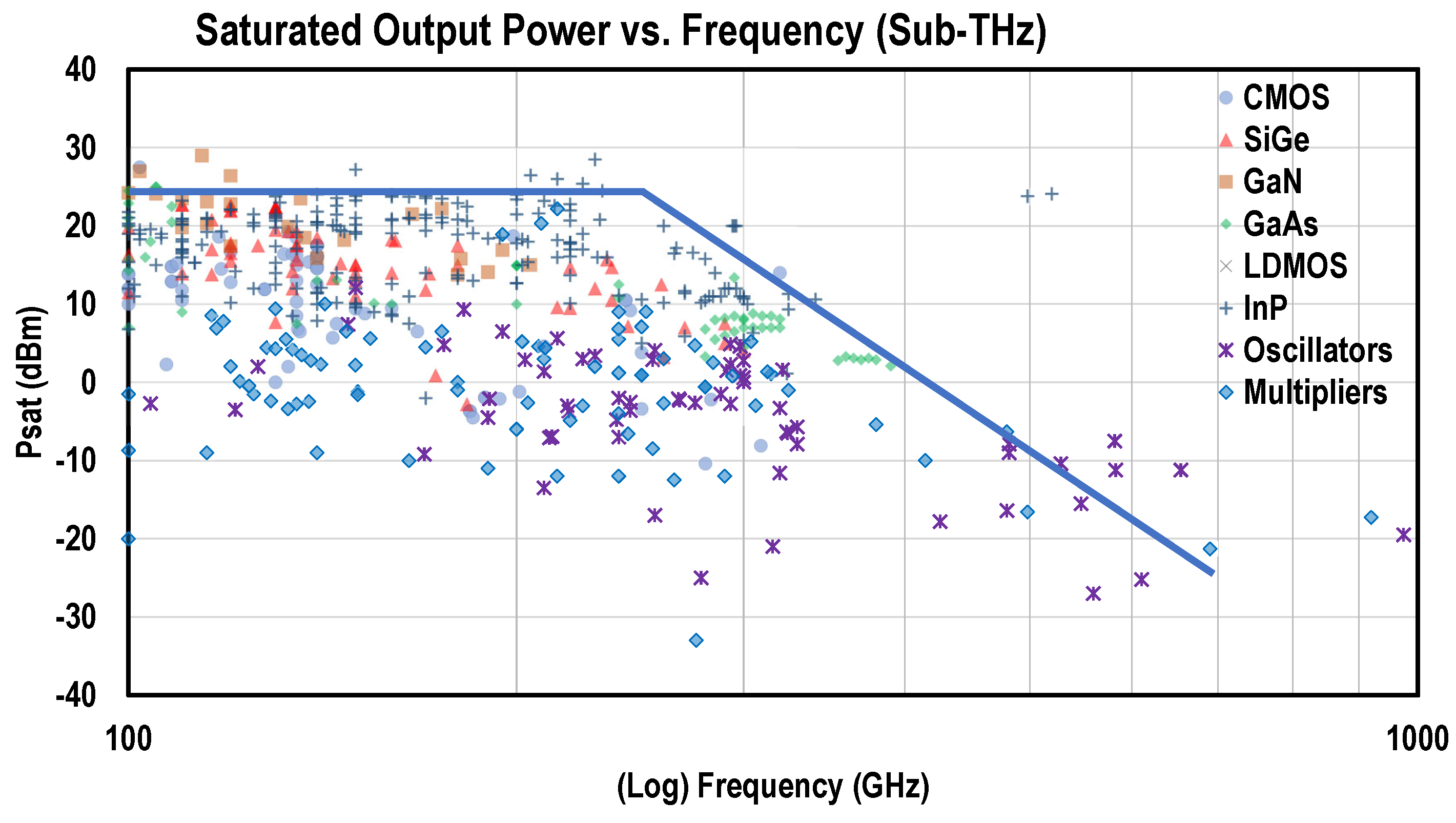

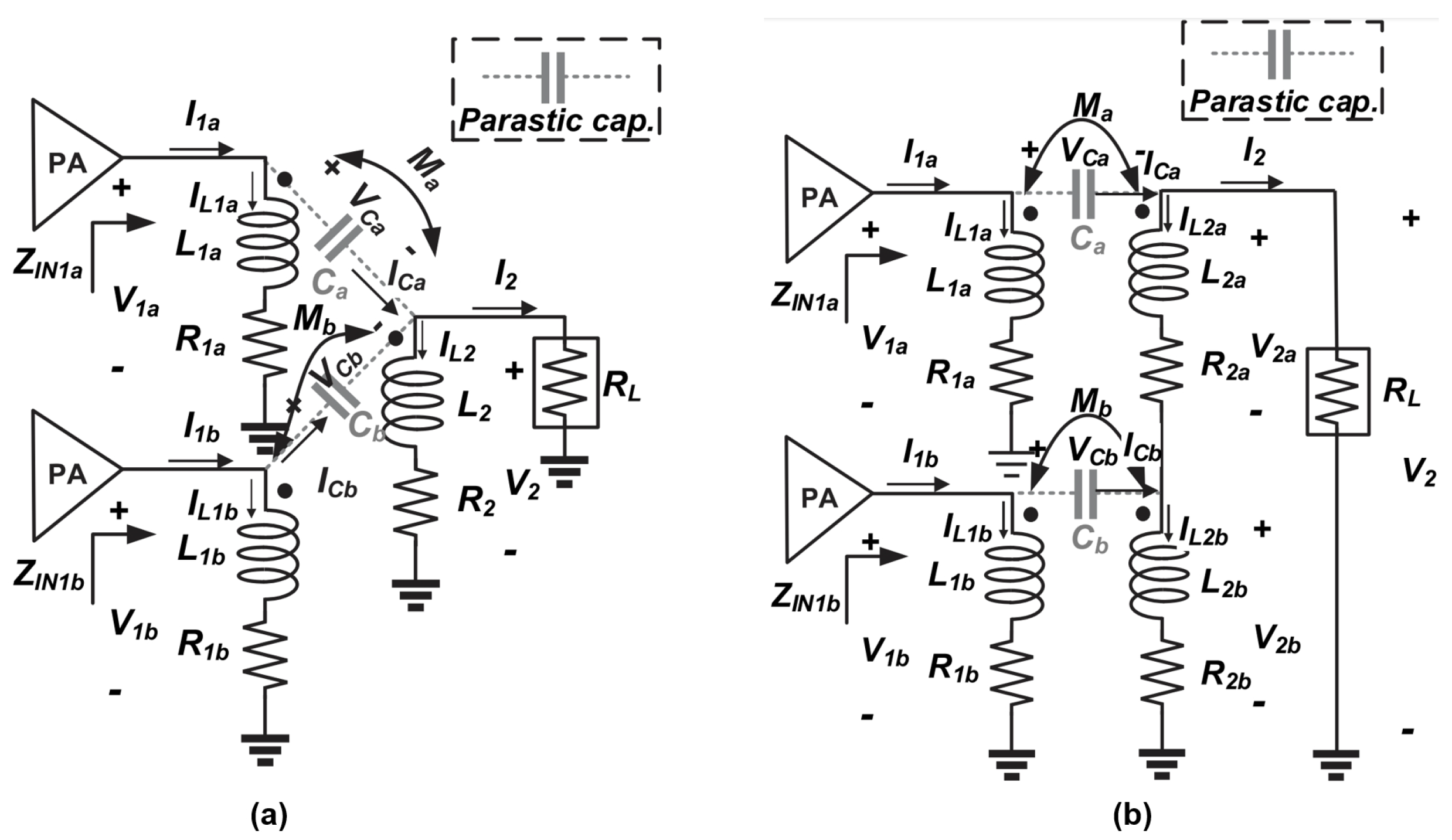

2.4. Power Amplifier

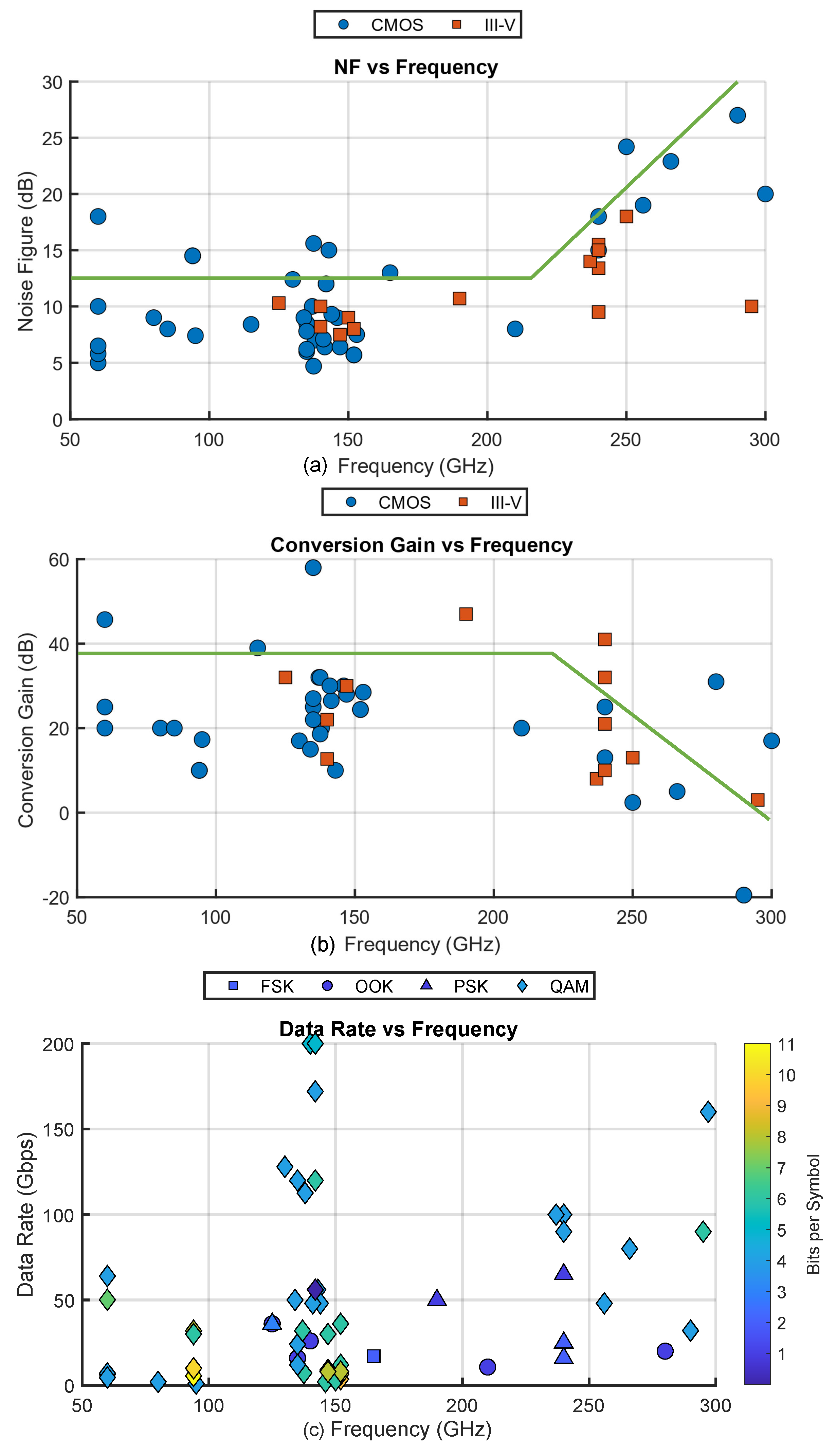

3. Receiver Design Considerations and Challenges

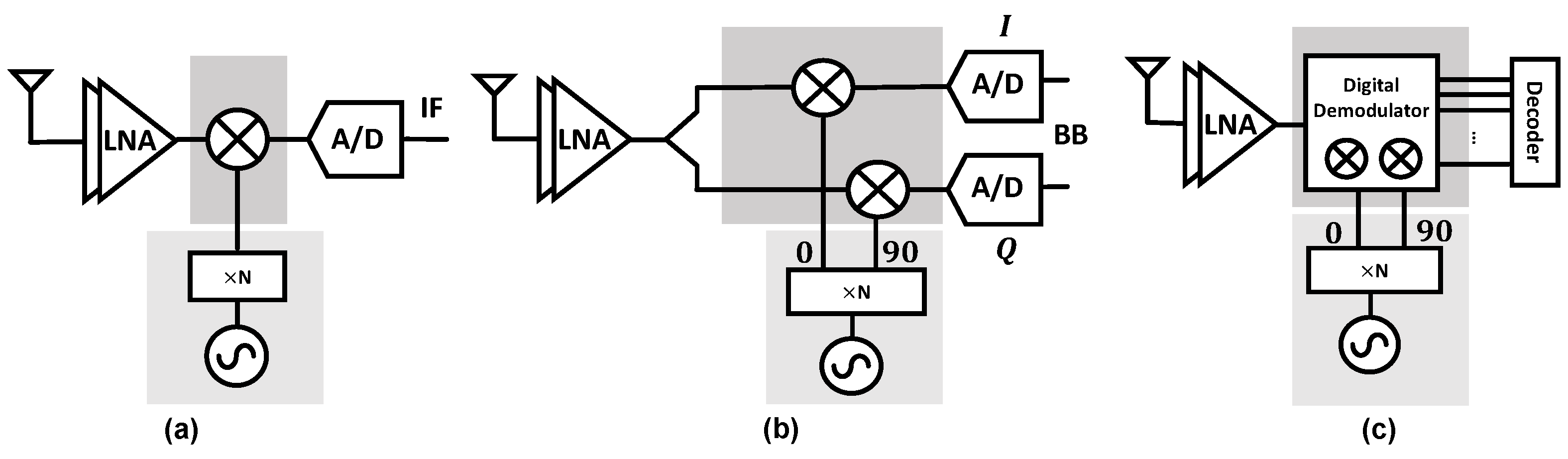

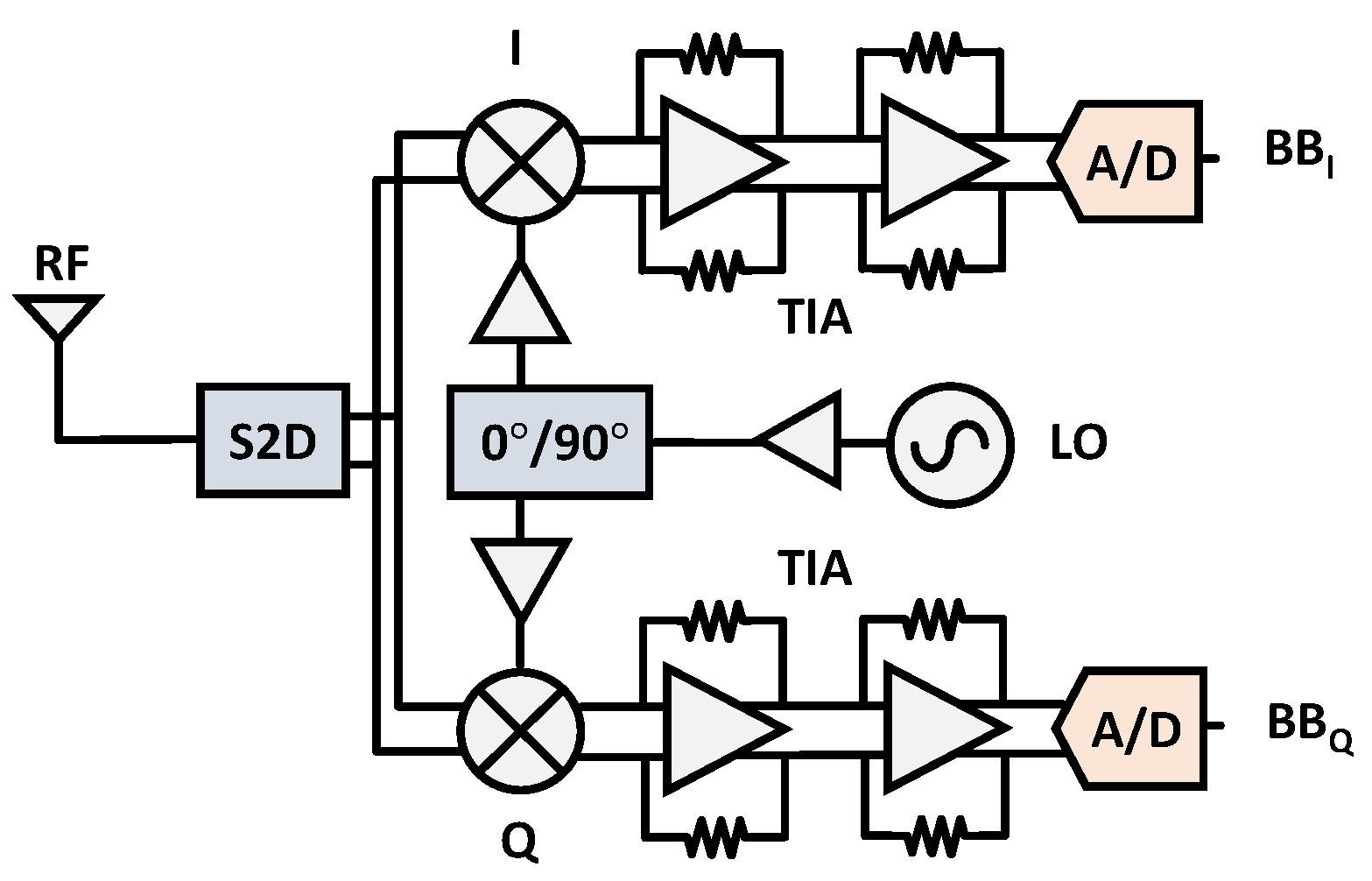

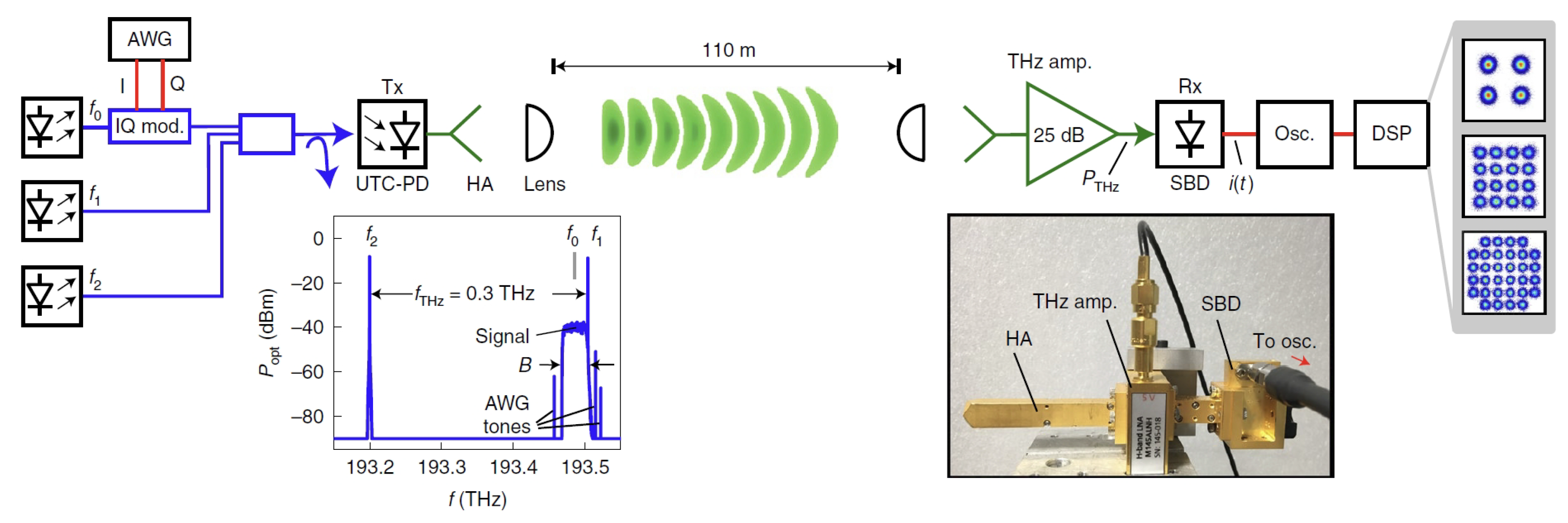

3.1. Heterodyne and Homodyne Receiver

3.2. LNA-First Versus Mixer-First Architectures

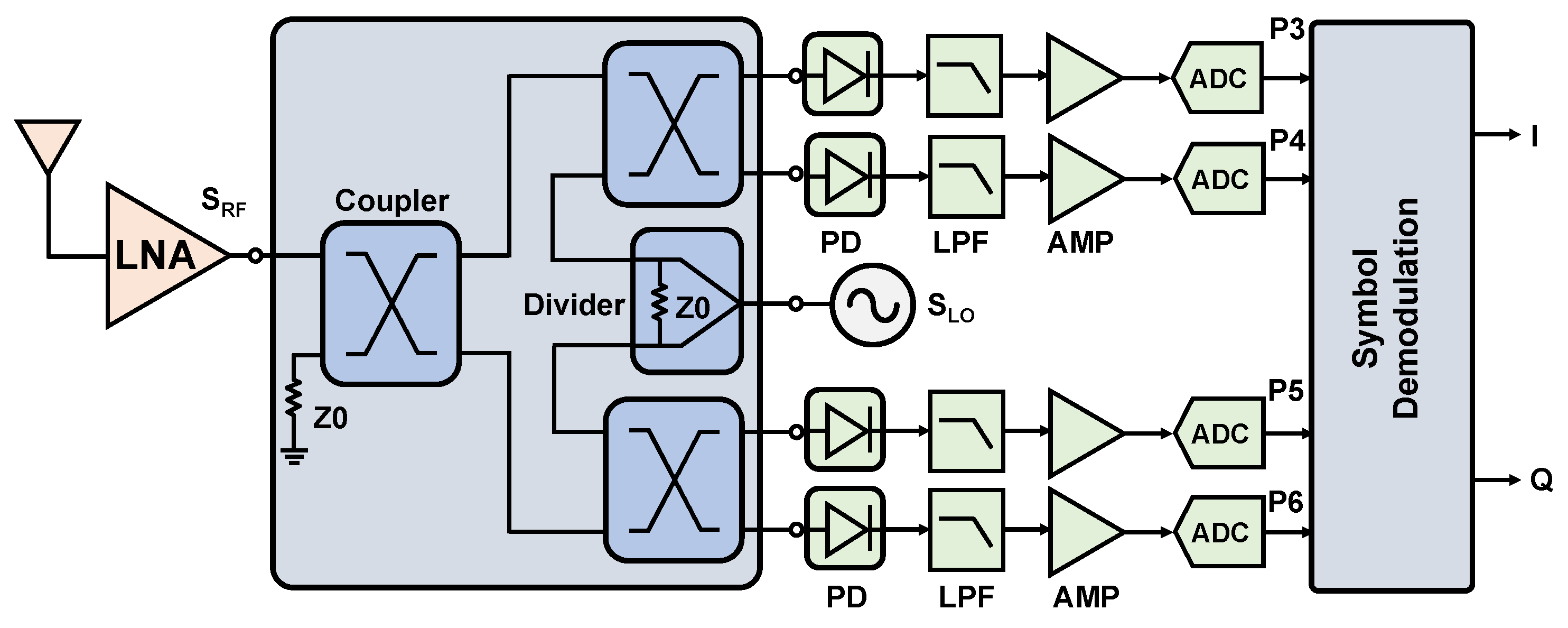

3.3. Direct-Demodulation Receiver

4. Transceiver System Design

4.1. System Considerations: Full Duplex with Single/Double Antenna, SIC, and LO Feedthrough

4.2. Phased-Array System and Beam-Forming

4.3. MIMO Systems

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| Acronym | Full Term |

| ADC | Analog-to-Digital Converter |

| AM/AM | Amplitude Modulation to Amplitude Modulation Distortion |

| AM/PM | Amplitude Modulation to Phase Modulation Distortion |

| APSK | Amplitude Phase Shift Keying |

| BER | Bit Error Rate |

| BB | Baseband |

| CMOS | Complementary Metal-Oxide-Semiconductor |

| DAC | Digital-to-Analog Converter |

| DDMT | Direct-Digital Modulation Transmitter |

| DPD | Digital Pre-Distortion |

| DSP | Digital Signal Processing |

| EIRP | Effective Isotropic Radiated Power |

| EVM | Error Vector Magnitude |

| FET | Field-Effect Transistor |

| FSK | Frequency Shift Keying |

| HBT | Heterojunction Bipolar Transistor |

| IF | Intermediate Frequency |

| IP1dB | 1-dB Compression Point |

| LNA | Low Noise Amplifier |

| LO | Local Oscillator |

| MIMO | Multiple-Input Multiple-Output |

| NF | Noise Figure |

| OOK | On-Off Keying |

| PA | Power Amplifier |

| PPF | Poly-Phase Filter |

| PS | Phase Shifter |

| QAM | Quadrature Amplitude Modulation |

| QPSK | Quadrature Phase Shift Keying |

| RF | Radio Frequency |

| RX | Receiver |

| SIC | Self-Interference Cancellation |

| SNR | Signal-to-Noise Ratio |

| SPDT | Single-Pole Double-Throw |

| THz | Terahertz |

| TRX | Transceiver |

| TX | Transmitter |

| VCO | Voltage-Controlled Oscillator |

| VNA | Vector Network Analyzer |

References

- Rappaport, T.S.; Xing, Y.; Kanhere, O.; Ju, S.; Madanayake, A.; Mandal, S.; Alkhateeb, A.; Trichopoulos, G.C. Wireless Communications and Applications Above 100 GHz: Opportunities and Challenges for 6G and Beyond. IEEE Access 2019, 7, 78729–78757. [Google Scholar] [CrossRef]

- Zubair, M.; Jabbar, A.; Tahir, F.; Kazim, J.U.R.; Ur Rehman, M.; Imran, M.; Liu, B.; Abbasi, Q. A high-performance sub-THz planar antenna array for THz sensing and imaging applications. Sci. Rep. 2024, 14, 17030. [Google Scholar] [CrossRef] [PubMed]

- Rodwell, M.; Fang, Y.; Rode, J.; Wu, J.; Markman, B.; Brunelli, S.Š.; Klamkin, J.; Urteaga, M. 100–340ghz systems: Transistors and applications. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 14.3.1–14.3.4. [Google Scholar]

- Song, H.J.; Lee, N. Terahertz Communications: Challenges in the Next Decade. IEEE Trans. Terahertz Sci. Technol. 2022, 12, 105–117. [Google Scholar] [CrossRef]

- Yan, B.; Chen, R.; Chen, C.; Chang, M.C.F. A 180-GHz High-Sensitivity Dielectric Resonator Antenna-Coupled Detector in 16nm FinFET. In Proceedings of the 2024 IEEE/MTT-S International Microwave Symposium—IMS 2024, Washington DC, USA, 16–21 June 2024; pp. 1065–1068. [Google Scholar] [CrossRef]

- Kürner, T.; Priebe, S. Towards THz Communications—Status in Research, Standardization and Regulation. J. Infrared Millim. Terahertz Waves 2014, 35, 53–62. [Google Scholar] [CrossRef]

- Jiang, W.; Zhou, Q.; He, J.; Habibi, M.A.; Melnyk, S.; El-Absi, M.; Han, B.; Renzo, M.D.; Schotten, H.D.; Luo, F.L.; et al. Terahertz Communications and Sensing for 6G and Beyond: A Comprehensive Review. IEEE Commun. Surv. Tutor. 2024, 26, 2326–2381. [Google Scholar] [CrossRef]

- Maiwald, T.; Li, T.; Hotopan, G.R.; Kolb, K.; Disch, K.; Potschka, J.; Haag, A.; Dietz, M.; Debaillie, B.; Zwick, T.; et al. A Review of Integrated Systems and Components for 6G Wireless Communication in the D-Band. Proc. IEEE 2023, 111, 220–256. [Google Scholar] [CrossRef]

- Cherry, S. Edholm’s law of bandwidth. IEEE Spectr. 2004, 41, 58–60. [Google Scholar] [CrossRef]

- Rappaport, T.S.; Xing, Y.; MacCartney, G.R.; Molisch, A.F.; Mellios, E.; Zhang, J. Overview of Millimeter Wave Communications for Fifth-Generation (5G) Wireless Networks—With a Focus on Propagation Models. IEEE Trans. Antennas Propag. 2017, 65, 6213–6230. [Google Scholar] [CrossRef]

- Lee, C.J.; Kim, S.H.; Son, H.S.; Kang, D.M.; Kim, J.H.; Byeon, C.W.; Park, C.S. A 120 GHz I/Q transmitter front-end in a 40 nm CMOS for wireless chip to chip communication. In Proceedings of the 2018 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Philadelphia, PA, USA, 10–12 June 2018; pp. 192–195. [Google Scholar]

- Farid, A.A.; Simsek, A.; Ahmed, A.S.; Rodwell, M.J. A broadband direct conversion transmitter/receiver at D-band using CMOS 22nm FDSOI. In Proceedings of the 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2–4 June 2019; pp. 135–138. [Google Scholar]

- Zhang, Y.; Vaesen, K.; Mangraviti, G.; Park, S.; Zong, Z.; Wambacq, P.; Gramegna, G. A 56Gb/s Zero-IF D-Band Transmitter for a Beamformer in 22nm FD-SOI. In Proceedings of the 2024 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Washington DC, USA, 16–18 June 2024; pp. 347–350. [Google Scholar]

- Callender, S.; Whitcombe, A.; Agrawal, A.; Bhat, R.; Rahman, M.; Lee, C.C.; Sagazio, P.; Dogiamis, G.; Carlton, B.; Chakravorti, M.; et al. A fully integrated 160Gb/s D-band transmitter with 1.1 pJ/b efficiency in 22nm FinFET technology. In Proceedings of the 2022 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022; Volume 65, pp. 78–80. [Google Scholar]

- D’heer, C.; Reynaert, P. A fully integrated 135-GHz direct-digital 16-QAM wireless and dielectric waveguide link in 28-nm CMOS. IEEE J. Solid-State Circuits 2023, 59, 889–907. [Google Scholar] [CrossRef]

- Wang, H.; Mohammadnezhad, H.; Heydari, P. Analysis and design of high-order QAM direct-modulation transmitter for high-speed point-to-point mm-wave wireless links. IEEE J. Solid-State Circuits 2019, 54, 3161–3179. [Google Scholar] [CrossRef]

- Oveisi, M.; Wang, H.; Heydari, P. A study of a millimeter-wave transmitter architecture realizing QAM directly in RF domain. IEEE Trans. Circuits Syst. I Regul. Pap. 2023, 70, 2243–2256. [Google Scholar] [CrossRef]

- Philippe, B.; Reynaert, P. 24.7 A 15dBm 12.8Power Combining in 16nm FinFET CMOS. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 374–376. [Google Scholar] [CrossRef]

- Mohamed, E.; Fischer, G.; Mausolf, T.; Rücker, H.; Malignaggi, A.; Kahmen, G. 220–320-GHz J-Band 4-Way Power Amplifier in Advanced 130-nm BiCMOS Technology. IEEE Microw. Wirel. Compon. Lett. 2022, 32, 1335–1338. [Google Scholar] [CrossRef]

- Abdo, I.; da Gomez, C.; Wang, C.; Hatano, K.; Li, Q.; Liu, C.; Yanagisawa, K.; Fadila, A.A.; Fujimura, T.; Miura, T.; et al. A Bi-Directional 300-GHz-Band Phased-Array Transceiver in 65-nm CMOS with Outphasing Transmitting Mode and LO Emission Cancellation. IEEE J. Solid-State Circuits 2022, 57, 2292–2308. [Google Scholar] [CrossRef]

- Chien, J.S.C.; Buckwalter, J.F. A 110–120-GHz, 12.2/ Efficiency, 16.2-dBm Output Power Multiplying Outphasing Transmitter in 22-nm FDSOI. In Proceedings of the 2022 IEEE Asian Solid-State Circuits Conference (A-SSCC), Taipei, Taiwan, 6–9 November 2022; pp. 1–3. [Google Scholar] [CrossRef]

- Abdo, I.; Gomez, C.d.; Wang, C.; Hatano, K.; Li, Q.; Liu, C.; Yanagisawa, K.; Fadila, A.A.; Pang, J.; Hamada, H.; et al. 22.2 A 300GHz-Band Phased-Array Transceiver Using Bi-Directional Outphasing and Hartley Architecture in 65nm CMOS. In Proceedings of the 2021 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; Volume 64, pp. 316–318. [Google Scholar] [CrossRef]

- Afifi, A.; Ahmed, A.; Rebeiz, G.M. A 2x40 Gb/s Ultra-Wideband 131–173 GHz Dual Receiver for Point-to-Point Communication Systems with NF of 5.7 dB in RFSOI. In Proceedings of the 2024 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Washington DC, USA, 16–18 June 2024; pp. 279–282. [Google Scholar] [CrossRef]

- Wang, C.; Rebeiz, G. A 2-channel 136–156 GHz dual down-conversion I/Q receiver with 30 dB gain and 9.5 dB NF using CMOS 22nm FDSOI. In Proceedings of the 2021 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Atlanta, GA, USA, 7–9 June 2021; pp. 219–222. [Google Scholar]

- Chien, H.Y.; Chen, C.; Chen, R.; Woo, J.; Pamarti, S.; Chang, M.C.F.; Yang, C.K.K. A Low Power 185 GHz Static CML Frequency Divider in SiGe HBTs Using Band-switching Technique in 45nm PDSOI BiCMOS. In Proceedings of the 2024 IEEE/MTT-S International Microwave Symposium—IMS 2024, Washington DC, USA, 16–21 June 2024; pp. 174–177. [Google Scholar] [CrossRef]

- Preez, J.D.; Sinha, S.; Sengupta, K. SiGe and CMOS Technology for State-of-the-Art Millimeter-Wave Transceivers. IEEE Access 2023, 11, 55596–55617. [Google Scholar] [CrossRef]

- Chou, E.; Baniasadi, N.; Niknejad, A. A 200 GHz Wideband and Compact Differential LNA Leveraging an Active Balun Input Stage in 16nm FinFET Technology. In Proceedings of the 2024 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Washington DC, USA, 16–18 June 2024; pp. 375–378. [Google Scholar] [CrossRef]

- Chen, R.; Mani, H.; Marsh, P.; Al Hadi, R.; Shrestha, P.; Campbell, J.; Chen, C.; Chien, H.Y.; Galatsis, K.; Frank Chang, M.C. A 4-mW 2.2–6.9 GHz LNA in 16 nm FinFET Technology for Cryogenic Applications. IEEE Microw. Wirel. Technol. Lett. 2024, 34, 1351–1354. [Google Scholar] [CrossRef]

- Chen, R.; Mani, H.; Marsh, P.; Al Hadi, R.; Shrestha, P.; Campbell, J.; Chen, C.; Chien, H.Y.; Chang, M.C.F. A 0.16–3.7GHz Ultra-Compact Noise-Canceling Cryogenic Low-Noise Amplifier at 4 K using 16nm FinFET Technology for Qubit Readout. In Proceedings of the 2024 Device Research Conference (DRC), Washington DC, USA, 24–26 June 2024; pp. 1–2. [Google Scholar] [CrossRef]

- Karakuzulu, A.; Ahmad, W.A.; Kissinger, D.; Malignaggi, A. A Four-Channel Bidirectional D-Band Phased-Array Transceiver for 200 Gb/s 6G Wireless Communications in a 130-nm BiCMOS Technology. IEEE J. Solid-State Circuits 2023, 58, 1310–1322. [Google Scholar] [CrossRef]

- Liu, C.; Li, Z.; Yamazaki, Y.; Herdian, H.; Wang, C.; Tian, A.; Sakamaki, J.; Nie, H.; Fu, X.; Kato, S.; et al. A 640-Gb/s 4 × 4-MIMO D-Band CMOS Transceiver Chipset. IEEE J. Solid-State Circuits 2024, 1–18. [Google Scholar] [CrossRef]

- Hamada, H.; Abdo, I.; Tsutsumi, T.; Takahashi, H. 300-GHz 160-Gb/s InP-HEMT Wireless Front-End with Fully Differential Architecture. In Proceedings of the 2024 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), Fort Lauderdale, FL, USA, 27–30 October 2024; pp. 162–165. [Google Scholar] [CrossRef]

- Neofytou, M.; Doris, K.; Ganzerli, M.; Lont, M.; Radulov, G.I. 32.6 A 76-to-81GHz Direct-Digital 7b 14GS/s Double-Balanced I/Q Mixing-DAC Radar-Waveform Synthesizer. In Proceedings of the 2024 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 18–24 February 2024; Volume 67, pp. 530–532. [Google Scholar] [CrossRef]

- Elkhouly, M.; Ha, J.; Holyoak, M.J.; Hendry, D.; Sayginer, M.; Enright, R.; Kimionis, I.; Baeyens, Y.; Shahramian, S. Fully Integrated 2D Scalable TX/RX Chipset for D-Band Phased-Array-on-Glass Modules. In Proceedings of the 2022 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–24 February 2022; Volume 65, pp. 76–78. [Google Scholar] [CrossRef]

- Singh, A.; Sayginer, M.; Holyoak, M.J.; Weiner, J.; Kimionis, J.; Elkhouly, M.; Baeyens, Y.; Shahramian, S. A D-band radio-on-glass module for spectrally-efficient and low-cost wireless backhaul. In Proceedings of the 2020 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Los Angeles, CA, USA, 4–6 August 2020; pp. 99–102. [Google Scholar]

- Takano, K.; Amakawa, S.; Katayama, K.; Hara, S.; Dong, R.; Kasamatsu, A.; Hosako, I.; Mizuno, K.; Takahashi, K.; Yoshida, T.; et al. 17.9 A 105Gb/s 300GHz CMOS transmitter. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 308–309. [Google Scholar]

- Peng, Q.; Jia, H.; Fang, R.; Guan, P.; Deng, M.; Xue, J.; Deng, W.; Liang, X.; Chi, B. A 26-Gb/s 140-GHz OOK CMOS transmitter and receiver chipset for high-speed proximity wireless communication. In Proceedings of the 2023 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), San Diego, CA, USA, 11–13 June 2023; pp. 145–148. [Google Scholar]

- Zhang, R.; Tang, D.; Chen, Z.; Lu, L.; Tang, S.Y.; Zhou, P.; Chen, J.; Hong, W. A D-Band OOK Transmitter with 50-GHz Bandwidth Achieving 32-Gbps Data Rate in 28-nm CMOS. IEEE J. Solid-State Circuits 2024, 59, 2347–2361. [Google Scholar] [CrossRef]

- Kang, S.; Thyagarajan, S.V.; Niknejad, A.M. A 240 GHz fully integrated wideband QPSK transmitter in 65 nm CMOS. IEEE J. Solid-State Circuits 2015, 50, 2256–2267. [Google Scholar] [CrossRef]

- Nazari, P.; Jafarlou, S.; Heydari, P. A CMOS Two-Element 170-GHz Fundamental-Frequency Transmitter with Direct RF-8PSK Modulation. IEEE J. Solid-State Circuits 2020, 55, 282–297. [Google Scholar] [CrossRef]

- Guo, H.; Ghosh, S.; Zhang, F.; Lee, S.; Choi, W.; Dong, S.; Kenneth, O. 10-GSymbols/s Supply Modulated 250-GHz SiGe HBT Transmitter RF Front-End with 6.8-dBm Peak Modulated Power. In Proceedings of the 2024 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), Fort Lauderdale, FL, USA, 27–30 October 2024; pp. 181–184. [Google Scholar] [CrossRef]

- Afzal, H.; Li, C.; Momeni, O. A highly efficient 165-GHz 4FSK 17-Gb/s transceiver system with frequency overlapping architecture in 65-nm CMOS. IEEE J. Solid-State Circuits 2023, 58, 3113–3126. [Google Scholar] [CrossRef]

- Hamani, A.; Foglia-Manzillo, F.; Siligaris, A.; Cassiau, N.; Blampey, B.; Hameau, F.; Dehos, C.; Clemente, A.; Gonzalez-Jimenez, J.L. An 84.48 Gb/s CMOS D-band multi-channel TX system-in-package. In Proceedings of the 2021 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Atlanta, GA, USA, 7–9 June 2021; pp. 207–210. [Google Scholar]

- Gonzalez-Jimenez, J.L.; Siligaris, A.; Hamani, A.; Foglia-Manzillo, F.; Courouve, P.; Cassiau, N.; Dehos, C.; Clemente, A. A 57.6 Gb/s wireless link based on 26.4 dBm EIRP D-band transmitter module and a channel bonding chipset on CMOS 45nm. In Proceedings of the 2023 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), San Diego, CA, USA, 11–13 June 2023; pp. 97–100. [Google Scholar]

- Hamani, A.; Gonzalez-Jimenez, J.L.; Siligaris, A.; Foglia-Manzillo, F.; Dehos, C.; David, J.B.; Cassiau, N.; Clemente, A. A 112.64-Gb/s CMOS D-band Channel-Aggregation RX System-in-Package. In Proceedings of the 2024 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Washington DC, USA, 16–18 June 2024; pp. 283–286. [Google Scholar]

- Abdo, I.; Fujimura, T.; Miura, T.; Tokgoz, K.K.; Hamada, H.; Nosaka, H.; Shirane, A.; Okada, K. A 300GHz Wireless Transceiver in 65nm CMOS for IEEE802.15.3d Using Push-Push Subharmonic Mixer. In Proceedings of the 2020 IEEE/MTT-S International Microwave Symposium (IMS), Los Angeles, CA, USA, 4–6 August 2020; pp. 623–626. [Google Scholar] [CrossRef]

- Ahmed, A.; Li, L.; Jung, M.; Li, S.; Baltimas, D.; Rebeiz, G.M. 140-GHz 2-D Scalable On-Grid 8 × 8-Element Transmit–Receive Phased Arrays with Up/Down Converters Demonstrating a 5.2-m Link at 16 Gbps. IEEE Trans. Microw. Theory Tech. 2024, 72. [Google Scholar] [CrossRef]

- Farid, A.A.; Ahmed, A.S.; Rodwell, M.J. A 27.5 dBm EIRP D-band transmitter module on a ceramic interposer. In Proceedings of the 2021 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Atlanta, GA, USA, 7–9 June 2021; pp. 43–46. [Google Scholar]

- Li, S.; Zhang, Z.; Rebeiz, G.M. An Eight-Element 136–147 GHz Wafer-Scale Phased-Array Transmitter with 32 dBm Peak EIRP and >16 Gbps 16QAM and 64QAM Operation. IEEE J. Solid-State Circuits 2022, 57, 1635–1648. [Google Scholar] [CrossRef]

- Carpenter, S.; Nopchinda, D.; Abbasi, M.; He, Z.S.; Bao, M.; Eriksson, T.; Zirath, H. A D-band 48-Gbit/s 64-QAM/QPSK direct-conversion I/Q transceiver chipset. IEEE Trans. Microw. Theory Tech. 2016, 64, 1285–1296. [Google Scholar] [CrossRef]

- Wei, M.; Baniasadi, N.; Chou, E.; Beshary, H.; Krishnamurthy, S.; Alon, E.; Niknejad, A. A D-Band Packaged CMOS Integrated Transmitter for MU-MIMO Applications. In Proceedings of the 2022 IEEE Asian Solid-State Circuits Conference (A-SSCC), Taipei, Taiwan, 6–9 November 2022; pp. 6–8. [Google Scholar]

- Eissa, M.H.; Maletic, N.; Grass, E.; Krämer, R.; Kissinger, D.; Malignaggi, A. 100 Gbps 0.8-m wireless link based on fully integrated 240 GHz IQ transmitter and receiver. In Proceedings of the 2020 IEEE/MTT-S International Microwave Symposium (IMS), Los Angeles, CA, USA, 4–6 August 2020; pp. 627–630. [Google Scholar]

- Kim, S.H.; Jang, T.H.; Kang, D.M.; Jung, K.P.; Park, C.S. Wideband 120-GHz CMOS I/Q Transmitter with Suppressed IMRR and LOFT for Wireless Short-Range High-Speed 6G IoT Applications. IEEE Internet Things J. 2023, 10, 11739–11748. [Google Scholar] [CrossRef]

- Rodríguez-Vázquez, P.; Grzyb, J.; Sarmah, N.; Heinemann, B.; Pfeiffer, U.R. Towards 100 Gbps: A Fully Electronic 90 Gbps One Meter Wireless Link at 230 GHz. In Proceedings of the 2018 48th European Microwave Conference (EuMC), Madrid, Spain, 23–27 September 2018; pp. 1389–1392. [Google Scholar] [CrossRef]

- Shopov, S.; Gurbuz, O.D.; Rebeiz, G.M.; Voinigescu, S.P. A D-Band Digital Transmitter with 64-QAM and OFDM Free-Space Constellation Formation. IEEE J. Solid-State Circuits 2018, 53, 2012–2022. [Google Scholar] [CrossRef]

- Townley, A.; Baniasadi, N.; Krishnamurthy, S.; Sideris, C.; Hajimiri, A.; Alon, E.; Niknejad, A. A fully integrated, dual channel, flip chip packaged 113 GHz transceiver in 28nm CMOS supporting an 80 Gb/s wireless link. In Proceedings of the 2020 IEEE Custom Integrated Circuits Conference (CICC), Boston, MA, USA, 22–25 March 2020; pp. 1–4. [Google Scholar]

- Al-Rubaye, H.; Rebeiz, G.M. A 20 Gbit/s RFDAC-Based Direct-Modulation W-Band Transmitter in 32nm SOI CMOS. In Proceedings of the 2016 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), Austin, TX, USA, 23–26 October 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Al-Rubaye, H.; Rebeiz, G.M. W-Band Direct-Modulation >20-Gb/s Transmit and Receive Building Blocks in 32-nm SOI CMOS. IEEE J. Solid-State Circuits 2017, 52, 2277–2291. [Google Scholar] [CrossRef]

- D’heer, C.; Reynaert, P. A 135 GHz 32 Gb/s Direct-Digital Modulation 16-QAM Transmitter in 28 nm CMOS. In Proceedings of the ESSCIRC 2022—IEEE 48th European Solid State Circuits Conference (ESSCIRC), Milan, Italy, 19–22 September 2022; pp. 481–484. [Google Scholar] [CrossRef]

- Wang, Z.; Wang, H.; Hassan, Y.O.; Heydari, P. A CMOS Fully Integrated 120-Gbps RF-64QAM F-band Transmitter with an On-Chip Antenna for 6G Wireless Communication. In Proceedings of the 2024 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Washington DC, USA, 16–18 June 2024; pp. 343–346. [Google Scholar]

- Standaert, A.; Reynaert, P. A 390-GHz outphasing transmitter in 28-nm CMOS. IEEE J. Solid-State Circuits 2020, 55, 2703–2713. [Google Scholar] [CrossRef]

- Katayama, K.; Takano, K.; Amakawa, S.; Hara, S.; Kasamatsu, A.; Mizuno, K.; Takahashi, K.; Yoshida, T.; Fujishima, M. A 300 GHz CMOS Transmitter with 32-QAM 17.5 Gb/s/ch Capability over Six Channels. IEEE J. Solid-State Circuits 2016, 51, 3037–3048. [Google Scholar] [CrossRef]

- Lee, S.; Kim, J.; Lee, K.; Song, H.J. 248 GHz Sub-Harmonic Mixer Last Transmitter with I/Q Imbalance and LO Feedthrough Calibration. IEEE Solid-State Circuits Lett. 2024, 7, 159–162. [Google Scholar] [CrossRef]

- Zhang, J.; Peng, Y.; Kang, K. Analysis and Design of High-Harmonic-Rejection Multi-Ratio mm-Wave Frequency Multipliers. IEEE J. Solid-State Circuits 2022, 57, 260–277. [Google Scholar] [CrossRef]

- Chen, R.; Chien, H.Y.; Chang, M.C.F. A Compact D-Band Multiply-by-9 Frequency Multiplier with Inductor-Less Active Balun in 16nm p-FinFET Technology. In Proceedings of the 2024 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Washington DC, USA, 16–21 June 2024; pp. 147–150. [Google Scholar] [CrossRef]

- Li, Z.; Chen, J.; Li, H.; Yu, J.; Lu, Y.; Zhou, R.; Chen, Z.; Hong, W. A 220-GHz sliding-IF quadrature transmitter and receiver chipset for high data rate communication in 0.13-μm SiGe BiCMOS. IEEE J. Solid-State Circuits 2023, 58, 1913–1927. [Google Scholar] [CrossRef]

- Hagiwara, T.; Yamaki, N.; Sekine, K.; Sakai, H.; Sahara, K.; Takano, K.; Hara, S.; Lee, S.; Dong, R.; Tanoi, S.; et al. A 258-GHz CMOS transmitter with phase-shifting architecture for phased-array systems. In Proceedings of the 2021 IEEE MTT-S International Microwave Symposium (IMS), Atlanta, GA, USA, 6–11 June 2021; pp. 705–708. [Google Scholar]

- Lee, S.; Kim, K.; Lee, K.; Cho, S.; Choi, S.U.; Lee, J.; Koo, B.T.; Song, H.J. An E-band CMOS direct conversion IQ transmitter for radar and communication applications. In Proceedings of the 2022 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Denver, CO, USA, 19–21 June 2022; pp. 111–114. [Google Scholar]

- LaRocca, T.; Tam, S.W.; Huang, D.; Gu, Q.; Socher, E.; Hant, W.; Chang, F. Millimeter-wave CMOS digital controlled artificial dielectric differential mode transmission lines for reconfigurable ICs. In Proceedings of the 2008 IEEE MTT-S International Microwave Symposium Digest, Philadelphia, PA, USA, 10–15 June 2018; pp. 181–184. [Google Scholar] [CrossRef]

- Uchino, T.; Yamazaki, Y.; Park, S.; Liu, C.; Tian, A.; Shehata, A.; Sakai, H.; Kunihiro, K.; Shirane, A.; Okada, K. A Compact D-Band Phase Shifter with 0.1-degree Phase Resolution and 0.8-degree RMS Phase Error in 65 nm CMOS. In Proceedings of the 2024 IEEE Asian Solid-State Circuits Conference (A-SSCC), Hiroshima, Japan, 18–24 November 2024; pp. 1–3. [Google Scholar] [CrossRef]

- Abbasi, M.; Lee, W. A Low-Loss Passive D-Band Phase Shifter for Calibration-Free, Precise Phase Control. IEEE J. Solid-State Circuits 2024, 59, 1371–1380. [Google Scholar] [CrossRef]

- Wang, H.; Eleraky, M.; Abdelaziz, B.; Lin, B.; Liu, E.; Liu, Y.; Ghorbanpoor, M.; Chu, C.; Ruffino, A.; Xu, J.; et al. Power Amplifiers Performance Survey 2000-Present. 2023. Available online: https://ideas.ethz.ch/research/surveys/pa-survey.html (accessed on 18 February 2025).

- Chen, T.Y.; Lee, Y.C.; Chen, T.H.; Chen, H.S.; Liu, J.Y.C. Two-Way Current Combining Power Amplifier with Multi-Stage Adaptive Bias Control. In Proceedings of the 2018 Asia-Pacific Microwave Conference (APMC), Kyoto, Japan, 6–9 November 2018; pp. 144–146. [Google Scholar]

- Li, S.; Rebeiz, G.M. High Efficiency D-Band Multiway Power Combined Amplifiers with 17.5–19-dBm Psat and 14.2–12.1. IEEE J. Solid-State Circuits 2022, 57, 1332–1343. [Google Scholar] [CrossRef]

- Trinh, V.S.; Song, J.M.; Park, J.D. A 16.5-dBm D-Band Eight-Way Power Amplifier Utilizing Cascaded Transformers in 40-nm Bulk CMOS. IEEE Microw. Wirel. Technol. Lett. 2024, 34, 1019–1022. [Google Scholar] [CrossRef]

- Zhou, R.; Chen, J.; Li, Z.; Yu, J.; Tang, D.; Hong, W. A 260-GHz Power Amplifier with 12.5-dBm Psat and 21.4-dB Peak Gain Utilizing a Modified Coupled-Line-Balun Network. IEEE Trans. Microw. Theory Tech. 2024, 72, 3031–3045. [Google Scholar] [CrossRef]

- Gu, Q.J.; Xu, Z.; Chang, M.C.F. Two-Way Current-Combining W-Band Power Amplifier in 65-nm CMOS. IEEE Trans. Microw. Theory Tech. 2012, 60, 1365–1374. [Google Scholar] [CrossRef]

- Ahn, H.; Oh, K.; Nam, I.; Lee, O. A Highly Efficient and Linear mm-Wave CMOS Power Amplifier Using a Compact Symmetrical Parallel–Parallel Power Combiner with IMD3 Cancellation for 5G Applications. IEEE Access 2021, 9, 150304–150321. [Google Scholar] [CrossRef]

- Davidson, A.; Krishnaswamy, H. Phased-Array-Compatible Area-Efficient D-Band Power Amplifiers in 45 RF SOI based on Cascade Stacking. In Proceedings of the 2024 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Washington DC, USA, 16–18 June 2024; pp. 191–194. [Google Scholar]

- Agah, A.; Jayamon, J.A.; Asbeck, P.M.; Larson, L.E.; Buckwalter, J.F. Multi-drive stacked-FET power amplifiers at 90 GHz in 45 nm SOI CMOS. IEEE J. Solid-State Circuits 2014, 49, 1148–1157. [Google Scholar] [CrossRef]

- Kaymaksut, E.; Zhao, D.; Reynaert, P. Transformer-Based Doherty Power Amplifiers for mm-Wave Applications in 40-nm CMOS. IEEE Trans. Microw. Theory Tech. 2015, 63, 1186–1192. [Google Scholar] [CrossRef]

- Carlowitz, C.; Dietz, M. Integrated Front-End Approaches for Wireless 100 Gb/s and Beyond: Enabling Efficient Ultra-High Speed Wireless Communication Systems. IEEE Microw. Mag. 2023, 24, 16–34. [Google Scholar] [CrossRef]

- Gielen, S.; Zhang, Y.; Ingels, M.; Reynaert, P. A D-band 20.4 dBm OP1dB Transformer-Based Power Amplifier with 23.6PAE In A 250-nm InP HBT Technology. In Proceedings of the 2023 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), San Diego, CA, USA, 11–13 June 2023; pp. 309–312. [Google Scholar] [CrossRef]

- D’heer, C.; Reynaert, P. When High-Speed Communication Hits a Speed Bump: Exploring Shannon’s Equation in mm-Wave Links. IEEE Microw. Mag. 2024, 25, 41–57. [Google Scholar] [CrossRef]

- Camarchia, V.; Quaglia, R.; Piacibello, A.; Nguyen, D.P.; Wang, H.; Pham, A.V. A Review of Technologies and Design Techniques of Millimeter-Wave Power Amplifiers. IEEE Trans. Microw. Theory Tech. 2020, 68, 2957–2983. [Google Scholar] [CrossRef]

- Wang, F.; Wang, H. A High-Power Broadband Multi-Primary DAT-Based Doherty Power Amplifier for mm-Wave 5G Applications. IEEE J. Solid-State Circuits 2021, 56, 1668–1681. [Google Scholar] [CrossRef]

- Kaval, G.; Lasser, G.; Gavell, M.; Fager, C. A 100–114 GHz GaAs MMIC Power Amplifier with Fully Integrated Dynamic Gate Bias Control for Linearization and Efficiency Enhancement. In Proceedings of the 2024 19th European Microwave Integrated Circuits Conference (EuMIC), Paris, France, 24–26 September 2024; pp. 271–274. [Google Scholar] [CrossRef]

- Agrawal, A.; Whitcombe, A.; Shin, W.; Bhat, R.; Kundu, S.; Sagazio, P.; Chandrakumar, H.; Brown, T.; Carlton, B.; Hull, C.; et al. 18.2 A 128Gb/s 1.95pJ/b D-Band Receiver with Integrated PLL and ADC in 22nm FinFET. In Proceedings of the 2023 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 18–22 February 2023; pp. 284–286. [Google Scholar] [CrossRef]

- Hara, S.; Katayama, K.; Takano, K.; Dong, R.; Watanabe, I.; Sekine, N.; Kasamatsu, A.; Yoshida, T.; Amakawa, S.; Fujishima, M. A 32Gbit/s 16QAM CMOS receiver in 300GHz band. In Proceedings of the 2017 IEEE MTT-S International Microwave Symposium (IMS), Honolulu, HI, USA, 4–9 June 2017; pp. 1703–1706. [Google Scholar]

- Snai, M.C.; Razavi, H.; Khanna, P.K.; Razavi, B. A 140-GHz 40-mW Receiver with LO Generation and Phase Shifting for Beamforming Applications. In Proceedings of the 2024 IEEE European Solid-State Electronics Research Conference (ESSERC), Bruge, Belgium, 9–12 September 2024; pp. 492–495. [Google Scholar] [CrossRef]

- Memioglu, O.; Zhao, Y.; Razavi, B. A 300-ghz 52-mw cmos receiver with on-chip lo generation. IEEE J. Solid-State Circuits 2023, 58, 2141–2156. [Google Scholar] [CrossRef]

- Dong, S.; Sharma, N.; Li, S.; Chen, M.; Zhang, X.; Hu, Y.; Li, J.; Su, Y.; Xu, X.; Loseu, V.; et al. A 140ghz rf beamforming phased-array receiver supporting> 20db irr with 8ghz channel bandwidth at low if in 22nm fdsoi cmos. In Proceedings of the 2023 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), San Diego, CA, USA, 11–13 June 2023; pp. 293–296. [Google Scholar]

- Li, S.; Rebeiz, G.M. A 134–149 GHz IF beamforming phased-array receiver channel with 6.4–7.5 dB NF using CMOS 45nm RFSOI. In Proceedings of the 2020 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Los Angeles, CA, USA, 4–6 August 2020; pp. 103–106. [Google Scholar]

- Lee, S.; Amakawa, S.; Yoshida, T.; Hara, S.; Fujishima, M. A 32-Gb/s CMOS receiver with analog carrier recovery and synchronous QPSK demodulation. IEEE Microw. Wirel. Compon. Lett. 2021, 31, 768–770. [Google Scholar] [CrossRef]

- Eissa, M.; Awny, A.; Ko, M.; Schmalz, K.; Elkhouly, M.; Malignaggi, A.; Ulusoy, A.; Kissinger, D. A 220–275 GHz direct-conversion receiver in 130-nm SiGe: C BiCMOS technology. IEEE Microw. Wirel. Compon. Lett. 2017, 27, 675–677. [Google Scholar] [CrossRef]

- Eissa, M.H.; Malignaggi, A.; Wang, R.; Elkhouly, M.; Schmalz, K.; Ulusoy, A.C.; Kissinger, D. Wideband 240-GHz Transmitter and Receiver in BiCMOS Technology with 25-Gbit/s Data Rate. IEEE J. Solid-State Circuits 2018, 53, 2532–2542. [Google Scholar] [CrossRef]

- Jeon, H.R.; Yun, B.H.; Lee, H.K.; Lee, S.G.; Choi, K.S. A 250-GHz Wideband Direct-Conversion CMOS Receiver Adopting Baseband Equalized Low-Loss Resistive Passive Mixer. IEEE Trans. Circuits Syst. II Express Briefs 2023, 70, 3852–3856. [Google Scholar] [CrossRef]

- Razavi, B. RF Microelectronics, 2nd ed.; Prentice Hall Communications Engineering and Emerging Technologies Series; Prentice Hall Press: Hoboken, NJ, USA, 2011. [Google Scholar]

- Aksoyak, İ.K.; Möck, M.; Ulusoy, A.Ç. A Highly Linear D-Band I/Q Receiver with Active Mixer-First Architecture in SiGe Technology. IEEE Trans. Microw. Theory Tech. 2023, 72, 3476–3484. [Google Scholar] [CrossRef]

- Andrews, C.; Molnar, A.C. A passive mixer-first receiver with digitally controlled and widely tunable RF interface. IEEE J. Solid-State Circuits 2010, 45, 2696–2708. [Google Scholar] [CrossRef]

- Iotti, L.; Krishnamurthy, S.; LaCaille, G.; Niknejad, A.M. A low-power 70–100-GHz mixer-first RX leveraging frequency-translational feedback. IEEE J. Solid-State Circuits 2020, 55, 2043–2054. [Google Scholar] [CrossRef]

- Kuo, T.Y.; Tsai, T.C.; Ulusoy, A.C. A D-Band Mixer-First Receiver in 22-nm FD-SOI CMOS with Back-Gate Biasing for I/Q Imbalance Optimization. In Proceedings of the 2024 19th European Microwave Integrated Circuits Conference (EuMIC), Paris, France, 24–26 September 2024; pp. 134–137. [Google Scholar] [CrossRef]

- Thyagarajan, S.V.; Kang, S.; Niknejad, A.M. A 240 GHz fully integrated wideband QPSK receiver in 65 nm CMOS. IEEE J. Solid-State Circuits 2015, 50, 2268–2280. [Google Scholar] [CrossRef]

- Safari, M.M.; Pourrostam, J. Power Consumption and I/Q-to-Phase Analysis in Direct Demodulation Approaches. In Proceedings of the 2024 32nd International Conference on Electrical Engineering (ICEE), Jeju, Republic of Korea, 3–7 June 2024; pp. 1–5. [Google Scholar]

- Mohammadnezhad, H.; Wang, H.; Cathelin, A.; Heydari, P. A 115–135-GHz 8PSK receiver using multi-phase RF-correlation-based direct-demodulation method. IEEE J. Solid-State Circuits 2019, 54, 2435–2448. [Google Scholar] [CrossRef]

- Mnasri, B.; Djerafi, T.; Tatu, S.O.; Wu, K. Spatially Distributed Multi-Input Interferometric Receiver for 5G Wireless Systems and Beyond. IEEE Trans. Microw. Theory Tech. 2019, 67, 2904–2915. [Google Scholar] [CrossRef]

- Dan, I.; Ducournau, G.; Hisatake, S.; Szriftgiser, P.; Braun, R.P.; Kallfass, I. A Terahertz Wireless Communication Link Using a Superheterodyne Approach. IEEE Trans. Terahertz Sci. Technol. 2020, 10, 32–43. [Google Scholar] [CrossRef]

- Beshary, H.; Chen, Y.; Chou, E.; Niknejad, A.M. A 1.54pJ/b 80Gb/s D-Band 2-D Scalable Transceiver Array with On-Chip Antennas in 28-nm Bulk CMOS. IEEE Solid-State Circuits Lett. 2025, 1. [Google Scholar] [CrossRef]

- Deng, J.; Burasa, P.; Wu, K. Joint Multiband Linear Interferometric Receiver for Integrated Microwave and Terahertz Sensing and Communication Systems. IEEE Trans. Microw. Theory Tech. 2024, 72, 5550–5562. [Google Scholar] [CrossRef]

- Ghozzy, S.; Allam, M.; Karahan, E.A.; Liu, Z.; Sengupta, K. 12.2 A mm-Wave/Sub-THz Synthesizer-Free Coherent Receiver with Phase Reconstruction Through Mixed-Signal Kramer-Kronig Processing. In Proceedings of the 2024 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 18–22 February 2024; Volume 67, pp. 220–222. [Google Scholar]

- Harter, T.; Füllner, C.; Kemal, J.N.; Ummethala, S.; Steinmann, J.; Brosi, M.; Hesler, J.L.; Bründermann, E.; Müller, A.S.; Freude, W.; et al. Generalized Kramers-Kronig Receiver for Coherent THz Communications. Nature Photonics 2020, 14, 601–606. [Google Scholar] [CrossRef]

- Wang, C.; Abdo, I.; Liu, C.; da Gomez, C.; Mayeda, J.; Herdian, H.; Wang, W.; Fu, X.; You, D.; Shehata, A.; et al. A sub-THz full-duplex phased-array transceiver with self-interference cancellation and LO feedthrough suppression. IEEE J. Solid-State Circuits 2024, 59, 978–992. [Google Scholar] [CrossRef]

- Pang, J.; Maki, S.; Kawai, S.; Nagashima, N.; Seo, Y.; Dome, M.; Kato, H.; Katsuragi, M.; Kimura, K.; Kondo, S.; et al. A 50.1-Gb/s 60-GHz CMOS transceiver for IEEE 802.11 ay with calibration of LO feedthrough and I/Q imbalance. IEEE J. Solid-State Circuits 2019, 54, 1375–1390. [Google Scholar] [CrossRef]

- Lee, S.; Hara, S.; Yoshida, T.; Amakawa, S.; Dong, R.; Kasamatsu, A.; Sato, J.; Fujishima, M. An 80-Gb/s 300-GHz-band single-chip CMOS transceiver. IEEE J. Solid-State Circuits 2019, 54, 3577–3588. [Google Scholar] [CrossRef]

- Tokgoz, K.K.; Maki, S.; Pang, J.; Nagashima, N.; Abdo, I.; Kawai, S.; Fujimura, T.; Kawano, Y.; Suzuki, T.; Iwai, T.; et al. A 120Gb/s 16QAM CMOS millimeter-wave wireless transceiver. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 168–170. [Google Scholar] [CrossRef]

- Guan, P.; Jia, H.; Deng, W.; Ma, R.; Deng, M.; Xue, J.; Yan, A.; Sun, S.; Wang, Z.; Chi, B. A Fully Integrated Bit-to-Bit 24/48Gb/s QPSK/16-QAM D-Band Transceiver with Mixed-Signal Baseband in 28nm CMOS Technology. In Proceedings of the 2023 IEEE Asian Solid-State Circuits Conference (A-SSCC), Singapore, 11–13 November 2023; pp. 1–3. [Google Scholar]

- Yang, Y.; Zihir, S.; Lin, H.; Inac, O.; Shin, W.; Rebeiz, G.M. A 155 GHz 20 Gbit/s QPSK transceiver in 45nm CMOS. In Proceedings of the 2014 IEEE Radio Frequency Integrated Circuits Symposium, Tampa, FL, USA, 1–3 June 2014; pp. 365–368. [Google Scholar] [CrossRef]

- Gungor, B.; Reynaert, P. Non-Coherent TX-RX Chipsets for J-band Communication in 16-nm FinFET CMOS. In Proceedings of the 2024 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Washington, DC, USA, 16–18 June 2024; pp. 75–78. [Google Scholar]

- Sadhu, B.; Gu, X.; Valdes-Garcia, A. The more (antennas), the merrier: A survey of silicon-based mm-wave phased arrays using multi-IC scaling. IEEE Microw. Mag. 2019, 20, 32–50. [Google Scholar] [CrossRef]

- Okada, K. Sub-THz CMOS Phased-Array Transceiver Design for 6G. In Proceedings of the 2024 IEEE International Symposium on Circuits and Systems (ISCAS), Singapore, 19–22 May 2024; pp. 1–4. [Google Scholar] [CrossRef]

- Farid, A.A.; Ahmed, A.S.; Dhananjay, A.; Rodwell, M.J. A fully packaged 135-GHz multiuser MIMO transmitter array tile for wireless communications. IEEE Trans. Microw. Theory Tech. 2022, 70, 3396–3405. [Google Scholar] [CrossRef]

- Chou, E.; Baniasadi, N.; Beshary, H.; Wei, M.; Naviasky, E.; Iotti, L.; Niknejad, A. A low-power and energy-efficient D-band CMOS four-channel receiver with integrated LO generation for digital beamforming arrays. In Proceedings of the ESSCIRC 2022-IEEE 48th European Solid State Circuits Conference (ESSCIRC), Milan, Italy, 19–22 September 2022; pp. 489–492. [Google Scholar]

- Jung, M.; Li, L.; Ahmed, A.; Hassan, O.; Rebeiz, G.M. A D-Band Scalable 128-Channel Dual-Polarized Receive Phased-Array with On-Chip Down Converters for 2×2 MIMO Achieving 2×42 Gbps. In Proceedings of the 2024 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Washington DC, USA, 16–18 June 2024; pp. 287–290. [Google Scholar] [CrossRef]

- Zhang, J.; Dai, B.; Meng, X.; Hu, Y.; Guan, M.; Deng, H.; Zhang, B.; Wang, C. 24.2 A Scalable 134-to-141GHz 16-Element CMOS 2D λ/2-Spaced Phased Array. In Proceedings of the 2024 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 18–22 February 2024; Volume 67, pp. 414–416. [Google Scholar]

- Li, S.; Zhang, Z.; Rupakula, B.; Rebeiz, G.M. An eight-element 140-GHz wafer-scale IF beamforming phased-array receiver with 64-QAM operation in CMOS RFSOI. IEEE J. Solid-State Circuits 2021, 57, 385–399. [Google Scholar] [CrossRef]

- Naviasky, E.; Iotti, L.; LaCaille, G.; Nikolić, B.; Alon, E.; Niknejad, A.M. A 71-to-86-GHz 16-element by 16-beam multi-user beamforming integrated receiver sub-array for massive MIMO. IEEE J. Solid-State Circuits 2021, 56, 3811–3826. [Google Scholar] [CrossRef]

- Ebrahimi, N.; Wu, P.Y.; Bagheri, M.; Buckwalter, J.F. A 71–86-GHz Phased Array Transceiver Using Wideband Injection-Locked Oscillator Phase Shifters. IEEE Trans. Microw. Theory Tech. 2017, 65, 346–361. [Google Scholar] [CrossRef]

- Wang, C.; Herdian, H.; Zheng, W.; Liu, C.; Mayeda, J.; Liu, Y.; Yong, O.A.; Wang, W.; Zhang, Y.; Gomez, C.D.; et al. 24.3 A 236-to-266GHz 4-Element Amplifier-Last Phased-Array Transmitter in 65nm CMOS. In Proceedings of the 2024 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 18–22 February 2024; Volume 67, pp. 415–417. [Google Scholar] [CrossRef]

- Rodriguez-Vazquez, P.; Grzyb, J.; Heinemann, B.; Pfeiffer, U.R. A QPSK 110-Gb/s Polarization-Diversity MIMO Wireless Link with a 220–255 GHz Tunable LO in a SiGe HBT Technology. IEEE Trans. Microw. Theory Tech. 2020, 68, 3834–3851. [Google Scholar] [CrossRef]

- Choi, K.S.; Abdelmagid, B.A.; Liu, Y.; Wang, H. A D -Band Concurrent 20-Beam MIMO Transmitter Array with a Four-Element Joint Static/Dynamic Beam-Multiplication Beamformer. IEEE J. Solid-State Circuits 2024, 1–15. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, R.; Yan, B.; Chang, M.-C.F. A Review of Circuits and Systems for Advanced Sub-THz Transceivers in Wireless Communication. Electronics 2025, 14, 861. https://doi.org/10.3390/electronics14050861

Chen R, Yan B, Chang M-CF. A Review of Circuits and Systems for Advanced Sub-THz Transceivers in Wireless Communication. Electronics. 2025; 14(5):861. https://doi.org/10.3390/electronics14050861

Chicago/Turabian StyleChen, Runzhou, Boxun Yan, and Mau-Chung Frank Chang. 2025. "A Review of Circuits and Systems for Advanced Sub-THz Transceivers in Wireless Communication" Electronics 14, no. 5: 861. https://doi.org/10.3390/electronics14050861

APA StyleChen, R., Yan, B., & Chang, M.-C. F. (2025). A Review of Circuits and Systems for Advanced Sub-THz Transceivers in Wireless Communication. Electronics, 14(5), 861. https://doi.org/10.3390/electronics14050861