Heuristic Enz–Krummenacher–Vittoz (EKV) Model Fitting for Low-Power Integrated Circuit Design: An Open-Source Implementation

Abstract

1. Introduction

2. Background

2.1. Overview on MOSFET Models

2.2. The Simplified EKV Model

- is the specific current, given by ;

- is the pinch-off voltage, defined as (here, is typically defined as the gate voltage at which the inversion charge density equals the depletion charge density);

- and n are the thermal voltage and the subthreshold slope factor, respectively (previously defined in Section 2.1);

- is the carrier mobility;

- is the oxide capacitance per unit area;

- W and L are the width and the length of the transistor, respectively.

2.3. The Rise of Open-Source Tools in Integrated Circuit Design

- Accessibility: Open-source tools are freely available, democratizing access to advanced design tools and empowering researchers, academics, and independent designers [30].

- Cost-Effectiveness: Eliminating the high costs associated with commercial licenses makes open-source tools an attractive option for both individual researchers and smaller organizations.

- Transparency and Collaboration: Open-source tools foster transparency and collaboration by allowing users to inspect, modify, and contribute to the codebase. This collaborative environment accelerates innovation and fosters a vibrant community of developers and users [31].

- Education and Research: Open-source tools play a crucial role in education and research by providing students and researchers with hands-on experience with real-world design tools and methodologies [36].

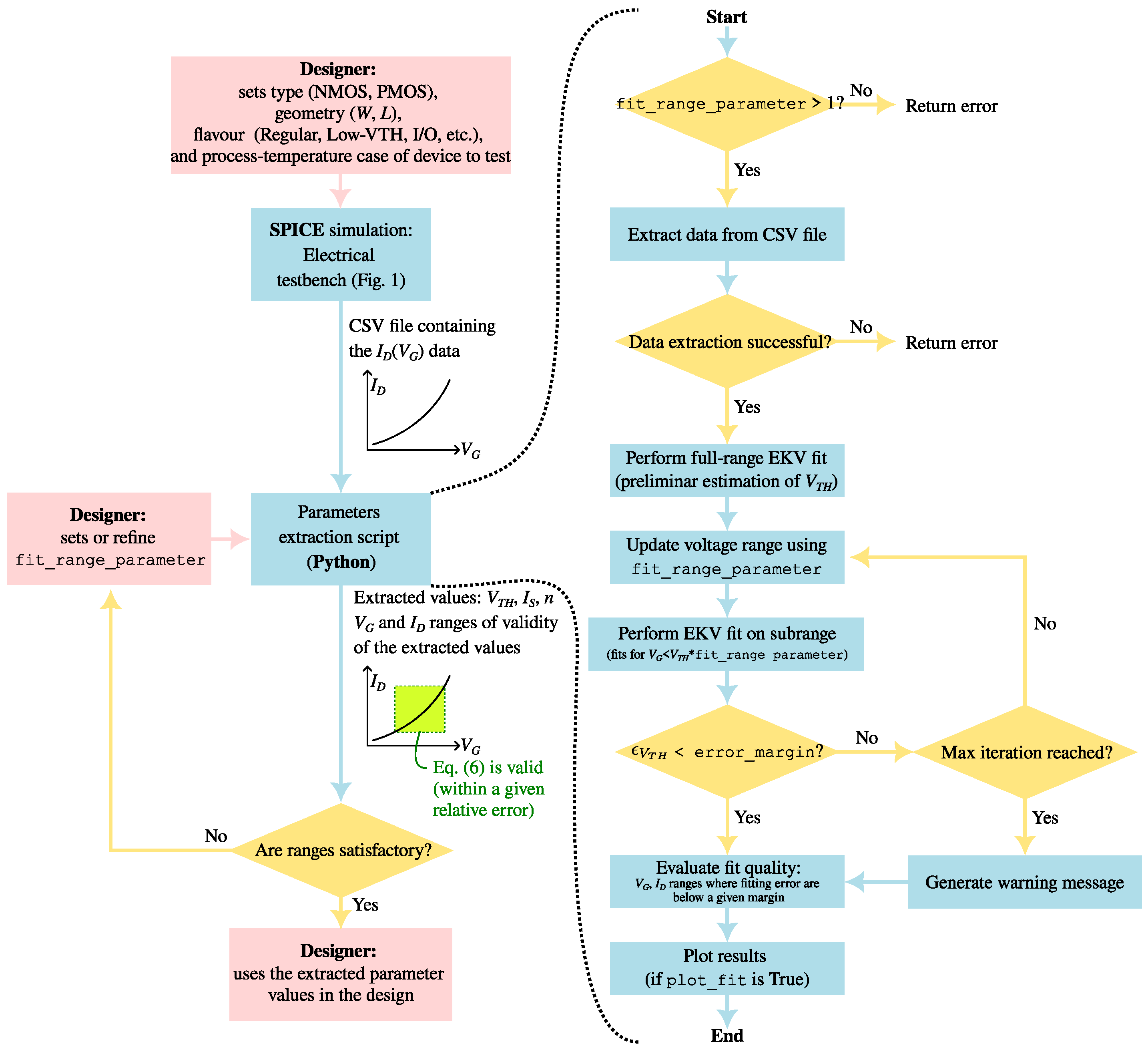

3. Methodology

3.1. Electrical Configuration for Data Extraction

3.2. Least-Squares Optimization: Weighting and Log-Scaling

3.3. Heuristic EKV Model Fitting

3.3.1. Initial Full-Range Fit

3.3.2. Iterative Threshold Voltage Refinement

3.3.3. Fit Quality Assessment

4. Implementation

5. Results and Discussion

5.1. Case Study

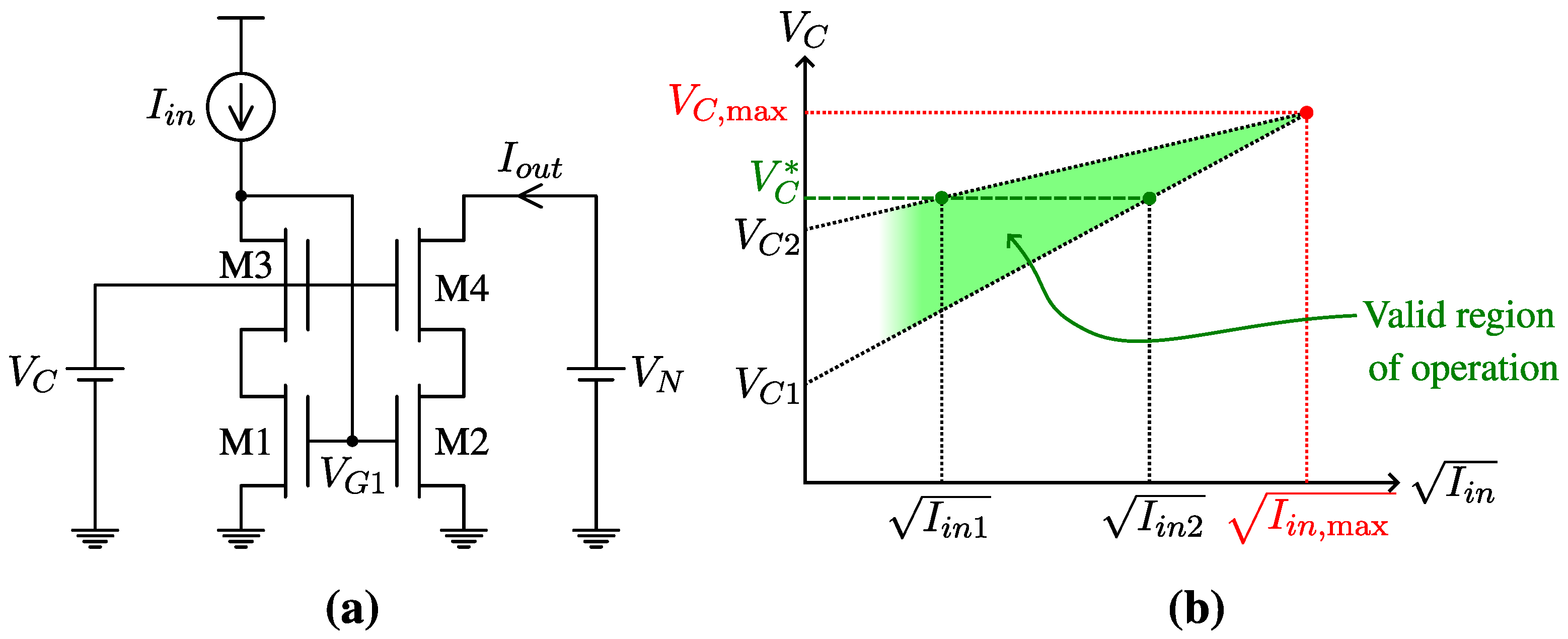

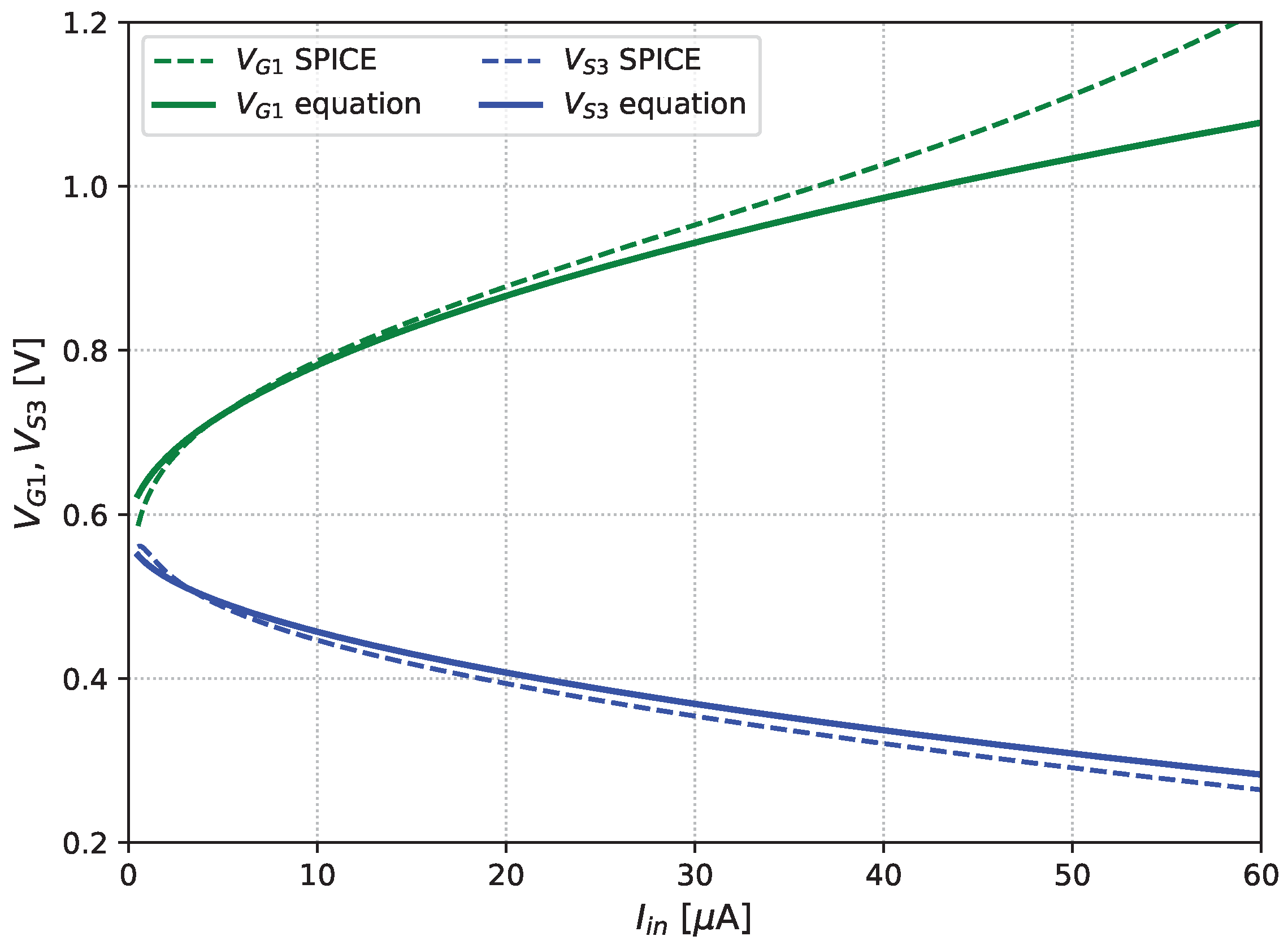

5.2. Design Example: Wide-Swing Cascode Current Mirror

6. Conclusions

- Flexibility: Users can control various aspects of the fitting process, such as the number of iterations (max_iter) and error margins (error_margin), allowing for tailored parameter extraction.

- Fit Quality Assessment: The fit_quality function evaluates the quality of the fitted curve by comparing it to the measured data within a specified error margin (quality_margin). This provides a quantitative measure of the fitting accuracy and is particularly useful in design practice to increase confidence in preliminary analytical estimations prior to extensive electrical simulations.

- Open-Source and Reproducibility: By leveraging open-source tools like scipy, numpy, and matplotlib, the implementation promotes reproducibility and accessibility, aligning with the principles of open science.

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Appendix A

Appendix A.1. Simplified Fitter Class Code

Appendix A.2. Step-by-Step Basic Usage

- 1.

- Initializing the Fitter class: to begin, create an instance of the Fitter class. This involves specifying the path to your data file and optionally, setting any specific fitting parameters.

- 2.

- Accessing the results: once the Fitter object is set up, it automatically begins the fitting process. The results are stored as attributes of the Fitter instance, including the fitted parameters and quality metrics.

- 3.

- Customizing the fitting process: by adjusting parameters like fit_range_parameter, error_margin, and quality_margin, you can tailor the fitting process to meet the specific needs of your analysis.

- 4.

- Leveraging additional features: beyond the basic fitting process, the Fitter class includes additional capabilities such as current logarithmic scaling (see Section 3.2) and extended plotting options for detailed analysis.

References

- Gielen, G.; De Graaf, H.C.; Sansen, W.M.C. A new efficient MOS transistor model (BSIM) for circuit simulation. In Proceedings of the 1990 IEEE International Symposium on Circuits and Systems, New Orleans, LA, USA, 1–3 May 1990; pp. 182–185. [Google Scholar] [CrossRef]

- Sheu, B.J.; Scharfetter, D.L.; Ko, P.K.; Jeng, M.C. BSIM: Berkeley short-channel IGFET model for MOS transistors. IEEE J. Solid-State Circuits 1987, 22, 558–566. [Google Scholar] [CrossRef]

- Cheng, Y.; Hu, C. MOSFET Modeling & BSIM3 User’s Guide; Springer: New York, NY, USA, 1999. [Google Scholar]

- Schichman, H.; Hodges, D.A. Modeling and simulation of insulated-gate field-effect transistor switching circuits. IEEE J. Solid-State Circuits 1968, 3, 285–289. [Google Scholar] [CrossRef]

- Enz, C.C.; Krummenacher, F.; Vittoz, E.A. An analytical MOS transistor model valid in all regions of operation and dedicated to low-voltage and low-current applications. Analog Integr. Circuits Signal Process. 1995, 8, 83–114. [Google Scholar] [CrossRef]

- Enz, C.C.; Vittoz, E.A. CMOS low-power analog circuit design. In Emerging Technologies: Designing Low Power Digital Systems; IEEE: Piscataway, NJ, USA, 1996; pp. 79–133. [Google Scholar] [CrossRef]

- Enz, C.C.; Vittoz, E.A. Charge-Based MOS Transistor Modeling: The EKV Model for Low-Power and RF IC Design; Wiley: Hoboken, NJ, USA, 2006. [Google Scholar]

- Enz, C.; Chicco, F.; Pezzotta, A. Nanoscale MOSFET modeling: Part 1: The simplified EKV model for the design of low-power analog circuits. IEEE Solid-State Circuits Mag. 2017, 9, 26–35. [Google Scholar] [CrossRef]

- Enz, C.; Chicco, F.; Pezzotta, A. Nanoscale MOSFET modeling: Part 2: Using the inversion coefficient as the primary design parameter. IEEE Solid-State Circuits Mag. 2017, 9, 73–81. [Google Scholar] [CrossRef]

- Serra-Graells, F. VLSI CMOS low-voltage log companding filters. In Proceedings of the 2000 IEEE International Symposium on Circuits and Systems (ISCAS), Geneva, Switzerland, 28–31 May 2000; Volume 1, pp. 172–175. [Google Scholar] [CrossRef]

- Sansen, W. Biasing for zero distortion: Using the EKV/BSIM6 expressions. IEEE Solid-State Circuits Mag. 2018, 10, 48–53. [Google Scholar] [CrossRef]

- Xie, Q.; Xu, J.; Taur, Y. Review and Critique of Analytic Models of MOSFET Short-Channel Effects in Subthreshold. IEEE Trans. Electron Devices 2012, 59, 1569–1579. [Google Scholar] [CrossRef]

- Chaudhry, A.; Roy, J.N. MOSFET models, quantum mechanical effects and modeling approaches: A review. JSTS J. Semicond. Technol. Sci. 2010, 10, 20–27. [Google Scholar] [CrossRef]

- Cerederia, A.; Estrada, M.; Alvardo, J.; Garduno, I.; Contreras, E.; Tinoco, J. Review On Double Gate Mosfets and Finfet Modelling. Electron. Energ. 2013, 26, 197–213. [Google Scholar]

- Chauhan, Y.S.; Venugopalan, S.; Chalkiadaki, M.-A.; Karim, M.A.U.; Agarwal, H.; Khandelwal, S. BSIM6: Analog and RF Compact Model for Bulk MOSFET. IEEE Trans. Electron. Dev. 2014, 61, 234–244. [Google Scholar] [CrossRef]

- BSIM Group at UC Berkeley. The BSIM Family. Available online: https://www.bsim.berkeley.edu/models/ (accessed on 4 March 2025).

- Mattausch, H.J.; Miura-Mattausch, M.; Sadachika, N.; Miyake, M.; Navarro, D. The HiSIM compact model family for integrated devices containing a surface-potential MOSFET core. In Proceedings of the 2008 15th International Conference on Mixed Design of Integrated Circuits and Systems, Poznan, Poland, 19–21 June 2008; pp. 39–50. [Google Scholar]

- Bhattacharyya, A.B. Semiconductor Physics Review for MOSFET Modeling. In Compact MOSFET Models for VLSI Design; IEEE: New York, NY, USA, 2009; pp. 1–53. [Google Scholar] [CrossRef]

- Gildenblat, G.; Wu, W.; Li, X.; Zhu, Z.; Smit, G.D.J.; Scholten, A.J.; Klaassen, D.B.M. Surface-potential-based MOSFET models with introduction to PSP (invited). In Proceedings of the 2009 IEEE 10th Annual Wireless and Microwave Technology Conference, Clearwater, FL, USA, 20–21 April 2009; pp. 1–2. [Google Scholar] [CrossRef]

- Araujo-Cunha, A.I.; Schneider, M.C.; Galup-Montoro, C. An MOS transistor model for analog circuit design. IEEE J. Solid-State Circuits 1998, 33, 1510–1519. [Google Scholar] [CrossRef]

- Sansen, W.M. Analog Design Essentials; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2007; Volume 859. [Google Scholar]

- Jespers, P. The gm/ID Methodology, a Sizing Tool for Low-Voltage Analog CMOS Circuits: The Semi-Empirical and Compact Model Approaches; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2009. [Google Scholar]

- Sansen, W. Minimum power in analog amplifying blocks: Presenting a design procedure. IEEE Solid-State Circuits Mag. 2015, 7, 83–89. [Google Scholar] [CrossRef]

- Neto, D.G.A.; Bouchoucha, M.K.; Maranhão, G.; Barragan, M.J.; Schneider, M.C.; Cathelin, A.; Galup-Montoro, C. Design-oriented single-piece 5-DC-parameter MOSFET model. IEEE Access. 2024, 12, 87420–87437. [Google Scholar] [CrossRef]

- Bucher, M.; Lallement, C.; Enz, C.; Theodoloz, F.; Krummenacher, F. The EPFL-EKV MOSFET Model Equations for Simulation, Model Version 2.6; Electronics Laboratories, Swiss Federal Institute of Technology (EPFL): Lausanne, Switzerland, 1997. [Google Scholar]

- Bucher, M.; Lallement, C.; Enz, C.C. An efficient parameter extraction methodology for the EKV MOST model. In Proceedings of the International Conference on Microelectronic Test Structures, Osaka, Japan, 25–28 March 1996; pp. 145–150. [Google Scholar] [CrossRef]

- Li, X.; Gildenblat, G. Robust parameter extraction for MOSFET models. IEEE Trans. Electron Devices 2009, 56, 952–958. [Google Scholar] [CrossRef]

- Bajer, K.; Paul, S.; Peters-Drolshagen, D. Parameter extraction for a simplified EKV-model in a 28nm FDSOI technology. In Proceedings of the 2020 27th International Conference on Mixed Design of Integrated Circuits and System (MIXDES), Wrocław, Poland, 25–27 June 2020; pp. 45–49. [Google Scholar] [CrossRef]

- Serra-Graells, F.; Rueda, A.; Huertas, J.L. Low-Voltage CMOS Log Companding Analog Design; Springer: New York, NY, USA, 2006; Volume 733. [Google Scholar]

- Ajayi, T.; Blaauw, D.; Chan, T.B.; Cheng, C.K.; Chhabria, V.; Choo, D.K.; Coltella, M.; Dreslinski, R.; Fogaça, M.; Hashemi, S.; et al. OpenROAD: Toward a self-driving, open-source digital layout implementation tool. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2020, 39, 2925–2936. [Google Scholar]

- Gagliardi, F.; Dei, M. Open and Collaborative Dataset for the Classification of Operational Transconductance Amplifiers for Switched-Capacitor Applications. Data 2024, 9, 114. [Google Scholar] [CrossRef]

- Reda, S.; Stok, L.; Gaillardon, P.E. Guest Editors’ Introduction: The Resurgence of Open-Source EDA Technology. IEEE Des. Test 2021, 38, 5–7. [Google Scholar] [CrossRef]

- Goyal, C.; Khandeparkar, H.; Charan, S.; Baquero, J.S.; Li, A.; Euphrosine, J.; Saligane, M. Disrupting conventional chip design through the open source EDA ecosystem. In Proceedings of the 2024 8th IEEE Electron Devices Technology & Manufacturing Conference (EDTM), Singapore, 10–13 March 2024; pp. 1–3. [Google Scholar] [CrossRef]

- Kahng, A.B. Open-source EDA: If we build it, who will come? In Proceedings of the 2020 IFIP/IEEE 28th International Conference on Very Large Scale Integration (VLSI-SOC), Salt Lake City, UT, USA, 6–9 October 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Galán-Benítez, I.; Carmona-Galán, R.; de la Rosa, J.M. On the use of open-source EDA tools for teaching and learning microelectronics. In Proceedings of the 2024 XVI Congreso de Tecnología, Aprendizaje y Enseñanza de la Electrónica (TAEE), Valencia, Spain, 19–21 June 2024; pp. 1–6. [Google Scholar] [CrossRef]

- Koohang, A.; Harman, K. Open source: A metaphor for e-learning. Inform. Sci. 2005, 8, 75–86. [Google Scholar] [CrossRef]

- scipy.optimize.curve_fit, SciPy v1.13.0 Manual; SciPy: Austin, TX, USA, 2023; Available online: https://docs.scipy.org/doc/scipy/reference/generated/scipy.optimize.curve_fit.html (accessed on 7 January 2025).

- Virtanen, P.; Gommers, R.; Oliphant, T.E.; Haberland, M.; Reddy, T.; Cournapeau, D.; Burovski, E.; Peterson, P.; Weckesser, W.; Bright, J.; et al. SciPy 1.0: Fundamental algorithms for scientific computing in Python. Nat. Methods 2020, 17, 261–272. [Google Scholar] [CrossRef]

- Carusone, T.C.; Johns, D.A.; Martin, K.W. Analog Integrated Circuit Design; John Wiley & Sons: Hoboken, NJ, USA, 2011; Chapter 6. [Google Scholar]

- Ria, A.; Cicalini, M.; Bruschi, P.; Piotto, M.; Dei, M. Wide-Range Low-Power Low-Voltage Integrated Capacitance-to-Digital Converter for On-Body Sweat-Rate Sensing. IEEE Sens. J. 2025, 25, 10250–10260. [Google Scholar] [CrossRef]

- Catania, A.; Gagliardi, F.; Piotto, M.; Bruschi, P.; Dei, M. Ultralow-Power Inverter-Based Delta-Sigma Modulator for Wearable Applications. IEEE Access 2024, 12, 80009–80019. [Google Scholar] [CrossRef]

- Gagliardi, F.; Ria, A.; Piotto, M.; Bruschi, P. A 114 ppm/oC-TC 0.78%-(σ/μ) Current Reference with Minimum-Current-Search Calibration. IEEE Trans. Circuits Syst. II Express Briefs 2024, 71, 1561–1565. [Google Scholar] [CrossRef]

- Aymerich, J.; Ferrer-Vilanova, A.; Cisneros-Fernández, J.; Escudé-Pujol, R.; Guirado, G.; Terés, L.; Dei, M.; Muñoz-Berbel, X.; Serra-Graells, F. Ultrasensitive bacterial sensing using a disposable all-in-one amperometric platform with self-noise cancellation. Biosens. Bioelectron. 2023, 234, 115342. [Google Scholar] [CrossRef] [PubMed]

- Aymerich, J.; Márquez, A.; Muñoz-Berbel, X.; Del Campo, F.J.; Guirado, G.; Terés, L. A 15-µW 105-dB 1.8-Vpp Potentiostatic Delta-Sigma Modulator for Wearable Electrochemical Transducers in 65-nm CMOS Technology. IEEE Access 2020, 8, 62127–62136. [Google Scholar] [CrossRef]

- DeepSeek. DeepSeek-V3: Artificial Intelligence Model. 2024. Available online: https://www.deepseek.com (accessed on 24 January 2025).

- Dei, M. EKV-Fit: A Python Library for EKV MOSFET Model Fitting; GitHub Repository. 2024. Available online: https://github.com/michele-dei/EKV-fit (accessed on 12 March 2025).

| fit_range_parameter | Extracted | Validity Interval | IC Interval |

|---|---|---|---|

| [µA] | [µA] | Equation (5) | |

| 1.001 | 0.574 | 0.001–0.515 | ≈0.001–0.9 |

| 1.100 | 1.015 | 0.006–6.644 | ≈0.006–6.5 |

| 1.600 | 0.534 | 0.356–25.842 | ≈0.7–48 |

| Device | M1, M2 | M3, M4 | |

|---|---|---|---|

| W, L | [µm] | 2.0, 1.0 | 2.0, 0.5 |

| Extracted | [mV] | 578 | 609 |

| Extracted | [µA] | 0.845 | 1.413 |

| Extracted n | 1.146 | 1.095 | |

| Valid current range | [µA] | 0.9–57.9 | 1.9–105.7 |

| Valid gate voltage range | [V] | 0.61–1.08 | 0.65–1.09 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Dei, M. Heuristic Enz–Krummenacher–Vittoz (EKV) Model Fitting for Low-Power Integrated Circuit Design: An Open-Source Implementation. Electronics 2025, 14, 1162. https://doi.org/10.3390/electronics14061162

Dei M. Heuristic Enz–Krummenacher–Vittoz (EKV) Model Fitting for Low-Power Integrated Circuit Design: An Open-Source Implementation. Electronics. 2025; 14(6):1162. https://doi.org/10.3390/electronics14061162

Chicago/Turabian StyleDei, Michele. 2025. "Heuristic Enz–Krummenacher–Vittoz (EKV) Model Fitting for Low-Power Integrated Circuit Design: An Open-Source Implementation" Electronics 14, no. 6: 1162. https://doi.org/10.3390/electronics14061162

APA StyleDei, M. (2025). Heuristic Enz–Krummenacher–Vittoz (EKV) Model Fitting for Low-Power Integrated Circuit Design: An Open-Source Implementation. Electronics, 14(6), 1162. https://doi.org/10.3390/electronics14061162