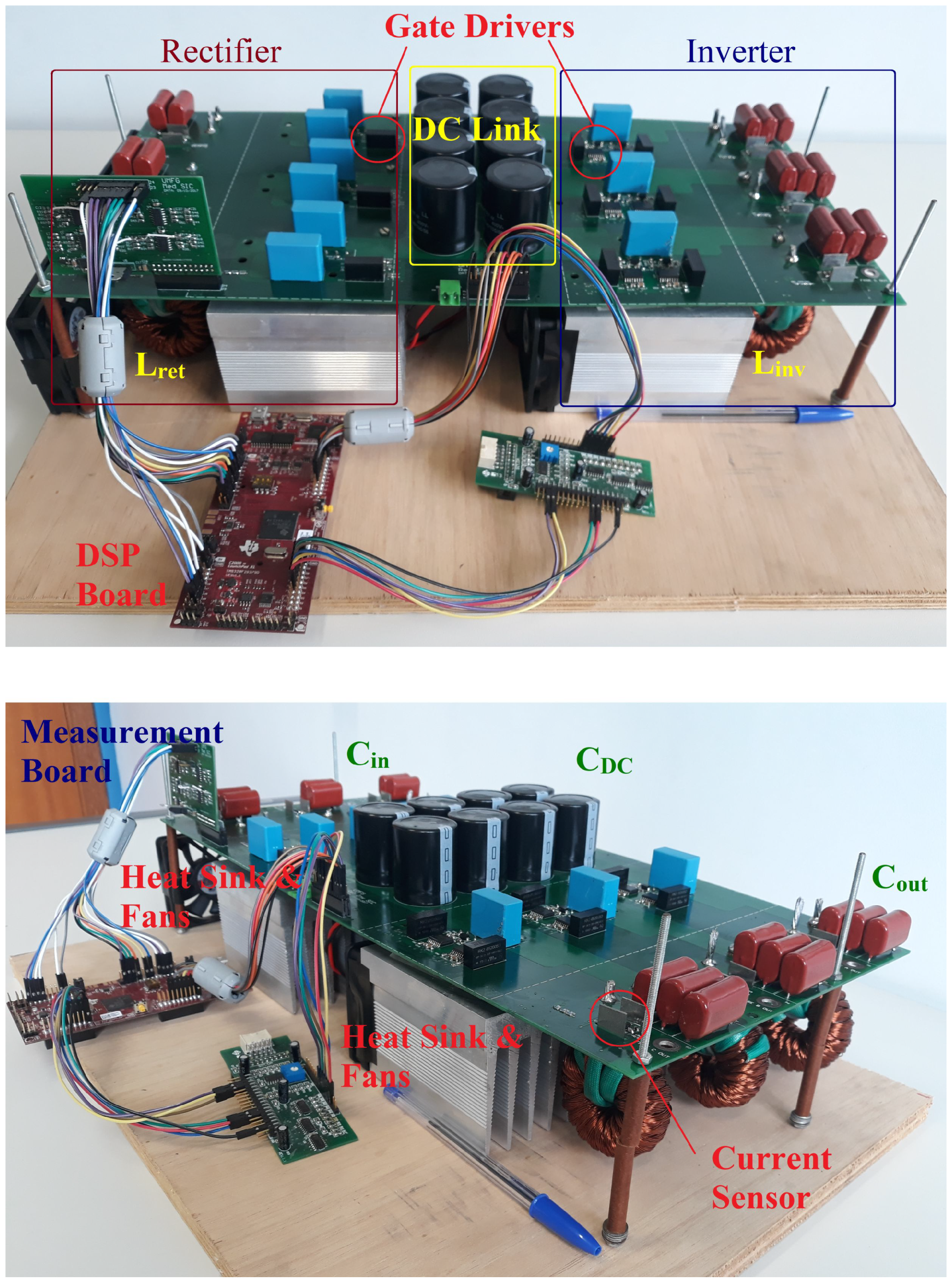

This section is focused on the design of the main hardware components. The following topics are addressed: Thermal design (loss estimation and heat sink sizing), inductor design ( and ), and capacitors sizing (DC link and filter capacitors).

3.1. Thermal Design

Despite being a good first step for comparison and topology choice, the estimation of switch losses through the use of datasheet’s switching energy curves, as done in [

18], is not accurate. The manufacturer does not clearly state the conditions under which the double pulse test was performed, the measuring equipment used, and the inductance of the switching loop are not reported. Some researchers have published recent works reporting big differences between the energy curves available in the datasheet and experimental curves verified in real prototypes [

19,

20,

21].

The cited works used experimental setups to measure the switching energies to, then, be able to use this data in the converter loss estimation. However, most of the time it is necessary that the designer can estimate the losses of a converter without the need to perform an experimental procedure.

Thus, this work will use a simulation approach to estimate the energy curves of the SiC MOSFET and, afterward, estimate the losses. The simulation will be done in Spice via SImetrix software using the Spice model of the SCT3030AL transistor provided by the manufacturer. However, the simulation must be done in order to model a more realistic condition of operation considering the inductances of the power loop and transistors leads. These inductances exert great influence on the transistor’s switching and can make it slower. Thus, a more realistic simulation was performed including the parasitic inductances of decoupling capacitors, transistors, and PCB tracks. The simulation diagram can be seen in

Figure 2.

The simulation was performed for current values between 0 and 75 A, and the energy curves obtained were plotted in

Figure 3 with the curves provided by the manufacturer.

By analyzing the graph, it is possible to notice that the inclusion of the parasite inductances greatly affects the switching losses, which reaffirms the need to minimize these inductances. The difference reaches about 70% to the maximum current point. In addition, it is noted that when the current is close to zero, the switching energy is not zero, this is due to insufficient energy to discharge and charge the parasitic capacitances of the transistors. In this way, the switching will only occur after the end of the dead time, when the complementary key will be closed, realizing the abrupt charge and discharge of the MOSFETs output capacitances. Therefore, when the current is close to zero, the energy lost in the switching corresponds to the energy stored in the parasitic capacitances.

The total losses were calculated, using the method of loss estimation described in [

22] and the curves obtained by simulation, and are shown in

Table 2 for the rectifier and in

Table 3 for the inverter. Since the SiC Schottky diode has negligible reverse recovery, its switching losses were considered zero.

From the estimation of losses it is possible to size the heatsink for cooling the converter. Two identical heatsinks have been chosen for use, one for the rectifier switches and one for cooling the inverter switches, the part number is P 16 from Semikron with standard length of 100 mm.

The thermal resistance (

) of this heatsink, when subjected to an air flow of 6 m/s in its fins, is 0.175 ℃/W. A Sil-Pad 2000 thermal interface was used whose thermal resistance (

) is 0.23 ℃/W. As the junction-case (

) thermal resistance of the diode and the MOSFET are respectively 0.6 ℃/W and 0.44 ℃/W, the temperatures at the junctions of the transistors can be calculated through the thermal models of the

Figure 4 and

Figure 5.

The temperatures were calculated and are shown in

Table 4, it was considered an ambient temperature of 40 ℃. As can be seen, the none of the junction temperatures of the semiconductor devices exceeded the maximum operating limit of 175 ℃. Thus, the thermal design developed is considered adequate.

3.2. Inductor Design

The input and output inductors are responsible for filtering the harmonic components at the switching frequency. The inductor design involves calculating the inductance required to obtain a particular ripple, choice of magnetic core material, and winding design.

The required inductance value can be calculated by the following generic equation [

23]:

where

n is a variable that depends on the number of levels, for 2-level converters

and for 3-level converters

. Thus, it is possible to calculate the value for input and output inductances. Firstly for the rectifier:

Then, a similar calculation is made for the inverter:

It was decided to use relatively high ripple values to reduce the inductance required and improve system dynamics.

For the choice of magnetic material, only alloy powder cores were considered because they are often more suitable for operation at high currents and mid switching frequency range. It was decided to fix the core size and choose the material based on its losses and its cost.

Table 5 shows the main characteristics of the evaluated cores.

Core losses can be calculated using the formula proposed by Steinmetz, which is an empirical expression that is adjusted to the loss data by choosing 3 coefficients supplied by the manufacturers or obtained from curves that can also be supplied by the manufacturers. The equation can be written as:

where

,

, and

are the Steinmetz coefficients which depend on the characteristics of the material,

f is the operating frequency,

is the peak value of the flux density, and

is the volume of the magnetic core.

However, this empirical equation is obtained from the application of sinusoidal flux densities. The flux density imposed on magnetic materials of static converters usually has non-sinusoidal waveforms. For this reason, many researchers have proposed improvements to the Steinmetz equation to take into account the application of non-sinusoidal waveforms. Some of these proposals are Modified Steinmetz Equation-MSE [

24], Generalized Steinmetz Equation-GSE [

25], improved Generalized Steinmetz Equation-iGSE [

26], and improved-improved Generalized Steinmetz Equation-i

GSE [

27].

Some papers have presented accurate results when iGSE or i

GSE are used to estimate core losses, with errors between the experimental and theoretical results lower than 10% [

26,

27,

28,

29]. The difference between iGSE and i

GSE is the fact that i

GSE includes the relaxation effects due to DC levels of the flux density. However, the flux-density waveforms of the converters in this work do not show DC levels, so the use of iGSE is sufficient for calculating core losses. The formula for using the iGSE method is given below:

with

being determined by:

Although the iGSE has been demonstrated to be accurate, the computational routine proposed by its authors has two drawbacks: the first is the computational complexity of the algorithm that must scan the flux density data vector to perform a loops separation, the second is the generation of the flux density data vector which, if done by simulation, can spend considerable time.

For this reason, a method to accelerate the process of using iGSE has been proposed in [

30]. The method consists of the deduction of the closed-form solution of the excitation waveform. In this way, it is possible to perform the iGSE calculations only with the converter input data (RMS voltage, RMS current, switching frequency, magnetic core data), i.e., without the need for simulation or complex algorithms, making it ideal for use in design optimization softwares for inductors. The authors in [

30] made the deductions in the case of a single-phase Bridgeless PFC converter, and can also be applied to 3-level Vienna rectifiers. An extension was made to cover a 2-level inverter and was used in this work to calculate core losses.

Then, the losses were calculated for the four cores evaluated as a function of the number of turns for

.

Figure 6 shows the results of calculating the core losses. First, it can be seen that the core with the highest losses is the XFlux, so it is discarded from selection. Then, the higher the number of turns the lower the difference between the losses of the High Flux core and the high-cost MPP core. Moreover, MPP and Kool M

cores have the disadvantage of low saturation flux density,

Figure 6 shows that, even with few turns, these cores saturate due to the high current of the inverter. Therefore, the core High Flux will be chosen for the rectifier and inverter inductors.

The number of turns used in the rectifier and inverter inductors will be 26 and 33, respectively. With this amount of turns it is possible to achieve the required inductance. To compose the windings, 38 AWG25 gauge copper wires will be used in parallel. Considering that the copper resistivity at 100 ℃ is

[

31], the dc winding resistance will be 6.1 m

and 7.8 m

for the rectifier and inverter inductors, respectively. The estimated copper losses and core losses are shown in

Table 6, only the fundamental component was considered to calculate copper losses, core losses were considered constant and independent of the load.

3.3. Capacitor Sizing

The sizing of the DC link capacitor takes into account the ripple criteria. For the DC link capacitor, the worst case occurs when the inverter feeds an unbalanced load, the higher the unbalance the greater the ripple. Thus, it is possible to calculate the needed capacitance when the neutral current and the ripple are given [

4]:

where

is the output voltage peak value and

is the neutral current peak value.

It was decided to use 4 electrolytic capacitors of 560 F/400 V, manufactured by EPCOS part number B43644B9567M000, in parallel, totaling a capacitance of 2240 F for each group.

Then, the output LC filter capacitor will be sized based on the attenuation criteria, this filter is required to attenuate harmonic components close to the switching frequency. It is a second order and has attenuation of 40 dB per decade from the cutoff frequency, so the cutoff frequency,

, will be defined as less than one-tenth of the switching frequency, which will guarantee a 100-fold attenuation in the amplitude of the harmonics. Therefore, the capacitor value can be determined by:

Thus, it was decided to use three capacitors of 2.2 F/400 V in parallel, totaling a capacitance of 6.6 F, the capacitors are manufactured by Panasonic part number ECQ-E4225KF.

The input LCL filter is formed by the grid inductance (

), rectifier inductance (

) and input capacitance (

). Several researchers have published works where the central subject is the design and modeling of LCL filters using different methodologies and criteria [

32,

33,

34,

35]. However, the grid inductance changes depending on the electrical network, the equipment is expected to operate in facilities where the grid inductance varies from 64.19

H to 1.28 mH, which allows a short circuit power from 10 to 200 times the power of the equipment. As the rectifier inductance and the grid inductance were already defined, it remains only to size the input capacitor.

One of the criteria defined in [

32] recommends to allocate the resonance frequency between ten times the grid frequency (600 Hz) and half the switching frequency (51 kHz). The resonant frequency of an LCL filter can be calculated by the equation:

By rearranging the terms of the Equation (

9) and allocating the resonance frequency at 15 kHz, it is possible to obtain a range of values for the capacitor.

In this way, it was decided to use two 2.2 F/400 V capacitors in parallel, totalizing a capacitance of 4.4 F, the capacitors are manufactured by Panasonic part number ECQ-E4225KF.