A Complementary Recycling Operational Transconductance Amplifier with Data-Driven Enhancement of Transconductance †

Abstract

:1. Introduction

2. Folded Cascode OTA and Recycling Technique

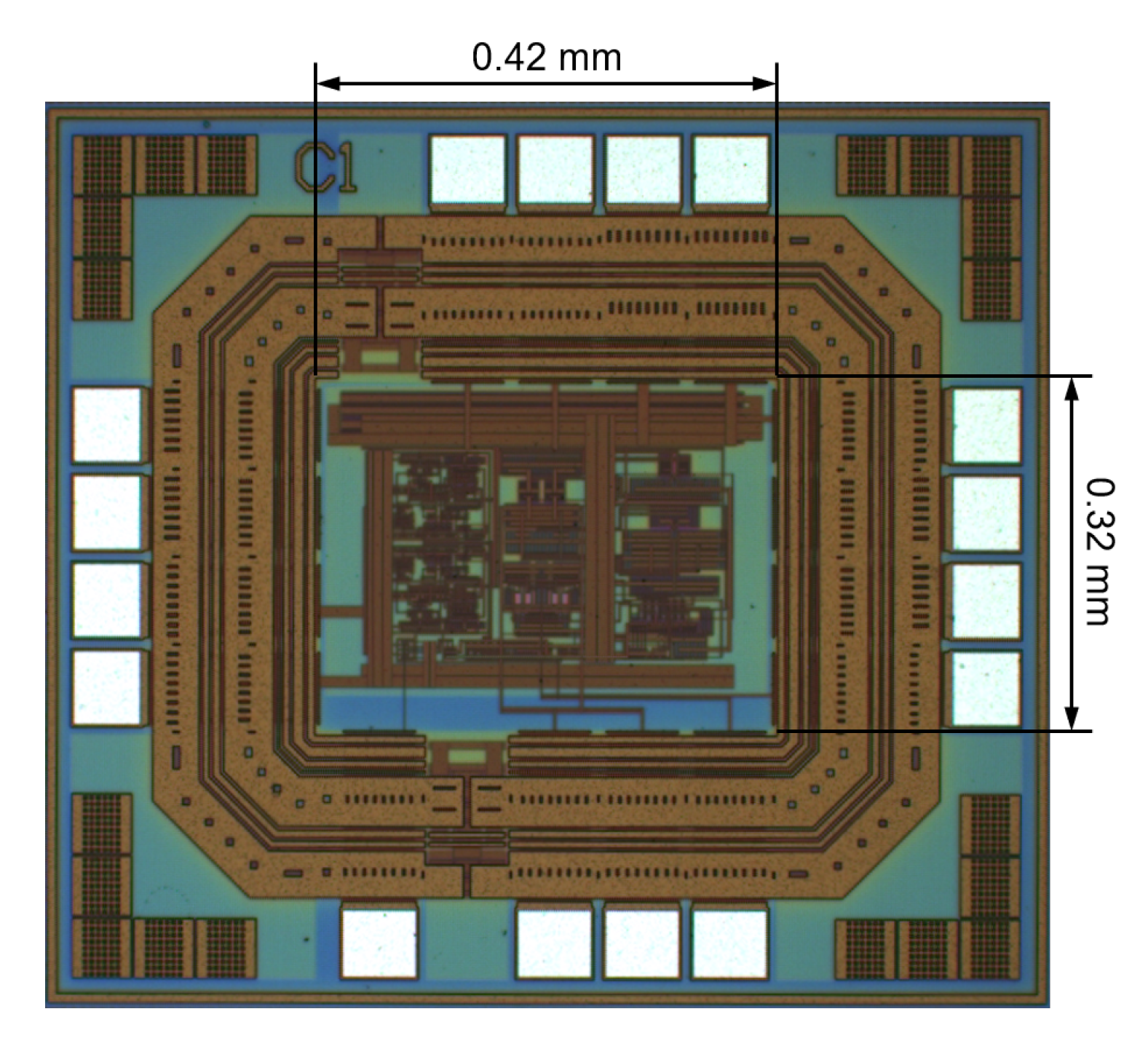

3. Proposed Data-Driven CRFC OTA

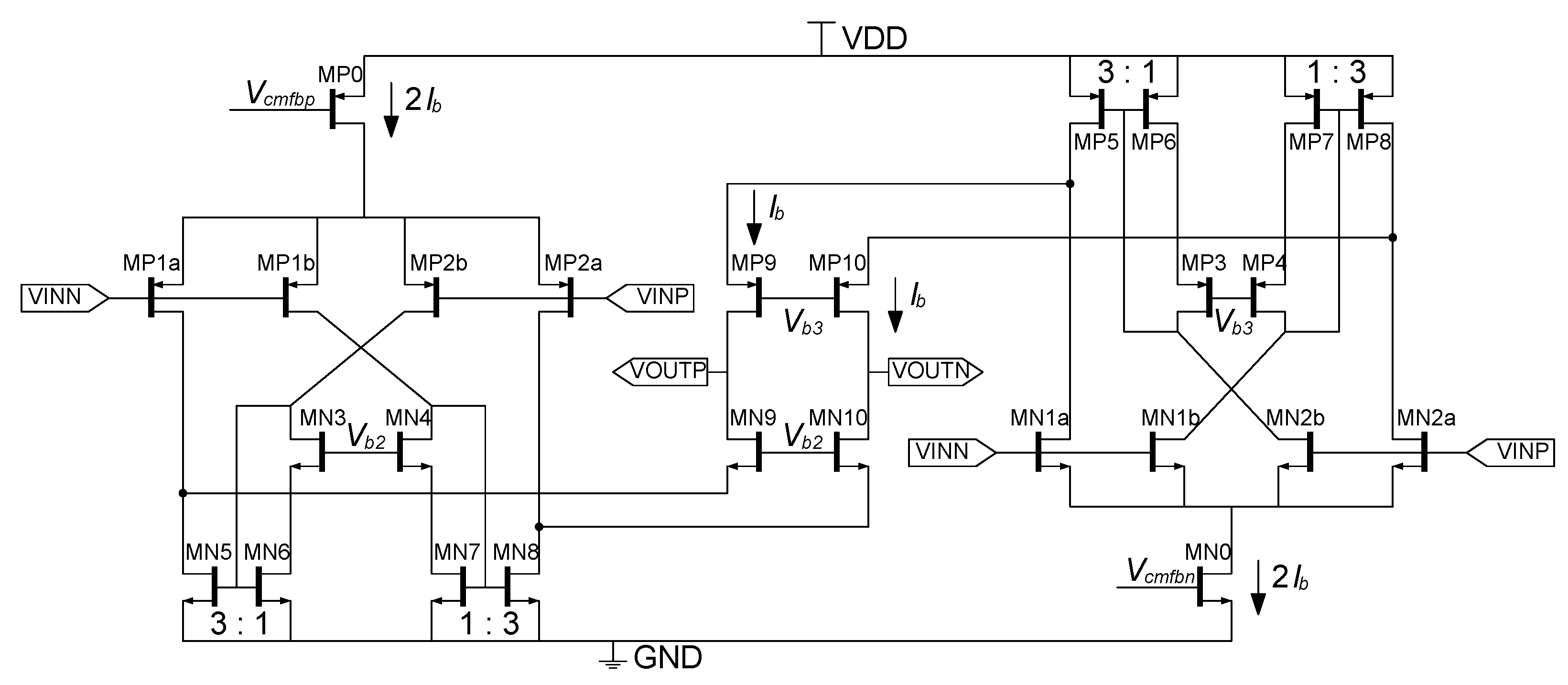

3.1. CRFC Amplifier Circuit

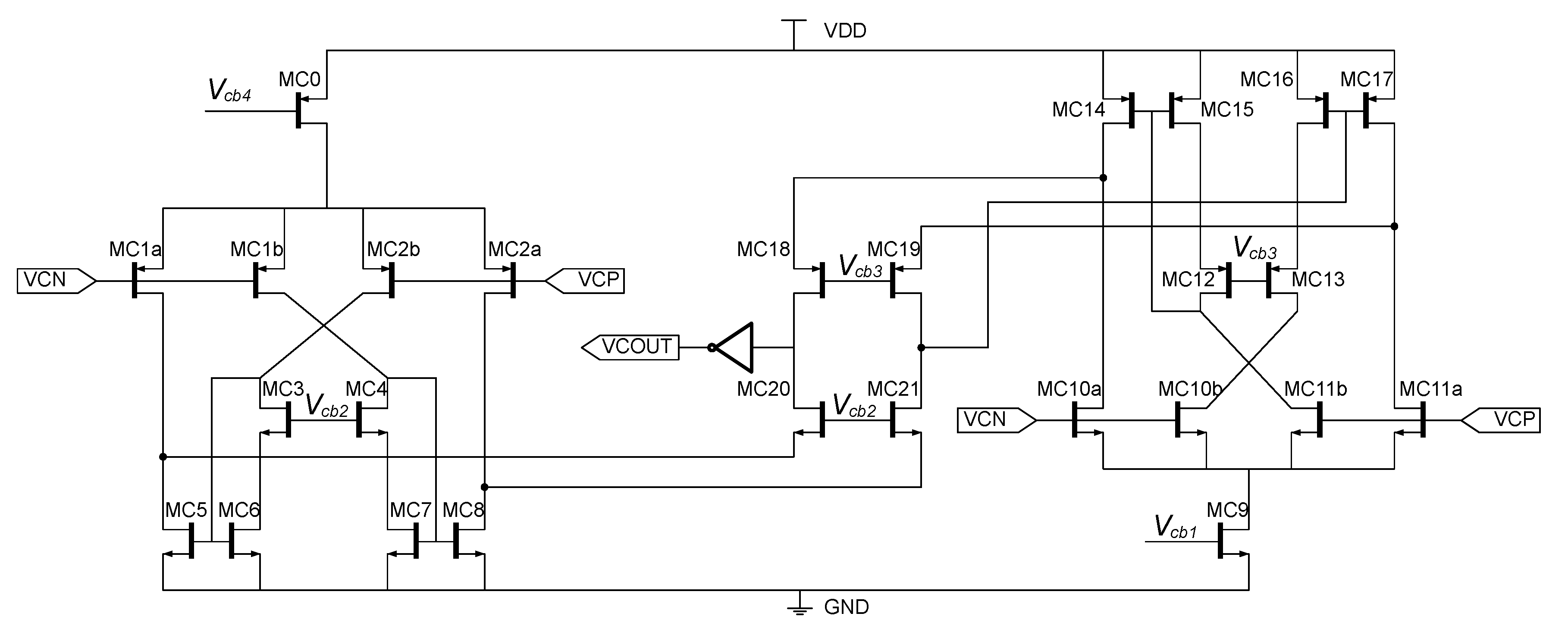

3.2. Data-Driven Biasing Scheme

3.3. Common-Mode Feedback (CMFB) Realisation

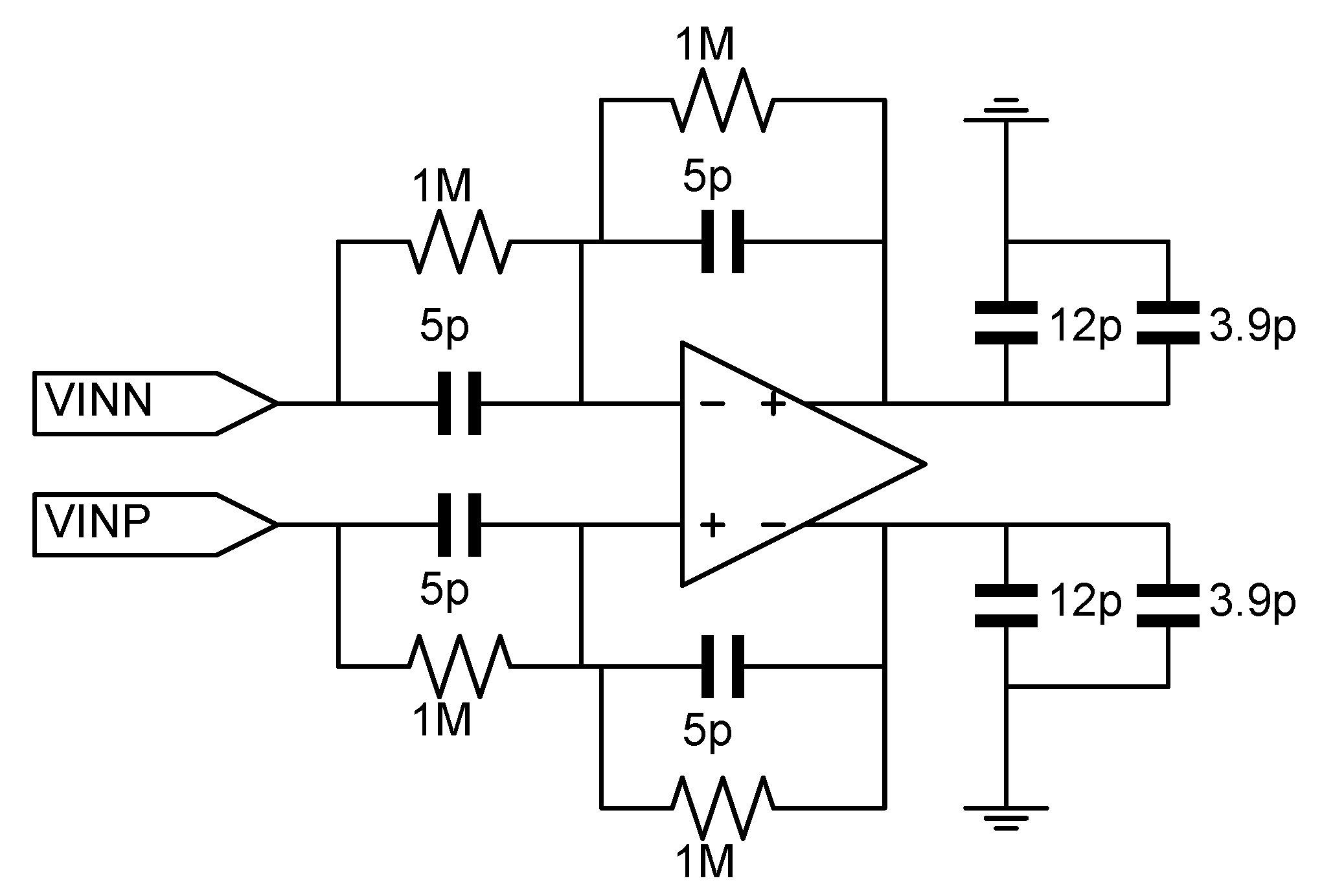

4. Simulation and Experimental Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Singh, T.; Saether, T.; Ytterdal, T. Current-Mode Capacitive Sensor Interface Circuit With Single-Ended to Differential Output Capability. IEEE Trans. Instrum. Meas. 2009, 58, 3914–3920. [Google Scholar] [CrossRef]

- Naderi, M.H.; Prakash, S.; Silva-Martinez, J. Operational Transconductance Amplifier With Class-B Slew-Rate Boosting for Fast High-Performance Switched-Capacitor Circuits. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 3769–3779. [Google Scholar] [CrossRef]

- Sun, J.; Rahkonen, T. Speed-Up Technique by Pre-Charging Load Capacitor in a SC Residue Circuit. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 522–526. [Google Scholar] [CrossRef]

- Petkov, V.P.; Boser, B.E. A fourth-order ΣΔ interface for micromachined inertial sensors. IEEE J. Solid State Circuits 2005, 40, 1602–1609. [Google Scholar] [CrossRef]

- Mojarad, M.; Kamarei, M. Low-voltage high-gain large-capacitive-load amplifiers in 90-nm CMOS technology. AEU Int. J. Electron. Commun. 2015, 69, 666–672. [Google Scholar] [CrossRef]

- Lee, J.; Song, S.; Roh, J. A 103 dB DR Fourth-Order Delta-Sigma Modulator for Sensor Applications. Electronics 2019, 8, 1093. [Google Scholar] [CrossRef]

- Bano, S.; Narejo, G.B.; Ali Shah, S.M.U. Power Efficient Fully Differential Bulk Driven OTA for Portable Biomedical Application. Electronics 2018, 7, 41. [Google Scholar] [CrossRef]

- Assaad, R.; Silva-Martinez, J. Enhancing general performance of folded cascode amplifier by recycling current. Electron. Lett. 2007, 43, 1243. [Google Scholar] [CrossRef]

- Assaad, R.S.; Silva-Martinez, J. The Recycling Folded Cascode: A General Enhancement of the Folded Cascode Amplifier. IEEE J. Solid State Circuits 2009, 44, 2535–2542. [Google Scholar] [CrossRef]

- Yan, Z.; Mak, P.I.; Martins, R.P. Double recycling technique for folded-cascode OTA. Analog Integr. Circuits Signal Process. 2012, 71, 137–141. [Google Scholar] [CrossRef]

- Akbari, M. Single-stage fully recycling folded cascode OTA for switched-capacitor circuits. Electron. Lett. 2015, 51, 977–979. [Google Scholar] [CrossRef]

- Aghaee, T.; Biabanifard, S.; Golmakani, A. Gain boosting of recycling folded cascode OTA using positive feedback and introducing new input path. Analog Integr. Circuits Signal Process. 2017, 90, 237–246. [Google Scholar] [CrossRef]

- Zhao, X.; Zhang, Q.; Wang, Y.; Deng, M. Transconductance and slew rate improvement technique for current recycling folded cascode amplifier. AEU Int. J. Electron. Commun. 2016, 70, 326–330. [Google Scholar] [CrossRef]

- Yin, S.; Sun, Y.; Li, X. Digital 1 V 82 μW Pseudo-Two-Stage Class-AB OTA. Tsinghua Sci. Technol. 2009, 14, 601–605. [Google Scholar] [CrossRef]

- Sansen, W.M.C. Analog Design Essentials; Springer: Berlin/Heidelberg, Germany, 2006. [Google Scholar]

- Li, X.; Wei, Q.; Zhou, B.; Chen, Z.; Zhang, R. Data-driven complementary recycling folded cascode OTA. In Proceedings of the International Conference on Mechanical, Electric and Industrial Engineering, Hangzhou, China, 26–28 May 2018. [Google Scholar]

- Crovetti, P.S. A Digital-Based Analog Differential Circuit. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 3107–3116. [Google Scholar] [CrossRef]

- Shen, J.; Shikata, A.; Fernando, L.D.; Guthrie, N.; Chen, B.; Maddox, M.; Mascarenhas, N.; Kapusta, R.; Coln, M.C.W. A 16-bit 16-MS/s SAR ADC With On-Chip Calibration in 55-nm CMOS. IEEE J. Solid State Circuits 2018, 53, 1149–1160. [Google Scholar] [CrossRef]

- Lopez-Martin, A.; Garde, M.; Ramirez-Angulo, J. Class AB differential difference amplifier for enhanced common-mode feedback. Electron. Lett. 2017, 53, 454–456. [Google Scholar] [CrossRef]

- Hou, B.; Li, C.; Gao, Z.; Wei, Q.; Zhou, B.; Zhang, R. Design, Optimization, and Compensation of a High-Precision Single-Excitation Absolute Capacitance Angular Encoder up to ±4″. IEEE Trans. Ind. Electron. 2019, 66, 8161–8171. [Google Scholar] [CrossRef]

| Parameter | [9] | [10] | [11] | [13] | This Work | |

|---|---|---|---|---|---|---|

| Static | Data-Driven | |||||

| DC supply (V) | 1.8 | 1 | 1.2 | 1 | 5 | 5 |

| Current (A) | 400 | 800 | 483 | 40 | 530 | 1320 |

| Capacitive load (pF) | 5.6 | 10 | 5 | 30 | 18.4 | 18.4 |

| GBW (MHz) | 70.4 | 203.2 | 650 | 10.2 | 17.5 | 83 |

| Phase margin () | 79.8 | 66.2 | 50 | 80.4 | 58.5 | 66.2 |

| DC gain (dB) | 59.7 | 54.5 | 59.1 | 80.3 | 70.2 | 61.0 |

| Average SR (V/s) | 48.1 | 91.6 | 115.2 | 1.78 | 10.2 | 55.5 |

| FoM (MHz·pF/mA) | 985.6 | 2540 | 6279 | 7650 | 607.5 | 1157 |

| FoM ((V/s)pF/mA) | 673.4 | 1145 | 1193 | 1335 | 354.1 | 773.6 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, X.; Hou, B.; Ju, C.; Wei, Q.; Zhou, B.; Zhang, R. A Complementary Recycling Operational Transconductance Amplifier with Data-Driven Enhancement of Transconductance. Electronics 2019, 8, 1457. https://doi.org/10.3390/electronics8121457

Li X, Hou B, Ju C, Wei Q, Zhou B, Zhang R. A Complementary Recycling Operational Transconductance Amplifier with Data-Driven Enhancement of Transconductance. Electronics. 2019; 8(12):1457. https://doi.org/10.3390/electronics8121457

Chicago/Turabian StyleLi, Xiang, Bo Hou, Chunge Ju, Qi Wei, Bin Zhou, and Rong Zhang. 2019. "A Complementary Recycling Operational Transconductance Amplifier with Data-Driven Enhancement of Transconductance" Electronics 8, no. 12: 1457. https://doi.org/10.3390/electronics8121457