1. Induction

Power converters composed of SiC MOSFETs are widely used in home, aerospace, and other fields due to their high operating frequency, high voltage, and high power density. However, due to the high dv/dt and di/dt of SiC MOSFET for high-speed switching, electromagnetic interference (EMI) is generated so that the SiC MOSFET becomes an electromagnetic interference source [

1]. High dv/dt may produce common mode interference signals in power electronic circuits, while higher di/dt can cause higher voltage and current overshoot and oscillation due to parasitic factors in the circuit. The EMI signal can easily affect external sensitive components by radiation or conduction. It is common to reduce conducted interference by adding filters in the conduction path and radiated interference by shielding sensitive components. However, these two methods will take up more PCB space and increase the cost greatly. It is a challenge for engineers to balance the suppression effect of electromagnetic interference and costs [

2]. Therefore, it is an interseting research direction that is suppressing EMI by controlling the fast switching transient [

3]. Changing gate driving current [

4], and using a built-in snubber [

5] all have limited effect for suppressing EMI. Active voltage control (AVC) method is applied to control the slope dv/dt of the output voltage, which is effective to control the switching transients of IGBT to reduce the EMI [

6]. References [

7,

8,

9] introduced how to predict the EMI for the defined edges of signal and what the influence of the defined reference signal is for the transients of IGBT, which provided the possibility to shape the Gaussian switching transients to suppress EMI. The active gate drive (AGD) method is an effective method for suppressing electromagnetic interference from the viewpoint of suppressing electromagnetic interference sources. The AGD method mainly includes three methods: controlling the gate current, controlling the gate voltage, and controlling the gate resistance. References [

10,

11] applied a method of controlling the gate current to control the switching transient. During the turn-off period of SiC MOSFET, a large current is injected into the gate to increase dv/dt to reduce the turn-off time and the turn-off loss is reduced thereby. When the output current drops, the rapidly decreasing gate current reduces the di/dt of the output current and the oscillation of the voltage generated by the inductance and parasitic capacitance is reduced. However, the dv/dt of the output voltage is not adjustable.

Reference [

12] proposes a method of controlling the gate current by closed-loop and adding a delay compensation device to control the gate source turn-off voltage slope dv/dt and current slope di/dt, thereby achieving the trade-off between switching losses and electromagnetic interference. However, this method also has its limitations, because it can only control dv/dt and di/dt when MOSFET is closed. A new method of active gate drive method is proposed Reference [

13], the principle of which is to increase the gate resistance value during the Miller plateau of the gate voltage during the turn-on and turn-off of the SiC MOSFET. This control method can control di/dt during turn-on and dv/dt during turn-off, respectively, and its switching loss is low. This control method can control di/dt during turn-on and dv/dt during turn-off, respectively, and its switching loss is low but this method cannot control dv/dt during turn-on and di/dt during turn-off. The precondition for this method to work properly is to select the correct switching time of gate resistance and the gate voltage cannot have large fluctuations, however, which is difficult to implement in engineering. In [

14], the closed-loop control method is applied and di/dt and dv/dt are measured and then compared with reference signals to get the error. The error is input to the buffer pole through a differential op amp to dynamically adjust the gate voltage. The power semiconductor is turned on by the waveform following the reference signal. However, it is impossible to adjust dv/dt without di/dt restrictions because the same reference and the same gain are used [

4]. All of the above methods of controlling a single dv/dt or di/dt have limited suppression of high frequency noise, and fail to achieve simultaneous control of voltage and current turn-on and turn-off. The results of reference [

1] indicate that any switching waveform can be expressed in the form of convolution that it is get by an ideal square wave signal and a normalized instantaneous function derivative. From a frequency domain perspective, the switching waveform is the product of the square wave signal spectrum and the instantaneous function derivative spectrum. Reference [

15] shows that if the transient function can be derived n times, the high-frequency spectral envelope of the switching waveform will be attenuated by a slope of −20(n + 1) dB/dec. The Gaussian signal has continuous infinitely conductive characteristics, so that the high frequency spectrum of the Gaussian waveform is attenuated faster than the high frequency spectrum of the single slope theoretically. Therefore, in [

2], the convolution waveform of the square wave signal and the Gaussian signal as the reference signal is used, and the switching voltage following the reference voltage by the method of closed-loop active voltage control is realized.

This paper proposed an intelligent control method based on the characteristic that voltage and current are not synchronized during SiC MOSFET switching. The intelligent control method that include a closed-loop circuit to shape the output voltage and an open-loop circuit to control the slope of the output current control the switching voltage and current simultaneously.

The article is organized as follows: Theoretical analysis of voltage reference signals and current control signals is discussed in the

Section 2. An intelligent control method combining closed-loop and open-loop control methods is proposed in the

Section 3. Simulation and experimental verification were performed based on the proposed method in

Section 4 and

Section 5. The conclusion of the experiment is presented in

Section 6.

3. Proposed Intelligent Control Method and Operation Principle

The total circuit diagram used in the proposed intelligent control method for voltage and current is shown in

Figure 3. The circuit consists of an open-loop circuit, a closed-loop circuit and a conventional totem pole drive. The drain-source voltage V

ds of the SiC MOSFET is shaped by the closed-loop circuit in the upper side. When Logic1 outputs 1, switches S1 and S2 are turned on at the same time, the closed-loop circuit starts to work and the drain voltage is fed back by the drain voltage feedback circuit to the positive terminal of the operational amplifier according to the ratio β. The feedback signal is compared with a reference signal generated by the reference signal generator 1, and the gate of the SiC MOSFET is controlled by a totem pole drive circuit. When Logic2 outputs 1, the switches S3 and S4 are turned on, and the current control signal V

i control the gate voltage by the operational amplifier 2. It is necessary to add a resistor R

g to the gate to connect the gate to prevent the SiC MOSFET from operating outside the safe zone. Another function for the R

g is to reduce the oscillation of voltage and current when turned on and off. The value of R

g can be selected according to the values recommended in the datasheet. In this paper, its value is 5 ohms.

The control signal selected is the Gaussian signal in this paper, which is generated by arbitrary waveform generator, M3202A, according to Equation (11). The proposed intelligent control method for voltage and current is based on fact that the current and voltage are not synchronized during MOSFET switching period.

Figure 4 and

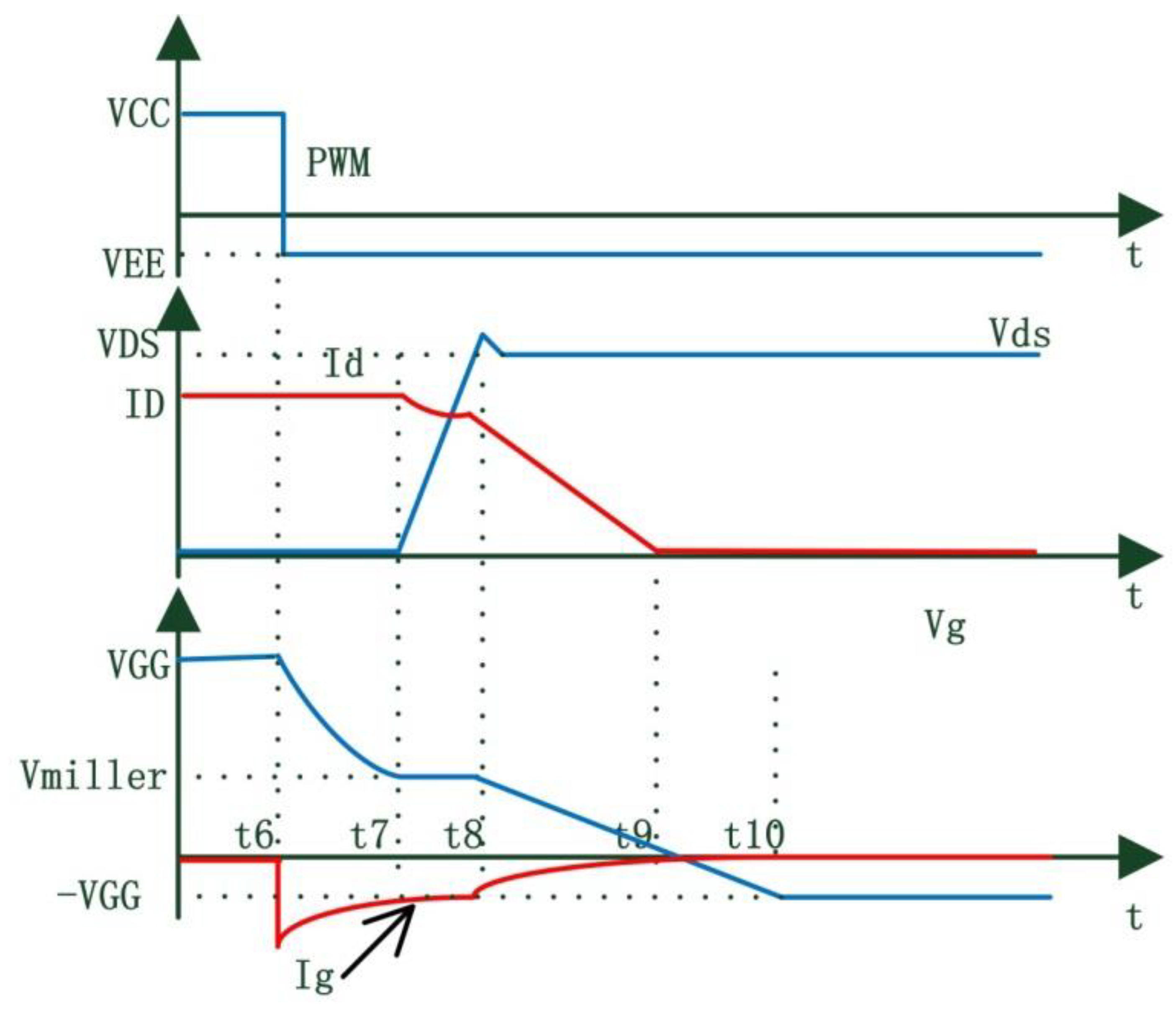

Figure 5 show the time domain signal of the SiC MOSFET during turn-on and turn-off period under hard switching conditions respectively. During the period from t2 to t3, the current I

d rises firstly, and the voltage V

d has a small decrease (in order to simplify the analysis, V

d is regarded as unchanged in this paper). At the time t3, the current rises to the maximum, the voltage begins to drop rapidly, and it drops to the lowest moment. During the period from t7 to t8, the voltage V

d rises rapidly, and the current I

d has a small drop (to simplify the analysis, the I

d does not change during this time period). At t8, the voltage V

d (Drain voltage) gets the maximum value. The current I

d drops rapidly after t8 and the current gets the minimum value t9. Therefore, the drain voltage and current of SiC MOSFET are not synchronized during switching period, which provides a possibility for intelligent control.

Time domain diagram of Gaussian control signals for voltage and current is shown in

Figure 6. S1(t) and S2(t) are rising edges for drain voltage and current respectively and the falling edge signal is symmetric with the rising edge signal. They can be obtained by Equation (11).

Figure 7 and

Figure 8 are the theoretical waveforms of the voltage and current of the proposed intelligent control for turn-on and turn-off, respectively. The switch S3 is turned on and the current control signal is connected to the circuit to control the output current during the 0–t3 period. At time t3, switch S3 is opened and the open-loop circuit stop working. It should be noted that S1 and S2 are closed at time t21 that is before time t3. The delay time for switches S1 and S2 is td1 = t3 − t21. The delay time is caused by MOSFET, operational amplifier, and coupling circuit, which must be taken into account to make the upper part of the circuit achieve the best turn-on transient behavior, when the open-loop stops working. In contrast to the turn-on transient, S1 and S2 are turned on during the t21–t8 period and the voltage closed-loop operates normally. At time t8, S1 and S2 are turned off. However, S3 is turned on at time t

71 that is before time t8. This is because a delay time td2 = t8 − t71 is required to achieve current control after the switch S3 turned-on. The delay time that we concerned to cause by MOSFET, operational amplifier, and coupling circuit guarantees that MOSFET has an optimal turn-off behavior transient. The values of td1 and td2 can be dynamically adjusted to determine the optimum value, according to the switching voltage and current transients of the MOSFET.

4. Circuit Simulation and Discussion

Before the experiment, it is necessary to simulate the proposed circuit, which can improve the experimental guidance and improve the efficiency for the experiment. Pspice is a professional circuit simulation software so it was chosen as the simulation software in this paper. Japan’s ROHM semiconductor’s SCT2160KE SiC MOSFET was selected and the body manufacturer offered the user a 1200-V/22-A Pspice model of SiC MOSFET. In order to simplify the circuit, the standard chopper unit was selected as the control object with inductive load in this paper. Both the voltage reference signal and the current control signal are Gaussian signals and the rising edge time, 1 µs, is equal to the falling edge time. The amplitudes of the voltage reference signal and the current control signal are 5, 4, respectively. According to Equation (11), the values of the Gaussian signal was calculated by the MATLAB and then imports into Pspice. The period is set to 6 µs and the duty cycle is 2/3. It is worth noting that in the simulation, the Gaussian reference signal is compared with the output signal that is fed back according to a certain ratio, rather than compared with the real output signal.

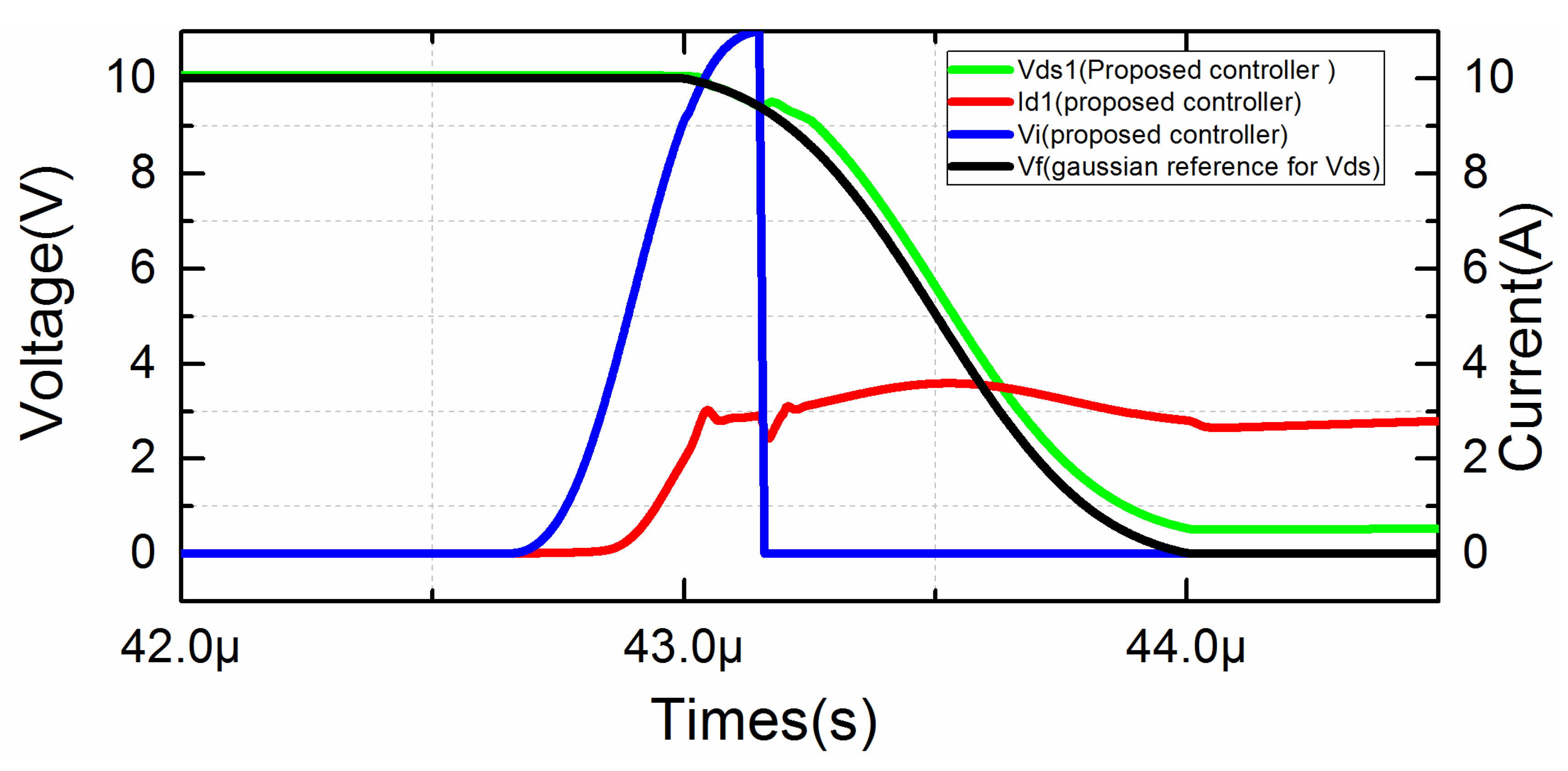

Figure 9 and

Figure 10 are simulation diagram for turn-on and turn-off in time domain respectively. The rising edge time and falling edge time of the voltage reference signal are both 1 µs and the rising edge time and falling edge time of the current control signal are also 1 µs in

Figure 9 and

Figure 10. The rising edge time and the falling edge time of the reference voltage are both 1 us, and the rising edge time rise time and the falling edge time of the current control voltage are both 0.5 µs.

Figure 11 has the same working conditions with

Figure 12 including the voltage reference signal and the current control signal. Comparing

Figure 9,

Figure 10,

Figure 11 and

Figure 12, it can be seen that the proposed method can not only achieve the output voltage following the reference voltage, but also control the rising and falling edge of the drain current. It is worth mentioning that due to the presence of the on-resistance and the sampling resistor, the minimum value of the output voltage V

ds is not zero, and the minimum voltage of V

ds is defined as VD1 in this paper.

where I

D is the on-state current, R

in is on-state resistance and R

3 is the sampling resistor.

It is worth mentioning that the time domain diagrams of the gate-source voltage and gate current of the conventional gate drive method are also shown in

Figure 9 and

Figure 10. This paper compares the spectrum of the obtained drain voltage and drain current obtained by the conventional gate driving method and the proposed method shown in

Figure 13 and

Figure 14.

Figure 13 shows the spectrum of the drain voltage obtained by the conventional method and the proposed method. It can be seen from

Figure 13 that the envelope of the spectrum obtained by the proposed method is lower than the conventional gate driving method in the frequency range of 100 kHz to 70 MHz. However, the proposed method has obvious bumps in the spectrum around 80 M, which may be caused by fluctuations of the drain voltage caused by voltage switching.

Figure 14 compared the spectrum of the drain current obtained by the proposed method with the drain current obtained by the conventional method. It can be seen from

Figure 14 that when the frequency is less than 200 kHz, their spectral envelopes are basically coincident. When the frequency is higher than 200 kHz, the envelope obtained by the proposed method has a significant attenuation compared with the classical gate driving method and the attenuation is about 30 dB. Therefore, the effect of the proposed control method for suppressing EMI is very obvious.

5. Experiment Results of Proposed Method and Classic Method and Discussion

Similar to the simulation, the chopper unit with inductive load was also selected as the experimental circuit for simplicity. The op amp TH3091 that has wide Supply Range ±5 v to ±15 v, low voltage noise 2 nV

and high band 200 MHz was used in this paper. The specific parameters of the proposed circuit and the classical gate drive circuit are listed in

Table 1. The time domain data of the Gaussian signal is obtained by MATLAB and imported into the M3202A that is an arbitrary signal generator. The hardware configuration of the proposed intelligent control method is shown in

Table 1. In the first experiment, proposed controller 1 was used, assuming that the rising edge time t

off = 1 µs, the falling edge time t

fall = 1 µs, cycle T = 6 µs, duty cycle D = 1/3 for the reference signal V

f and the rising edge time t

r2 = 1 µs, the falling edge time t

f2 = 1 µs for the control voltage V

i. The time domain relationship between voltage reference signal and current control signal is shown in

Figure 6. In the second experiment, the proposed controller 2 was used, in which the setting of the voltage reference signal V

f was the same as the first experiment, but V

i, t

off = 0.5 µs, t

fall = 0.5 µs, is different with the first experiment.

In

Figure 15, the drain-source voltage V

ds for the blue track of the controller 1 and the red track of controller 2 is delayed by 0.1 µs compared with the reference voltage at turn-on. At turn-off the drain-source voltage V

ds for the blue track of the controller 1 and the red track of controller 2 follows the reference voltage well. However, for the blue trajectory and the red trajectory, there is a significant fluctuation in the top corner region at turn-on and turn-off, which may be caused by fluctuations in current for switching, parasitic inductance, and sampling resistor parasitic capacitance.

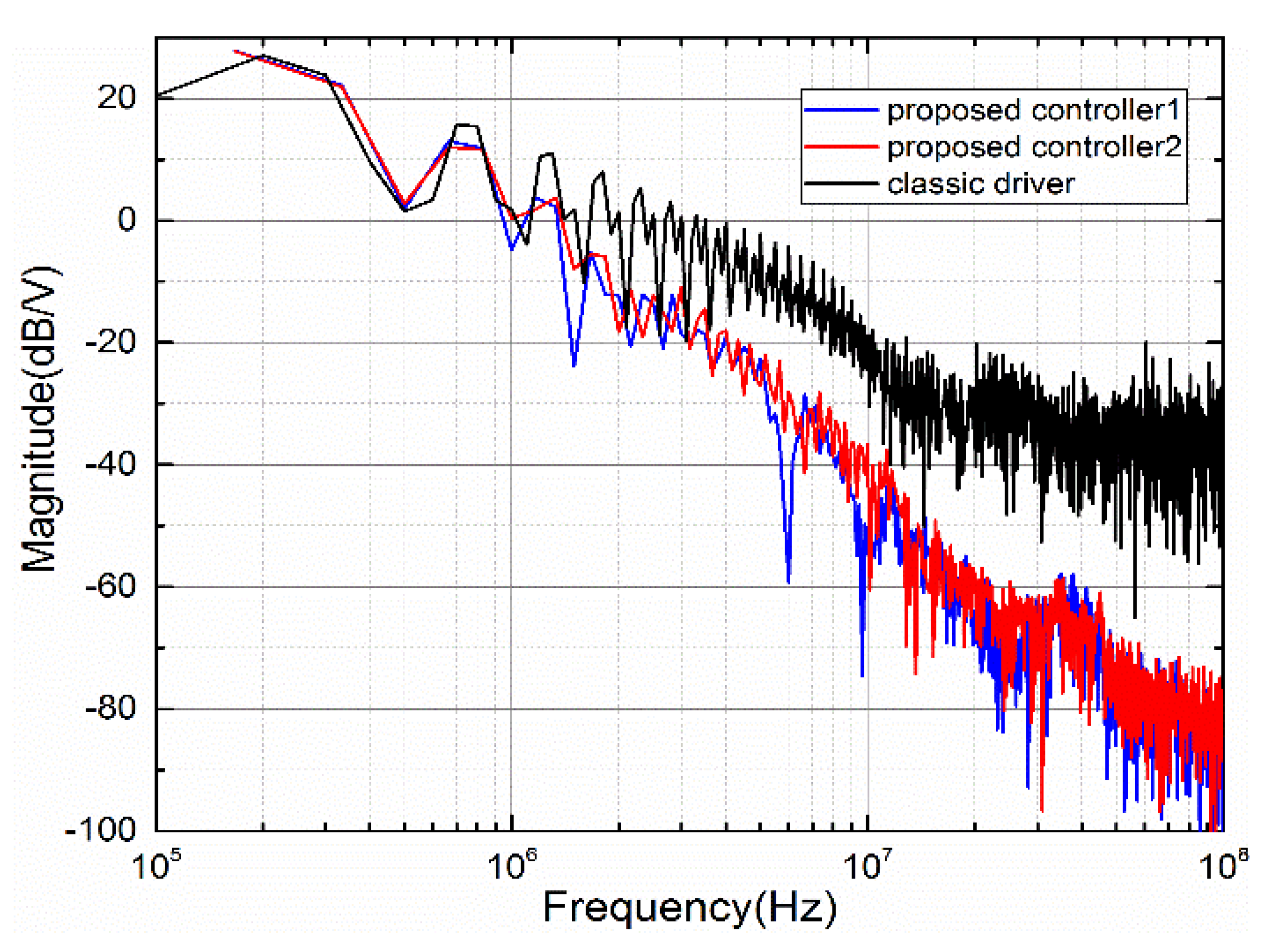

The classic gate driver is also used in the chopper for comparison, in which the hardware configuration is shown in

Table 1 and the drive signal is the ideal PWM, the period 6 µs, duty cycle 1/3. The spectrum comparison of the drain-source voltage is shown in

Figure 16. As can be seen from

Figure 16, the envelopes of the three spectra in the low frequency region are almost coincident. The envelope of the classic gate drive in the 10

6–10

7 Hz range is 20 dB higher than the envelope of the proposed control 1 and control 2. The envelope of the classic gate drive in the range of 10

7–10

8 Hz is 40 dB higher than the proposed envelope of control 1 and control 2. In the analyzed frequency range of 10

5–10

8 Hz, the spectral envelopes of the proposed control 1 and control 2 are almost coincident, which shows that the current control signal V

i has little effect on the drain-source noise when the reference voltage V

f is the same in the proposed circuit.

In

Figure 17, the drain current I

d of proposed controller 1 has lower slope di/dt of 2.94 A/us than controller 2 of 6.46 A/us so that the controller 1 reduces the current overshoot 40% at turn-off. At turn-on, the switching speed di/dt of controller 1 is 4.58 A/us, and the di/dt of controller 2 is 6.87 A/us. Accordingly, the controller 1 reduces the current overshoot about 50%.

The spectrum comparison of the drain-source current I

d is shown in

Figure 18. It can be seen from the

Figure 18 that before 3 × 10

6 Hz, the spectrum of the classical gate driver, the proposed control 1 and control 2 are almost coincident. When the frequency is greater than 3 × 10

6 Hz, the spectrum envelope of the classical gate driver is 10–40 dB higher than the proposed controller 1 and controller 2. In the frequency range of 10

7–5 × 10

7 Hz, control 1 is reduced by 5–10 dB compared with controller 2, since the current slope di/dt of controller 1 is smaller than controller 2.

Switching losses also has been studied in this paper. The switching power of the three experiments are compared in

Figure 19. As can be seen from

Figure 19, there are mainly two peaks in one cycle. The first power peak is generated when the SiC MOSFET is turned on, and the second power peak is generated when the SiC MOSFET is turned off. The area enclosed by the power curve and the time axis represents the energy of the loss, and the loss at turn-on is higher than it at turn-off significantly. The typical gate driver switching losses are smaller than the proposed controller 1 and controller 2.

Figure 20 shows the curve of switching loss over time in one cycle. It can be seen in

Figure 20 that the proposed controller’s switching losses are approximately 120% higher than the classic gate drivers at the end of a cycle, since the switching time of the classic gate drive is much shorter than the proposed controller 1 and controller 2. The switching loss of the controller 2 is 6.4% lower than the controller 1, because the current rise and fall time of the controller 2 is shorter than the controller 1. It should be noted that in actual application, we can adjust the parameters to adjust the loss. According to [

20], we know that there is compromise between EMI and switching losses. Therefore, we can reduce the switching loss by reducing the rising and falling edge times of the reference voltage within the acceptable EMI range.