Electric Double Layer Field-Effect Transistors Using Two-Dimensional (2D) Layers of Copper Indium Selenide (CuIn7Se11)

Abstract

:1. Introduction

2. Materials and Methods

3. Results and Discussion

3.1. Electronic Transport with Dielectric Gate

3.2. Electronic Transport with an Electric Double Layer Gate

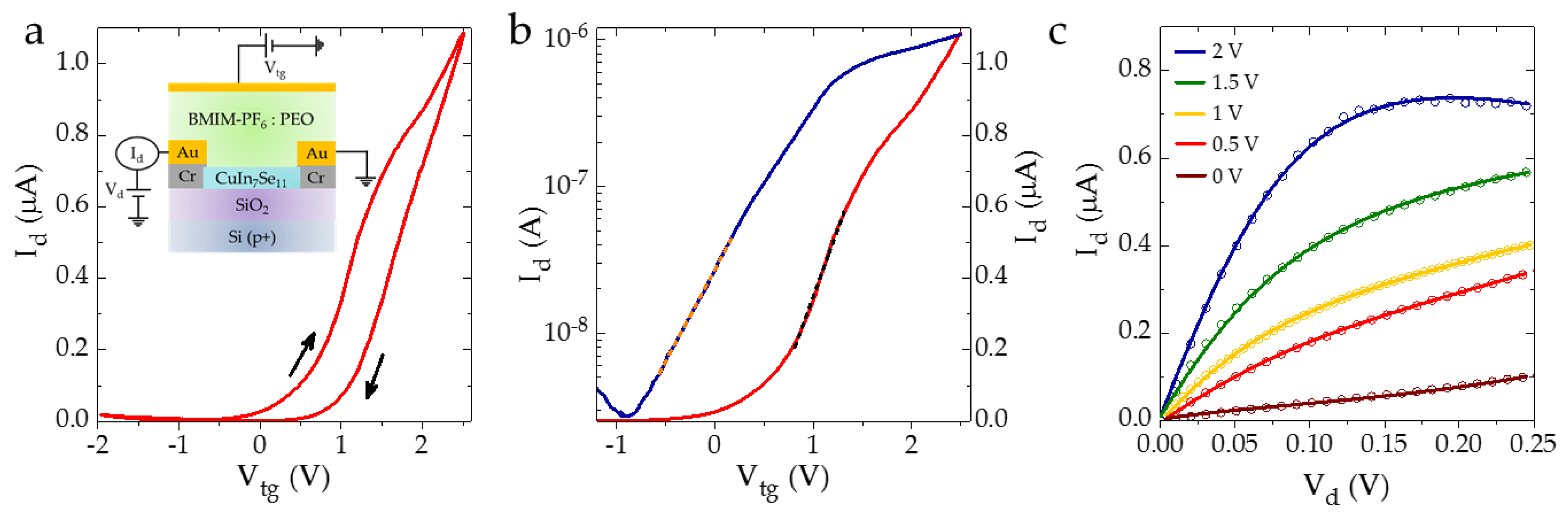

3.3. Electronic Transport with Ion-Gel Gate

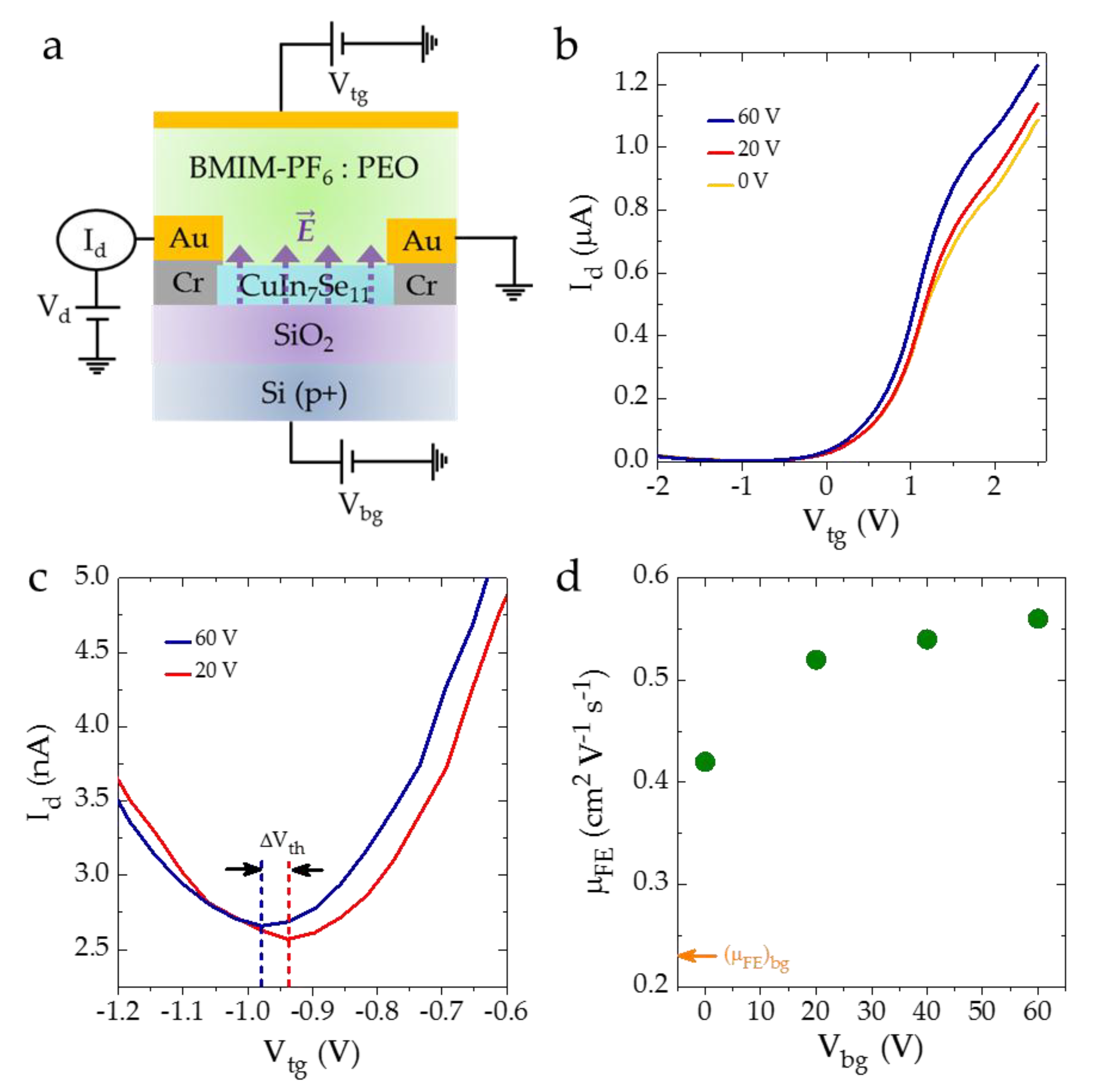

3.4. Electronic Transport with a Dual Gate

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 2011, 6, 147–150. [Google Scholar] [CrossRef] [PubMed]

- Miró, P.; Audiffred, M.; Heine, T. An atlas of two-dimensional materials. Chem. Soc. Rev. 2014, 43, 6537–6554. [Google Scholar] [CrossRef] [PubMed]

- Wasala, M.; Sirikumara, H.I.; Raj Sapkota, Y.; Hofer, S.; Mazumdar, D.; Jayasekera, T.; Talapatra, S. Recent advances in investigations of the electronic and optoelectronic properties of group III, IV, and V selenide based binary layered compounds. J. Mater. Chem. C 2017, 5, 11214–11225. [Google Scholar] [CrossRef]

- Wang, B.; Huang, W.; Chi, L.; Al-Hashimi, M.; Marks, T.J.; Facchetti, A. High-k Gate Dielectrics for Emerging Flexible and Stretchable Electronics. Chem. Rev. 2018, 118, 5690–5754. [Google Scholar] [CrossRef] [PubMed]

- Ye, M.; Zhang, D.; Yap, Y.K. Recent Advances in Electronic and Optoelectronic Devices Based on Two-Dimensional Transition Metal Dichalcogenides. Electronics 2017, 6, 43. [Google Scholar] [Green Version]

- Du, H.; Lin, X.; Xu, Z.; Chu, D. Electric double-layer transistors: A review of recent progress. J. Mater. Sci. 2015, 50, 5641–5673. [Google Scholar] [CrossRef]

- Wang, D.; Noël, V.; Piro, B. Electrolytic Gated Organic Field-Effect Transistors for Application in Biosensors—A Review. Electronics 2016, 5, 9. [Google Scholar] [CrossRef]

- Fujimoto, T.; Awaga, K. Electric-double-layer field-effect transistors with ionic liquids. Phys. Chem. Chem. Phys. 2013, 15, 8983–9006. [Google Scholar] [CrossRef]

- Armand, M.; Endres, F.; MacFarlane, D.R.; Ohno, H.; Scrosati, B. Ionic-liquid materials for the electrochemical challenges of the future. Nat. Mater. 2009, 8, 621. [Google Scholar] [CrossRef]

- Watanabe, M.; Thomas, M.L.; Zhang, S.; Ueno, K.; Yasuda, T.; Dokko, K. Application of Ionic Liquids to Energy Storage and Conversion Materials and Devices. Chem. Rev. 2017, 117, 7190–7239. [Google Scholar] [CrossRef] [Green Version]

- Bisri, S.Z.; Shimizu, S.; Nakano, M.; Iwasa, Y. Endeavor of Iontronics: From Fundamentals to Applications of Ion-Controlled Electronics. Adv. Mater. 2017, 29, 1607054. [Google Scholar] [CrossRef] [PubMed]

- Huffstutler, J.D.; Wasala, M.; Richie, J.; Barron, J.; Winchester, A.; Ghosh, S.; Yang, C.; Xu, W.; Song, L.; Kar, S.; et al. High Performance Graphene-Based Electrochemical Double Layer Capacitors Using 1-Butyl-1-methylpyrrolidinium tris (pentafluoroethyl) trifluorophosphate Ionic Liquid as an Electrolyte. Electronics 2018, 7, 229. [Google Scholar] [CrossRef]

- Ye, J.T.; Inoue, S.; Kobayashi, K.; Kasahara, Y.; Yuan, H.T.; Shimotani, H.; Iwasa, Y. Liquid-gated interface superconductivity on an atomically flat film. Nat. Mater. 2009, 9, 125–128. [Google Scholar] [CrossRef] [PubMed]

- Saito, Y.; Iwasa, Y. Ambipolar Insulator-to-Metal Transition in Black Phosphorus by Ionic-Liquid Gating. ACS Nano 2015, 9, 3192–3198. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Yamada, Y.; Ueno, K.; Fukumura, T.; Yuan, H.T.; Shimotani, H.; Iwasa, Y.; Gu, L.; Tsukimoto, S.; Ikuhara, Y.; Kawasaki, M. Electrically Induced Ferromagnetism at Room Temperature in Cobalt-Doped Titanium Dioxide. Science 2011, 332, 1065–1067. [Google Scholar] [CrossRef] [PubMed]

- Perera, M.M.; Lin, M.-W.; Chuang, H.-J.; Chamlagain, B.P.; Wang, C.; Tan, X.; Cheng, M.M.-C.; Tománek, D.; Zhou, Z. Improved Carrier Mobility in Few-Layer MoS2 Field-Effect Transistors with Ionic-Liquid Gating. ACS Nano 2013, 7, 4449–4458. [Google Scholar] [CrossRef] [PubMed]

- Jo, S.; Costanzo, D.; Berger, H.; Morpurgo, A.F. Electrostatically Induced Superconductivity at the Surface of WS2. Nano Lett. 2015, 15, 1197–1202. [Google Scholar] [CrossRef]

- Lu, J.M.; Zheliuk, O.; Leermakers, I.; Yuan, N.F.Q.; Zeitler, U.; Law, K.T.; Ye, J.T. Evidence for two-dimensional Ising superconductivity in gated MoS2. Science 2015, 350, 1353–1357. [Google Scholar] [CrossRef]

- Lu, J.; Zheliuk, O.; Chen, Q.; Leermakers, I.; Hussey, N.E.; Zeitler, U.; Ye, J. Full superconducting dome of strong Ising protection in gated monolayer WS2. Proc. Natl. Acad. Sci. USA 2018, 115, 3551–3556. [Google Scholar] [CrossRef]

- Saito, Y.; Nojima, T.; Iwasa, Y. Highly crystalline 2D superconductors. Nat. Rev. Mater. 2016, 2, 16094. [Google Scholar] [CrossRef] [Green Version]

- Schwierz, F.; Pezoldt, J.; Granzner, R. Two-dimensional materials and their prospects in transistor electronics. Nanoscale 2015, 7, 8261–8283. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Li, S.-L.; Tsukagoshi, K.; Orgiu, E.; Samorì, P. Charge transport and mobility engineering in two-dimensional transition metal chalcogenide semiconductors. Chem. Soc. Rev. 2016, 45, 118–151. [Google Scholar] [CrossRef] [PubMed]

- Ghosh, S.; Wasala, M.; Pradhan, N.R.; Rhodes, D.; Patil, P.D.; Fralaide, M.; Xin, Y.; McGill, S.A.; Balicas, L.; Talapatra, S. Low temperature photoconductivity of few layer p-type tungsten diselenide (WSe2) field-effect transistors (FETs). Nanotechnology 2018, 29, 484002. [Google Scholar] [CrossRef] [PubMed]

- Lin, Z.; McCreary, A.; Briggs, N.; Subramanian, S.; Zhang, K.; Sun, Y.; Li, X.; Borys, N.J.; Yuan, H.; Fullerton-Shirey, S.K.; et al. 2D materials advances: From large scale synthesis and controlled heterostructures to improved characterization techniques, defects and applications. 2D Mater. 2016, 3, 042001. [Google Scholar] [CrossRef]

- Wang, L.; Hu, P.; Long, Y.; Liu, Z.; He, X. Recent advances in ternary two-dimensional materials: Synthesis, properties and applications. J. Mater. Chem. A 2017, 5, 22855–22876. [Google Scholar] [CrossRef]

- Stanbery, B.J. Copper Indium Selenides and Related Materials for Photovoltaic Devices. Crit. Rev. Solid State Mater. Sci. 2002, 27, 73–117. [Google Scholar] [CrossRef]

- Lei, S.; Sobhani, A.; Wen, F.; George, A.; Wang, Q.; Huang, Y.; Dong, P.; Li, B.; Najmaei, S.; Bellah, J.; et al. Ternary CuIn7Se11: Towards Ultra-Thin Layered Photodetectors and Photovoltaic Devices. Adv. Mater. 2014, 26, 7666–7672. [Google Scholar] [CrossRef] [PubMed]

- Ghosh, S.; Patil, P.D.; Wasala, M.; Lei, S.; Nolander, A.; Sivakumar, P.; Vajtai, R.; Ajayan, P.; Talapatra, S. Fast photoresponse and high detectivity in copper indium selenide (CuIn7Se11) phototransistors. 2D Mater. 2017, 5, 015001. [Google Scholar] [CrossRef]

- Fujimoto, T.; Matsushita, M.M.; Awaga, K. Ionic-Liquid Component Dependence of Carrier Injection and Mobility for Electric-Double-Layer Organic Thin-Film Transistors. J. Phys. Chem. C 2012, 116, 5240–5245. [Google Scholar] [CrossRef]

- Das, S.; Chen, H.-Y.; Penumatcha, A.V.; Appenzeller, J. High Performance Multilayer MoS2 Transistors with Scandium Contacts. Nano Lett. 2013, 13, 100–105. [Google Scholar] [CrossRef]

- Lin, M.-W.; Kravchenko, I.I.; Fowlkes, J.; Li, X.; Puretzky, A.A.; Rouleau, C.M.; Geohegan, D.B.; Xiao, K. Thickness-dependent charge transport in few-layer MoS2 field-effect transistors. Nanotechnology 2016, 27, 165203. [Google Scholar] [CrossRef] [PubMed]

- Li, S.-L.; Wakabayashi, K.; Xu, Y.; Nakaharai, S.; Komatsu, K.; Li, W.-W.; Lin, Y.-F.; Aparecido-Ferreira, A.; Tsukagoshi, K. Thickness-Dependent Interfacial Coulomb Scattering in Atomically Thin Field-Effect Transistors. Nano Lett. 2013, 13, 3546–3552. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Island, J.O.; Blanter, S.I.; Buscema, M.; van der Zant, H.S.J.; Castellanos-Gomez, A. Gate Controlled Photocurrent Generation Mechanisms in High-Gain In2Se3 Phototransistors. Nano Lett. 2015, 15, 7853–7858. [Google Scholar] [CrossRef] [PubMed]

- Zhou, J.; Zeng, Q.; Lv, D.; Sun, L.; Niu, L.; Fu, W.; Liu, F.; Shen, Z.; Jin, C.; Liu, Z. Controlled Synthesis of High-Quality Monolayered α-In2Se3 via Physical Vapor Deposition. Nano Lett. 2015, 15, 6400–6405. [Google Scholar] [CrossRef] [PubMed]

- Tamalampudi, S.R.; Lu, Y.-Y.; Kumar, U.R.; Sankar, R.; Liao, C.-D.; Moorthy, B.K.; Cheng, C.-H.; Chou, F.C.; Chen, Y.-T. High Performance and Bendable Few-Layered InSe Photodetectors with Broad Spectral Response. Nano Lett. 2014, 14, 2800–2806. [Google Scholar] [CrossRef] [PubMed]

- Feng, W.; Wu, J.-B.; Li, X.; Zheng, W.; Zhou, X.; Xiao, K.; Cao, W.; Yang, B.; Idrobo, J.-C.; Basile, L.; et al. Ultrahigh photo-responsivity and detectivity in multilayer InSe nanosheets phototransistors with broadband response. J. Mater. Chem. C 2015, 3, 7022–7028. [Google Scholar] [CrossRef]

- Yang, S.; Yue, Q.; Cai, H.; Wu, K.; Jiang, C.; Tongay, S. Highly efficient gas molecule-tunable few-layer GaSe phototransistors. J. Mater. Chem. C 2016, 4, 248–253. [Google Scholar] [CrossRef]

- Kalb, W.L.; Batlogg, B. Calculating the trap density of states in organic field-effect transistors from experiment: A comparison of different methods. Phys. Rev. B 2010, 81, 035327. [Google Scholar] [CrossRef]

- Zebrev, G.I.; Melnik, E.V.; Tselykovskiy, A.A. Interface Traps in Graphene Field-Effect Devices: Extraction Methods and Influence on Characteristics. In Graphene Science Handbook: Size-Dependent Properties; Aliofkhazraei, M., Ali, N., Milne, W.I., Ozkan, C., Mitura, S.S., Gervasoni, J.L., Eds.; CRC Press: Boca Raton, FL, USA, 2016; Volume 5, p. 14. [Google Scholar]

- Late, D.J.; Liu, B.; Matte, H.R.; Dravid, V.P.; Rao, C.N. Hysteresis in Single-Layer MoS2 Field Effect Transistors. ACS Nano 2012, 6, 5635–5641. [Google Scholar] [CrossRef]

- Zhang, Y.; Ye, J.; Matsuhashi, Y.; Iwasa, Y. Ambipolar MoS2 Thin Flake Transistors. Nano Lett. 2012, 12, 1136–1140. [Google Scholar] [CrossRef]

- Yuan, H.; Shimotani, H.; Tsukazaki, A.; Ohtomo, A.; Kawasaki, M.; Iwasa, Y. High-Density Carrier Accumulation in ZnO Field-Effect Transistors Gated by Electric Double Layers of Ionic Liquids. Adv. Funct. Mater. 2009, 19, 1046–1053. [Google Scholar] [CrossRef]

- Zhou, Y.; Ramanathan, S. Relaxation dynamics of ionic liquid—VO2 interfaces and influence in electric double-layer transistors. J. Appl. Phys. 2012, 111, 084508. [Google Scholar] [CrossRef]

- Singh, M.; Manoli, K.; Tiwari, A.; Ligonzo, T.; Di Franco, C.; Cioffi, N.; Palazzo, G.; Scamarcio, G.; Torsi, L. The double layer capacitance of ionic liquids for electrolyte gating of ZnO thin film transistors and effect of gate electrodes. J. Mater. Chem. C 2017, 5, 3509–3518. [Google Scholar] [CrossRef]

- Almora, O.; Aranda, C.; Mas-Marzá, E.; Garcia-Belmonte, G. On Mott–Schottky analysis interpretation of capacitance measurements in organometal perovskite solar cells. Appl. Phys. Lett. 2016, 109, 173903. [Google Scholar] [CrossRef]

- Lockett, V.; Horne, M.; Sedev, R.; Rodopoulos, T.; Ralston, J. Differential capacitance of the double layer at the electrode/ionic liquids interface. Phys. Chem. Chem. Phys. 2010, 12, 12499–12512. [Google Scholar] [CrossRef] [PubMed]

- Sze, S.M.; Ng, K.K. Physics of Semiconductor Devices; John Wiley & Sons: Hoboken, NJ, USA, 2007. [Google Scholar]

- Kim, S.; Nah, J.; Jo, I.; Shahrjerdi, D.; Colombo, L.; Yao, Z.; Tutuc, E.; Banerjee, S.K. Realization of a high mobility dual-gated graphene field-effect transistor with Al2O3 dielectric. Appl. Phys. Lett. 2009, 94, 062107. [Google Scholar] [CrossRef]

- Hwang, B.-W.; Yeom, H.-I.; Kim, D.; Kim, C.-K.; Lee, D.; Choi, Y.-K. Enhanced transconductance in a double-gate graphene field-effect transistor. Solid-State Electron. 2018, 141, 65–68. [Google Scholar] [CrossRef]

- Zhu, W.; Low, T.; Farmer, D.B.; Jenkins, K.; Ek, B.; Avouris, P. Effect of dual gate control on the alternating current performance of graphene radio frequency device. J. Appl. Phys. 2013, 114, 044307. [Google Scholar] [CrossRef]

- Lee, G.-H.; Cui, X.; Kim, Y.D.; Arefe, G.; Zhang, X.; Lee, C.-H.; Ye, F.; Watanabe, K.; Taniguchi, T.; Kim, P.; et al. Highly Stable, Dual-Gated MoS2 Transistors Encapsulated by Hexagonal Boron Nitride with Gate-Controllable Contact, Resistance, and Threshold Voltage. ACS Nano 2015, 9, 7019–7026. [Google Scholar] [CrossRef]

- Miyazaki, H.; Tsukagoshi, K.; Kanda, A.; Otani, M.; Okada, S. Influence of Disorder on Conductance in Bilayer Graphene under Perpendicular Electric Field. Nano Lett. 2010, 10, 3888–3892. [Google Scholar] [CrossRef] [Green Version]

| Device # | μFE (cm2 V−1 s−1) | SS (V/dec) | on/off ratio | |||

|---|---|---|---|---|---|---|

| BG | TG | BG | TG | BG | TG | |

| Device I | 4.04 | 21.84 | 9.6 | 0.30 | ~103 | ~104 |

| Device II | 2.66 | 17.73 | 29.8 | 0.19 | ~102 | ~104 |

| † Device III | 0.23 | 0.42 | 107 | 0.81 | ~100 | ~103 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Patil, P.D.; Ghosh, S.; Wasala, M.; Lei, S.; Vajtai, R.; Ajayan, P.M.; Talapatra, S. Electric Double Layer Field-Effect Transistors Using Two-Dimensional (2D) Layers of Copper Indium Selenide (CuIn7Se11). Electronics 2019, 8, 645. https://doi.org/10.3390/electronics8060645

Patil PD, Ghosh S, Wasala M, Lei S, Vajtai R, Ajayan PM, Talapatra S. Electric Double Layer Field-Effect Transistors Using Two-Dimensional (2D) Layers of Copper Indium Selenide (CuIn7Se11). Electronics. 2019; 8(6):645. https://doi.org/10.3390/electronics8060645

Chicago/Turabian StylePatil, Prasanna D., Sujoy Ghosh, Milinda Wasala, Sidong Lei, Robert Vajtai, Pulickel M. Ajayan, and Saikat Talapatra. 2019. "Electric Double Layer Field-Effect Transistors Using Two-Dimensional (2D) Layers of Copper Indium Selenide (CuIn7Se11)" Electronics 8, no. 6: 645. https://doi.org/10.3390/electronics8060645