High-Voltage Temperature Humidity Bias Test (HV-THB): Overview of Current Test Methodologies and Reliability Performances

Abstract

:1. Introduction

Current Normatives

2. Comparison of Test Methodologies

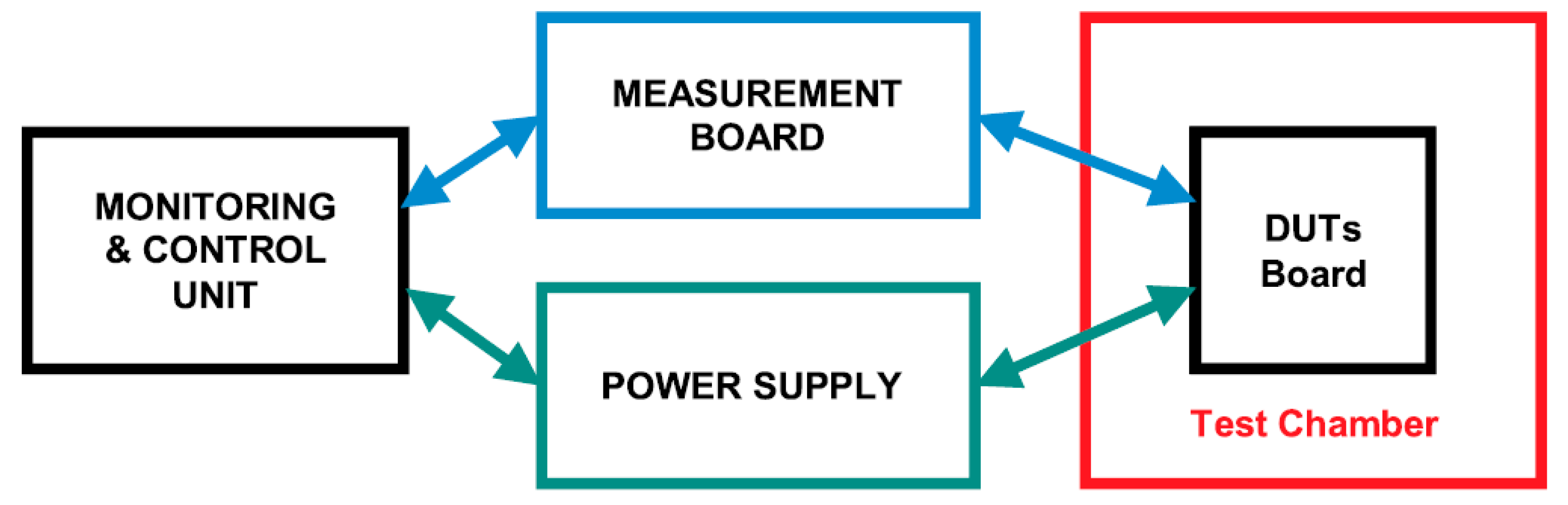

2.1. Test Setup and Procedures

2.2. Leakage Current Monitoring

2.3. Intermediate Testing and Electrical Degradation

2.4. Accelerated Test Models

3. An Overview of the Failure Modes

3.1. The Corrosion Cell

3.2. Aluminum Corrosion

3.3. Electrochemical Migration (ECM)

3.4. Device Failure Analysis

4. Materials and Accelerated Testing Performances

4.1. Passivation and Termination Materials

4.2. Silicon Nitride as a Passivation Material

4.3. Silicon Carbide Devices

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Lopes, J.A.P.; Madureira, A.G.; Matos, M.; Bessa, R.J.; Monteiro, V.; Afonso, J.L.; Santos, S.F.; Catalão, J.P.S.; Antunes, C.H.; Magalhães, P. The future of power systems: Challenges, trends, and upcoming paradigms. WIREs Energy Environ. 2020, 9, 9. [Google Scholar] [CrossRef]

- Kaminski, N.; Rugen, S.; Hoffmann, F. Gaining Confidence—A Review of Silicon Carbide’s Reliability Status. In Proceedings of the 2019 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 31 March–4 April 2019; pp. 1–7. [Google Scholar]

- Lutz, J.; Schlangenotto, H.; Scheuermann, U.; De Doncker, R. Semiconductor Power Devices; Springer International Publishing: Cham, Switzerland, 2018; ISBN 978-3-319-70916-1. [Google Scholar]

- Zorn, C.; Piton, M.; Kaminski, N. Impact of humidity on railway converters. In Proceedings of the PCIM Europe 2017, Nuremberg, Germany, 16–18 May 2017. [Google Scholar] [CrossRef]

- Papadopoulos, B.C.; Rahimo, M.; Corvasce, C.; Schneider, D.; Jabrany, R.; Shin, N.; Ruef, K.; Widmer, C.; Pâques, G. High Humidity Robustness of ABB’s IGBTs and Diodes. 2017. Available online: https://search.abb.com/library/Download.aspx?DocumentID=bp-05-2017&LanguageCode=en&DocumentPartId=&Action=Launch (accessed on 9 November 2020).

- Busca, R.; Cimmino, D.; Ferrero, S.; Scaltrito, L.; Pirri, C.F.; Richieri, G.; Carta, R. Multilayer film passivation for enhanced reliability of power semiconductor devices. J. Vac. Sci. Technol. B 2020, 38, 022206. [Google Scholar] [CrossRef]

- Zorn, C.; Kaminski, N. Temperature humidity bias (THB) testing on IGBT modules at high bias levels. In Proceedings of the CIPS 2014—8th International Conference on Integrated Power Electronics Systems, Nuremberg, Germany, 25–27 February 2014. [Google Scholar]

- Cimmino, D.; Busca, R.; Ferrero, S.; Pirri, F.; Richieri, G.; Carta, R. High Voltage Temperature Humidity Bias Test (THB) customized system and methodologies for reliability assessment of power semiconductor devices. Microelectron. Reliab. 2019, 100–101, 113319. [Google Scholar] [CrossRef]

- Zorn, C.; Kaminski, N. Acceleration of temperature humidity bias (THB) testing on IGBT modules by high bias levels. In Proceedings of the 2015 IEEE 27th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Hong Kong, China, 10–14 May 2015; pp. 385–388. [Google Scholar]

- Papadopoulos, C.; Boksteen, B.; Paques, G.; Corvasce, C. Humidity Robustness of IGBT Guard Ring Termination. In Proceedings of the PCIM Europe 2019, International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 7–9 May 2019; pp. 1–8. [Google Scholar]

- Automotive Electronic Council. Stress Test Qualification for Automotive Grade Discrete Semiconductors. AEC-Q101-Rev-D1, Technical Report. 2013. Available online: http://www.aecouncil.com/Documents/AEC_Q101_Rev_D1_Base_Document.pdf (accessed on 9 November 2020).

- European Center for Power Electronics. ECPE Guideline AQG 324—Qualification of Power Modules for Use in Power Electronic Converter Units in Motor Vehicles. 2019. Available online: https://www.ecpe.org/index.php?eID=dumpFile&t=f&f=23930&token=ab9f61d08229d223b108cb44f00aa4db948ad4e4 (accessed on 9 November 2020).

- International Electrotechnical Commission. IEC 60068-2-67:1995+AMD1:2019—Environmental Testing—Part 2-67: Tests—Test Cy: Damp Heat, Steady State, Accelerated Test Primarily Intended for Components. 2019, p. 40. Available online: https://webstore.iec.ch/publication/60223 (accessed on 9 November 2020).

- International Electrotechnical Commission. IEC 60749-5—Semiconductor Devices—Mechanical and Climatic Test Methods—Part 5: Steady-State Temperature Humidity Bias Life Test. 2017, p. 18. Available online: https://webstore.iec.ch/publication/27654 (accessed on 9 November 2020).

- Stroehle, D. Influence of the Chip Temperature on the Moisture Induced Failure Rate of Plastic Encapsulated Devices. IEEE Trans. Components Hybrids Manuf. Technol. 1983, 6, 537–543. [Google Scholar] [CrossRef]

- Jormanainen, J.; Mengotti, E.; Batista, T.; Bianda, E.; Baumann, D.; Friedli, T.; Heineman, A.; Vulli, A.; Ingman, J. High humidity, high temperature and high voltage reverse bias—A relevant test for industrial applications. In Proceedings of the PCIM Europe 2018, Nuremberg, Germany, 5–7 June 2018. [Google Scholar]

- Kremp, S.; Schilling, O. Humidity robustness for high voltage power modules: Limiting mechanisms and improvement of lifetime. Microelectron. Reliab. 2018, 88–90, 447–452. [Google Scholar] [CrossRef]

- Hanf, M.; Zorn, C.; Kaminski, N.; Domeij, M.; Allerstam, F.; Buon, B.; Franchi, J.; Neyer, T. H3TRB test on 1.2 kv sic mosfets. In Proceedings of the PCIM Europe 2018, Nuremberg, Germany, 5–7 June 2018; pp. 1506–1511. [Google Scholar]

- Deng, H.T.; Meng, J.L.; Wang, D.B.; Zhang, W. Breakdown voltage impact on lifetime of 1200V IGBT modules under H3TRB-HVDC testing. In Proceedings of the International Symposium on the Physical and Failure Analysis of Integrated Circuits, IPFA, Hangzhou, China, 2–5 July 2019; pp. 1–4. [Google Scholar]

- Kaminski, N.; Zorn, C. Temperature-humidity-bias testing on insulated-gate bipolartransistor modules—Failure modes and acceleration due to high voltage. IET Power Electron. 2015, 8, 2329–2335. [Google Scholar] [CrossRef]

- Papadopoulos, C.; Corvasce, C.; Kopta, A.; Schneider, D.; Pâques, G.; Rahimo, M. The influence of humidity on the high voltage blocking reliability of power IGBT modules and means of protection. Microelectron. Reliab. 2018, 88–90, 470–475. [Google Scholar] [CrossRef]

- Sadik, D.-P.; Lim, J.-K.; Giezendanner, F.; Ranstad, P.; Nee, H.-P. Humidity testing of SiC power MOSFETs—An update. In Proceedings of the 2017 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; pp. 1–8. [Google Scholar]

- DiGiacomo, G. Metal Migration (Ag, Cu, Pb) in Encapsulated Modules and Time-to-Fail Model as a Function of the Environment and Package Properties. In Proceedings of the 20th International Reliability Physics Symposium, San Diego, NV, USA, 30 March–1 April 1982; pp. 27–33. [Google Scholar]

- Bumiller, E.; Hillman, C. A Review of Models for Time-To-Failure Due to Metallic Migration Mechanisms. DfR Solutions. 2009. Available online: https://www.dfrsolutions.com/hubfs/Resources/services/Review-of-Models-for-Time-to-Failure-Due-to-Metallic-Migration-Mechanisms.pdf (accessed on 9 November 2020).

- Paunovic, M.; Schlesinger, M. Fundamentals of Electrochemical Deposition, 2nd ed.; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2005; ISBN 9780470009406. [Google Scholar]

- IPC. IPC-9201 Surface Insulation Resistance Handbook; IPC: Northbrook, IL, USA, 1996. [Google Scholar]

- Hornung, A. Diffusion of silver in borosilicate glass. In Proceedings Electronic Components Conference; IEE: Piscataway, NJ, USA, 1968; p. 250. [Google Scholar] [CrossRef]

- Peck, D.S. Comprehensive model for humidity testing correlation. In Proceedings of the 24th International Reliability Physics Symposium, New York, NY, USA, 1–3 April 1986; pp. 44–50. [Google Scholar]

- Shirley, C.G.; Hong, C.E.C. Optimal acceleration of cyclic THB tests for plastic-packaged devices. In Proceedings of the 29th Annual Proceedings Reliability Physics, Las Vegas, NV, USA, 9–11 April 1991; pp. 12–21. [Google Scholar]

- Hallberg, Ö.; Peck, D.S. Recent humidity accelerations, a base for testing standards. Qual. Reliab. Eng. Int. 1991, 7, 169–180. [Google Scholar] [CrossRef]

- Pecht, M.G.; Shukla, A.A.; Kelkar, N.; Pecht, J. Criteria for the assessment of reliability models. IEEE Trans. Components Packag. Manuf. Technol. Part B 1997, 20, 229–234. [Google Scholar] [CrossRef]

- Yang, S.; Christou, A. Failure Model for Silver Electrochemical Migration. IEEE Trans. Device Mater. Reliab. 2007, 7, 188–196. [Google Scholar] [CrossRef]

- Osenbach, J.W.; Evanosky, T.L. Temperature-humidity-bias-behavior and acceleration model for InP planar PIN photodiodes. J. Light. Technol. 1996, 14, 1865–1881. [Google Scholar] [CrossRef]

- Kim, J.H.; Park, S.-D. Acceleration of applied voltage on metallic ion migration of wires in NTC thermistor temperature sensors. Eng. Fail. Anal. 2013, 28, 252–263. [Google Scholar] [CrossRef]

- Pecht, M. A Model for Moisture Induced Corrosion Failures in Microelectronic Packages. IEEE Trans. Components Hybrids Manuf. Technol. 1990, 13, 383–389. [Google Scholar] [CrossRef]

- Paulson, W.M.; Lorigan, R.P. The Effect of Impurities on the Corrosion of Aluminum Metallization. In Proceedings of the 14th International Reliability Physics Symposium, Las Vegas, NV, USA, 20–22 April 1976; pp. 42–47. [Google Scholar]

- Kohman, G.T.; Hermance, H.W.; Downes, G.H. Silver Migration in Electrical Insulation. Bell Syst. Tech. J. 1955, 34, 1115–1147. [Google Scholar] [CrossRef]

- Kolesar, S.C. Principles of Corrosion. In Proceedings of the 12th International Reliability Physics Symposium, Las Vegas, NV, USA, 2–4 April 1974; pp. 155–167. [Google Scholar] [CrossRef]

- Comizzoli, R.B.; Frankenthal, R.P.; Milner, P.C.; Sinclair, J.D. Corrosion of electronic materials and devices. Science 1986, 234, 340–345. [Google Scholar] [CrossRef] [Green Version]

- Frankel, G.S. Pitting Corrosion of Metals A Review of the Critical Factors. J. Electrochem. Soc. 1998, 145, 2186–2198. [Google Scholar] [CrossRef]

- Will, F.G.; Janora, K.H.; McMullen, J.G.; Yerman, A.J. Corrosion of Aluminum Metallization Through Flawed Polymer Passivation Layers; In-Situ Microscopy. In Proceedings of the 25th International Reliability Physics Symposium, San Diego, CA, USA, 7–9 April 1987; pp. 34–41. [Google Scholar]

- Pyun, S.-I.; Moon, S.M. Corrosion mechanism of pure aluminium in aqueous alkaline solution. J. Solid State Electrochem. 2000, 4, 267–272. [Google Scholar] [CrossRef]

- Iannuzzi, M. Reliability and Failure Mechanisms of Nonhermetic Aluminum SIC’s: Literature Review and Bias Humidity Performance. IEEE Trans. Components Hybrids Manuf. Technol. 1983, 6, 181–190. [Google Scholar] [CrossRef]

- Peck, D.S.; Zierdt, C.H. The reliability of semiconductor devices in the bell system. Proc. IEEE 1974, 62, 185–211. [Google Scholar] [CrossRef]

- Li, K.; Coulbeck, L.; Li, D.; Birkett, M.; Luo, H.; Li, H.; Wang, Y.; Dai, X.; Liu, G. Reliability considerations of high power IGBT modules under high temperature/humidity/bias (HTHB) condition. In Proceedings of the PCIM Europe Conference, Nuremberg, Germany, 7–9 May 2019; pp. 1052–1056. [Google Scholar]

- Rahimo, M.; Richter, F.; Fischer, F.; Vemulapati, U.; Kopta, A.; Corvasce, C.; Geissmann, S.; Bellini, M.; Bayer, M.; Bauer, F. The impact on power semiconductor device operation due to local electric field alterations in the planar junction termination. Microelectron. Reliab. 2016, 58, 51–57. [Google Scholar] [CrossRef]

- Qian, Q.; Liu, Y.; Irving, S.; Luk, T. Analysis of the impact of polyimide coating on passivation reliability by simulation. In Proceedings of the 57th Electronic Components and Technology Conference, Reno, NV, USA, 29 May–1 June 2007. [Google Scholar] [CrossRef]

- Tanaka, N.; Ota, K.; Iura, S.; Kusakabe, Y.; Nakamura, K.; Wiesner, E.; Thal, E. Robust HVIGBT module design against high humidity. In Proceedings of the PCIM Europe 2015, Nuremberg, Germany, 19–21 May 2015; pp. 368–373. [Google Scholar]

- Grossner, U.; Mihaila, A.; Vemulapati, U. Passivation in High-Power Si Devices—An Overview. ECS Trans. 2013, 50, 267–277. [Google Scholar] [CrossRef]

- Matsushima, H.; Yamada, R.; Shima, A. Two Mechanisms of Charge Accumulation in Edge Termination of 4H-SiC Diodes Caused by High-Temperature Bias Stress and High-Temperature and High-Humidity Bias Stress. IEEE Trans. Electron Devices 2018, 65, 3318–3325. [Google Scholar] [CrossRef]

- Matsushima, H.; Yamada, R.; Shima, A. Suppression of charge accumulation on termination area of 4H-SiC power devices. In Proceedings of the 2017 29th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Sapporo, Japan, 28 May–1 June 2017; pp. 347–350. [Google Scholar]

- Drandova, G.; Pacheco, A.; Della-Morrow, C.; Reese, E.; Poulton, M. EE World Online. 2018. Available online: https://www.eeworldonline.com/moisture-compliance-for-gan-and-gaas-based-products/ (accessed on 1 November 2020).

- McDonald, T. Meeting Industry Requirements for GaN Device Reliability. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 17–21 March 2019; Available online: https://www.psma.com/sites/default/files/IS11.2%20Meeting%20Industry%20Requirements%20for%20GaN%20Device%20Reliability.pdf (accessed on 9 November 2020).

- Schnable, G.L. Passivation Coatings on Silicon Devices. J. Electrochem. Soc. 1975, 122, 1092. [Google Scholar] [CrossRef]

- Atalla, M.M.; Tannenbaum, E.; Scheibner, E.J. Stabilization of Silicon Surfaces by Thermally Grown Oxides. Bell Syst. Tech. J. 1959, 38, 749–783. [Google Scholar] [CrossRef]

- Deal, B.E. The Oxidation of Silicon in Dry Oxygen, Wet Oxygen, and Steam. J. Electrochem. Soc. 1963, 110, 527. [Google Scholar] [CrossRef]

- Deal, B.E. Measurement and control of dielectric film properties during semiconductor device processing. In Proceedings of the Silicon Device Processing, Gaithersburg, MA, USA, 2 June 1970; pp. 36–50. [Google Scholar]

- Grove, A.S. Physics and Technology of Semiconductor Devices; Wiley: Hoboken, NJ, USA, 1967; ISBN 978-0-471-32998-5. [Google Scholar]

- Nicollian, E.H. Surface Passivation of Semiconductors. J. Vac. Sci. Technol. 1971, 8, S39–S49. [Google Scholar] [CrossRef]

- Revesz, A.G.; Zaininger, K.H. The Si-Si02 solid-solid interface system. RCA Rev. 1968, 29, 22–76. [Google Scholar]

- Castro, P.L.; Deal, B.E. Low-Temperature Reduction of Fast Surface States Associated with Thermally Oxidized Silicon. J. Electrochem. Soc. 1971, 118, 280. [Google Scholar] [CrossRef]

- Montillo, F.; Balk, P. High-Temperature Annealing of Oxidized Silicon Surfaces. J. Electrochem. Soc. 1971, 118, 1463. [Google Scholar] [CrossRef]

- Swaroop, B. Ambient Effect on Ionic Charges in Dielectric Films. IEEE Trans. Parts Hybrids Packag. 1973, 9, 234–236. [Google Scholar] [CrossRef]

- Yeow, Y.T.; Clancy, J.W.; Lamb, D.R. The influence of phosphosilicate glass deposition conditions on the surface state charge at the silicon-silicon dioxide interface! Int. J. Electron. 1973, 34, 115–119. [Google Scholar] [CrossRef]

- Wolborski, M. Characterization of Dielectric Layers for Passivation of 4H-SiC Devices. Ph.D. Thesis, KTH Royal Institute of Technology, Stockholm, Sweden, 2006. [Google Scholar]

- Osenbach, J.W. Water-Induced Corrosion of Materials Used for Semiconductor Passivation. J. Electrochem. Soc. 1993, 140, 3667. [Google Scholar] [CrossRef]

- Matsushima, H.; Okino, H.; Mochizuki, K.; Yamada, R. Analyzing charge distribution in the termination area of 4H-SiC diodes by measuring depletion-layer capacitance. Jpn. J. Appl. Phys. 2016, 55, 04ER17. [Google Scholar] [CrossRef]

- Matsushima, H.; Okino, H.; Mochizuki, K.; Yamada, R. The Impact of Interface Charge on the Breakdown Voltage of Terminated 4H-SiC Power Devices. Mater. Sci. Forum 2015, 821–823, 652–655. [Google Scholar] [CrossRef]

- Zorn, C.; Hoffmann, F.; Hanf, M.; Kaminski, N.; Allerstam, F.; Konstantinov, A.; Neyer, T. H3TRB Test on 650 V SiC JBS Diodes. Mater. Sci. Forum 2018, 924, 581–584. [Google Scholar] [CrossRef]

| Parameter | Standard THB (or H3TRB) | High Voltage THB |

|---|---|---|

| Temperature | 85 °C | 85 °C |

| Relative Humidity | 85% | 85% |

| Reverse Bias | 80% of rated Vnom | Up to 90% Vnom |

| Bias Limitation | Max. 80 ÷ 100 V | Unlimited |

| Leakage Monitoring | Not required | Continuous |

| Material | Relative Dielectric Constant | Band-Gap (eV) | Critical Electric Field (MV/cm) | Thermal Conductivity (W/cmK) |

|---|---|---|---|---|

| Al2O3 | 8 | 8.8 | >5 | 0.02 # |

| AlN | 9.14 | 6.03 | 1.2 ÷ 1.8 | 11.7 |

| CaF2 | 6.81 | 12.3 | 14.44 | 0.1 |

| HfO2 | ~30 | 6 | 8.5 | 0.015 # |

| LiF | 9 | 11.6 | 12.24 | 0.15 ## |

| Si3N4 | 7.4 | 5.3 | 10 | 0.3 |

| SiO2 | 3.9 | 9 | 10 | 0.015 # |

| TiO2 | 24 ÷ 57 | 3.05 | 2.7 | 0.07 # |

| ZrO2 | 15 | 5.8 | 15 ÷ 20 | 0.02 |

| Si | 11.7 | 1.12 | 0.3 | 1.5 |

| 4H-SiC | 9.66 | 3.23 | 3 ÷ 5 | 3.7 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cimmino, D.; Ferrero, S. High-Voltage Temperature Humidity Bias Test (HV-THB): Overview of Current Test Methodologies and Reliability Performances. Electronics 2020, 9, 1884. https://doi.org/10.3390/electronics9111884

Cimmino D, Ferrero S. High-Voltage Temperature Humidity Bias Test (HV-THB): Overview of Current Test Methodologies and Reliability Performances. Electronics. 2020; 9(11):1884. https://doi.org/10.3390/electronics9111884

Chicago/Turabian StyleCimmino, Davide, and Sergio Ferrero. 2020. "High-Voltage Temperature Humidity Bias Test (HV-THB): Overview of Current Test Methodologies and Reliability Performances" Electronics 9, no. 11: 1884. https://doi.org/10.3390/electronics9111884