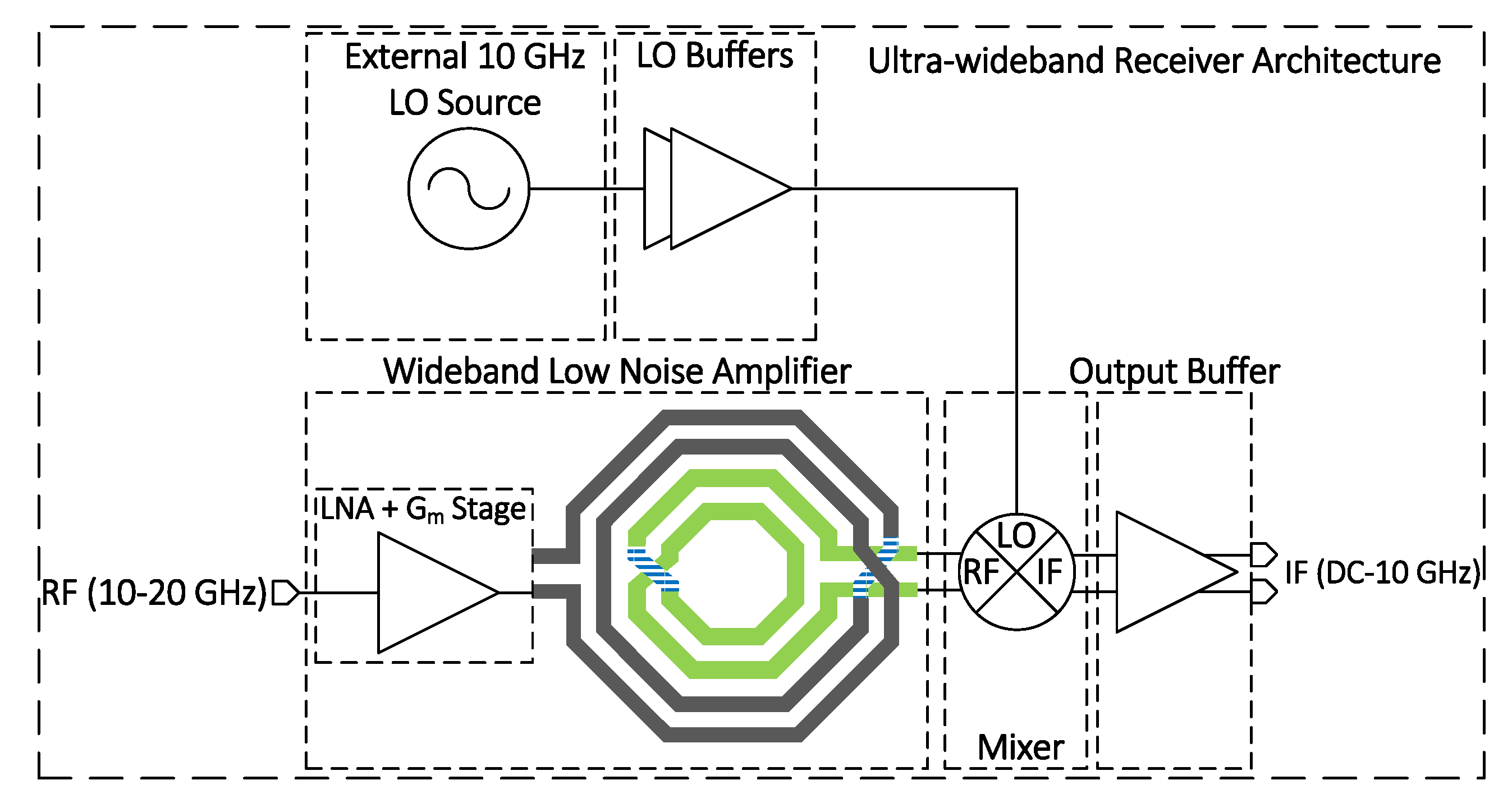

A description of the major building blocks, including wideband LNA and mixer, is given in the following sections.

3.1. Low Noise Amplifier (LNA)

Low-Noise Amplifier (LNA) with wide bandwidth is one of the most crucial components in designing receivers for instrumentation systems, optical communications, and software defined radios (SDR) [

6]. Distributed Amplifiers (DA) were extensively used in the past to achieve high gain and broadband input matching. Several low power DA architectures have been proposed [

7,

8]; however, their main downside was occupation of large chip area. Hence, DAs have been deemed as an unsuitable choice for fully integrated receivers. The common source amplifier with inductive degeneration has been the most widely used topology to implement LNA [

9], because of its high gain, good noise performance, and ability to match to the source impedance. However, inductor degenerated LNA is an inherently narrowband circuit topology with series RLC resonator as an input matching network [

10]. Such an implementation provides high gain over a narrow band, and hence is not suitable for the broadband signal reception. Such a scheme can be adopted for wideband signaling provided that the power budget available for the whole system is high.

Resistive-feedback LNA provides high gain and broadband characteristics, along with good input matching, lower NF, and occupy small chip area [

11].

Figure 2a shows the architecture and design philosophy of the proposed two-stage wideband LNA. The two-stage topology ensures wideband signal reception by enhancing the LNA bandwidth using lowpass type first stage, and bandpass type second stage. The first stage enhances the low frequency content around the lower end of resonant frequency of the second stage, and combined together with the bandpass type second stage, guarantees wideband RF input signal reception and amplification.

Figure 2b shows the schematic of proposed on-chip LNA. It consists of RFI as the first stage of LNA and a transformer-loaded common source amplifier as a second stage. The RFI can be thought of as an extension of resistive feedback common source amplifier, and can provide high linearity and good power efficiency as compared to its conventional counterpart, i.e., resistive feedback common source amplifier. As for the input matching to 50

source, a single matching inductor,

, has been employed. According to the Friis NF equation [

12], the NF of the overall system depends on the NF of the first stage, given that the gain of the first stage is adequately high. The DC gain of the RFI is given by:

In Equation (

1),

, where

and

are the transconductances of the NMOS and PMOS devices in the RFI. Equation (

1) states that the gain of the LNA can be increased by increasing the transconductance of both NMOS and PMOS devices. This is possible only if the output resistances of both NMOS and PMOS devices stay constant over device size variation. However, in short channel devices, by increasing the size of transistors to obtain high

at the same DC current, the corresponding output resistances decrease and, hence, the intrinsic gain of the RFI stays relatively constant. The NF of the RFI is given by [

13]:

where

is the source resistance and

is the thermal noise coefficient for the NMOS and PMOS devices with values ranging from 1 to 2 in saturation condition. In short channel MOSFETs, the value of

is usually very small, if the size of the transistors is chosen very large to increase the transconductance of the MOSFETs, and, hence, this value can drop below 100

. Therefore, in Equation (

2), if

, then only the first term in the bracket will dominate. Accordingly, increasing the

and satisfying

condition simultaneously not only makes the gain of first stage LNA to approach its intrinsic gain, i.e.,

, but also reduces the NF of the overall system. It is important to note that Equation (

2) only models the thermal noise effect of RFI and does not include

noise, and, hence, Equation (

2) is constant for all frequencies.

Figure 3 shows the calculated and simulated NF of the RFI based on the parameters given in

Table 1. A good correlation between post-layout simulated NF of RFI and calculated NF can be seen from approximately 1 to 12 GHz based on the given NF model. Given that the circuit is properly designed, the RFI can provide a gain almost twice that of a conventional resistive feedback common source amplifier. This also indicates that the

efficiency of the RFI is better as compared to simple resistive feedback common source configuration owing to the utilization of current reuse technique. From a more rigorous analysis, it can be proven that, if

, then the amplifier is biased near

, which makes the amplifier linear and stable.

With the input signal having a 10 GHz bandwidth in this work, it is necessary that not only wideband amplification is achieved, but also the input of the LNA is matched to the source resistance over this whole frequency band to allow maximum power of the signal to be transferred to the LNA input. Hence, a wideband matching circuit needs to be designed as opposed to commonly employed narrowband matching techniques. Ref. [

14] proposed a three-section bandpass Chebyshev filter to achieve ultrawideband input matching ranging 3.1–10.6 GHz RF input band. However, the proposed three-section filter employs three on-chip inductors to achieve wideband matching. It can be easily seen in [

14] that the majority of the on-chip area has been occupied by the input matching network. One of the major focuses of this work is to alleviate this issue and achieve input matching with as few passive components as possible, provided that a slight compromise on the NF of whole system can be made.

With only first-order approximations taken into account by ignoring the parasitic capacitances and gate resistance, the input admittance,

, of the RFI can be given by Equations (

3) and (

4), where

and

. It can be observed from Equation (

3) that the real part of input impedance is dependent on the frequency. Hence, the transistors in RFI should be sized so that not only desirable gain and NF is achieved, but also an input conductance of around 20 mS is obtained within the input band of interest, i.e., from 10–20 GHz. Based on MATLAB simulations, Equations (

3) and (

4) are plotted in

Figure 4. Based on the parameters given in

Table 1, the input conductance,

, falls in the range of 16.6–20 mS in the desired input frequency band. Moreover, the input susceptance,

, increases almost linearly with frequency, which implies that the input admittance of the RFI can be modelled by a resistor in parallel with a capacitor. In

Figure 4, the input resistance,

, and input capacitance,

, fall in the range from 60 to 49

, and from 0.260 to 0.256 pF, respectively, based on the parameters chosen for transistor and other passive components in LNA. Combining this model of input admittance with the input matching inductor and a small pad capacitance results in a

-network.

Figure 5 shows the equivalent model of the input matching circuit, i.e.,

, along with the input admittance,

, of RFI and the pad capacitance,

. The input trace inductance,

, connecting the input pad and the matching inductor has been ignored here for simplicity, and hence the value of

are evaluated at higher resonant frequencies relative to desired RF input band. Eventually,

will shift the resonant band from higher end to the desired input band of 10–20 GHz. In the following, it is theoretically demonstrated that the proposed network can achieve wideband input matching with only a single matching inductor.

It is desired that the impedance,

(or equivalently

), being seen at the input pad should be equal to

(or equivalently

if talking in terms of admittance parameters) over the whole input frequency band. The

-matching network can be designed by considering it as two cascaded

L-section matching circuits, as described in

Figure 6. It is important to note that

and

are the series resistances of their respective inductors. The

-section matching network tunes out

at a lower frequency, while the

-section matching network tunes out

at a higher frequency, since the value of pad capacitance is quite small. To tune out

at 15 GHz (which is the midpoint frequency of interest of the input band, and is hence called

), it is important to evaluate the value of the inductor

along with its series resistance,

, that can achieve such a task, and that value can be evaluated as per the following expression:

where

= 15 is chosen as the quality factor of inductor

. Having plotted Equations (

5) and (

6) in

Figure 7, the desired value of

to tune out

at 15 GHz is roughly equal to 280 pH. It is interesting to note, however, that the value of

is frequency dependent and that Equation (

5) provides freedom in choosing the value of

which can tune out

at any desired frequency of interest. For instance, to tune out the

at 10 GHz, the required value of inductor would roughly be equal to 478 pH. The value of equivalent series resistance,

, can be chosen based on Equation (

6). In

Figure 7, the value of

is approximately equal to 1.76

at

= 15 GHz. The input admittance and impedance at the intermediate node,

, plotted in

Figure 8, can be theoretically derived as:

As evident in

Figure 8, the chosen value for

indeed tunes out

at desired resonant frequency,

, which suggests that the input impedance at the intermediate node is composed purely of the resistive portion at

, and is given by:

where

is the quality factor of

, also plotted in

Figure 7. Equation (

8) marks a reduction in series resistance being seen at the intermediate node at

. With

at

, the value of input resistance is approximately halved as compared to

of RFI, where the input resistance varies from approximately 32 to 16

at the intermediate node within the band of interest. However, the reactive part is zero only at

and non-zero over rest of the frequency band, which illustrates that the total impedance being incorporated into the

-section matching network is

, where the value of

at

is given by Equation (

8).

To ensure a good, wideband power match, it is vital that

is also tuned out at

, and, to achieve it, the value of the inductor,

, in the

-section matching network must be sorted out. To tune out the

, it is important that the total impedance,

, being incorporated in

-section matching network given by Equation (

7), is purely resistive at

. As mentioned above,

Figure 7 provides freedom in choosing the value of inductor

to tune out

at any desired higher resonant frequency. At a frequency of 25 GHz (which is referred to as

), the value of

obtained in

Figure 7 is roughly equal to 119 pH with the value of

being equal to 1.25

. This implies that at

, only resistive part will be incorporated into

-section matching network, and the circuit at

would resemble the one in

Figure 9. It is important to note that, at

, the total series resistance for

has now increased from mere

to

. With the multiple unknowns being encountered, an initial assumption is required to evaluate the value of

. As a starting point, it assumed that

, where

a is a multiplication factor ranging from as low as 1 to as high as required. By transforming the series

circuit into parallel

circuit in

Figure 9, the values of equivalent components can be found by the subsequent equations:

where

,

, and

can be evaluated at

in

Figure 4 and

Figure 7. In this design,

has been modeled by a 100 fF capacitance. The equivalent parallel inductance,

, can be found by:

The quality factor of the equivalent parallel inductor can be evaluated through

), and by substituting the values of Equation (

9) in the aforementioned equation, a quadratic equation is obtained as mentioned in Equation (

11). Solving Equation (

11) yields two different values of

from which the larger one would be employed in subsequent calculations. Having known the values of

and

, the required value of

-section series matching inductor,

, can be figured out through the following equation:

In the current design, having arbitrarily chosen the value of

along with the values of

,

, and

at

, and

being obtained from Equation (

10),

is evaluated equal to 2.15 and from Equation (

12), the value of

is found equal to 333 pH. With the values of all the components evaluated, the input impedance,

, at the source can be described by the following equation:

Figure 10 shows the MATLAB simulation plot of the input impedance,

, and input matching,

. In

Figure 10, the input resistance seen by the source ranges from 40 to 63

over the entire frequency band of 10–20 GHz, while the reactive portion ranges from −13 to 22

. It can also be observed that the reactive portion of

is zero at the desired resonant frequencies of 15 and 25 GHz. The effect of

has been ignored in the aforementioned calculations. If the inductance of

is taken into account, then the resonant frequency shifts towards the lower end of the input RF band, as shown in

Figure 11. It can also be seen that the input matching no longer remains <−10 dB above 18 GHz. Hence, to compensate for this, the value of

is reduced to 270 pH in the second iteration, which provides a perfect <−10 dB matching over whole input band. Having found the values of both the inductors at

, the value of an equivalent, single matching inductor can be found as follows:

From Equation (

14), the value of an ideal, single equivalent matching inductor,

, is equal to 389 pH, which is equal to the one used in the actual design (value mentioned in

Table 1). It must be noted that the value of

evaluated previously was 280 pH. However, to resonate both

and

, the total matching inductance value must satisfy Equation (

14). In that case, if the value of

was chosen to be 280 pH, then that of

must be 109 pH as opposed to 270 pH. The quality factor of an equivalent, single matching inductor,

, can be calculated by:

Therefore, apart from the input trace inductance (which is fixed because of the fixed length of the input signal line in the current design, but can be changed by laying out the chip in more efficient way so as to reduce

), a theoretical

value of 389 pH with a quality factor of approximately 18 is required to tune out both

and

over a wide bandwidth of 10 GHz. A minor difference was observed in

between the MATLAB simulation and actual design, which can be attributed to the unaccounted parasitics and first-order approximations made in evaluating the input admittance of RFI mentioned in Equations (

3) and (

4).

With implementation of the aforementioned input matching network and considering that the maximum signal power has been transferred to the input of the LNA, this whole band requires amplification. The first-stage LNA, i.e., RFI, cannot provide such a wideband signal amplification alone as it depicts a lowpass nature. In this work, the input signal is a bandpass type and, hence, an amplifier with bandpass characteristics is desired. The transformer-loaded common source amplifier has been adopted as the second stage, which is AC coupled with the previous stage and has its own biasing through the bias resistor,

, as shown in

Figure 2. This configuration provides high gain in a narrow band (with its bandwidth dependent upon the quality factor of the transformer) around the resonant frequency,

, which in this work is tuned towards the upper end of the input band. The proposed signaling method combining the lowpass and bandpass characteristics of first and second stage LNA, respectively, can thereby provide wideband signal amplification. The LNA gain plot has been shown in the

Figure 12. The 3-dB cutoff frequency of the first-stage LNA is 16.5 GHz (relative to 10 GHz), while the second-stage LNA is resonant at 18 GHz. The total LNA gain has been shown as a sum of gain from both stages where LNA provides a gain flatness of less than 4 dB. The transformer load also achieves single-to-differential conversion. Without the transformer load, high gain due to the front-end along with the parasitic ground inductance incurs unwanted oscillations. Another reason to convert the amplified signal from single-ended to differential is that the differential signaling in the mixer reduces the second-order distortions and improves robustness to power supply and substrate noise while also improving stability.