Design and Realization of an Aviation Computer Micro System Based on SiP

Abstract

1. Introduction

2. Related Work

2.1. SiP Technology Status

2.2. SiP Applications in Aviation

3. Methodology

3.1. Technical Requirements

- (1)

- Minimal computer system: processor, programmable logic resources, memory (data, program), etc.;

- (2)

- Computing power: fixed-point number processing capability is not less than 2GIPS, floating-point number processing capability is not less than 1GFLOPS;

- (3)

- The typical power consumption is not greater than 2.5 W;

- (4)

- The chip area is not greater than 4 × 4 cm2.

3.2. Plan Selection

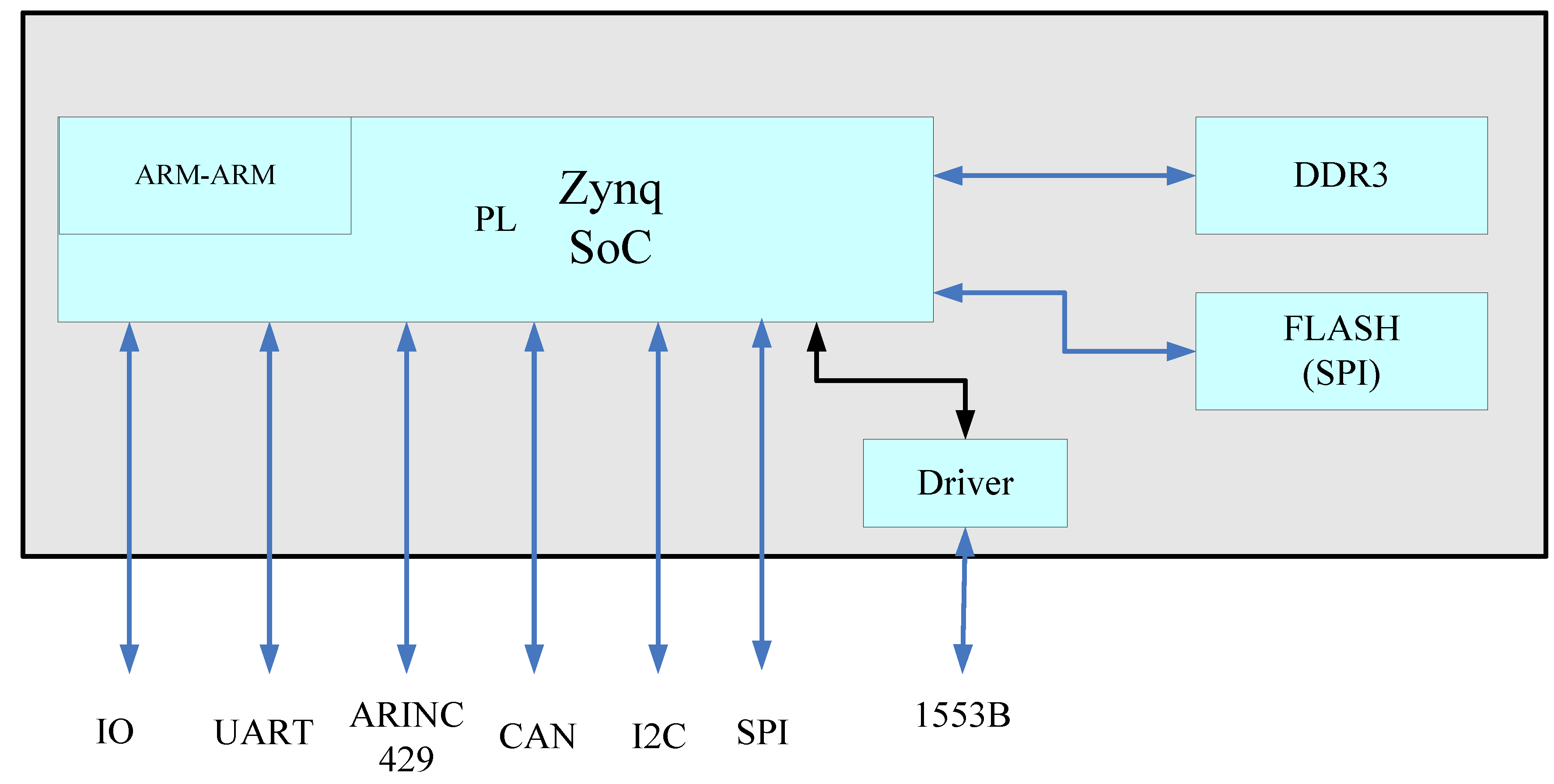

3.3. System Components

3.4. Chip Design and Simulation

4. Experimental Design and Analysis

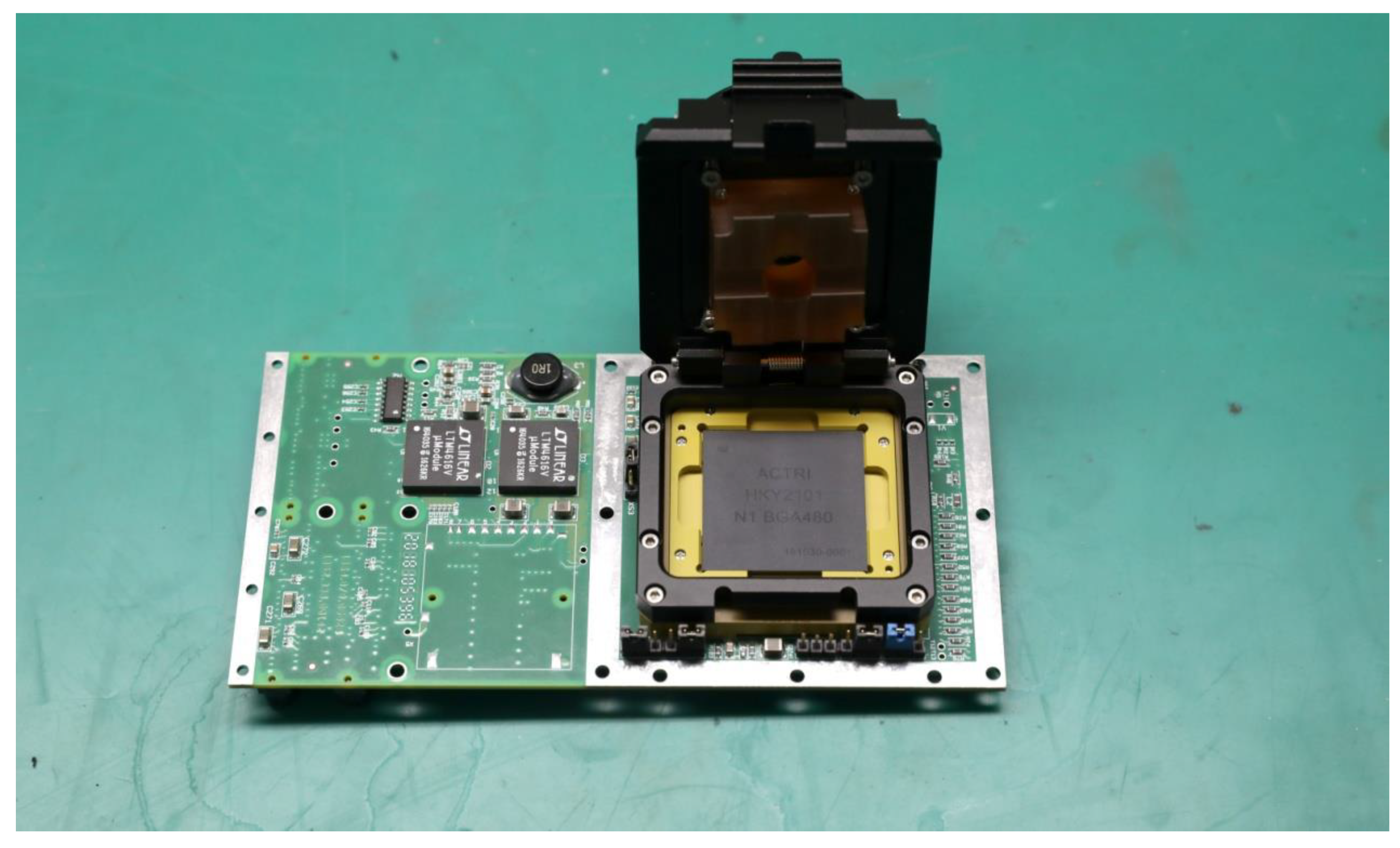

4.1. Functional Testing

4.2. Analysis and Improvement of Chip Thermal Test

4.2.1. Test Situation before Improvement

4.2.2. Thermal Analysis

4.2.3. Thermal Improvement

4.3. Comparison with PCB Design

4.3.1. Comparison of Size and Power Consumption

4.3.2. DDR3 Memory Test Comparison and Analysis

4.4. Aviation Computer Test and Comparison

4.4.1. Test Algorithm Selection

4.4.2. Algorithm Design

4.4.3. Aviation Computer Selection

4.4.4. Comparison and Analysis of Test Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Hu, Y.; Cai, J.; Cao, L.; Chen, L.; Liu, Z.; Shi, L.; Wang, Q. The research status and development trends of system in package (sip) technology. Equip. Electron. Prod. Manuf. 2012, 14, 1–6. [Google Scholar]

- Mounce, G.; Lyke, J.; Horan, S.; Doyle, R.; Some, R. Chiplet Based Approach for Heterogeneous Processing and Packaging Architectures. In Proceedings of the 2016 IEEE Aerospace Conference, Big Sky, MT, USA, 5–12 March 2016. [Google Scholar]

- Hao, W. Application of Sip Technology in Aerospace Products. Aerosp. Stand. 2013, 1, 30–33. [Google Scholar]

- Hang, C. Research of Missile-borne Computer Based on SiP. Dev. Innov. Mach. Electr. Prod. 2016, 29, 14–16. [Google Scholar]

- Ming, W.; Feng, W. SIP Packaging Technology. Electron. Packag. 2009, 2, 6. [Google Scholar]

- Pasca, V.; Anghel, L.; Nicolaidis, M.; Benabdenbi, M. Csl: Configurable fault tolerant serial links for inter-die communication in 3d systems. J. Electron. Test. 2016, 28, 137–150. [Google Scholar] [CrossRef]

- Tseng, H.L.; Huang, W.T.; Dai, J.C.; Chen, C.H.; Tan, S.Y. An evaluation eye diagram of a high-reliability fpga platform for high-resolution camera. Appl. Mech. Mater. 2015, 764, 1270–1274. [Google Scholar] [CrossRef]

- Lorena, A.; Mounir, B.; Alberto, B.; Marcello, T.; Ioana, V.E. Test and reliability in approximate computing. J. Electron. Test. 2018, 34, 375–387. [Google Scholar]

- Wang, H.; Bai, X.; Wu, Q. Multichannel High-Speed Data Caching System on FPGA for RAID Storage. In Proceedings of the International Conference in Communications, Signal Processing, and Systems, Dalian, China, 14–16 July 2018; Springer: Singapore, 2018. [Google Scholar]

- Meng, X. Temperature estimation of high temperature data acquisition multichip module for oil field apparatus. In Proceedings of the IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), Las Vegas, NV, USA, 31 May–3 June 2016. [Google Scholar]

- Liu, L.; Jiang, P.; Zhao, X. The study of testing scenario for a SIP microcomputer. In Proceedings of the International Conference on Electronic Packaging Technology & High Density Packaging, Guilin, China, 13–16 August 2012; IEEE: Piscataway, NJ, USA, 2012. [Google Scholar]

- Canras, B.; Albarbar, A. A Technique for Mitigating Thermal Stress and Extending Life Cycle of Power Electronic Converters Used for Wind Turbines. Electronics 2015, 4, 947–968. [Google Scholar]

- Charles, H. Electronic Packaging and Interconnection Handbook; McGraw-Hill, Inc.: New York, NY, USA, 2004. [Google Scholar]

- Khan, A. Equilibrium Molecular Dynamics (MD) Simulation Study of Thermal Conductivity of Graphene Nanoribbon: A Comparative Study on MD Potentials. Electronics 2015, 4, 1109–1124. [Google Scholar] [CrossRef]

- Masahiro, I. Temperature Dependence of Electrical and Thermal Conductivities of an Epoxy-Based Isotropic Conductive Adhesive. J. Electron. Mater. 2008, 37, 462–468. [Google Scholar]

- Chen, M.S.; Chang, Y.C.; Chen, W.T.; Kuo, T.Y. Design and implementation of ultra-thin SiP modules. In Proceedings of the International Microsystems, Packaging, Assembly & Circuits Technology Conference, Taipei, Taiwan, 24–26 October 2012; IEEE: Piscataway, NJ, USA, 2012. [Google Scholar]

- Gao, L.; Wei, X.C.; Huang, Y.T.; Li, B.; Shu, Y.F. Analysis of near-field shielding effectiveness for the sip module. IEEE Trans. Electromagn. Compat. 2017, 60, 288–291. [Google Scholar] [CrossRef]

- Chastang, C.; Gautier, C.; Amedeo, A.; Costa, F. Crosstalk Analysis of Multigigabit Links on High Density Interconnects PCB using IBIS AMI Models. In Proceedings of the 2012 IEEE Electrical Design of Advanced Packaging and Systems Symposium (EDAPS), Taipei, Taiwan, 9–11 December 2012. [Google Scholar]

- Almalkawi, M.; Devabhaktuni, V. Far-End Crosstalk Reduction in PCB Interconnects Using Stepped Impedance Elements and Open-Circuited Stubs. Int. J. RF Microw. Comput.-Aided Eng. 2011, 21, 596–601. [Google Scholar] [CrossRef]

- Jin, S.; Han, L.; Xie, X. Signal integrity analysis of high-speed circuit board interconnecting DDR3 and FPGA. Mod. Electron. Tech. 2017, 40, 10–13. [Google Scholar]

- Jung, M.; Mathew, D.M.; Rheinlander, C.C.; Weis, C.; Wehn, N. A platform to analyze ddr3 dram’s power and retention time. IEEE Des. Test 2017, 34, 52–59. [Google Scholar] [CrossRef]

- Lee, J.-H. A Novel Meander Split Power/Ground Plane Reducing Crosstalk of Traces Crossing Over. Electronics 2019, 8, 1041. [Google Scholar] [CrossRef]

- Chuang, H.H.; Guo, W.D.; Lin, Y.H.; Chen, H.S.; Lu, Y.C.; Cheng, Y.S. Signal/power integrity modeling of high-speed memory modules using chip-package-board coanalysis. IEEE Trans. Electromagn. Compat. 2012, 52, 381–391. [Google Scholar] [CrossRef]

- Lai, Y.L.; Chiang, W.J. Characteristics of a system in a package with silver wires. Key Eng. Mater. 2015, 661, 121–127. [Google Scholar] [CrossRef]

- Odintsov, S.; Jutman, A.; Devadze, S.; Aleksejev, I. Embedded instrumentation toolbox for screening marginal defects and outliers for production. In Proceedings of the 2017 IEEE Autotestcon, Schaumburg, IL, USA, 9–15 September 2017; IEEE: Piscataway, NJ, USA, 2017. [Google Scholar]

- Yan, J. Realization of high speed link channel ber eye diagram based on der. Electron. Sci. Technol. 2016, 29, 30–33. [Google Scholar]

- Zynq Dram Diagnostics Test. Available online: www.xilinx.com (accessed on 15 January 2015).

- Chen, Y. Research on Attitude Measurement System Based on MEMS Inertial Devices. Master’s Thesis, North University of China, Taiyuan, China, 2019. [Google Scholar]

- Zakerzadeh, M.R.; Gerdefaramarzi, M.S.; Bozorg, M. Parameter estimation of an sma actuator model using an extended kalman filter. Mechatronics 2018, 50, 148–159. [Google Scholar]

- Barrios-dV, S.; Lopez-Franco, M.; Rios, J.D.; Arana-Daniel, N.; Lopez-Franco, C.; Alanis, A.Y. An Autonomous Path Controller in a System on Chip for Shrimp Robot. Electronics 2020, 9, 441. [Google Scholar] [CrossRef]

- Hao, Y. Indoor robots heading measurement system based on zynq platform. Microcontrollers Embed. Syst. 2017, 6, 22–27. [Google Scholar]

- Zhao, H. Analysis and Simulation of Integrated Guidance and Control System for R-77 Missile. Master’s Thesis, Southwest University of Science and Technology, Mianyang, China, 2012. [Google Scholar]

| NO. | Case Temperature | Power Consumption | Junction Temperature |

|---|---|---|---|

| 1 | 25 °C | 5 V, 0.235 A, 1.175 W | 35 °C |

| 2 | 75 °C | 5 V, 0.265 A, 1.325 W | 90 °C |

| 3 | 85 °C | 5 V, 0.268 A, 1.34 W | 101 °C |

| 4 | 95 °C | 5 V, 0.278 A, 1.39 W | 113 °C |

| 5 | 100 °C | 5 V, 0.29 A, 1.45 W | 120 °C |

| 6 | 105 °C | 5 V, 0.294 A, 1.47 W | 128 °C |

| Material | Thermal Conductivity (W/mm · °C) |

|---|---|

| PCB | 0.013 |

| Silicon | 0.146 |

| Epoxy resin | 0.002 |

| Thermal conductive silver adhesive | 0.0258 |

| Gas (air) | 0.026 × 10−3 |

| NO. | Case Temperature | Power Consumption | Junction Temperature |

|---|---|---|---|

| 1 | 25 °C | 5 V, 0.234 A, 1.17 W | 31 °C |

| 2 | 75 °C | 5 V, 0.260 A, 1.3 W | 84 °C |

| 3 | 85 °C | 5 V, 0.264 A, 1.32 W | 96 °C |

| 4 | 95 °C | 5 V, 0.277 A, 1.385 W | 106 °C |

| 5 | 100 °C | 5 V, 0.284 A, 1.42 W | 111 °C |

| 6 | 105 °C | 5 V, 0.292 A, 1.46 W | 117 °C |

| Eye Result: (128 Unites = 1 Bit Time (Ideal Eye Width)) | |||||

|---|---|---|---|---|---|

| Description | LANE-0 | LANE-1 | LANE-2 | LANE-3 | |

| SIP_DDR3_Read | EYE[MIN-MAX] | [4, 120] | [4, 116] | [4, 120] | [4, 120] |

| EYE CENTER | 62/128 | 60/128 | 62/128 | 62/128 | |

| EYE WIDTH | 90.62% | 87.5% | 90.62% | 90.62% | |

| SIP_DDR3_Write | EYE[MIN-MAX] | [4, 120] | [8, 124] | [4, 120] | [8, 120] |

| EYE CENTER | 62/128 | 66/128 | 62/128 | 64/128 | |

| EYE WIDTH | 90.62% | 90.62% | 90.62% | 87.50% | |

| principle board_DDR3_Read | EYE[MIN-MAX] | [4, 120] | [8, 120] | [4, 116] | [8, 120] |

| EYE CENTER | 62/128 | 64/128 | 60/128 | 64/128 | |

| EYE WIDTH | 90.62% | 87.50% | 87.50% | 87.50% | |

| principle board_DDR3_Write | EYE[MIN-MAX] | [8, 116] | [8, 116] | [8, 120] | [8, 120] |

| EYE CENTER | 62/128 | 62/128 | 64/128 | 64/128 | |

| EYE WIDTH | 84.38% | 84.38% | 87.50% | 87.50% | |

| Actual Angle | Solution Angle | Error | Actual Angle | Solution Angle | Error |

|---|---|---|---|---|---|

| −30° | −30.685° | 0.685 | 30° | 29.510° | 0.490 |

| −90° | −89.692° | −0.308 | 90° | 90.812° | −0.812 |

| −180° | −178.24° | −0.76 | 180° | 181.571° | −1.571 |

| Test Chip | Architecture | Resources & Extensions | Frequency/MHz | Time | Power/W | Area/mm2 |

|---|---|---|---|---|---|---|

| STM32F407ZGT6 | ARM Cortex-M4 | Flash 1MB+4MB Sram 512KB+1MB | 168 | 3.413 ms | 0.502 | 43 × 39 |

| TMS320F28335PGFA | DSP | Flash 512KB+4MB Sram 68KB+1MB | 150 | 3.345 ms | 1.307 | 49 × 42 |

| SiP chip | ARM Cortex-A9 +FPGA | Flash 16MB Ram 256KB DDR3 128MB | 667 (ARM) 50 (FPGA) | 14.749 µs | 1.195 | 31 × 31 |

| Resources | BRAM_18K | DSP48E | Flip-Flops | LUT |

|---|---|---|---|---|

| Total resources | 120 | 80 | 35,200 | 17,600 |

| Involved dosage | 42 | 60 | 26,315 | 13,552 |

| Utilization/% | 35 | 75 | 74.8 | 77 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lv, H.; Zhang, S.; Han, W.; Liu, Y.; Liu, S.; Chu, Y.; Zhang, L. Design and Realization of an Aviation Computer Micro System Based on SiP. Electronics 2020, 9, 766. https://doi.org/10.3390/electronics9050766

Lv H, Zhang S, Han W, Liu Y, Liu S, Chu Y, Zhang L. Design and Realization of an Aviation Computer Micro System Based on SiP. Electronics. 2020; 9(5):766. https://doi.org/10.3390/electronics9050766

Chicago/Turabian StyleLv, Hao, Shengbing Zhang, Wei Han, Yongqiang Liu, Shuo Liu, Yaoqin Chu, and Lei Zhang. 2020. "Design and Realization of an Aviation Computer Micro System Based on SiP" Electronics 9, no. 5: 766. https://doi.org/10.3390/electronics9050766

APA StyleLv, H., Zhang, S., Han, W., Liu, Y., Liu, S., Chu, Y., & Zhang, L. (2020). Design and Realization of an Aviation Computer Micro System Based on SiP. Electronics, 9(5), 766. https://doi.org/10.3390/electronics9050766