Active Power-Decoupling Methods for Photovoltaic-Connected Applications: An Overview

Abstract

1. Introduction

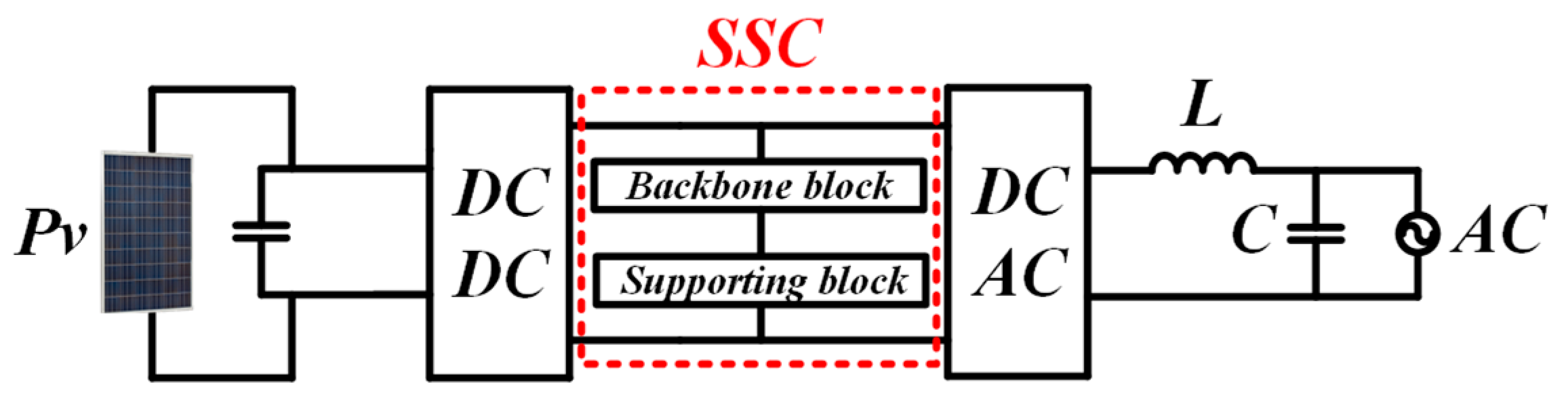

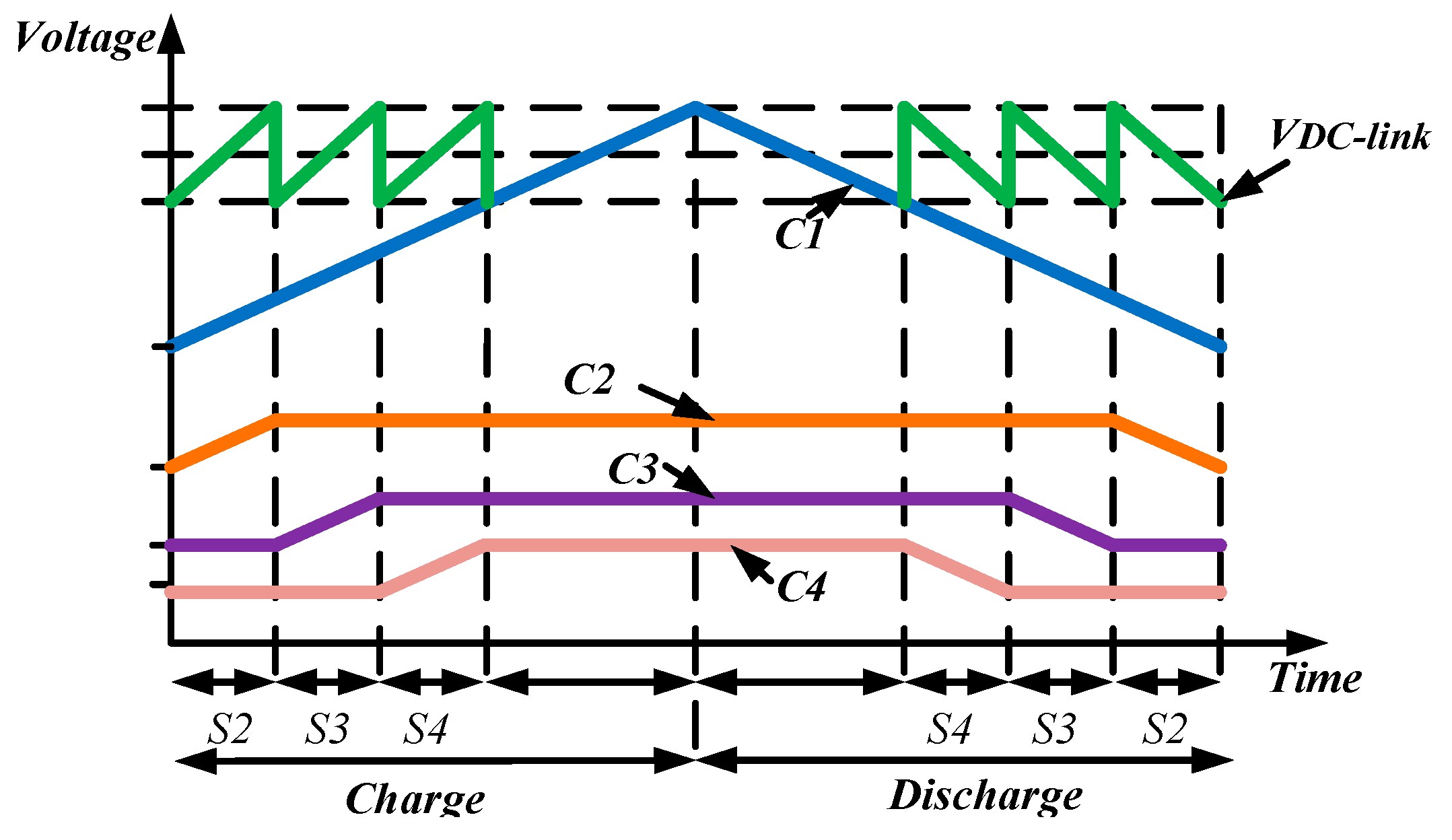

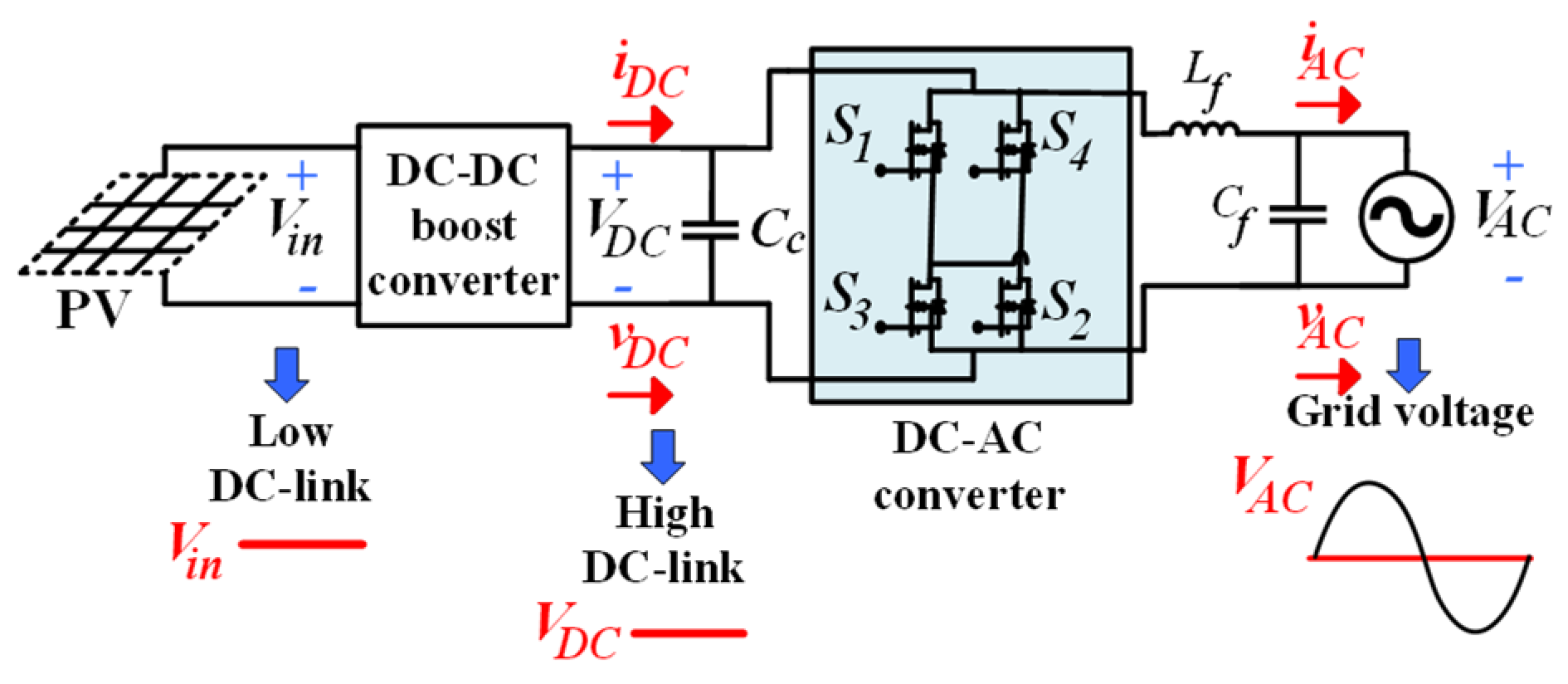

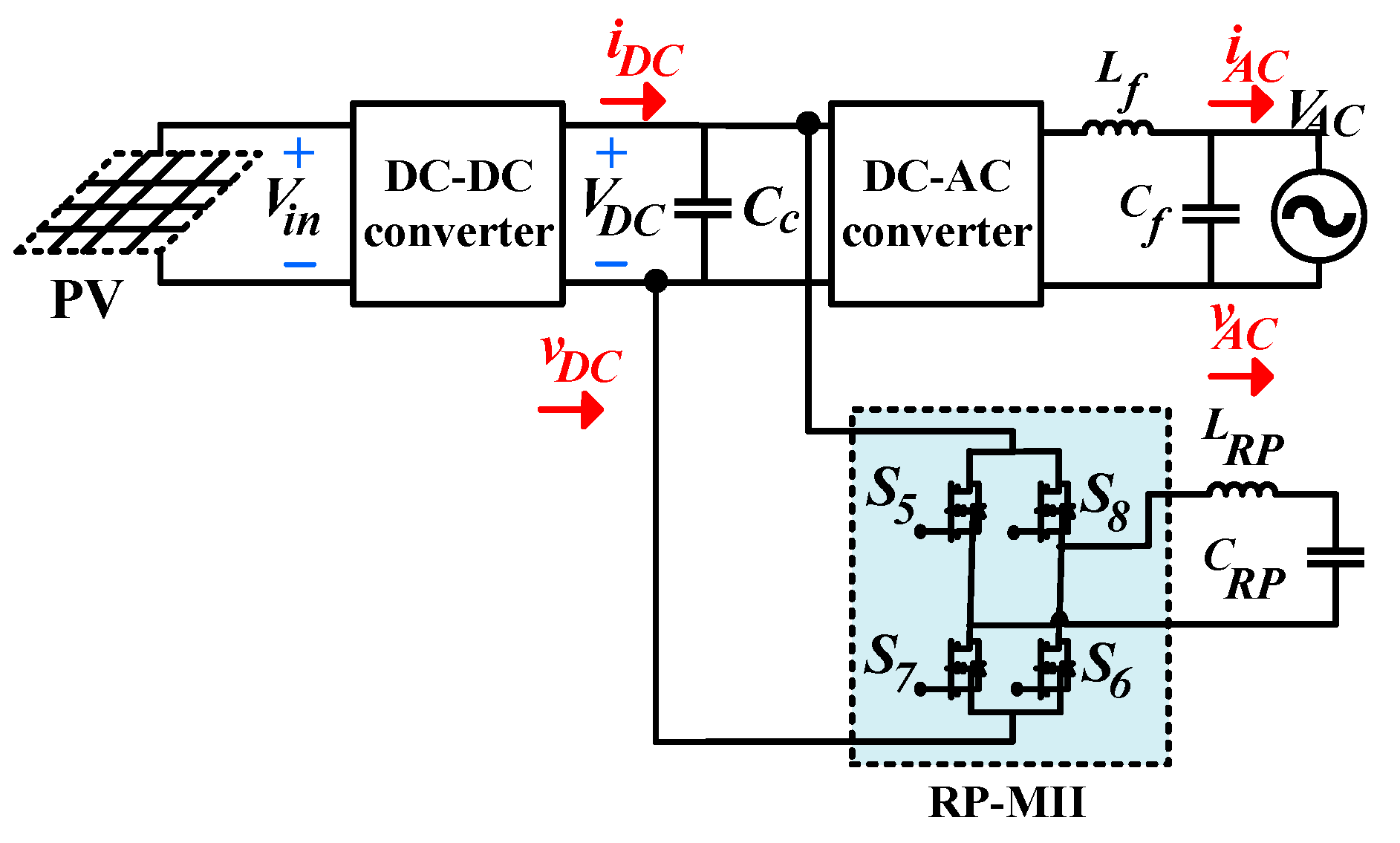

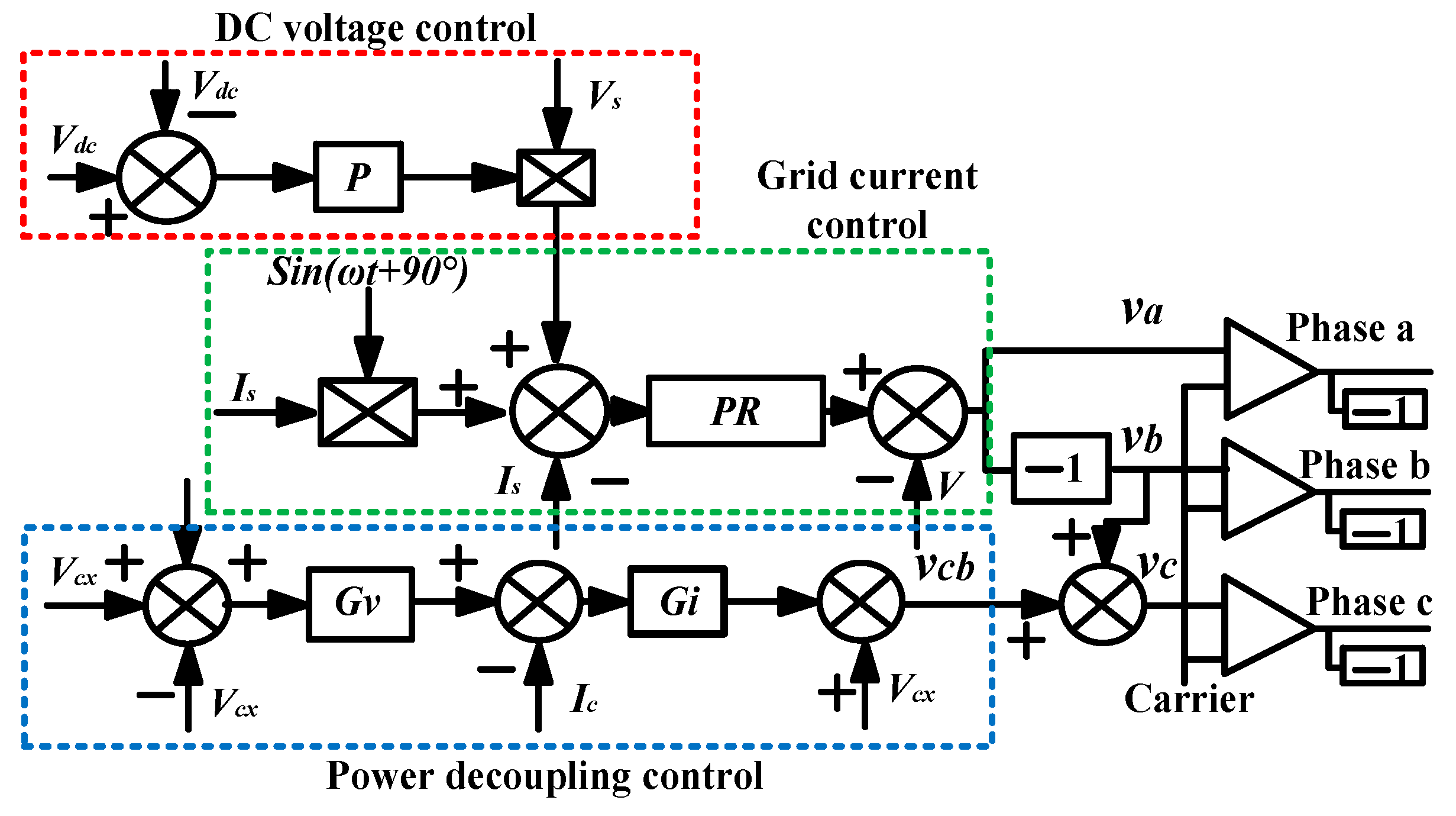

2. The Principal Operation of the SSC, RP-MII, and VCAPD Methods

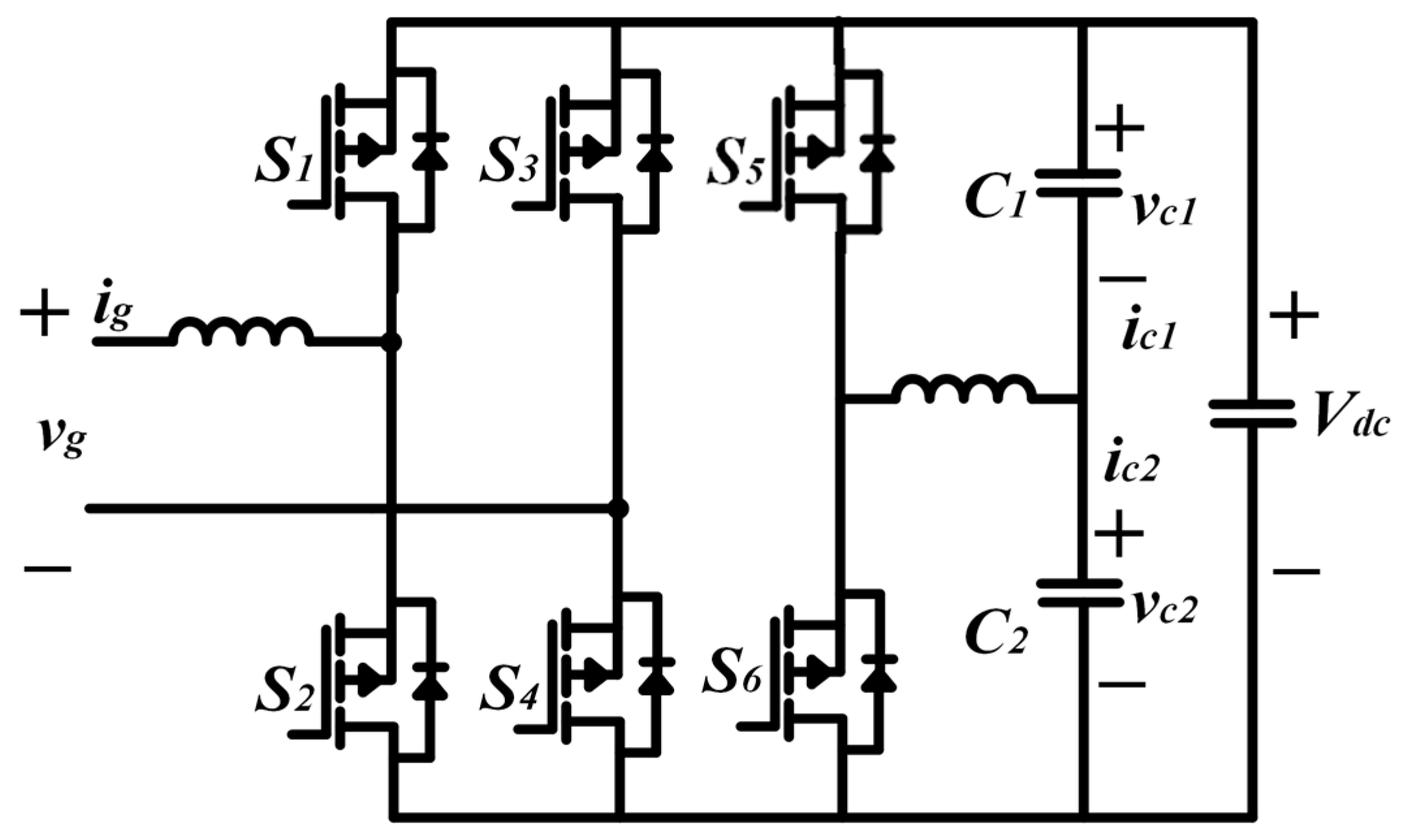

2.1. SSC Architectures

2.2. Capacitive Energy Storage for Ripple Power Compensation

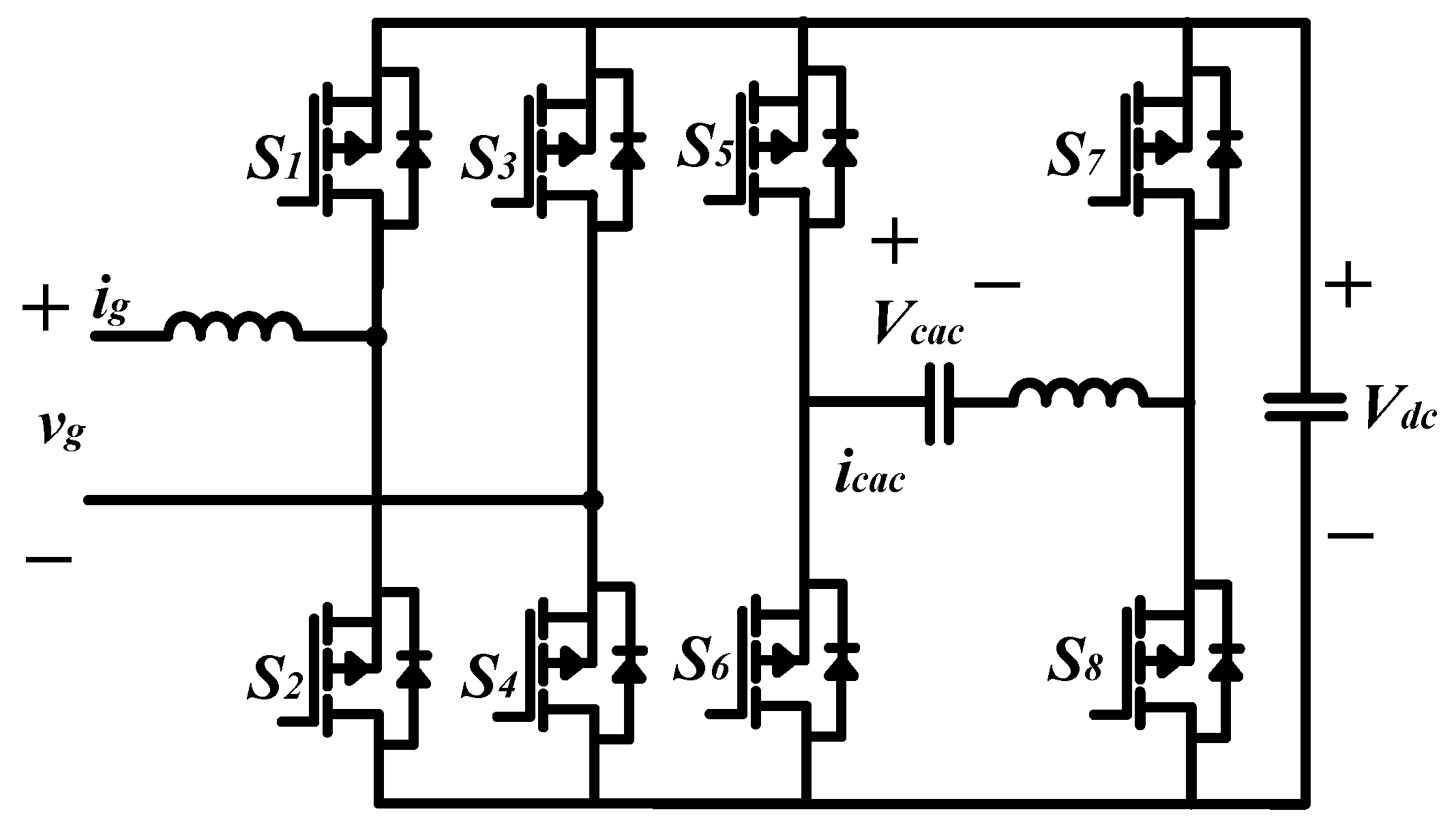

2.3. RP-MII

3. Overview

3.1. SSC as an APD Method

3.2. VCAPD as an APD Method

3.3. RP-MII as an APD Method

4. Comparison of SSC, RP-MII, and VCAPD

5. Concluding Remarks

- Greater energy efficiency is achieved and a substantial reduction of the decoupling capacitor due to the effective use of stored energy;

- Higher effective energy density (an increment of 100%) and lower passive volume are achieved by energy buffer optimization;

- Small DC-link voltage is maintained;

- Need for inductors is eliminated (eliminating magnetic losses).

- Overall size of the system is reduced by eliminating a rectifier stage;

- Inverter and rectifier applications are supported;

- Most simple control stage (SPWM) is performed;

- Reduced decoupling capacitor peak voltage (Vdc) by applying a higher voltage, because Vdc is not limited by the DC-link;

- Any isolated DC–DC converter can be implemented;

- Direct control over the decoupling capacitor voltage and current can be performed;

- Better MPPT performance in the PV-connected system;

- Minimum possible capacitance value for the system with a nominal load (the active filter capacitance of 33nF per watt is sufficient for power ripple cancellation in a single-phase 60 Hz application) can be achieved;

- Voltage limitations of the DC–DC topology are avoided.

Author Contributions

Funding

Conflicts of Interest

References

- Perpiñán, O.; Marcos, J.; Lorenzo, E. Electrical power fluctuations in a network of DC/AC inverters in a large PV plant: Relationship between correlation, distance and time scale. Sol. Energy 2013, 88, 227–241. [Google Scholar] [CrossRef]

- Farivar, G.G.; Manalastas, W.; Tafti, H.D.; Ceballos, S.; Sanchez-Ruiz, A.; Lovell, E.C.; Konstantinou, G.; Townsend, C.D.; Srinivasan, M.; Pou, J. Grid-connected energy storage systems: State-of-the-art and emerging technologies. Proc. IEEE 2022, 111, 397–420. [Google Scholar] [CrossRef]

- Passey, R.; Spooner, T.; MacGill, I.; Watt, M.; Syngellakis, K. The potential impacts of grid-connected distributed generation and how to address them: A review of technical and non-technical factors. Energy Policy 2011, 39, 6280–6290. [Google Scholar] [CrossRef]

- Shao, B.; Miao, Z.; Wang, L.; Meng, X.; Chen, Z. Low-frequency oscillation analysis of two-stage photovoltaic grid-connected system. Energy Rep. 2022, 8, 241–248. [Google Scholar] [CrossRef]

- Vakacharla, V.R.; Gnana, K.; Xuewei, P.; Narasimaharaju, B.; Bhukya, M.; Banerjee, A.; Sharma, R.; Rathore, A.K. State-of-the-art power electronics systems for solar-to-grid integration. Sol. Energy 2020, 210, 128–148. [Google Scholar] [CrossRef]

- Hajiaghasi, S.; Salemnia, A.; Hamzeh, M. Hybrid energy storage system for microgrids applications: A review. J. Energy Storage 2019, 21, 543–570. [Google Scholar] [CrossRef]

- Bouguerra, S.; Yaiche, M.R.; Gassab, O.; Sangwongwanich, A.; Blaabjerg, F. The impact of PV panel positioning and degradation on the PV inverter lifetime and reliability. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 9, 3114–3126. [Google Scholar] [CrossRef]

- Rodriguez, C.; Amaratunga, G.A. Long-lifetime power inverter for photovoltaic AC modules. IEEE Trans. Ind. Electron. 2008, 55, 2593–2601. [Google Scholar] [CrossRef]

- Zhao, Z.; Davari, P.; Lu, W.; Wang, H.; Blaabjerg, F. An overview of condition monitoring techniques for capacitors in DC-link applications. IEEE Trans. Power Electron. 2020, 36, 3692–3716. [Google Scholar] [CrossRef]

- Ronanki, D.; Williamson, S.S. Failure prediction of submodule capacitors in modular multilevel converter by monitoring the intrinsic capacitor voltage fluctuations. IEEE Trans. Ind. Electron. 2019, 67, 2585–2594. [Google Scholar] [CrossRef]

- Basit, M.A.; Dilshad, S.; Badar, R.; Sami ur Rehman, S.M. Limitations, challenges, and solution approaches in grid-connected renewable energy systems. Int. J. Energy Res. 2020, 44, 4132–4162. [Google Scholar] [CrossRef]

- Kabalcı, E. Review on novel single-phase grid-connected solar inverters: Circuits and control methods. Sol. Energy 2020, 198, 247–274. [Google Scholar] [CrossRef]

- Kanathipan, K.; Lam, J. An Electrolytic Capacitor-Less PV Micro-Inverter Based on CLL Resonant Conversion with a Power Control Scheme Using Resonant Circuit Voltage Control Loops. CPSS Trans. Power Electron. Appl. 2022, 7, 139–149. [Google Scholar] [CrossRef]

- Liao, Z.; Gu, H.; Cao, C.; Chen, Z. Research on a single-stage isolated electrolytic capacitor-less LED driver. Optik 2021, 225, 165688. [Google Scholar] [CrossRef]

- Liao, Z.; Qiu, D.; Zhang, S.; Cao, C. New electrolytic capacitor-less LED driver based on model predictive control. Optik 2019, 199, 163324. [Google Scholar] [CrossRef]

- Ramos-Paja, C.A.; Danilo-Montoya, O.; Grisales-Noreña, L.F. Photovoltaic System for Microinverter Applications Based on a Non-Electrolytic-Capacitor Boost Converter and a Sliding-Mode Controller. Electronics 2022, 11, 2923. [Google Scholar] [CrossRef]

- Tausif, A.; Jung, H.; Choi, S. Single-stage isolated electrolytic capacitor-less ev onboard charger with power decoupling. CPSS Trans. Power Electron. Appl. 2019, 4, 30–39. [Google Scholar] [CrossRef]

- Chaturvedi, S.; Wang, M.; Fan, Y.; Fulwani, D.; Hollweg, G.V.; Khan, S.A.; Su, W. Control Methodologies to Mitigate and Regulate Second-Order Ripples in DC–AC Conversions and Microgrids: A Brief Review. Energies 2023, 16, 817. [Google Scholar] [CrossRef]

- Gautam, A.R.; Fulwani, D.M.; Makineni, R.R.; Rathore, A.K.; Singh, D. Control strategies and power decoupling topologies to mitigate 2ω-ripple in single-phase inverters: A review and open challenges. IEEE Access 2020, 8, 147533–147559. [Google Scholar] [CrossRef]

- Jia, G.; Chen, M.; Tang, S.; Zhang, C.; Zhu, G. Active power decoupling for a modified modular multilevel converter to decrease submodule capacitor voltage ripples and power losses. IEEE Trans. Power Electron. 2020, 36, 2835–2851. [Google Scholar] [CrossRef]

- Liu, Y.; Zhang, W.; Sun, Y.; Su, M.; Xu, G.; Dan, H. Review and comparison of control strategies in active power decoupling. IEEE Trans. Power Electron. 2021, 36, 14436–14455. [Google Scholar] [CrossRef]

- Neumayr, D.; Knabben, G.C.; Varescon, E.; Bortis, D.; Kolar, J.W. Comparative evaluation of a full-and partial-power processing active power buffer for ultracompact single-phase DC/AC converter systems. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 9, 1994–2013. [Google Scholar] [CrossRef]

- Qiu, M.; Wang, P.; Bi, H.; Wang, Z. Active power decoupling design of a single-phase AC–DC converter. Electronics 2019, 8, 841. [Google Scholar] [CrossRef]

- Sal y Rosas, D.; Zarate, A. Single-Phase Grid-Forming Strategy with Power Decoupling Implementation for Electrolytic-Capacitor-Free EV Smart Battery Charger. Energies 2023, 16, 894. [Google Scholar] [CrossRef]

- Wang, Y.; Wai, R.-J. Adaptive power decoupling strategy for single-phase grid-connected converter. IEEE Trans. Ind. Appl. 2019, 55, 4275–4285. [Google Scholar] [CrossRef]

- Yang, Z.; Zeng, J.; Zhang, Q.; Zhang, Z.; Winstead, V.; Yu, D. A composite power decoupling method for a PV inverter with optimized energy buffer. IEEE Trans. Ind. Appl. 2021, 57, 3877–3887. [Google Scholar] [CrossRef]

- Rodríguez-Benítez, O.M.; Aqui-Tapia, J.A.; Ortega-Velázquez, I.; Espinosa-Pérez, G. Current Source Topologies for Photovoltaic Applications: An Overview. Electronics 2022, 11, 2953. [Google Scholar] [CrossRef]

- Zhang, J.; Ding, H.; Wang, B.; Guo, X.; Padmanaban, S. Active power decoupling for current source converters: An overview scenario. Electronics 2019, 8, 197. [Google Scholar] [CrossRef]

- Vitorino, M.A.; Alves, L.F.S.; Wang, R.; de Rossiter Corrêa, M.B. Low-frequency power decoupling in single-phase applications: A comprehensive overview. IEEE Trans. Power Electron. 2016, 32, 2892–2912. [Google Scholar] [CrossRef]

- Nandi, P.; Adda, R. An Active Power Decoupling-integrated Reduced-Switch Current-Fed Switched Inverter. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 11, 1929–1942. [Google Scholar] [CrossRef]

- Xiong, J.; Zhang, J.; Xu, Z. Active power decoupling method for single-phase PWM converters without LC branch sensors. J. Power Electron. 2022, 22, 1188–1198. [Google Scholar] [CrossRef]

- Pan, X.; Li, H.; Liu, Y.; Zhao, T.; Ju, C.; Rathore, A.K. An overview and comprehensive comparative evaluation of current-fed-isolated-bidirectional DC/DC converter. IEEE Trans. Power Electron. 2019, 35, 2737–2763. [Google Scholar] [CrossRef]

- Isik, S.; Alharbi, M.; Bhattacharya, S. An optimized circulating current control method based on PR and PI controller for MMC applications. IEEE Trans. Ind. Appl. 2021, 57, 5074–5085. [Google Scholar] [CrossRef]

- Nassary, M.; Orabi, M.; Arias, M.; Ahmed, E.M.; Hasaneen, E.-S. Analysis and control of electrolytic capacitor-less LED driver based on harmonic injection technique. Energies 2018, 11, 3030. [Google Scholar] [CrossRef]

- Nassary, M.; Orabi, M.; Ahmed, E.M.; Hasaneen, E.-S.; Gaafar, M. Modified harmonic injection technique for electrolytic capacitor-less LED driver. In Proceedings of the 2017 Nineteenth International Middle East Power Systems Conference (MEPCON), Cairo, Egypt, 19–21 December 2017; pp. 1459–1464. [Google Scholar]

- Paul, A.R.; Bhattacharya, A.; Chatterjee, K. A Single Phase Grid Connected Boost/Buck-Boost Derived Solar PV Micro-inverter Topology Having Power Decoupling Capability. IEEE J. Emerg. Sel. Top. Power Electron. 2023, 11, 2340–2349. [Google Scholar] [CrossRef]

- Xu, S.; Shao, R.; Chang, L.; Mao, M. Single-phase differential buck–boost inverter with pulse energy modulation and power decoupling control. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 2060–2072. [Google Scholar] [CrossRef]

- Wang, B.; Ruan, X.; Yao, K.; Xu, M. A method of reducing the peak-to-average ratio of LED current for electrolytic capacitor-less AC–DC drivers. IEEE Trans. Power Electron. 2009, 25, 592–601. [Google Scholar] [CrossRef]

- de Freitas, I.S.; Brand, C.; dos Santos Jr, E.C. Single-phase to single-phase full-bridge converter operating with reduced ac power in the dc-link capacitor. IEEE Trans. Power Electron. 2009, 25, 272–279. [Google Scholar] [CrossRef]

- Gu, B.-G.; Nam, K. A DC-link capacitor minimization method through direct capacitor current control. IEEE Trans. Ind. Appl. 2006, 42, 573–581. [Google Scholar]

- Li, S.; Ozpineci, B.; Tolbert, L.M. Evaluation of a current source active power filter to reduce the dc bus capacitor in a hybrid electric vehicle traction drive. In Proceedings of the 2009 IEEE Energy Conversion Congress and Exposition, San Jose, CA, USA, 20–24 September 2009; pp. 1185–1190. [Google Scholar]

- Li, Z.; Yang, L.; Yang, D.; Peng, Z.; Shao, D.; Liu, J. Indirect current control method based on reference current compensation of an lcl-type grid-connected inverter. Energies 2022, 15, 965. [Google Scholar] [CrossRef]

- Yagoub, M.A.; Elserougi, A.A.; Abdelhamid, T.H. Closed-loop string current control for string optimizer circuits-based PV system to enhance extracted PV power during partial shading conditions. Alex. Eng. J. 2022, 61, 11159–11170. [Google Scholar] [CrossRef]

- Ronilaya, F.; Putri, R.I.; Hidayat, M.; Hermawan, N.; Ridzki, I.; Fadlika, I. A phase-based control method to control power flow of a grid-connected solar photovoltaics through a single phase micro-inverter. Int. J. Renew. Energy Res. 2020, 10, 912–921. [Google Scholar]

- Shimizu, T.; Wada, K.; Nakamura, N. Flyback-type single-phase utility interactive inverter with power pulsation decoupling on the DC input for an AC photovoltaic module system. IEEE Trans. Power Electron. 2006, 21, 1264–1272. [Google Scholar] [CrossRef]

- Chen, M.; Afridi, K.K.; Perreault, D.J. Stacked switched capacitor energy buffer architecture. IEEE Trans. Power Electron. 2013, 28, 5183–5195. [Google Scholar] [CrossRef]

- Tang, Y.; Chen, M.; Ran, L. A compact MMC submodule structure with reduced capacitor size using the stacked switched capacitor architecture. IEEE Trans. Power Electron. 2015, 31, 6920–6936. [Google Scholar] [CrossRef]

- Larsson, T.; Ostlund, S. Active DC link filter for two frequency electric locomotives. In Proceedings of the 1995 International Conference on Electric Railways in a United Europe, Amsterdam, The Netherlands, 27–30 March 1995; pp. 97–100. [Google Scholar]

- Krein, P.T.; Balog, R.S.; Mirjafari, M. Minimum energy and capacitance requirements for single-phase inverters and rectifiers using a ripple port. IEEE Trans. Power Electron. 2012, 27, 4690–4698. [Google Scholar] [CrossRef]

- Sun, Y.; Liu, Y.; Su, M.; Xiong, W.; Yang, J. Review of active power decoupling topologies in single-phase systems. IEEE Trans. Power Electron. 2015, 31, 4778–4794. [Google Scholar] [CrossRef]

- Xu, S.; Xue, Y.; Chang, L. Review of power system support functions for inverter-based distributed energy resources-standards, control algorithms, and trends. IEEE Open J. Power Electron. 2021, 2, 88–105. [Google Scholar] [CrossRef]

- Zhang, Y.; Xiong, J.; He, P.; Wang, S. Review of power decoupling methods for micro-inverters used in PV systems. Chin. J. Electr. Eng. 2018, 4, 26–32. [Google Scholar] [CrossRef]

- McHugh, C.; Sinha, S.; Meyer, J.; Pervaiz, S.; Lu, J.; Zhang, F.; Chen, H.; Kim, H.; Anwar, U.; Kumar, A. A high power density single-phase inverter using stacked switched capacitor energy buffer. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20 March 2016; pp. 1947–1953. [Google Scholar]

- Li, Y.; Chen, J.; John, M.; Liou, R.; Sanders, S.R. Resonant switched capacitor stacked topology enabling high DC-DC voltage conversion ratios and efficient wide range regulation. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Long Beach, CA, USA, 20–24 March 2016; pp. 1–7. [Google Scholar]

- Chang, A.H.; Leeb, S.B. Improved transient response control strategy and design considerations for switched-capacitor (SC) energy buffer architectures. In Proceedings of the 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 17–21 March 2013; pp. 281–290. [Google Scholar]

- Pervaiz, S.; Ni, Y.; Afridi, K.K. Improved capacitance ratio optimization methodology for stacked switched capacitor energy buffers. In Proceedings of the 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015; pp. 513–520. [Google Scholar]

- Chen, M.; Ni, Y.; Serrano, C.; Montgomery, B.; Perreault, D.; Afridi, K. An electrolytic-free offline LED driver with a ceramic-capacitor-based compact SSC energy buffer. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 2713–2718. [Google Scholar]

- Ni, Y.; Pervaiz, S.; Chen, M.; Afridi, K.K. Energy density enhancement of unipolar SSC energy buffers through capacitance ratio optimization. In Proceedings of the 2014 IEEE 15th Workshop on Control and Modeling for Power Electronics (COMPEL), Santander, Spain, 22–25 June 2014; pp. 1–8. [Google Scholar]

- Ni, Y. Design of Stacked Switched Capacitor Energy Buffers for offline LED Drivers. Ph.D. Thesis, University of Colorado at Boulder, Boulder, CO, USA, 2014. [Google Scholar]

- Pervaiz, S.; Kumar, A.; Afridi, K.K. GaN-based high-power-density electrolytic-free universal input LED driver. IEEE Trans. Ind. Appl. 2018, 54, 3890–3901. [Google Scholar] [CrossRef]

- Li, H.; Zhang, K.; Zhao, H.; Fan, S.; Xiong, J. Active power decoupling for high-power single-phase PWM rectifiers. IEEE Trans. Power Electron. 2012, 28, 1308–1319. [Google Scholar] [CrossRef]

- Chen, R.; Liu, Y.; Peng, F.Z. DC capacitor-less inverter for single-phase power conversion with minimum voltage and current stress. IEEE Trans. Power Electron. 2014, 30, 5499–5507. [Google Scholar] [CrossRef]

- Wang, R.; Wang, F.; Lai, R.; Ning, P.; Burgos, R.; Boroyevich, D. Study of energy storage capacitor reduction for single phase PWM rectifier. In Proceedings of the 2009 Twenty-Fourth Annual IEEE Applied Power Electronics Conference and Exposition, Washington, DC, USA, 15–19 February 2009; pp. 1177–1183. [Google Scholar]

- Feng, Y.; Konstantinou, G.; Hredzak, B.; Fletcher, J.; Sun, K. Topologies for reduction of second harmonic ripple in battery energy storage systems. In Proceedings of the 2019 IEEE 10th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Xi’an, China, 3–6 June 2019; pp. 414–419. [Google Scholar]

- MOUNIKA, K.; LALITHA, S.V. Single-Phase Inverter using Stacked Switched Capacitor Energy Buffer with EMI Filter. Int. J. Adv. Technol. Innov. Res. 2017, 9, 2429–2433. [Google Scholar]

- Nauman, A. Stacked switched capacitor architecture using electrolytic capacitors for size reduction. In Proceedings of the 2016 IEEE 7th Power India International Conference (PIICON), Bikaner, India, 25–27 November 2016; pp. 1–5. [Google Scholar]

- Ni, Y.; Pervaiz, S.; Chen, M.; Afridi, K.K. Energy density enhancement of stacked switched capacitor energy buffers through capacitance ratio optimization. IEEE Trans. Power Electron. 2016, 32, 6363–6380. [Google Scholar] [CrossRef]

- Li, Y.; Gu, L.; Hariya, A.; Ishizuka, Y.; Rivas-Davila, J.; Sanders, S. A wide input range isolated stacked resonant switched-capacitor dc-dc converter for high conversion ratios. In Proceedings of the 2018 IEEE 19th Workshop on Control and Modeling for Power Electronics (COMPEL), Padova, Italy, 25–28 June 2018; pp. 1–7. [Google Scholar]

- Afridi, K.K.; Chen, M.; Perreault, D.J. Enhanced bipolar stacked switched capacitor energy buffers. IEEE Trans. Ind. Appl. 2013, 50, 1141–1149. [Google Scholar] [CrossRef]

- Pervaiz, S.; Kumar, A.; Afridi, K.K. A compact electrolytic-free two-stage universal input offline LED driver with volume-optimized SSC energy buffer. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 1116–1130. [Google Scholar] [CrossRef]

- Yang, J.; Yu, D.; Cheng, H.; Zan, X.; Wen, H. Dual-coupled inductors-based high step-up DC/DC converter without input electrolytic capacitor for PV application. IET Power Electron. 2017, 10, 646–656. [Google Scholar] [CrossRef]

- Chen, R.; Liu, Y.; Peng, F.Z. A solid state variable capacitor with minimum capacitor. IEEE Trans. Power Electron. 2017, 32, 5035–5044. [Google Scholar] [CrossRef]

- Bush, C.R.; Wang, B. A single-phase current source solar inverter with reduced-size DC link. In Proceedings of the 2009 IEEE Energy Conversion Congress and Exposition, San Jose, CA, USA, 20–24 September 2009; pp. 54–59. [Google Scholar]

- Tang, Y.; Blaabjerg, F. A component-minimized single-phase active power decoupling circuit with reduced current stress to semiconductor switches. IEEE Trans. Power Electron. 2014, 30, 2905–2910. [Google Scholar] [CrossRef]

- Wang, R.; Wang, F.; Boroyevich, D.; Burgos, R.; Lai, R.; Ning, P.; Rajashekara, K. A high power density single-phase PWM rectifier with active ripple energy storage. IEEE Trans. Power Electron. 2010, 26, 1430–1443. [Google Scholar] [CrossRef]

- Hwang, D.-H.; Lee, J.-Y.; Cho, Y. PCC voltage compensation of PV inverter with active power decoupling circuit. In Proceedings of the 2018 International Power Electronics Conference (IPEC-Niigata 2018-ECCE Asia), Niigata, Japan, 20–24 May 2018; pp. 1403–1408. [Google Scholar]

- Fan, S.; Xue, Y.; Zhang, K. A novel active power decoupling method for single-phase photovoltaic or energy storage applications. In Proceedings of the 2012 IEEE Energy Conversion Congress and Exposition (ECCE), Raleigh, NC, USA, 15 September 2012; pp. 2439–2446. [Google Scholar]

- Salazar-Pérez, D.; Ponce-Silva, M.; Alonso, J.M.; Aquí-Tapia, J.A.; Cortés-García, C. A novel high-power-factor electrolytic-capacitorless LED driver based on ripple port. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 6248–6258. [Google Scholar] [CrossRef]

- Harb, S.; Zhang, H.; Balog, R.S. AC-link, single-phase, photovoltaic Module Integrated Inverter. In Proceedings of the 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 17–21 March 2013; pp. 177–182. [Google Scholar]

- Harb, S.; Mirjafari, M.; Balog, R.S. Ripple-port module-integrated inverter for grid-connected PV applications. IEEE Trans. Ind. Appl. 2013, 49, 2692–2698. [Google Scholar] [CrossRef]

- Harb, S.; Balog, R.S. Single-phase PWM rectifier with power decoupling ripple-port for double-line-frequency ripple cancellation. In Proceedings of the 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 17–21 March 2013; pp. 1025–1029. [Google Scholar]

- Chen, Z.; Wu, Q.; Li, M.; Xu, Y.; Wang, Q. A three-port DC-DC converter with low frequency current ripple reduction technique. In Proceedings of the 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015; pp. 2069–2074. [Google Scholar]

- Alsolami, M. Active Power Decoupling for Single-Phase Grid-Connected PV System using a Ripple Port. Arab. J. Sci. Eng. 2021, 46, 9981–9993. [Google Scholar] [CrossRef]

- Kim, J.-G.; Kim, K.-D.; Noh, Y.-S.; Jung, Y.-C.; Won, C.-Y. Analysis and design of a three-port flyback inverter using an active power decoupling method to minimize input capacitance. J. Power Electron. 2013, 13, 558–568. [Google Scholar] [CrossRef]

- Metry, M.; Kim, M.; Rohouma, W.; Balog, R.S. Model predictive control based controller for grid-connected ripple-port inverters. In Proceedings of the 2020 IEEE 21st Workshop on Control and Modeling for Power Electronics (COMPEL), Aalborg, Denmark, 9–12 November 2020; pp. 1–6. [Google Scholar]

- Tian, B.; Harb, S.; Balog, R.S. Ripple-port integrated PFC rectifier with fast dynamic response. In Proceedings of the 2014 IEEE 57th International Midwest Symposium on Circuits and Systems (MWSCAS), College Station, TX, USA, 3–6 August 2014; pp. 781–784. [Google Scholar]

- Hu, H.; Harb, S.; Fang, X.; Zhang, D.; Zhang, Q.; Shen, Z.J.; Batarseh, I. A three-port flyback for PV microinverter applications with power pulsation decoupling capability. IEEE Trans. Power Electron. 2012, 27, 3953–3964. [Google Scholar] [CrossRef]

| Ref. | P (kW) | η (%) | (Vpp) | (Rc) (µF) | (Rec) (µF) | (Redc) | Comments |

|---|---|---|---|---|---|---|---|

| [46] | 0.135 | 95.2 | 32 | 34.97 | 17.6 | 1.98 | The objective is to restrict the apparent voltage ripple while utilizing a large fraction of the energy in the capacitors. |

| [47] | 92 | - | 10 | 1248 | 624 | 2 | Fewer power losses and a reduction of 60% in passive volume. |

| [53] | 2 | 90 | 1.5 | 7200 | 960 | 7.5 | The physical volume of the system decreased from 40 to 17 in3. |

| [57] | 0.008 | 98 | 21 | 720 | 560 | 1.2 | Presents a methodology optimization for increasing the energy density. |

| [68] | 0.06 | 93 | 5 | 141 | 47.2 | 3 | Wide dimming range with combined frequency and selective phase shift tuning. |

| [69] | 0.135 | 97.2 | 32 | 40 | 17.6 | 2.2 | Achieves higher effective energy density and round-trip efficiency by modifying the control and switching patterns, maintaining the bus voltage ripple ratio, and applying fewer capacitors and switches than similar architectures. |

| [70] | 0.3 | 98.5 | 20 | 980 | 280 | 3.5 | Presents an improved closed-loop capacitance ratio optimization methodology. |

| Advantages | Disadvantages |

|---|---|

| Can significantly reduce the capacitor size in a single-phase system. | Needs many switches and capacitors to maintain a narrow-range bus voltage while achieving high energy utilization. |

| Is effective in low-voltage, low-power DC–AC and AC-DC applications. | Presents more complexity. |

| The overall volume is much smaller. | It is crucial to identify the capacitance ratio that results in the highest effective energy density for a given SSC energy buffer topology. |

| Maintains a small DC-link voltage. | Commonly, the number of capacitors used has a stronger effect on the failure rate than the value of the capacitance itself. |

| Energy density can be almost doubled. | |

| Enables better capacitor reduction performance. | |

| Achieves higher energy efficiency conversion than magnetic passive solutions. | |

| Eliminates the need for inductors (eliminating magnetic losses). | |

| Utilizes relatively low blocking voltage switches (reducing conduction losses). | |

| Commutes at low multiples of the line frequency (minimizing switching losses). | |

| Presents a high-energy buffering capability. | |

| The energy buffer achieves a smaller bus voltage or a higher energy buffering ratio. |

| Ref. | P (kW) | η (%) | (Vpp) | (Rc) (µF) | (Rec) (µF) | (Redc) | Comments |

|---|---|---|---|---|---|---|---|

| [61] | 4 | -- | 14.2 | 2025 | 440 | 4.6 | Complex control, full utilization of capacitor energy. |

| [74] | 1 | 93.7 | 10 | 757 | 180 | 4.2 | Big inductance is used as filter, power density is reduced. |

| [75] | 15 | 93.2 | 28 | 1600 | 300 | 5.33 | DC capacitor reduction is not remarkable. |

| [72] | 1.5 | 92 | 5 | 4600 | 385 | 11.94 | Complex control, operation is limited to the resonant controller. |

| [76] | -- | -- | 10 | -- | 310 | -- | Half-bridge plus two capacitors and one inductor are used. Power density is reduced. |

| [77] | 1 | -- | 8 | 1658 | 132 | 12.5 | Capacitance reduction is considerably reduced. |

| Advantages | Disadvantages |

|---|---|

| Capacitance is reduced by approximately 13 times as compared to using an electrolytic capacitor. | Control complex. |

| Current and voltage stress in switches can be reduced. | A dual loop with an outer voltage loop and an inner current loop is necessary for the control. |

| Stable DC voltage and fast dynamic response. | To minimize the voltage and current stress is necessary to adopt SPWM. |

| The proposed control can be extended to other single-phase power applications. | |

| The minimum energy storage in the capacitor is minimum Ecmin. |

| Ref. | P (kW) | η (%) | (Vpp) | (Rc) (µF) | (Rec) (µF) | (Redc) | Comments |

|---|---|---|---|---|---|---|---|

| [79] | 0.2 | 95.6 | 1.25 | 1700 | 150 | 11.33 | This proposal can increase the power density; however, additional component cost is added. |

| [80] | 0.23 | - | 12 | 200 | 100 | 2 | Easy control stage by applying the SPWM modulation. |

| [81] | 0.1 | - | 8 | 1330 | 220 | 6 | The design and control are easy. |

| [85] | 0.5 | - | 20 | 156 | 14 | 11.1 | Controlled using a modulator-based regulator, requires multiple control loops and tuning numerous gains. |

| [86] | 0.16 | 90 | 5.5 | 200 | 150 | 1.3 | Closed-loop strategy implemented, which guarantees the ripple cancellation even under time-varied conditions. |

| Advantages | Disadvantages |

|---|---|

| The interface of the grid network can be performed by thyristors. | Introduces substantial implementation complexity. |

| The control stage at a closed loop is simpler than other APD techniques. | Potential added cost. |

| Reduces the size of the overall system by eliminating a rectifier stage. | |

| Can support inverter and rectifier applications. | |

| Increases the MPPT performance in the PV-connected system. | |

| Achieves the minimum possible capacitance value in a determined application since energy storage is addressed directly. | |

| Is controlled directly to achieve the desired double-frequency value. | |

| The decoupling capacitor voltage is independent of other system voltages. | |

| Permits direct control of the ripple power, allowing direct control over the coupling capacitor voltage and current. | |

| Avoids voltage limitations of the DC–DC topology. |

| Ref. | Type of Method | Topology | Dca (μF) | P (W) | fsw (kHz) | E (J) | η (%) | Vdc (V) | Additional Elements | Features |

|---|---|---|---|---|---|---|---|---|---|---|

| [80] | RP-MII | Flyback | 36 | 235 | 100 | 0.72 | -- | 200 | 4 MOSFETs, 1 inductor, and 1 capacitor. | Simple control; ripple current suppression to less than 10% peak-to-peak. |

| [81] | Full-bridge inverter | 220 | 100 | 100 | 0.352 | -- | 200 | 4 MOSFETs, 1 inductor, and 1 capacitor. | The design and control are easy and affordable. | |

| [85] | Flyback | 14 | 500 | 40 | 0.077 | -- | 250 | 4 MOSFETs, 1 inductor, and 1 capacitor. | The control requires multiple control loops and tuning numerous gains. | |

| [53] | SSC | Single-phase inverter | 80 | 2000 | -- | 0.048 | 90 | 400 | 16 switches and 11 capacitor. | DC–AC conversion, high-frequency operation, and SiC-MOSFET solution by applying variable-frequency constant peak current control. |

| [65] | Single-phase inverter | -- | 2000 | -- | -- | 90 | -- | -- | Advanced implementation of the SSC architecture, soft-switching SiC-FET DC–AC conversion, and digitally implemented variable-frequency constant peak current control. | |

| [87] | Flyback | 46 | 110 | 50 | 0.29 | 90.6 | 150 | 5 MOSFETs and 2 capacitors. | The transformer leakage energy is stored in the decoupling capacitor with minimal added components. | |

| [74] | VCAPD | Single-phase inverter | 180 | 1000 | 19.2 | 0.63 | 93.7 | 350 | 1 capacitor and 1 inductor. | The capacitance is considerably reduced. |

| [72] | Single-phase inverter | 385 | 1500 | 10.8 | 1.33 | 92 | 200 | 2 MOSFETs, 1 inductor, and 1 capacitor. | The control is complex, and the operation is limited to the resonant controller. |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Rodríguez-Benítez, O.; Ponce-Silva, M.; Aqui-Tapia, J.A.; Rodríguez-Benítez, Ó.M.; Lozoya-Ponce, R.E.; Adamas-Pérez, H. Active Power-Decoupling Methods for Photovoltaic-Connected Applications: An Overview. Processes 2023, 11, 1808. https://doi.org/10.3390/pr11061808

Rodríguez-Benítez O, Ponce-Silva M, Aqui-Tapia JA, Rodríguez-Benítez ÓM, Lozoya-Ponce RE, Adamas-Pérez H. Active Power-Decoupling Methods for Photovoltaic-Connected Applications: An Overview. Processes. 2023; 11(6):1808. https://doi.org/10.3390/pr11061808

Chicago/Turabian StyleRodríguez-Benítez, Omar, Mario Ponce-Silva, Juan Antonio Aqui-Tapia, Óscar Miguel Rodríguez-Benítez, Ricardo Eliú Lozoya-Ponce, and Heriberto Adamas-Pérez. 2023. "Active Power-Decoupling Methods for Photovoltaic-Connected Applications: An Overview" Processes 11, no. 6: 1808. https://doi.org/10.3390/pr11061808

APA StyleRodríguez-Benítez, O., Ponce-Silva, M., Aqui-Tapia, J. A., Rodríguez-Benítez, Ó. M., Lozoya-Ponce, R. E., & Adamas-Pérez, H. (2023). Active Power-Decoupling Methods for Photovoltaic-Connected Applications: An Overview. Processes, 11(6), 1808. https://doi.org/10.3390/pr11061808