Three-Dimensional TID Hardening Design for 14 nm Node SOI FinFETs

Abstract

:1. Introduction

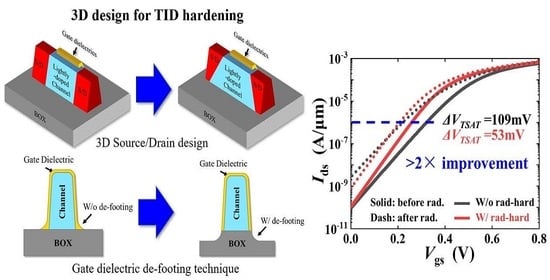

2. 3D Design for TID Hardening

3. Results and Analysis

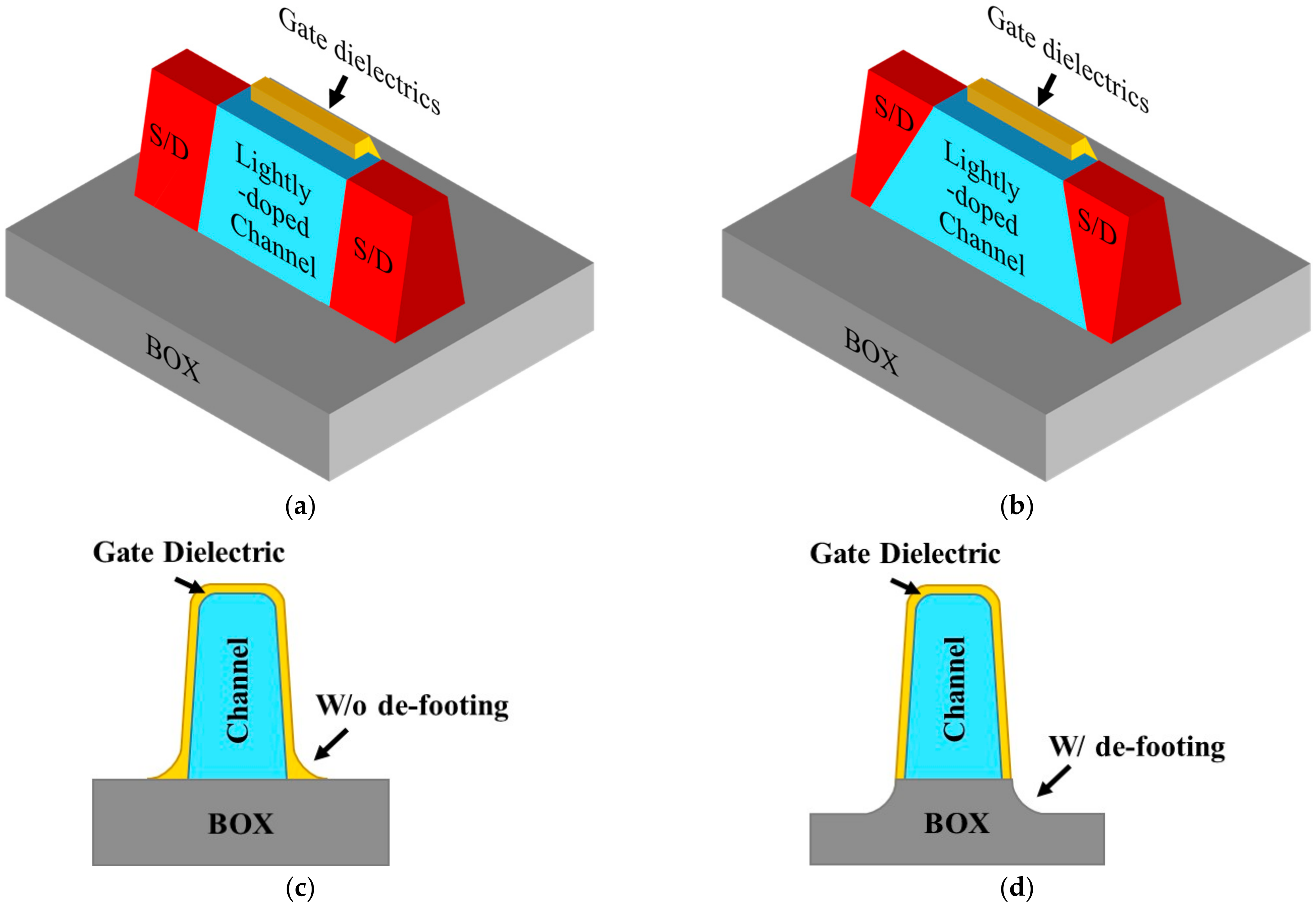

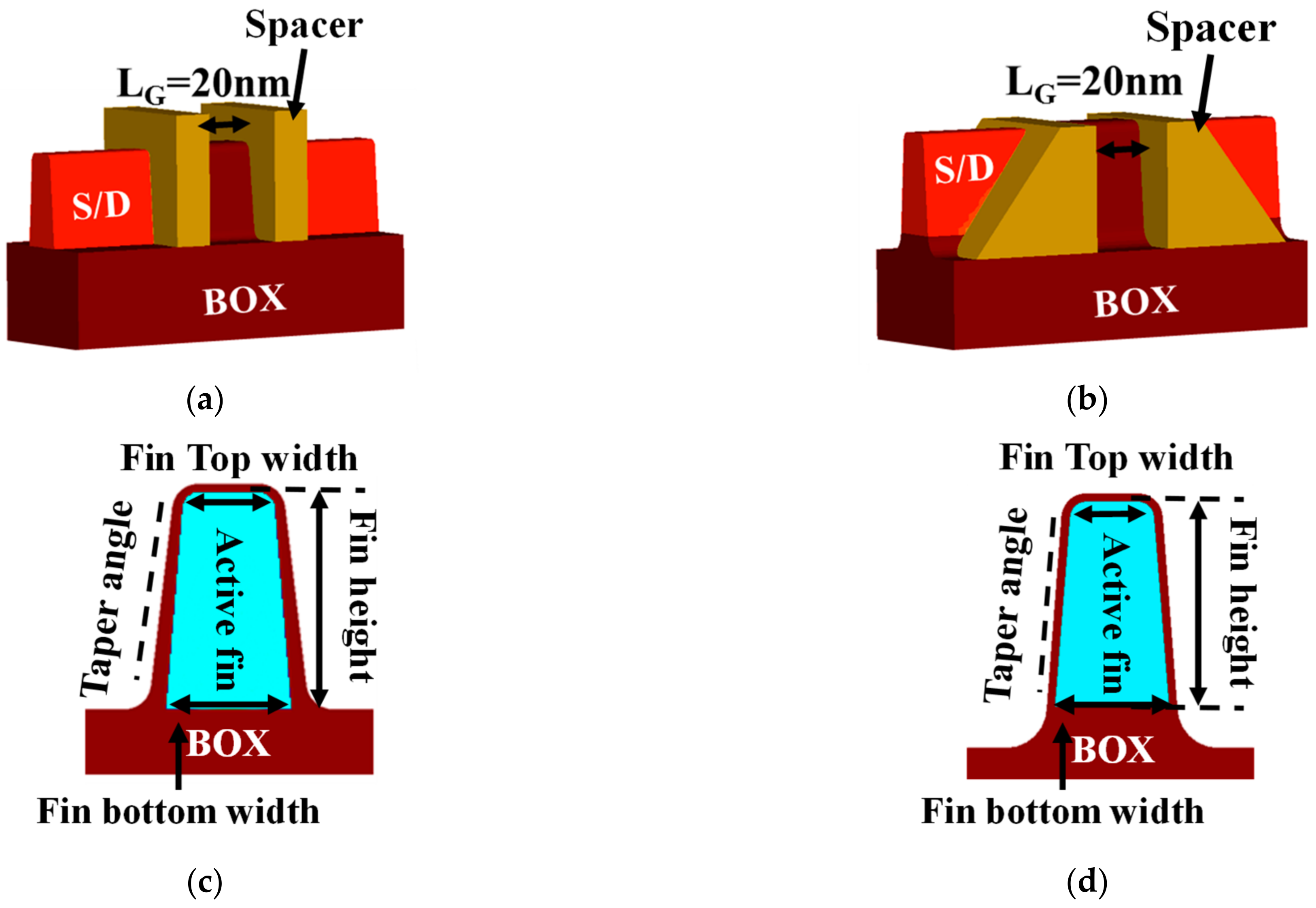

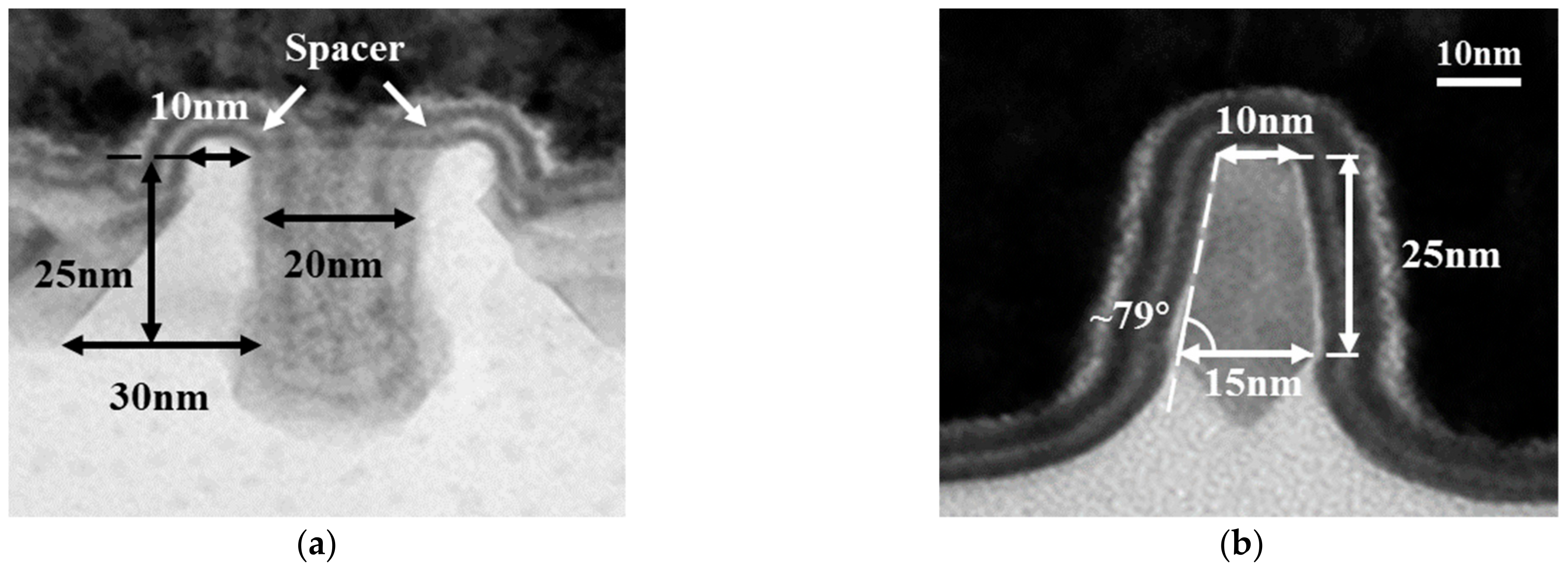

3.1. Structure Setup for TID Hardening Evaluation

3.2. Physical Model Setup

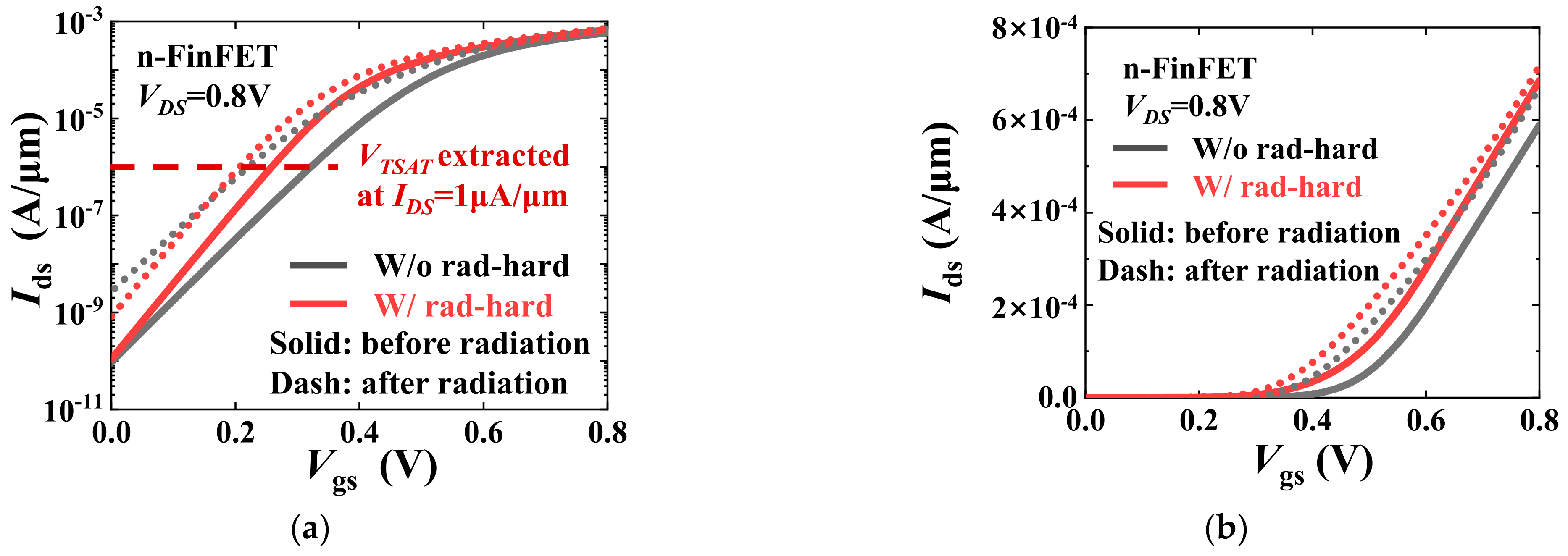

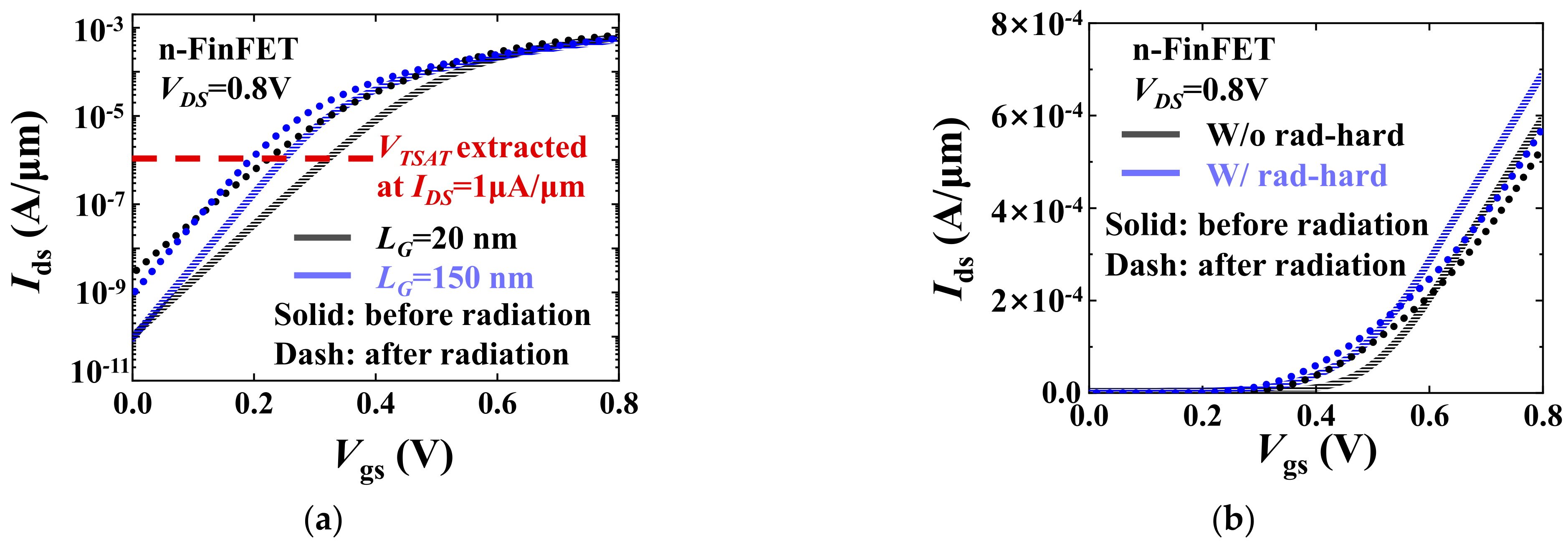

3.3. TID Hardening Result

3.4. Analysis and Discussion

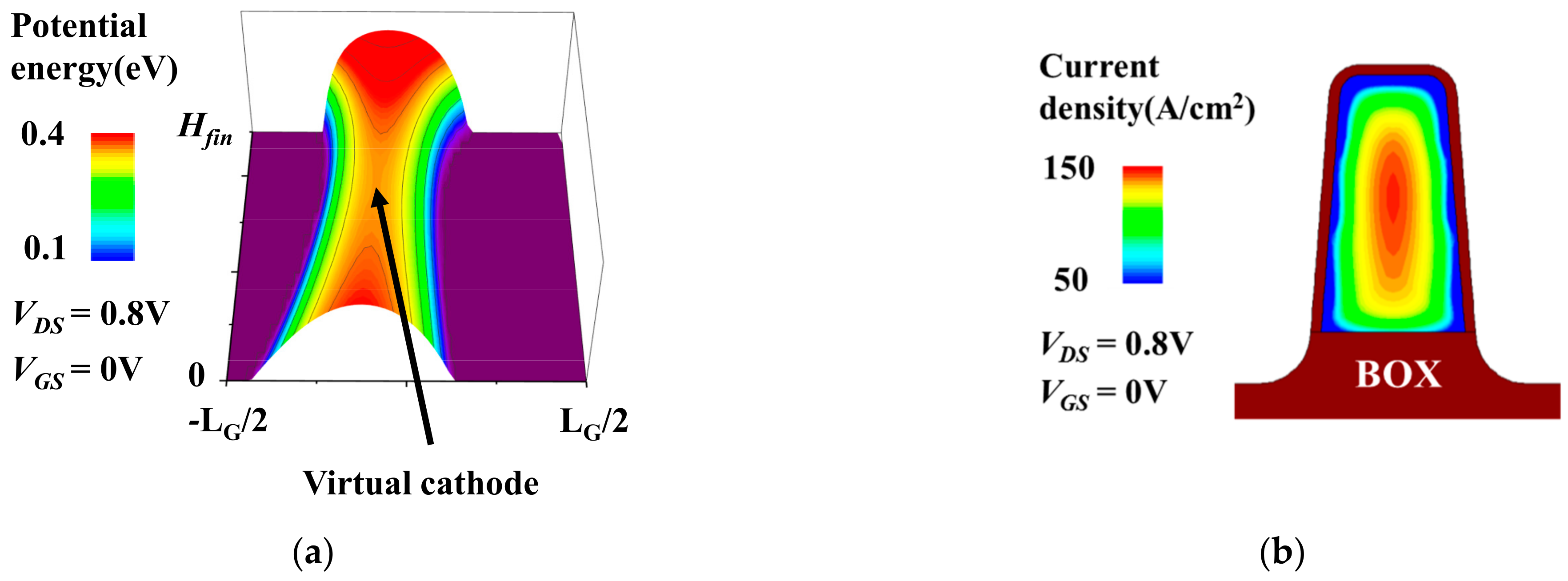

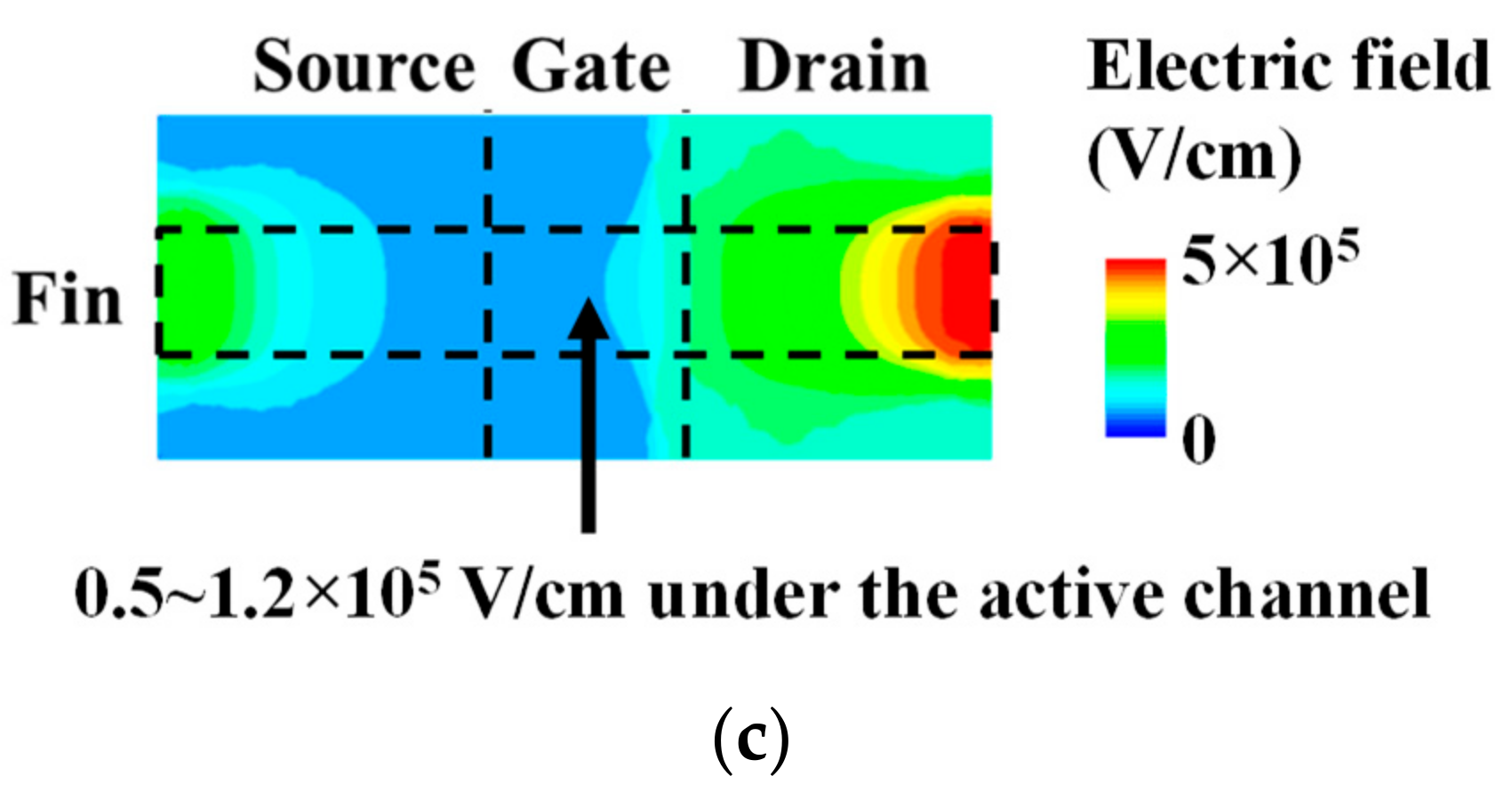

3.4.1. TID Effect’s Mechanism in SOI FinFETs

3.4.2. TID Hardening Methodology

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Acknowledgments

Conflicts of Interest

References

- Jan, C.-H.; Bhattacharya, U.; Brain, R.; Choi, S.-J.; Curello, G.; Gupta, G.; Hafez, W.; Jang, M.; Kang, M.; Komeyli, K.; et al. A 22nm SoC platform technology featuring 3-D tri-gate and high-k/metal gate, optimized for ultra low power, high performance and high density SoC applications. In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012; pp. 3.1.1–3.1.4. [Google Scholar] [CrossRef]

- Natarajan, S.; Agostinelli, M.; Akbar, S.; Bost, M.; Bowonder, A.; Chikarmane, V.; Chouksey, S.; Dasgupta, A.; Fischer, K.; Fu, Q.; et al. A 14nm logic technology featuring 2nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 m2 SRAM cell size. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 3.7.1–3.7.3. [Google Scholar] [CrossRef]

- Auth, C.; Aliyarukunju, A.; Asoro, M.; Bergstrom, D.; Bhagwat, V.; Birdsall, J.; Bisnik, N.; Buehler, M.; Chikarmane, V.; Ding, G.; et al. A 10nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, Self-Aligned Quad Patterning, contact over active gate and cobalt local interconnects. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 29.1.1–29.1.4. [Google Scholar] [CrossRef]

- Hashemi, P.; Balakrishnan, K.; Majumdar, A.; Khakifirooz, A.; Kim, W.; Baraskar, A.; Yang, L.A.; Chan, K.; Engelmann, S.U.; Ott, J.A.; et al. Strained Si1xGex-on-insulator PMOS FinFETs with excellent sub-threshold leakage, extremely-high short-channel performance and source injection velocity for 10nm node and beyond. In Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014; pp. 1–2. [Google Scholar] [CrossRef]

- Liu, J.; Mukhopadhyay, S.; Kundu, A.; Chen, S.; Wang, H.; Huang, D.; Lee, J.; Wang, M.; Lu, R.; Lin, S.; et al. A Reliability Enhanced 5nm CMOS Technology Featuring 5th Generation FinFET with Fully-Developed EUV and High Mobility Channel for Mobile SoC and High Performance Computing Application. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020; pp. 9.2.1–9.2.4. [Google Scholar] [CrossRef]

- Yonghong, L.; Chaohui, H.; Fazhan, Z.; Tianlei, G.; Gang, L.; Zhengsheng, H.; Jie, L.; Gang, G. Experimental study on heavy ion single event effects in SOI SRAMs. Nucl. Instrum. Methods Phys. Res. Sect. B Beam Interact. Mater. Atoms 2009, 267, 83–86. [Google Scholar] [CrossRef]

- Li, G.; An, X.; Ren, Z.; Wang, J.; Huang, R. Investigation on Impact of Fin Width on Single-Event-Transient in Bulk and SOI FinFETs. In Proceedings of the 2018 14th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Qingdao, China, 31 October–3 November 2018; pp. 1–3. [Google Scholar] [CrossRef]

- Hughes, H.; McMarr, P.; Alles, M.; Zhang, E.; Arutt, C.; Doris, B.; Liu, D.; Southwick, R.; Oldiges, P. Total Ionizing Dose Radiation Effects on 14 nm FinFET and SOI UTBB Technologies. In Proceedings of the 2015 IEEE Radiation Effects Data Workshop (REDW), Boston, MA, USA, 13–17 July 2015; pp. 1–6. [Google Scholar] [CrossRef] [Green Version]

- Tan, F.; Huang, R.; An, X.; Wu, W.; Feng, H.; Huang, L.; Fan, J.; Zhang, X.; Wang, Y. Total ionizing dose (TID) effect and single event effect (SEE) in quasi-SOI nMOSFETs. Semicond. Sci. Technol. 2013, 29, 015010. [Google Scholar] [CrossRef]

- Rezzak, N.; Zhang, E.X.; Ball, D.R.; Alles, M.L.; Loveless, T.D.; Schrimpf, R.D.; Rodbell, K. Total-ionizing-dose radiation response of 32 nm partially and 45 nm fully-depleted SOI devices. In Proceedings of the 2012 IEEE International SOI Conference (SOI), Napa, CA, USA, 1–4 October 2012; pp. 1–2. [Google Scholar] [CrossRef]

- Domae, Y.; Komatsubara, H.; Shindou, H.; Makihara, A.; Kuboyama, S.; Ida, J. Improvement of the tolerance to total ionizing dose in SOI CMOS. In Proceedings of the 2008 IEEE International SOI Conference, New Paltz, NY, USA, 6–9 October 2008; pp. 135–136. [Google Scholar]

- Li, B.; Huang, Y.; Wu, J.; Zhang, Q.; Yang, L.; Wan, F.; Luo, J.; Han, Z.; Yin, H. Constant voltage stress characterization of nFinFET transistor during total ionizing dose experiment. Microelectron. Reliab. 2018, 88–90, 969–973. [Google Scholar] [CrossRef]

- Ren, Z.; An, X.; Li, G.; Chen, G.; Li, M.; Yu, G.; Guo, Q.; Zhang, X.; Huang, R. TID Response of Bulk Si PMOS FinFETs: Bias, Fin Width, and Orientation Dependence. IEEE Trans. Nucl. Sci. 2020, 67, 1320–1325. [Google Scholar] [CrossRef]

- Moon, J.-B.; Moon, D.-I.; Choi, Y.-K. Influence of Total Ionizing Dose on Sub-100 nm Gate-All-Around MOSFETs. IEEE Trans. Nucl. Sci. 2014, 61, 1420–1425. [Google Scholar] [CrossRef]

- Huang, Y.; Li, B.; Zhao, X.; Zheng, Z.; Gao, J.; Zhang, G.; Li, B.; Zhang, G.; Tang, K.; Han, Z.; et al. An Effective Method to Compensate Total Ionizing Dose-Induced Degradation on Double-SOI Structure. IEEE Trans. Nucl. Sci. 2018, 65, 1532–1539. [Google Scholar] [CrossRef]

- Gaillardin, M.; Martinez, M.; Paillet, P.; Raine, M.; Andrieu, F.; Faynot, O.; Thomas, O. Total Ionizing Dose Effects Mitigation Strategy for Nanoscaled FDSOI Technologies. IEEE Trans. Nucl. Sci. 2014, 61, 3023–3029. [Google Scholar] [CrossRef]

- Roh, Y.T.; Lee, H.C. Layout Modification of a PD-SOI n-MOSFET for Total Ionizing Dose Effect Hardening. IEEE Trans. Electron Devices 2018, 66, 308–315. [Google Scholar] [CrossRef]

- Liu, C.; Zhu, H.; Xie, X.; Hu, Z.; Bi, D.; Zhang, Z.; Zou, S. Investigation of Radiation Hardening by Back-Channel Adjustment in PDSOI MOSFETs. IEEE Trans. Nucl. Sci. 2021, 68, 2609–2615. [Google Scholar] [CrossRef]

- Peng, C.; Hu, Z.; En, Y.; Chen, Y.; Lei, Z.; Zhang, Z.; Zhang, Z.; Li, B. Radiation Hardening by the Modification of Shallow Trench Isolation Process in Partially Depleted SOI MOSFETs. IEEE Trans. Nucl. Sci. 2018, 65, 877–883. [Google Scholar] [CrossRef]

- Li, B.; Wu, J.; Gao, J.; Kuang, Y.; Li, J.; Zhao, X.; Zhao, K.; Han, Z.; Luo, J. The total ionizing dose response of a DSOI 4Kb SRAM. Microelectron. Reliab. 2017, 76–77, 714–718. [Google Scholar] [CrossRef]

- Li, B.; Zhao, K.; Wu, J.; Zhao, X.; Su, J.; Gao, J.; Gao, C.; Luo, J. Electromagnetic susceptibility characterization of double SOI device. Microelectron. Reliab. 2016, 64, 168–171. [Google Scholar] [CrossRef]

- Chatterjee, I.; Zhang, E.X.; Bhuva, B.L.; Reed, R.A.; Alles, M.L.; Mahatme, N.N.; Ball, D.R.; Schrimpf, R.D.; Fleetwood, D.M.; Linten, D.; et al. Geometry Dependence of Total-Dose Effects in Bulk FinFETs. IEEE Trans. Nucl. Sci. 2014, 61, 2951–2958. [Google Scholar] [CrossRef]

- Duan, G.X.; Zhang, C.X.; Zhang, E.X.; Hachtel, J.; Fleetwood, D.M.; Schrimpf, R.D.; Reed, R.A.; Alles, M.L.; Pantelides, S.T.; Bersuker, G.; et al. Bias Dependence of Total Ionizing Dose Effects in SiGe-MOS FinFETs. IEEE Trans. Nucl. Sci. 2014, 61, 2834–2838. [Google Scholar] [CrossRef]

- Riffaud, J.; Gaillardin, M.; Marcandella, C.; Martinez, M.; Paillet, P.; Duhamel, O.; Lagutere, T.; Raine, M.; Richard, N.; Andrieu, F.; et al. Investigations on the Geometry Effects and Bias Configuration on the TID Response of nMOS SOI Tri-Gate Nanowire Field-Effect Transistors. IEEE Trans. Nucl. Sci. 2017, 65, 39–45. [Google Scholar] [CrossRef]

- Zhang, Q.; Yin, H.; Luo, J.; Yang, H.; Meng, L.; Li, Y.; Wu, Z.; Zhang, Y.; Zhang, Y.; Qin, C.; et al. FOI FinFET with ultra-low parasitic resistance enabled by fully metallic source and drain formation on isolated bulk-fin. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 17.3.1–17.3.4. [Google Scholar] [CrossRef]

- Li, B.; Huang, Y.-B.; Yang, L.; Zhang, Q.-Z.; Zheng, Z.-S.; Zhu, H.-P.; Bu, J.-H.; Yin, H.-X.; Luo, J.-J.; Han, Z.-S.; et al. Process variation dependence of total ionizing dose effects in bulk nFinFETs. Microelectron. Reliab. 2018, 88–90, 946–951. [Google Scholar] [CrossRef]

- Mochizuki, S.; Colombeau, B.; Yu, L.; Dube, A.; Choi, S.; Stolfi, M.; Bi, Z.; Chang, F.; Conti, R.A.; Liu, P.; et al. Advanced Arsenic Doped Epitaxial Growth for Source Drain Extension Formation in Scaled FinFET Devices. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 35.2.1–35.2.4. [Google Scholar] [CrossRef]

- Badran, M.S.; Issa, H.H.; Eisa, S.M.; Ragai, H. Low Leakage Current Symmetrical Dual-k 7 nm Trigate Bulk Underlap FinFET for Ultra Low Power Applications. IEEE Access 2019, 7, 17256–17262. [Google Scholar] [CrossRef]

- Yoon, J.-S.; Jeong, J.; Lee, S.; Baek, R.-H. Sensitivity of Source/Drain Critical Dimension Variations for Sub-5-nm Node Fin and Nanosheet FETs. IEEE Trans. Electron Devices 2020, 67, 258–262. [Google Scholar] [CrossRef]

- Liang, X.; Taur, Y. A 2-D Analytical Solution for SCEs in DG MOSFETs. IEEE Trans. Electron Devices 2004, 51, 1385–1391. [Google Scholar] [CrossRef]

- Seo, K.-I.; Haran, B.; Gupta, D.; Guo, D.; Standaert, T.; Xie, R.; Shang, H.; Alptekin, E.; Bae, D.-I.; Bae, G.; et al. A 10nm platform technology for low power and high performance application featuring FINFET devices with multi workfunction gate stack on bulk and SOI. In Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014; pp. 1–2. [Google Scholar] [CrossRef]

- Synopsys Inc. Sentaurus User’s Manual; Synopsys: Mountain View, CA, USA, 2018. [Google Scholar]

- Granzner, R.; Polyakov, V.; Schwierz, F.; Kittler, M.; Luyken, R.; Rösner, W.; Städele, M. Simulation of nanoscale MOSFETs using modified drift-diffusion and hydrodynamic models and comparison with Monte Carlo results. Microelectron. Eng. 2006, 83, 241–246. [Google Scholar] [CrossRef]

- Tsutsui, G.; Saitoh, M.; Saraya, T.; Nagumo, T.; Hiramoto, T. Mobility enhancement due to volume inversion in [110]-oriented ultra-thin body double-gate nMOSFETs with body thickness less than 5 nm. In Proceedings of the IEEE InternationalElectron Devices Meeting, 2005. IEDM Technical Digest, Washington, DC, USA, 5 December 2005; pp. 729–732. [Google Scholar] [CrossRef]

- Simoen, E.; Gaillardin, M.; Paillet, P.; Reed, R.A.; Schrimpf, R.; Alles, M.L.; El-Mamouni, F.; Fleetwood, D.M.; Griffoni, A.; Claeys, C. Radiation Effects in Advanced Multiple Gate and Silicon-on-Insulator Transistors. IEEE Trans. Nucl. Sci. 2013, 60, 1970–1991. [Google Scholar] [CrossRef]

- Haeffner, T.D.; Reed, R.A.; Schrimpf, R.D.; Fleetwood, D.M.; Keller, R.F.; Jiang, R.; Sierawski, B.D.; McCurdy, M.W.; Zhang, E.X.; Mohammed, R.W.; et al. Comparison of Total-Ionizing-Dose Effects in Bulk and SOI FinFETs at 90 and 295 K. IEEE Trans. Nucl. Sci. 2019, 66, 911–917. [Google Scholar] [CrossRef]

- Shu, L.; Wang, L.; Zhao, K.; Zhou, X.; Zhao, Y.-F.; Galloway, K.F.; Sui, C.-L.; Liu, C.-M.; Cao, W.-Y.; Chen, W.-P.; et al. TID-Induced OFF-State Leakage Current in Partially Radiation-Hardened SOI LDMOS. IEEE Trans. Nucl. Sci. 2020, 67, 1133–1138. [Google Scholar] [CrossRef]

- Alles, M.L.; Hughes, H.L.; Ball, D.R.; McMarr, P.J.; Schrimpf, R.D. Total-Ionizing-Dose Response of Narrow, Long Channel 45 nm PDSOI Transistors. IEEE Trans. Nucl. Sci. 2014, 61, 2945–2950. [Google Scholar] [CrossRef]

- Lu, P.; Colombeau, B.; Hung, S.; Li, W.; Duan, X.; Li, Y.; Bazizi, E.M.; Natarajan, S.; Woo, J.C.S. Source/Drain Extension Doping Engineering for Variability Suppression and Performance Enhancement in 3-nm Node FinFETs. IEEE Trans. Electron Devices 2021, 68, 1352–1357. [Google Scholar] [CrossRef]

| Reference | TID Hardening Methodology | SOI FinFET Compatible |

|---|---|---|

| Y. Huang et al. [15] | Double SOI | N |

| M. Gaillardin et al. [16] | Ground plane implantation under the BOX | N |

| Y. T. Roh et al. [17] | Dummy gate-assisted SOI | N |

| C. Liu et al. [18] | Back-channel adjustment | N |

| C. Peng et al. [19] | STI oxide nitridation | N |

| This work | 3D S/D & gate dielectric optimization | Y |

| Physical Parameters | Conventional Design | Rad-Hard Design |

|---|---|---|

| Fin top width (nm) | 10 | |

| Fin height (nm) | 25 | |

| Fin pitch (nm) | 40 | |

| Taper angle (°) | 79 | |

| Channel length (nm) | 20 | |

| Fin top spacer length (nm) | 10 | |

| S/D doping concentration (cm−3) | 2 × 1020 | |

| Channel doping concentration (cm−3) | 1016 | |

| Junction doping diffusion gradient (nm/dec) | 5 | |

| Fin top EOT (nm) | 1.0 | |

| Fin bottom spacer length (nm) | 10 | 30 |

| Fin bottom EOT (nm) | 1.2 | 1.0 |

| Oxide footing | Yes | No |

| Electrical Characteristics | Conventional Design before Radiation | Conventional Design after Radiation | 3D Design before Radiation | 3D Design after Radiation |

|---|---|---|---|---|

| Threshold Voltage (V) | 0.329 | 0.220 | 0.258 | 0.205 |

| On-state Current (A/μm) | 5.80 × 10−4 | 6.85 × 10−4 | 6.71 × 10−4 | 7.17 × 10−4 |

| Off-state Current (A/μm) | 1.0 × 10−10 | 3.5 × 10−9 | 1.0 × 10−10 | 8.2 × 10−10 |

| Sub-threshold Swing(mV/dec) | 79.0 | 85.9 | 64.9 | 67.4 |

| Transconductance (mS/μm) | 1.96 | 2.13 | 1.51 | 1.56 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lu, P.; Yang, C.; Li, Y.; Li, B.; Han, Z. Three-Dimensional TID Hardening Design for 14 nm Node SOI FinFETs. Eng 2021, 2, 620-631. https://doi.org/10.3390/eng2040039

Lu P, Yang C, Li Y, Li B, Han Z. Three-Dimensional TID Hardening Design for 14 nm Node SOI FinFETs. Eng. 2021; 2(4):620-631. https://doi.org/10.3390/eng2040039

Chicago/Turabian StyleLu, Peng, Can Yang, Yifei Li, Bo Li, and Zhengsheng Han. 2021. "Three-Dimensional TID Hardening Design for 14 nm Node SOI FinFETs" Eng 2, no. 4: 620-631. https://doi.org/10.3390/eng2040039

APA StyleLu, P., Yang, C., Li, Y., Li, B., & Han, Z. (2021). Three-Dimensional TID Hardening Design for 14 nm Node SOI FinFETs. Eng, 2(4), 620-631. https://doi.org/10.3390/eng2040039