Bandpass Sigma–Delta Modulation: The Path toward RF-to-Digital Conversion in Software-Defined Radio

Abstract

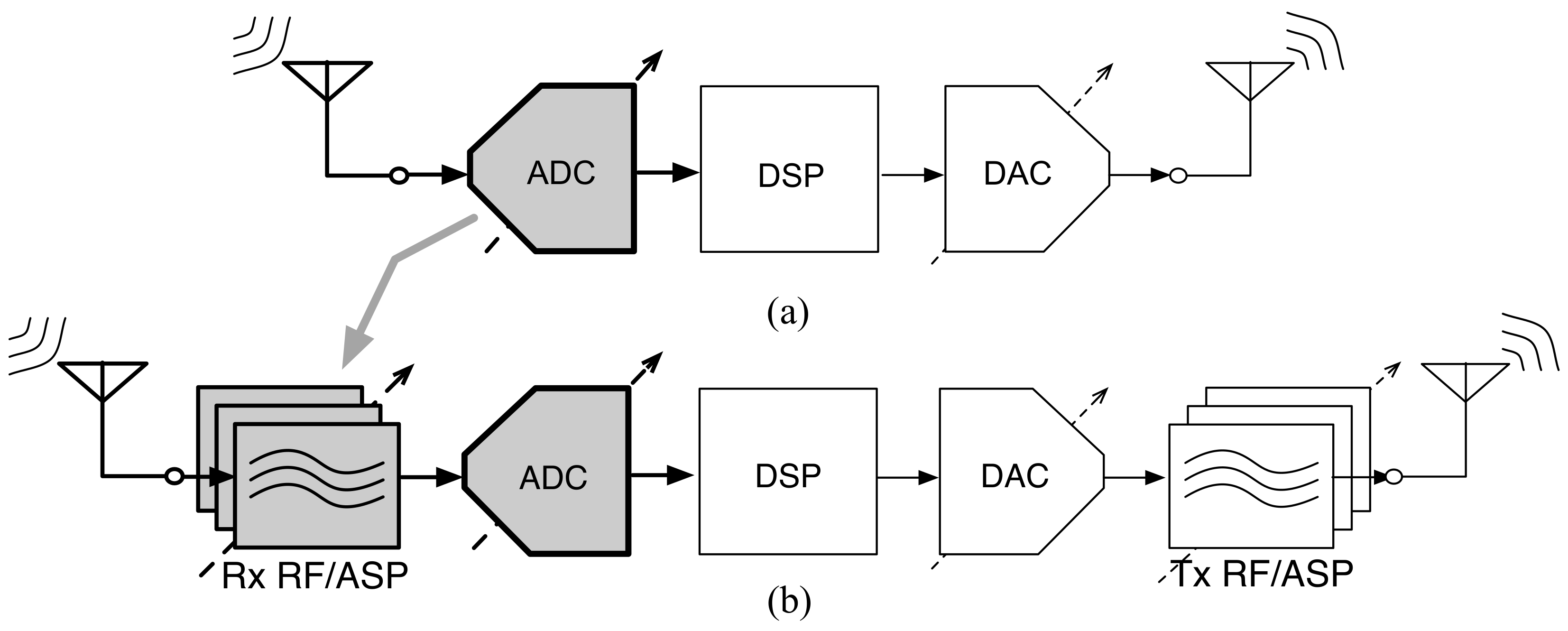

:1. Introduction

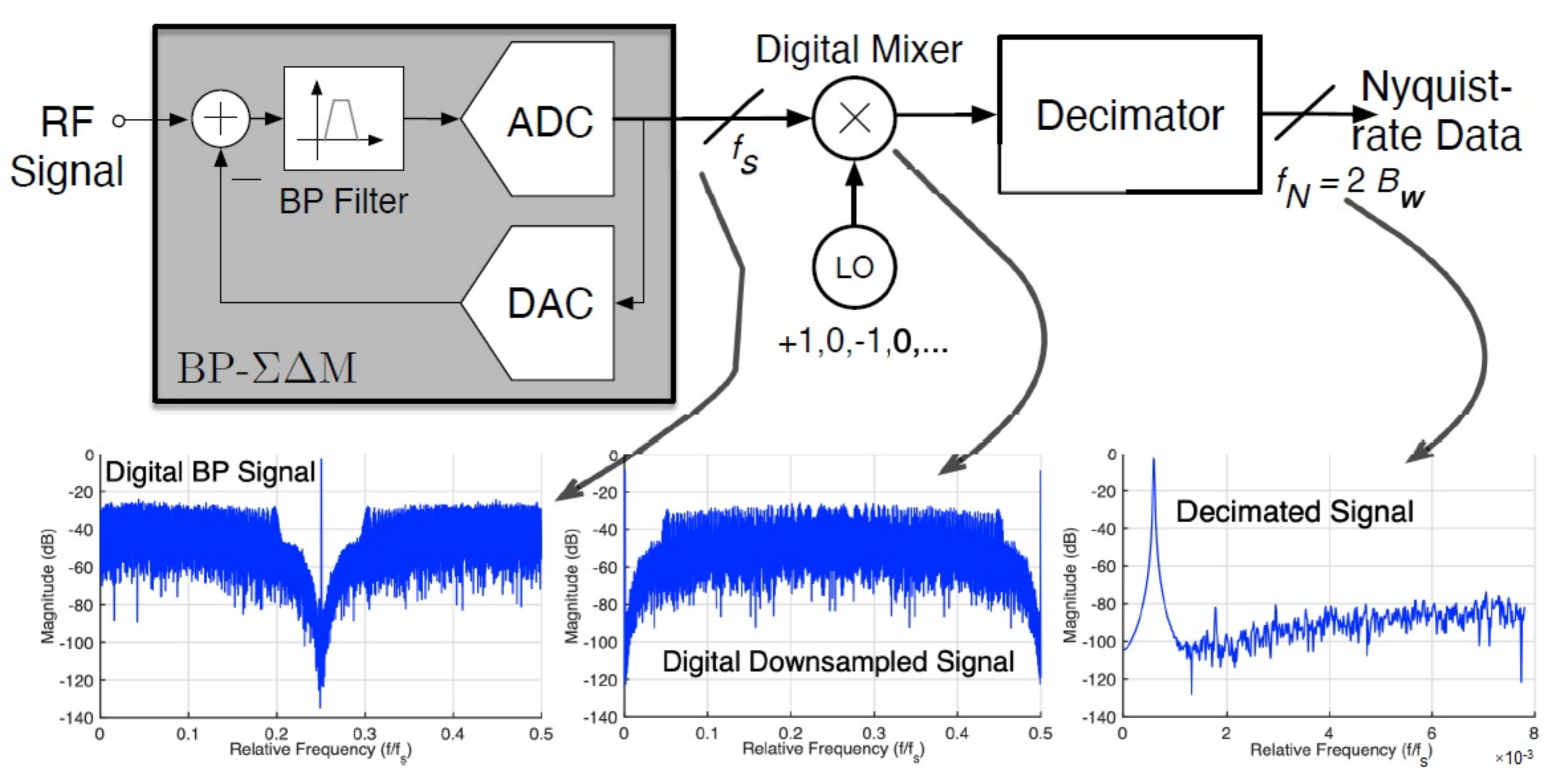

2. Bandpass Modulators: Fundamentals and Basic Concepts

2.1. Quantization Noise Shaping in BP-Ms

2.2. Notch Frequency Location and Basic Architectures

3. Continuous-Time BP-Ms

3.1. LC-Based CT BP-M Architectures

3.2. Widely Tunable CT BP-Ms

4. State of the Art on BP-Ms

4.1. Low-Pass vs. Bandpass Ms

4.2. Comparison of Different Architectures and Circuits of BP-Ms

4.3. Lessons Learned from State-of-the-Art BP-Ms

5. Conclusions

- System-level: A more simple BP-M architecture—based on a 2nd- or 4th-order loop filter and a 1-bit quantizer—achieves cutting-edge performance, being a good choice that balances performance and efficiency.

- Circuit-level: There are some circuit strategies which can improve the performance of BP-Ms in terms of power consumption, scaling and reconfigurability. Among others, the following techniques are good candidates: inverter-based OTAs, N-path filtering, FIR-filtered feedback DAC and embedded time/frequency-interleaving topologies.

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Letaief, K.B.; Chen, W.; Shi, Y.; Zhang, J.; Zhang, Y.-J.A. The Roadmap to 6G: AI Empowered Wireless Networks. IEEE Commun. 2019, 57, 84–90. [Google Scholar] [CrossRef] [Green Version]

- Loh, K. Fertilizing AIoT from Roots to Leaves. In Proceedings of the 2020 IEEE International Solid- State Circuits Conference—(ISSCC), San Francisco, CA, USA, 16–20 February 2020. [Google Scholar]

- Liu, M. Unleashing the Future of Innovation. In Proceedings of the 2021 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; pp. 9–16. [Google Scholar]

- Park, S.M.; Kim, Y.G. A Metaverse: Taxonomy, Components, Applications, and Open Challenges. IEEE Access 2022, 10, 4209–4251. [Google Scholar] [CrossRef]

- Bagheri, R.; Mirzaei, A.; Heidari, M.E.; Chehrazi, S.; Lee, M.; Mikhemar, M.; Abidi, A.A. Software-Defined Radio Receiver: Dream to Reality. IEEE Commun. Mag. 2006, 44, 111–118. [Google Scholar] [CrossRef]

- Desoli, G.; Filippi, E. An Outlook on the Evolution of Mobile Terminals: From Monolithic to Modular Multiradio, Multiapplication Platforms. IEEE Circuits Syst. Mag. 2006, 6, 17–29. [Google Scholar] [CrossRef]

- Rubestein, R. Radios Get Smart. IEEE Spectr. 2007, 44, 47–50. [Google Scholar]

- Abidi, A.A. The Path to the Software-Defined Radio Receiver. IEEE J.-Solid-State Circuits 2007, 42, 954–966. [Google Scholar] [CrossRef]

- Machado, R.G.; Wyglinski, A.M. Software-Defined Radio: Bridging the Analog/Digital Divide. Proc. IEEE 2015, 103, 409–423. [Google Scholar] [CrossRef]

- Bhagavatula, V. Exploring Multimode Cellular Transceiver Design: A Short Tutorial. IEEE Solid-State Circuits Mag. 2021, 13, 35–47. [Google Scholar] [CrossRef]

- Mitola, J. The Software Radio Architecture. IEEE Commun. Mag. 1995, 33, 26–38. [Google Scholar] [CrossRef]

- Tasic, A.; Serdijn, W.A.; Long, J.R. Adaptive Multi-Standard Circuits and Systems for Wireless Communications. IEEE Circuits Syst. Mag. 2006, 6, 29–37. [Google Scholar] [CrossRef]

- Mak, P.; Seng-Pan, U.; Martins, R. Transceiver Architecture Selection: Review, State-of-the-Art Survey and Case Study. IEEE Circuits Syst. Mag. 2007, 7, 6–25. [Google Scholar] [CrossRef]

- De la Rosa, J.M.; Castro-Lopez, R.; Morgado, A.; Becerra-Alvarez, E.C.; del Rio, R.; Fernández, F.V.; Perez-Verdu, B. Adaptive CMOS Analog Circuits for 4G Mobile Terminals—Review and State-of-the-Art Survey. Microelectron. J. 2009, 40, 156–176. [Google Scholar] [CrossRef]

- Opteynde, F. A maximally-digital radio receiver front-end. In Proceedings of the 2010 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 7–11 February 2010. [Google Scholar]

- Koli, K.; Kallioinen, S.; Jussila, J.; Sivonen, P.; Parssinen, A. A 900-MHz Direct Delta-Sigma Receiver in 65-nm CMOS. IEEE J. Solid-State Circuits 2010, 45, 2807–2818. [Google Scholar] [CrossRef]

- De la Rosa, J.M. AI-Managed Cognitive Radio Digitizers. IEEE Circuits Syst. Mag. 2022, 22, 10–39. [Google Scholar] [CrossRef]

- Schreier, R.; Snelgrove, M. Bandpass Sigma-Delta Modulation. IET Electron. Lett. 1989, 25, 1560–1561. [Google Scholar] [CrossRef] [Green Version]

- Gailus, P.H. Method and Arrangement for a Sigma Delta Converter for Bandpass Signals. U.S. Patent 4,857,828, 28 January 1989. [Google Scholar]

- Ryckaert, J.; Borremans, J.; Verbruggen, B.; Bos, L.; Armiento, C.; Craninckx, J.; van der Plas, G. A 2.4 GHz Low-Power Sixth-Order RF Bandpass ΔΣ Converter in CMOS. IEEE J. Solid-State Circuits 2009, 44, 2873–2880. [Google Scholar] [CrossRef]

- Beilleau, N.; Aboushady, H.; Montaudon, F.; Cathelin, A. A 1.3 V 26 mW 3.2GS/s Undersampled LC Bandpass ΣΔ ADC for a SDR ISM-band Receiver in 130 nm CMOS. In Proceedings of the IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, Boston, MA, USA, 7–9 June 2009. [Google Scholar]

- Ryckaert, J.; Geis, A.; Bos, L.; van der Plas, G.; Craninckx, J. A 6.1 GS/s 52.8 mW 43 dB DR 80MHz Bandwdith 2.4 GHz RF Bandpass ΔΣ ADC in 40 nm CMOS. In Proceedings of the 2010 IEEE Radio Frequency Integrated Circuits Symposium, Anaheim, CA, USA, 23–25 May 2010; pp. 443–446. [Google Scholar]

- Martens, E.; Bourdoux, A.; Couvreur, A.; Fasthuber, R.; Van Wesemael, P.; Van der Plas, G.; Craninckx, J.; Ryckaert, J. RF-to-Baseband Digitization in 40 nm CMOS with RF Bandpass ΔΣ Modulator and Polyphase Decimation Filter. IEEE J. Solid-State Circuits 2012, 47, 990–1002. [Google Scholar] [CrossRef]

- Shibata, H.; Shibata, H.; Schreier, R.; Yang, W.; Shaikh, A.; Paterson, D.; Caldwell, T.; Alldred, D.; Lai, P.W. A DC-to-1 GHz Tunable RF ΔΣ ADC Achieving DR = 7 4dB and BW = 150 MHz at f0= 450 MHz Using 550 mW. In Proceedings of the 2012 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012. [Google Scholar]

- Gupta, S.; Gangopadhyay, D.; Lakdawala, H.; Rudell, J.C.; Allstot, D.J. A 0.8-2 GHz Fully-Integrated QPLL-Timed Direct-RF-Sampling Bandpass ΣΔ ADC in 0.13 μm CMOS. IEEE J. Solid-State Circuits 2012, 47, 1141–1153. [Google Scholar] [CrossRef]

- Ashry, A.; Aboushady, H. A 4th Order 3.6 GS/s RF ΣΔ ADC with a FoM of 1 pJ/bit. IEEE Trans. Circuits Syst. Regul. Pap. 2013, 60, 2606–2617. [Google Scholar] [CrossRef]

- Englund, M.; Ostman, K.B.; Viitala, O.; Kaltiokallio, M.; Stadius, K.; Koli, K.; Ryynanen, J. A Programmable 0.7-2.7 GHz Direct ΔΣ Receiver in 40 nm CMOS. IEEE J. Solid-State Circ. 2015, 50, 644–655. [Google Scholar] [CrossRef]

- Chae, H.; Flynn, M. A 69 dB SNDR, 25 MHz BW, 800 MS/s Continuous-Time Bandpass ΔΣ Modulator Using a Duty-Cycle-Controlled DAC for Low Power and Reconfigurability. IEEE J. Solid-State Circuits 2016, 51, 649–659. [Google Scholar]

- Patras, C.Z.P.; Haddadi, H. Deep Learning in Mobile and Wireless Networking: A Survey. IEEE Commun. Surv. Tutorials 2019, 21, 2224–2287. [Google Scholar]

- Bell, J.; Flynn, M.P. A Simultaneous Multiband Continuous-Time ΔΣ ADC with 90-MHz Aggregate Bandwidth in 40-nm CMOS. IEEE Solid-State Lett. 2019, 2, 91–94. [Google Scholar] [CrossRef]

- Zhang, Y.; Kinget, P.R.; Pun, K.P. A 0.032-mm2 43.3-fJ/Step 100–200-MHz IF 2-MHz Bandwidth Bandpass ΔΣM Based on Passive N-Path Filters. IEEE J. Solid-State Circuits 2020, 55, 2443–2455. [Google Scholar] [CrossRef]

- Kim, S.; Rhee, J.; Kim, S. A Wide Dynamic Range Multi-Mode Band-Pass Continuous-Time Delta-Sigma Modulator Employing Single-Opamp Resonator with Positive Resistor-Feedback. IEEE Trans. Circuits Syst. Express Briefs 2020, 67, 235–239. [Google Scholar] [CrossRef]

- Kumar, R.A.; Krishnapura, N. Multi-Channel Analog-to-Digital Conversion Techniques Using a Continuous-Time Delta-Sigma Modulator without Reset. IEEE Trans. Circuits Syst. Regul. Pap. 2020, 67, 3693–3703. [Google Scholar] [CrossRef]

- Sayed, A.; Badran, T.; Louërat, M.M.; Aboushady, H. A 1.5-to-3.0 GHz Tunable RF Sigma-Delta ADC with a Fixed Set of Coefficients and a Programmable Loop Delay. IEEE Trans. Circuits Syst. Express Briefs 2020, 67, 1559–1563. [Google Scholar] [CrossRef]

- Ghaedrahmati, H.; Zhou, J.; Staszewski, R.B. A 38.6-fJ/Conv.-Step Inverter-Based Continuous-Time Bandpass ΔΣ ADC in 28 nm Using Asynchronous SAR Quantizer. IEEE Trans. Circuits Syst. Express Briefs 2021, 68, 3113–3117. [Google Scholar] [CrossRef]

- Jie, L.; Chen, H.-W.; Zheng, B.; Flynn, M.P. A 100 MHz-BW 68 dB-SNDR Tuning-Free Hybrid-Loop DSM with an Interleaved Bandpass Noise-Shaping SAR Quantizer. In Proceedings of the 2021 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021. [Google Scholar]

- De la Rosa, J.M. Sigma-Delta Converters: Practical Design Guide, 2nd ed.; Wiley: Hoboken, NJ, USA, 2018. [Google Scholar]

- Manivannan, S.; Pavan, S. Improved Continuous-Time Delta-Sigma Modulators with Embedded Active Filtering. IEEE Trans. Circuits Syst. Regul. Pap. 2020, 67, 3778–3789. [Google Scholar] [CrossRef]

- De la Rosa, J.M.; Pérez-Verdú, B.; del Río, R.; Medeiro, F.; Rodríguez-Vázquez, A. Bandpass Sigma-Delta A/D Converters: Fundamentals, Architectures and Circuits; Chapter 11 in CMOS Telecom Data Converters; Rodríguez-Vázquez, A., Medeiro, F., Janssens, E., Eds.; Kluwer Academic Publishers: Amsterdam, The Netherlands, 2003. [Google Scholar]

- Louis, L.; Abcarius, J.; Roberts, G.W. An Eigth-Order Bandpass ΔΣ Modulator for A/D Conversion in Digital Radio. IEEE J. Solid-State Circuits 1999, 34, 423–431. [Google Scholar] [CrossRef]

- Molina-Salgado, G.; Morgado, A.; Dolecek, G.J.; de la Rosa, J.M. LC-Based Bandpass Continuous-Time Sigma-Delta Modulators with Widely Tunable Notch Frequency. IEEE Trans. Circuits Syst. Regul. Pap. 2014, 61, 1442–1455. [Google Scholar] [CrossRef] [Green Version]

- Jantzi, S.A.; Martin, K.W.; Sedra, A.S. Quadrature Bandpass ΔΣ Modulation for Digital Radio. IEEE J. Solid-State Circuits 1997, 32, 1935–1950. [Google Scholar] [CrossRef]

- Paulus, T.; Somayajula, S.S.; Miller, T.A.; Trotter, B.; Kyong, C.; Kerth, D.A. A CMOS IF Transceiver with Reduced Analog Complexity. IEEE J. Solid-State Circuits 1998, 33, 2154–2159. [Google Scholar] [CrossRef]

- Cusinato, P.; Tonietto, D.; Stefani, F. A 3.3-V CMOS 10.7-MHz Sixth-Order Bandpass ΣΔ Modulator with 74-dB Dynamic Range. IEEE J. Solid-State Circuits 2001, 36, 629–638. [Google Scholar] [CrossRef]

- Ong, A.K.; Wooley, B.A. A Two-Path Bandpass ΣΔ Modulator for Digital IF Extraction at 20 MHz. IEEE J. Solid-State Circuits 1997, 32, 1920–1934. [Google Scholar] [CrossRef]

- Ferragina, V.; Fornasari, A.; Gatti, U.; Malcovati, P.; Maloberti, F. Gain and Offset Mismatch Calibration in Time-Interleaved Multipath A/D Sigma-Delta Modulators. IEEE Trans. Circuits Syst. Regul. Pap. 2004, 51, 2365–2373. [Google Scholar] [CrossRef]

- Feng, D.; Maloberti, F.; Sin, S.W.; Martins, R.P. Polyphase Decomposition for Tunable Band-Pass Sigma-Delta A/D Converters. IEEE J. Emerg. Sel. Top. Circuits Syst. 2015, 5, 537–547. [Google Scholar] [CrossRef]

- De la Rosa, J.M.; Schreier, R.; Pun, K.P.; Pavan, S. Next-Generation Delta-Sigma Converters: Trends and Perspectives. IEEE J. Emerg. Sel. Top. Circuits Syst. 2015, 5, 484–499. [Google Scholar] [CrossRef]

- Chae, H.; Jeong, J.; Manganaro, G.; Flynn, M.P. A 12 mW Low Power Continuous-Time Bandpass ΔΣ Modulator with 58 dB SNDR and 24 MHz Bandwidth at 200 MHz IF. IEEE J. Solid-State Circuits 2013, 49, 405–415. [Google Scholar] [CrossRef]

- Shoaei, O.; Snelgrove, W.M. Design and Implementation of a Tunable 40 MHz-70MHz Gm-C Bandpass ΔΣ Modulator. IEEE Trans. Circuits Syst. II: Analog. Digit. Signal Process. 1997, 44, 521–530. [Google Scholar] [CrossRef]

- Beilleau, N.; Aboushady, H.; Loureat, M. Using Finite Impulse Response Feedback DACs to design ΣΔ Modulators based on LC Filters. In Proceedings of the 52nd IEEE International Midwest Symposium on Circuits and Systems (MWSCAS 2009), Cancun, Mexico, 2–5 August 2005; pp. 696–699. [Google Scholar]

- Schreier, R. The Delta-Sigma Toolbox. 2011. Available online: http://www.mathworks.com/matlabcentral/fileexchange/19 (accessed on 11 December 2022).

- Pavan, S.; Schreier, R.; Temes, G.C. Understanding Delta-Sigma Data Converters, 2nd ed.; Wiley: Hoboken, NJ, USA, 2017. [Google Scholar]

- Morgado, A.; del Río, R.; de la Rosa, J.M. Design of a power-efficient widely-programmable Gm-LC band-pass sigma-delta modulator for SDR. In Proceedings of the 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montréal, QC, Canada, 22–25 May 2016. [Google Scholar]

- Jantzi, S.A.; Snelgrove, W.M.; Ferguson, P.F. A Fourth-Order Bandpass Sigma-Delta Modulator. IEEE J. Solid-State Circuits 1993, 28, 282–291. [Google Scholar] [CrossRef]

- Cheung, V.S.; Luong, H.; Ki, W. A 1 V 10.7 MHz Switched-Opamp Bandpass ΣΔ Modulator Using Double-Sampling Finite-Gain-Compensation Technique. IEEE J. Solid-State Circuits 2002, 37, 1215–1225. [Google Scholar] [CrossRef]

- Salo, T.O.; Lindfors, S.; Halonen, K. A 80-MHz Band-pass ΣΔ Modulator for a 100-MHz IF Receiver. IEEE J. Solid-State Circuits 2002, 37, 798–808. [Google Scholar] [CrossRef]

- Cheng, W.T.; Pun, K.P.; Choy, C.S.; Chan, C.F. A 75 dB Image Rejection IF-Input Quadrature Sampling SC ΣΔ Modulator. In Proceedings of the 31st European Solid-State Circuits Conference, Grenoble, France, 12–16 September 2005; pp. 455–458. [Google Scholar]

- Song, B.S. A Fourth-Order Bandpass Delta-Sigma Modulator with Reduced Number of Op Amps. IEEE J. Solid-State Circuits 1995, 30, 1309–1315. [Google Scholar] [CrossRef]

- Kuo, C.H.; Liu, S.I. A 1-V 10.7-MHz Fourth-Order Bandpass ΔΣ Modulators Using Two Switched Opamps. IEEE J. Solid-State Circuits 2004, 39, 2041–2045. [Google Scholar]

- Ueno, T.; Yasuda, A.; Yamaji, T.; Itakura, T. A Fourth-Order Bandpass Δ − Σ Modulator Using Second-Order Bandpass Noise-Shaping Dynamic Element Matching. IEEE J. Solid-State Circuits 2001, 37, 522–525. [Google Scholar] [CrossRef]

- Hairapetian, A. An 81 MHz IF receiver in CMOS. IEEE J. Solid-State Circuits 1996, 31, 1981–1986. [Google Scholar] [CrossRef]

- Tabatabaei, A.; Wooley, A. A Two-Path Bandpass Sigma-Delta Modulator with Extended Noise Shaping. IEEE J. Solid-State Circuits 2000, 35, 1799–1809. [Google Scholar] [CrossRef]

- Salo, T.O.; Lindfors, S.J.; Hollman, T.M.; Jarvinen, J.A.M.; Halonen, K.A. 80-MHz Bandpass ΔΣ Modulators for Multimode Digital IF Receivers. IEEE J. Solid-State Circuits 2003, 38, 464–474. [Google Scholar] [CrossRef]

- Galdi, I.; Bonizzoni, E.; Maloberti, F.; Manganaro, G.; Malcovati, P. Two-Path Band-Pass ΣΔ Modulator with 40-MHz IF 72-dB DR at 1-MHz Bandwidth Conuming 16mW. In Proceedings of the 2007 IEEE International Solid- State Circuits Conference, San Francisco, CA, USA, 11–15 February 2007; pp. 248–251. [Google Scholar]

- Yamamoto, T.; Kasahara, M.; Matsuura, T. A 63 mA 112/94 dB DR IF Bandpass ΔΣ Modulator with Direct Feed-Forward Compensation and Double Sampling. IEEE J. Solid-State Circuits 2008, 43, 1783–1794. [Google Scholar] [CrossRef]

- Maurino, R.; Papavassiliou, C. A 10 mW 81 dB Cascaded Multibit Quadrature ΣΔ ADC with a Dynamic Element Matching Scheme. In Proceedings of the 31st European Solid-State Circuits Conference, Grenoble, France, 12–16 September 2005; pp. 451–454. [Google Scholar]

- Yamamoto, K.; Carusone, A.C.; Dawson, F.P. A Delta-Sigma Modulator with a Widely Programmable Center Frequency and 82-dB Peak SNDR. In Proceedings of the 2007 IEEE Custom Integrated Circuits Conference. (CICC 07), San Jose, CA, USA, 16–19 September 2007; pp. 65–69. [Google Scholar]

- Ying, F.; Maloberti, F. A mirror image free two-path bandpass ΣΔ modulator with 72 dB SNR and 86 dB SFDR. IEEE ISSCC Dig. Tech. Pap. 2004, 84–85. [Google Scholar]

- Thomas, K.P.J.; Rana, R.S.; Lian, Y. A 1 GHz CMOS Fourth-Order Continuous-Time Bandpass Sigma-Delta Modulator for RF Receiver Front-End A/D Conversion. In Proceedings of the ASPDAC05: Asia and South Pacific Design Automation Conference, Shanghai, China, 18–21 January 2005; pp. 665–670. [Google Scholar]

- Tao, H.; Khoury, J.M. A 400-MS/s Frequency Translating Bandpass Sigma-Delta Modulator. IEEE J. Solid-State Circuits 1999, 34, 1741–1752. [Google Scholar] [CrossRef]

- Hsu, I.; Luong, H.C. A 70-MHz Continuous-Time CMOS Band-pass ΣΔ Modulator for GPS Receivers. In Proceedings of the IEEE International Symposium on Circuits and Systems, ISCAS 2000, Geneva, Switzerland, 28–31 May 2000; pp. 750–753. [Google Scholar]

- Chopp, P.M.; Hamoui, A. A 1-V 13-mW Single-Path Frequency-Translating ΔΣ Modulator with 55-dB SNDR and 4-MHz Bandwidth at 225 MHz. IEEE J. Solid-State Circuits 2013, 48, 473–486. [Google Scholar] [CrossRef]

- Yu, R.; Xu, Y.P. Bandpass Sigma-Delta Modulator Employing SAW Resonator as Loop Filter. IEEE Trans. Circuits Syst. Regul. Pap. 2007, 54, 723–735. [Google Scholar] [CrossRef]

- Gupta, S.; Gangopadhyay, D.; Lakdawala, H.; Rudell, J.C.; Allstot, D.J. A QPLL-Timed Direct-RF Sampling Band-Pass ΣΔ ADC with a 1.2 GHz Tuning Range in 0.13 μm CMOS. In Proceedings of the 2011 IEEE Radio Frequency Integrated Circuits Symposium, Baltimore, MD, USA, 5–7 June 2011. [Google Scholar]

- Engelen, J.V.; van de Plassche, R. BandPass Sigma-Delta Modulators: Stability Analysis, Performance and Design Aspects; Kluwer Academic Publishers: Amsterdam, The Netherlands, 1999. [Google Scholar]

- Englund, M.; Ostman, K.B.; Viitala, O.; Kaltiokallio, M.; Stadius, K.; Ryynanen, J.; Koli, K. A 2.5-GHz 4.2-dB NF Direct ΔΣ Receiver with a Frequency-Translating Integrator. In Proceedings of the 40th European Solid State Circuits Conference (ESSCIRC 2014), Venice, Italy, 22–26 September 2014; pp. 371–374. [Google Scholar]

- Kim, S.B.; Joeres, S.; Zimmermann, N.; Robens, M.; Wunderlich, R.; Heinen, S. Continuous-Time Quadrature Bandpass Sigma-Delta Modulator for GPS/Galileo Low-IF Receiver. In Proceedings of the 2007 IEEE Radio Frequency Integrated Circuits (RFIC), Honolulu, HI, USA, 3–5 June 2007; pp. 127–130. [Google Scholar]

- Chopp, P.M.; Hamoui, A.A. A 1V 13 mW Frequency-Translating ΔΣ ADC with 55dB SNDR for a 4MHz Band at 225MHz. In Proceedings of the 2011 IEEE Custom Integrated Circuits Conference (CICC 2011), San Jose, CA, USA, 19–21 September 2021. [Google Scholar]

- Ashry, A.; Aboushady, H. A 3.6 GS/s, 15 mW, 50 dB SNDR, 28 MHz Bandwidth RF ΣΔ ADC with FoM of 1 pJ/bit in 130 nm CMOS. In Proceedings of the 2011 IEEE Custom Integrated Circuits Conference (CICC 2011), San Jose, CA, USA, 19–21 September 2021. [Google Scholar]

- Veldhoven, R.H.M. A Triple-Mode Continuous-Time ΣΔ Modulator with Switched-Capacitor Feedback DAC for a GSM-EDGE/CDMA2000/UMTS Receiver. IEEE J. Solid-State Circuits 2003, 38, 2069–2076. [Google Scholar] [CrossRef]

- Van der Zwan, E.J.; Philips, K.; Bastiaansen, C.A.A. A 10.7-MHz IF-to-Baseband ΣΔ A/D Conversion System for AM/FM Radio Receivers. IEEE J. Solid-State Circuits 2000, 35, 1810–1819. [Google Scholar] [CrossRef] [Green Version]

- Kappes, M.S. A 2.2-mW CMOS Bandpass Continuous-Time Multibit Δ − Σ ADC with 68 dB of Dynamic Range and 1-MHz Bandwidth for Wireless Applications. IEEE J. Solid-State Circuits 2003, 38, 1098–1104. [Google Scholar] [CrossRef]

- Silva, P.G.; Breems, L.J.; Makinwa, K.A.; Roovers, R.; Huijsing, J.H. An IF-to-Baseband ΣΔ Modulator for AM/FM/IBOC Radio Receivers with a 118 dB Dynamic Range. IEEE J. Solid-State Circuits 2007, 42, 1076–1089. [Google Scholar] [CrossRef]

- Jeong, J.; Collins, N.; Flynn, M. A 260 MHz IF Sampling Bit-Stream Processing Digital Beamformer with an Integrated Array of Continuous-Time Band-Pass ΔΣ Modulators. IEEE J. Solid-State Circuits 2016, 51, 1168–1176. [Google Scholar] [CrossRef]

- Lu, C.Y.; Silva-Rivas, J.F.; Kode, P.; Silva-Martinez, J.; Hoyos, S. A Sixth-Order 200 MHz IF Bandpass Sigma-Delta Modulator with Over 68 dB SNDR in 10 MHz Bandwidth. IEEE J. Solid-State Circuits 2010, 45, 1122–1136. [Google Scholar] [CrossRef]

- Zhang, C.; Ueng, Y.L.; Studer, C.; Burg, A. Artificial Intelligence for 5G and Beyond 5G: Implementations, Algorithms, and Optimizations. IEEE J. Emerg. Sel. Top. Circuits Syst. 2020, 10, 149–163. [Google Scholar] [CrossRef]

- Lu, R.; Flynn, M.P. A 300 MHz-BW 38 mW 37 dB/40 dB SNDR/DR Frequency-Interleaving Continuous-Time Bandpass Delta-Sigma ADC in 28 nm CMOS. In Proceedings of the 2021 Symposium on VLSI Circuits, Kyoto, Japan, 13–19 June 2021. [Google Scholar]

- Kim, S.B.; Joeres, S.; Wunderlich, R.; Heinen, S. A 2.7 mW, 90.3 dB DR Continuous-Time Quadrature Bandpass Sigma-Delta Modulator for GSM/EDGE Low-IF Receiver in 0.25 μm CMOS. IEEE J. Solid-State Circuits 2009, 44, 891–900. [Google Scholar] [CrossRef]

- Chae, Y.; Souri, K.; Makinwa, K.A. A 6.3 μW 20 bit Incremental Zoom-ADC with 6 ppm INL and 1 μV Offset. IEEE J. Solid-State Circuits 2013, 48, 3019–3027. [Google Scholar] [CrossRef] [Green Version]

- Harrison, J.; Nesselroth, M.; Mamuad, R.; Behzad, A.; Adams, A.; Avery, S. An LC Bandpass ΔΣ ADC with 70 dB SNDR Over 20 MHz Bandwidth Using CMOS DACs. In Proceedings of the 2012 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012. [Google Scholar]

- Xu, Y.; Zhang, Z.; Chi, B.; Liu, Q.; Zhang, X.; Wang, Z. Dual-mode 10 MHz BW 4.8/6.3 mW Reconfigurable Lowpass/ Complex Bandpass CT ΣΔ Modulator with 65.8/74.2dB DR for a Zero/Low-IF SDR Receiver. In Proceedings of the 2014 IEEE Radio Frequency. Integrated Circuits Symposium, Tampla, FL, USA, 1–3 June 2014; pp. 313–316. [Google Scholar]

- Schreier, R.; Abaskharoun, N.; Shibata, H.; Paterson, D.; Rose, S.; Mehr, I.; Luu, Q. A 375-mW Quadrature Bandpass ΔΣ ADC with 8.5-MHz BW and 90-dB DR at 44 MHz. IEEE J. Solid-State Circuits 2006, 41, 2632–2640. [Google Scholar] [CrossRef]

- Murmann, B. A/D Converter Trends: Power Dissipation, Scaling and Digitally Assisted Architectures. In Proceedings of the 2008 IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 21–24 September 2008; pp. 105–112. [Google Scholar]

- Jonsson, B.E. An Empirical Approach to Finding Energy Efficient ADC Architectures. In Proceedings of the 2011 International Workshop on ADC Modelling, Testing and Data Converter Analysis and Design and IEEE 2011 ADC Forum, Orvieto, Italy, 30 June–1 July 2011. [Google Scholar]

- Manganaro, G. Advanced Data Converters; Cambridge University Press: Cambridge, UK, 2012. [Google Scholar]

- Walden, R.H. Analog-to-Digital Converter Survey and Analysis. IEEE J. Sel. Areas Commun. 1999, 17, 539–550. [Google Scholar] [CrossRef] [Green Version]

- Rabii, S.; Wooley, B.A. A 1.8 V Digital-Audio Sigma-Delta Modulator in 0.8 μm CMOS. IEEE J. Solid-State Circuits 1997, 32, 783–796. [Google Scholar] [CrossRef] [Green Version]

- Schreier, R.; Temes, G.C. Understanding Delta-Sigma Data Converters.; IEEE Press: New York, NY, USA, 2005. [Google Scholar]

- Pavan, S.; Sankar, P. Power Reduction in Continuous-Time Delta-Sigma Modulators Using the Assisted Opamp Technique. IEEE J. Solid-State Circuits 2010, 45, 1365–1379. [Google Scholar] [CrossRef]

- Shettigar, P.; Pavan, S. Design Techniques for Wideband Single-Bit Continuous-Time ΔΣ Modulators with FIR Feedback DACs. IEEE J. Solid-State Circuits 2012, 47, 2865–2879. [Google Scholar] [CrossRef]

- Shu, Y.S.; Tsai, J.Y.; Chen, P.; Lo, T.Y.; Chiu, P.C. A 28fJ/conv-step CT ΔΣ Modulator with 78 dB DR and 18 MHz BW in 28 nm CMOS Using a Highly Digital Multibit Quantizer. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013. [Google Scholar]

- Zeller, S.; Muenker, C.; Weigel, R.; Ussmueller, T. A 0.039 mm2 Inverter-Based 1.82 mW 68.6 dB-SNDR 10 MHz-BW CT-ΣΔ-ADC in 65 nm CMOS Using Power- and Area-Efficient Design Techniques. IEEE J. Solid-State Circuits 2014, 49, 1548–1560. [Google Scholar] [CrossRef]

- Sukumaran, A.; Pavan, S. Low Power Design Techniques for Single-Bit Audio Continuous-Time Delta Sigma ADCs Using FIR Feedback. IEEE J. Solid-State Circuits 2014, 49, 2515–2525. [Google Scholar] [CrossRef]

- Dong, Y.; Yang, W.; Schreier, R.; Sheikholeslami, A.; Korrapati, S. A Continuous-Time 0–3 MASH ADC Achieving 88 dB DR with 53 MHz BW in 28 nm CMOS. IEEE J. Solid-State Circuits 2014, 49, 2868–2877. [Google Scholar] [CrossRef]

- De Berti, C.; Malcovati, P.; Crespi, L.; Baschirotto, A. A 106 dB A-Weighted DR Low-Power Continuous-Time ΣΔ Modulator for MEMS Microphones. IEEE J. Solid-State Circuits 2016, 51, 1607–1618. [Google Scholar] [CrossRef]

- Briseno-Vidrios, C.; Edward, A.; Rashidi, N.; Silva-Martinez, J. A 4 Bit Continuous-Time ΣΔ Modulator with Fully Digital Quantization Noise Reduction Algorithm Employing a 7 Bit Quantizer. IEEE J. Solid-State Circuits 2016, 51, 1398–1409. [Google Scholar] [CrossRef]

- S Mondal, O.G.; Hall, D.A. A 139 μW 104.8dB-DR 24 kHz-BW CTΔΣM with Chopped AC-Coupled OTA-Stacking and FIR DACs. In Proceedings of the 2021 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021. [Google Scholar]

- Rodríguez-Vázquez, A.; Medeiro, F.; Janssens, E. CMOS Telecom Data Converters; Kluwer Academic Publishers: Amsterdam, The Netherlands, 2003. [Google Scholar]

- Nauta, B. A CMOS Transconductance-C Filter Technique for Very High Frequencies. IEEE J. Solid-State Circuits 1992, 27, 142–153. [Google Scholar] [CrossRef] [Green Version]

- Purushothaman, V.K.; Klumperink, E.A.; Clavera, B.T.; Nauta, B. A Fully Passive RF Front End with 13-dB Gain Exploiting Implicit Capacitive Stacking in a Bottom-Plate N-Path Filter/Mixer. IEEE J. Solid-State Circuits 2020, 55, 1139–1150. [Google Scholar] [CrossRef] [Green Version]

| Ref. | DR (bit) | (MHz) | (MHz) | L | Tech./Sup.Volt | P (mW) | FOMS (dB) |

|---|---|---|---|---|---|---|---|

| [56] | 6.8 | 10.7 | 0.2 | 2 | 0.35 mu/1 V | 12.0 | 115 |

| [57] | 6.7 | 20.0 | 3.84 | 4 | 0.35 mu /3 V | 56.0 | 120 |

| [42] | 10.8 | 3.75 | 0.2 | 4 | 0.8 mu/5 V | 130.0 | 129 |

| [58] | 9.7 | 3.25 | 0.2 | 3 | 0.35 mu/3.3 V | 18.7 | 130 |

| [59] | 9.0 | 2.0 | 0.03 | 4 | 2 mu/3.3 V | 0.8 | 132 |

| [60] | 10.0 | 10.7 | 0.2 | 4 | 0.25 mu/1 V | 8.5 | 136 |

| [44] | 12.0 | 10.7 | 0.2 | 6 | 0.35 mu/3.3 V | 116.0 | 136 |

| [57] | 11.7 | 20.0 | 0.27 | 4 | 0.35 mu/3 V | 56.0 | 139 |

| [45] | 12.2 | 20.0 | 0.2 | 4 | 0.6 mu/3.3 V | 72.0 | 140 |

| [61] | 12.6 | 0.56 | 0.25 | 2-2 | 0.25 mu/2.5 V | 77.0 | 143 |

| [62] | 11.7 | 3.25 | 0.2 | 4-2 | 0.8 mu/3 V | 14.4 | 144 |

| [60] | 12.0 | 10.7 | 0.1 | 4 | 0.25 mu/1 V | 8.5 | 145 |

| [63] | 12.0 | 16.0 | 2.0 | 6 | 0.25 mu/2.5 V | 110.0 | 147 |

| [60] | 12.7 | 10.7 | 0.06 | 4 | 0.25 mu /1 V | 8.5 | 147 |

| [64] | 11.7 | 20.0 | 1.76 | 4-4 | 0.35 mu/3 V | 37.0 | 149 |

| [65] | 11.7 | 40.0 | 1.0 | 4 | 0.18 mu/1.8 V | 16.0 | 150 |

| [60] | 13.4 | 10.7 | 0.06 | 4 | 0.25 mu/1 V | 8.5 | 151 |

| [66] | 14.5 | 10.7 | 0.4 | 4 | 0.15 V/3.3 V | 208.0 | 152 |

| [66] | 18.3 | 10.7 | 0.003 | 4 | 0.15 V/3.3 V | 208.0 | 154 |

| [66] | 15.3 | 10.7 | 0.2 | 4 | 0.15 V/3.3 V | 208.0 | 154 |

| [67] | 13.2 | 10.0 | 0.2 | 2 | 0.25 mu/2.1 V | 10.0 | 154 |

| [64] | 13.3 | 20.0 | 1.25 | 4-4 | 0.35 mu/3 V | 37.0 | 157 |

| [68] | 15.7 | 12.6 | 0.31 | 4 | 0.18 mu/1.8 V | 115.0 | 160 |

| [69] | 14.4 | 40.0 | 2.5 | 4 | 0.18 mu/1.8 V | 150.0 | 161 |

| Ref. | DR (bit) | (MHz) | (MHz) | L | Tech./Sup.Volt | P (mW) | FOMS (dB) |

|---|---|---|---|---|---|---|---|

| [70] | 6.0 | 1000 | 0.5 | 4 | 0.18 mu/1.8 V | 290.0 | 61 |

| [71] | 7.2 | 100 | 0.2 | 4 | 0.35 mu/3.3 V | 165.0 | 67 |

| [72] | 6.7 | 70 | 0.2 | 2 | 0.5 mu/2.5 V | 39.0 | 68 |

| [73] | 8.9 | 225 | 100 | 6 | 65 nm/1 V | 13.0 | 90 |

| [74] | 9.2 | 47.3 | 0.2 | 2 | 0.35 mu/3.3 V | 45.0 | 90 |

| [75] | 8.0 | 2000 | 1.0 | 2 | 0.13 mu/1.2 V | 30.0 | 92 |

| [27] | 6.8 | 2700 | 15.0 | 4 | 40 nm/1.1 V | 90.0 | 103 |

| [76] | 10.8 | 10.7 | 0.2 | 6 | 0.5 mu /5 V | 60.0 | 104 |

| [74] | 8.4 | 47.3 | 3.84 | 4 | 0.35 mu/3.3 V | 45.0 | 109 |

| [77] | 6.3 | 2500 | 15.0 | 3 | 40 nm/1.1 V | 90.0 | 109 |

| [78] | 8.1 | 4.09 | 4.0 | 2 | 0.25 mu /1.8 V | 20.5 | 109 |

| [78] | 9.3 | 4.09 | 2.0 | 2 | 0.25 mu/1.8 V | 20.5 | 114 |

| [79] | 9.3 | 228 | 4.0 | 4 | 65 nm/1 V | 13.0 | 122 |

| [80] | 8.3 | 2440 | 28.0 | 4 | 0.13 mu/1.2 V | 15.0 | 129 |

| [81] | 15.0 | 0.1 | 0.02 | 5 | 0.18 mu/2.9 V | 9.1 | 130 |

| [34] | 7.0 | 3000 | 93.0 | 2 | 65 nm/1.2 V | 13.0 | 130 |

| [82] | 13.3 | 10.7 | 0.2 | 5 | 0.25 mu/2.5 V | 11.0 | 133 |

| [83] | 11.0 | 2.0 | 1.0 | 2 | 0.18 mu/1.8 V | 2.2 | 134 |

| [84] | 14.0 | 10.7 | 0.5 | 5 | 0.18 mu/1.8 V | 210.0 | 135 |

| [85] | 10.2 | 260 | 20.0 | 4 | 65 nm/1.4 V | 124.0 | 135 |

| [23] | 7.7 | 2.2 | 80.0 | 4 | 40 nm/1.1 V | 9.86 | 135 |

| [86] | 11.3 | 200 | 10.0 | 4 | 0.18 mu/1.8 V | 160.0 | 137 |

| [84] | 19.3 | 10.7 | 0.003 | 5 | 0.18 mu/1.8 V | 210.0 | 138 |

| [32] | 14.6 | 20.0 | 0.2 | 3 | 180 nm/1.8 V | 25.8 | 142 |

| [49] | 9.7 | 200 | 24.0 | 4 | 65 nm/1.25 V | 12.0 | 142 |

| [87] | 10.0 | 175 | 2.0 | 4 | 65 nm/1 V | 0.15 | 144 |

| [84] | 16.0 | 10.7 | 0.2 | 5 | 0.18 mu/1.8 V | 210.0 | 145 |

| [81] | 12.0 | 50.0 | 3.84 | 5 | 0.18 mu/ 2.9 V | 14.1 | 146 |

| [88] | 8.3 | 1.5 | 300 | 4 | 28 nm/1 V | 38.0 | 147 |

| [20] | 10.0 | 2.4 | 60.0 | 6 | 90 nm/1 V | 40.0 | 148 |

| [81] | 13.5 | 50.0 | 1.23 | 5 | 0.18 mu/2.9 V | 13.1 | 150 |

| [28] | 11.3 | 180 | 25.0 | 6 | 65 nm/1.2 V | 35.0 | 152 |

| [35] | 9.8 | 100 | 30.0 | 2 | 28 nm/1 V | 2.5 | 152 |

| [89] | 14.7 | 0.13 | 0.2 | 3 | 0.25 mu/1.8 V | 2.7 | 152 |

| [90] | 11.3 | 200 | 25.0 | 6 | 65 nm/1 V | 35.0 | 153 |

| [91] | 11.3 | 2.45 | 20.0 | 6 | 40 nm/1.1 V | 20.0 | 153 |

| [92] | 12.0 | 6.0 | 10.0 | 2 | 65 nm/1.2 V | 6.3 | 158 |

| [93] | 14.7 | 44.0 | 8.5 | 4 | 0.18 mu/2.9 V | 375 | 163 |

| [36] | 11.2 | 400 | 100 | 2 | 28 nm/1 V | 13.4 | 167 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

de la Rosa, J.M. Bandpass Sigma–Delta Modulation: The Path toward RF-to-Digital Conversion in Software-Defined Radio. Chips 2023, 2, 44-69. https://doi.org/10.3390/chips2010004

de la Rosa JM. Bandpass Sigma–Delta Modulation: The Path toward RF-to-Digital Conversion in Software-Defined Radio. Chips. 2023; 2(1):44-69. https://doi.org/10.3390/chips2010004

Chicago/Turabian Stylede la Rosa, Jose M. 2023. "Bandpass Sigma–Delta Modulation: The Path toward RF-to-Digital Conversion in Software-Defined Radio" Chips 2, no. 1: 44-69. https://doi.org/10.3390/chips2010004

APA Stylede la Rosa, J. M. (2023). Bandpass Sigma–Delta Modulation: The Path toward RF-to-Digital Conversion in Software-Defined Radio. Chips, 2(1), 44-69. https://doi.org/10.3390/chips2010004