Optimal Bias Condition of Dummy WL for Sub-Block GIDL Erase Operation in 3D NAND Flash Memory

Abstract

:1. Introduction

2. Simulation Design and Results

2.1. 3D NAND Flash Memory Structure Setup

2.2. Simulation Setup

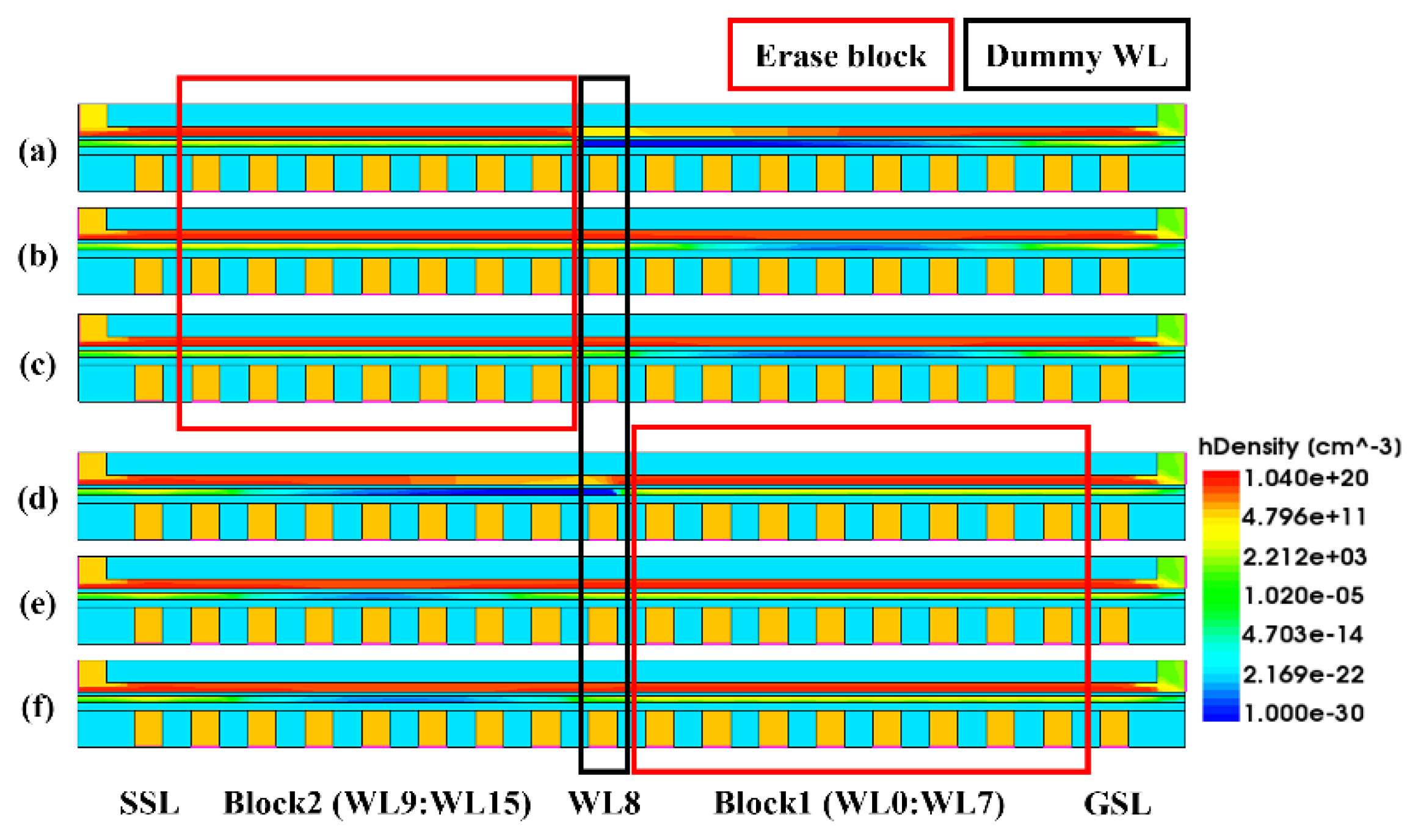

2.3. Analysis of hDensity

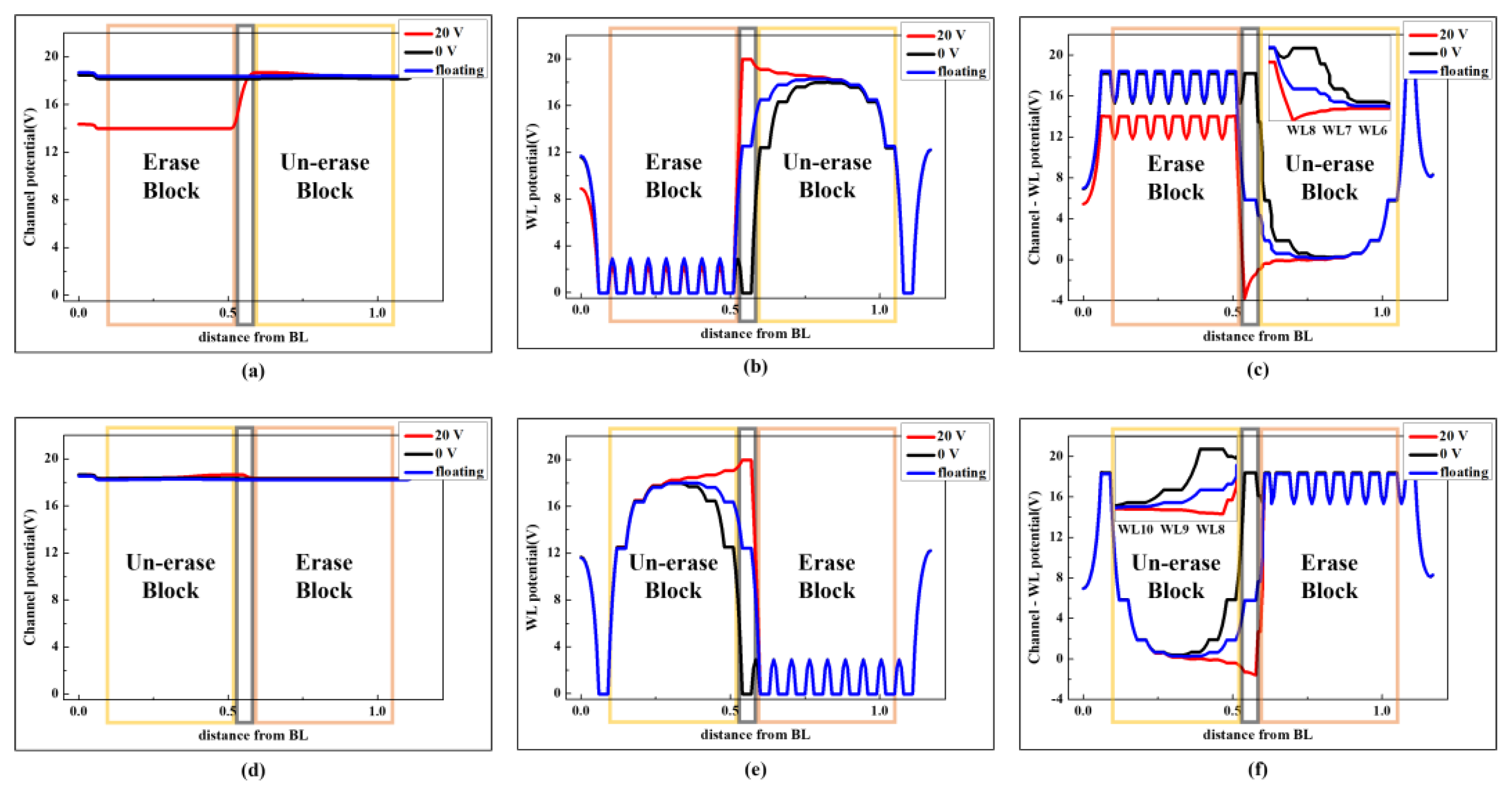

2.4. Analysis of Potential to Channel and WL

3. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Choe, J. Memory Technology 2021: Trends & Challenges. In Proceedings of the 2021 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Granada, Spain, 27–29 September 2021; pp. 111–115. [Google Scholar] [CrossRef]

- Kang, M.; Lete, K.; Chale, D.H.; Park, B.-G.; Shin, H. The compact modeling of channel potential in Sub-30-nm NAND flash cell string. IEEE Electron Device Lett. 2012, 33, 321–323. [Google Scholar] [CrossRef]

- Park, Y.; Lee, J.; Cho, S.S.; Jin, G.; Jung, E. Scaling and reliability of NAND flash devices. In Proceedings of the 2014 IEEE International Reliability Physics Symposium, Waikoloa, HI, USA, 1–5 June 2014. [Google Scholar] [CrossRef]

- Kim, Y.; Kang, M. Predictive modeling of channel potential in 3-D NAND flash memory. IEEE Trans. Electron Devices 2014, 61, 3901–3904. [Google Scholar] [CrossRef]

- Kim, H.; Ahn, S.-J.; Shin, Y.G.; Lee, K.; Jung, E. Evolution of NAND Flash Memory: From 2D to 3D as a Storage Market Leader. In Proceedings of the 2017 IEEE International Memory Workshop (IMW), Monterey, CA, USA, 14–17 May 2017; pp. 1–4. [Google Scholar] [CrossRef]

- Li, Y. 3D NAND memory and its application in solid-state drives: Architecture, reliability, flash management techniques, and current trends. IEEE Solid-State Circuits Mag. 2020, 12, 56–65. [Google Scholar] [CrossRef]

- Goda, A. 3-D NAND Technology Achievements and Future Scaling Perspectives. IEEE Trans. Electron Devices 2020, 67, 1373–1381. [Google Scholar] [CrossRef]

- Goda, A. Recent Progress on 3D NAND Flash Technologies. Electronics 2021, 10, 31563156. [Google Scholar] [CrossRef]

- Park, S.; Lee, J.; Jang, J.; Lim, J.K.; Kim, H.; Shim, J.J.; Yu, M.-T.; Kang, J.-K.; Ahn, S.J.; Song, J. Highly-Reliable Cell Characteristics with 128-Layer Single-Stack 3D-NAND Flash Memory. In Proceedings of the 2021 Symposium on VLSI Technology, Hsinchu, Taiwan, 19–22 April 2021; pp. 1–2. [Google Scholar]

- Kim, J.H.; Yim, Y.; Lim, J.; Kim, H.S.; Cho, E.S.; Yeo, C.; Lee, W.; You, B.; Lee, B.; Kang, M.; et al. Highly Manufacturable 7th Generation 3D NAND Flash Memory with COP structure and Double Stack Process. In Proceedings of the 2021 Symposium on VLSI Technology, Hsinchu, Taiwan, 19–22 April 2021; pp. 1–2. [Google Scholar]

- Fayrushin, A.; Seol, K.; Na, J.; Hur, S.; Choi, J.; Kim, K. The new program/erase cycling degradation mechanism of NAND flash memory devices. In Proceedings of the 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, USA, 7–9 December 2009; pp. 1–4. [Google Scholar] [CrossRef]

- Woo, C.; Kim, S.; Park, J.; Shin, H.; Kim, H.; Choi, G.-B.; Seo, M.-S.; Noh, K.H. Modeling of charge failure mechanisms during the short term retention depending on program/erase cycle counts in 3-D NAND flash memories. In Proceedings of the 2020 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April–30 May 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Kim, S.; Lee, K.; Woo, C.; Hwang, Y.; Shin, H. Analysis of Failure Mechanisms During the Long-Term Retention Operation in 3-D NAND Flash Memories. IEEE Trans. Electron Devices 2020, 67, 5472–5478. [Google Scholar] [CrossRef]

- Chiu, Y.-Y.; Chang, K.-C.; Lin, H.-J.; Tsai, H.-T.; Lin, P.-J.; Li, H.-C.; Takeshita, T.; Yano, M.; Shirota, R. Impact of Program/Erase Cycling Interval on the Transconductance Distribution of NAND Flash Memory Devices. IEEE Trans. Electron Devices 2020, 67, 4897–4903. [Google Scholar] [CrossRef]

- Wang, Y.; Tan, J.; Mao, R.; Li, T. Temperature-Aware Persistent Data Management for LSM-Tree on 3-D NAND Flash Memory. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2020, 39, 4611–4622. [Google Scholar] [CrossRef]

- Luo, Y.; Ghose, S.; Cai, Y.; Haratsch, E.F.; Mutlu, O. Improving 3D NAND Flash Memory Lifetime by Tolerating Early Retention Loss and Process Variation. Proc. ACM Meas. Anal. Comput. Syst. 2018, 2, 1–48. [Google Scholar] [CrossRef]

- Wang, Y.; Huang, J.; Chen, J.; Mao, R. PVSensing: A Process-Variation-Aware Space Allocation Strategy for 3D NAND Flash Memory. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2022, 41, 1302–1315. [Google Scholar] [CrossRef]

- Jeong, Y.; Ham, I.; Han, S.; Kang, M. Optimal dummy word line condition to suppress hot carrier injection phenomenon due to the natural local self-boosting effect in 3D NAND flash memory. Jpn. J. Appl. Phys. 2020, 59, 1–5. [Google Scholar] [CrossRef]

- Han, S.; Jeong, Y.; Jhon, H.; Kang, M. Investigation of inhibited channel potential of 3D NAND flash memory according to word-line location. Electronics 2020, 9, 268. [Google Scholar] [CrossRef]

- Lee, S.; Kim, C.; Kim, M.; Joe, S.-M.; Jang, J.; Kim, S.; Lee, K.; Kim, J.; Park, J.; Lee, H.-J.; et al. A 1Tb 4b/cell 64-stacked-WL 3D NAND flash memory with 12MB/s program throughput. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference, ISSCC 2018, San Francisco, CA, USA, 11–15 February 2018; pp. 340–342. [Google Scholar] [CrossRef]

- Jo, H.; Shin, H. New Read Schemes to Reduce Read Disturbance Due to HCI in Full Boosting Channel 3-D NAND Flash Memories. In Proceedings of the 2021 Silicon Nanoelectronics Workshop (SNW), Virtual Conference. 13 June 2021; pp. 1–2. [Google Scholar]

- Kim, Y.; Kang, M. Down-coupling phenomenon of floating channel in 3D NAND flash memory. IEEE Electron Dev. Lett. 2016, 37, 1566–1569. [Google Scholar] [CrossRef]

- Kang, M.; Kim, Y. Natural local self-boosting effect in 3D NAND flash memory. IEEE Electron Dev. Lett. 2017, 38, 1236–1239. [Google Scholar] [CrossRef]

- Breuil, L.; Nyns, L.; Banerjee, K.; Palayam, S.V.; Subirats, A.; Richard, O.; Conard, T.; Bosch, G.V.D.; Furnemont, A. Impact of SiON tunnel layer composition on 3D NAND cell performance. In Proceedings of the 2019 IEEE 11th International Memory Workshop (IMW), Monterey, CA, USA, 12–15 May 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Monzio Compagnoni, C.; Spinelli, A.S. Reliability of NAND Flash Arrays: A Review of What the 2-D–to–3-D Transition Meant. IEEE Trans. Electron Devices 2019, 66, 4504–4516. [Google Scholar] [CrossRef]

- Jeong, Y.; Ham, I.; Kang, M. Optimal bias condition of dummy WL for sub-block erase operation in 3D NAND flash memory. In Proceedings of the 2019 International Conference on Solid State Devices and Materials, Aichi, Japan, 2–5 September 2019; pp. 683–684. [Google Scholar]

- Malavena, G.; Lacaita, A.L.; Spinelli, A.S.; Monzio Compagnoni, C. Investigation and compact modeling of the time dynamics of the GIDL-assisted increase of the string potential in 3-D NAND flash arrays. IEEE Trans. Electron Devices 2018, 65, 2804–2811. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, B.; Kang, M. Optimal Bias Condition of Dummy WL for Sub-Block GIDL Erase Operation in 3D NAND Flash Memory. Electronics 2022, 11, 2738. https://doi.org/10.3390/electronics11172738

Kim B, Kang M. Optimal Bias Condition of Dummy WL for Sub-Block GIDL Erase Operation in 3D NAND Flash Memory. Electronics. 2022; 11(17):2738. https://doi.org/10.3390/electronics11172738

Chicago/Turabian StyleKim, Beomsu, and Myounggon Kang. 2022. "Optimal Bias Condition of Dummy WL for Sub-Block GIDL Erase Operation in 3D NAND Flash Memory" Electronics 11, no. 17: 2738. https://doi.org/10.3390/electronics11172738

APA StyleKim, B., & Kang, M. (2022). Optimal Bias Condition of Dummy WL for Sub-Block GIDL Erase Operation in 3D NAND Flash Memory. Electronics, 11(17), 2738. https://doi.org/10.3390/electronics11172738