- Article

A Novel SRAM In-Memory Computing Accelerator Design Approach with R2R-Ladder for AI Sensors and Eddy Current Testing

- Kevin Becker,

- Martin Zimmerling and

- Wolf-Joachim Fischer

- + 3 authors

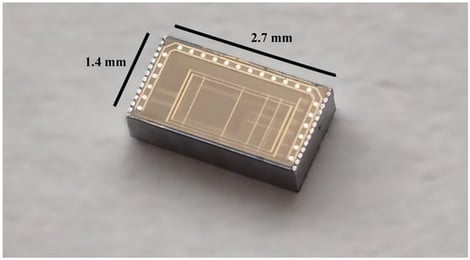

This work presents a 6T-SRAM-based in-memory computing (IMC) system fabricated in a 180 nm CMOS technology. A total of 128 integrated polysilicon R2R-DACs for fully analog wordline control and performance analysis are integrated into the system. The proposed architecture enables analog computation directly inside the memory array and introduces a compact 1-bit per-column comparator scheme for energy-efficient classification without requiring ADCs. A dedicated pull-down-dominant SRAM sizing and an analog activation scheme ensure stable analog discharge behavior and precise control of the computation through time-dependent bitline dynamics. The system integrates a complete sensor front-end, which allows real eddy current data to be classified directly on-chip. Measurements demonstrate a performance density of 3.2 TOPS/mm2, a simulated energy efficiency of 45 TOPS/W at 50 MHz, and a measured efficiency of 3.4 TOPS/W at 5 MHz on silicon. The implemented online training mechanism further improves classification accuracy by adapting the SRAM cell states during operation. These results highlight the suitability of the presented IMC architecture for compact, low-power edge intelligence and sensor-driven machine learning applications.

15 January 2026

![Overview of intelligent self-powered sensing system for AIoT. Reproduced with permission [23]. Copyright 2021, Elsevier. Reproduced with permission [24]. Copyright 2015, Wiley. Reproduced with permission [25]. Copyright 2024, Springer Nature. Reproduced with permission [29]. Copyright 2021, American Chemical Society.](https://mdpi-res.com/cdn-cgi/image/w=281,h=192/https://mdpi-res.com/aisens/aisens-02-00001/article_deploy/html/images/aisens-02-00001-g001-550.jpg)