Differential CMOS Sub-Terahertz Detector with Subthreshold Amplifier

Abstract

:1. Introduction

2. Operating Principle and Architecture of the Proposed CMOS Detector

3. Design and Implementation of the Proposed Detector

3.1. Detector Core and Subthreshold Preamplifier

3.2. Three-Stage Folded Cascode Amplifier

3.3. Differential Patch Antenna

3.4. Implementation of the Proposed Detector Using CMOS Process

4. Measurement Results and Discussion

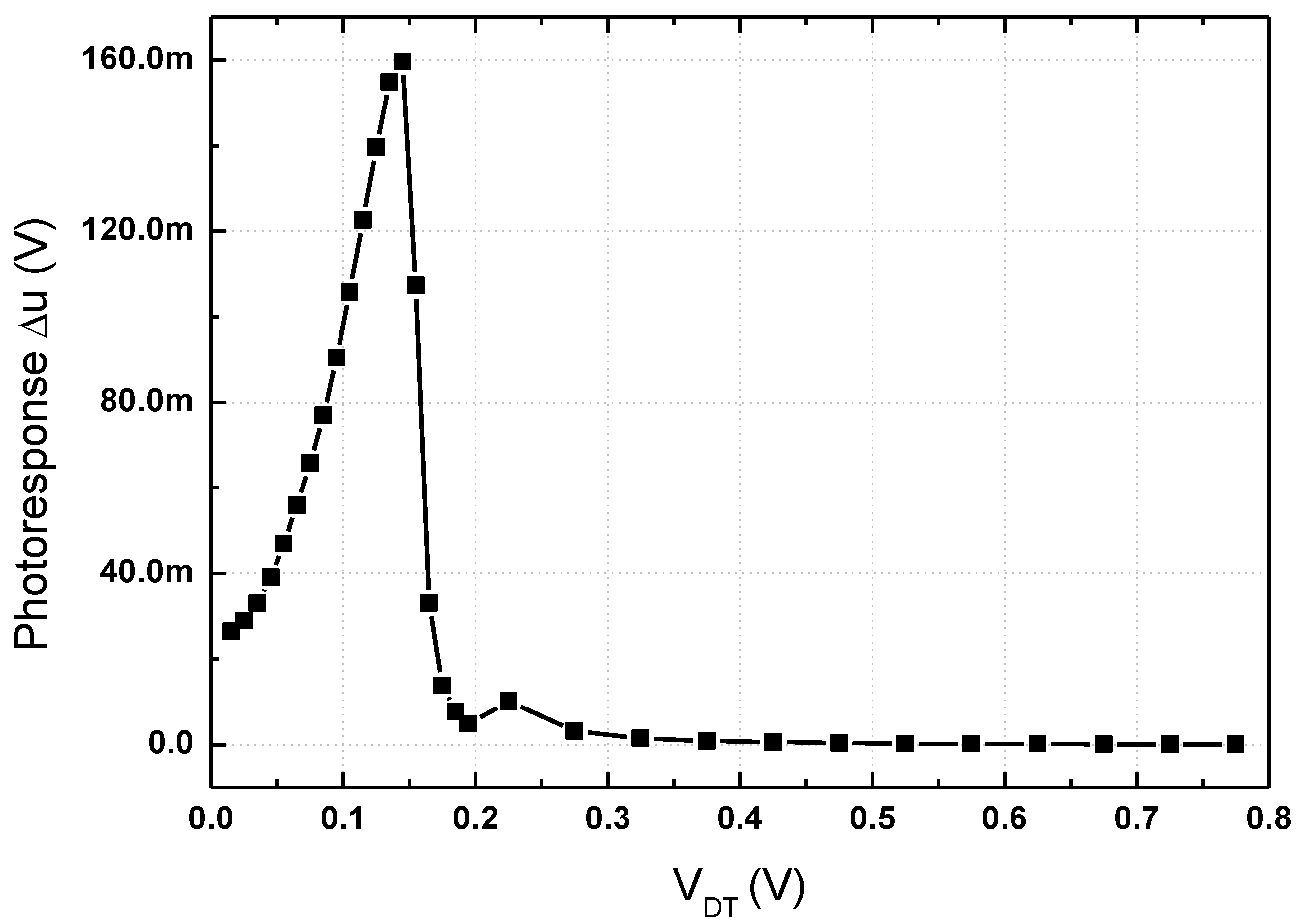

4.1. Performance of the Proposed Detector IC

4.2. THz Imaging with the Proposed Detector Using Raster Scan Method

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Otsuji, T.; Shur, M. Terahertz plasmonics: Good results and great expectations. IEEE Microw. Mag. 2014, 15, 43–50. [Google Scholar] [CrossRef]

- Schuster, F.; Coquillat, D.; Videlier, H.; Sakowicz, M.; Teppe, F.; Dussopt, L.; Giffard, B.; Skotnicki, T.; Knap, W. Broadband terahertz imaging with highly sensitive silicon CMOS detectors. Opt. Express 2011, 19, 7827–7832. [Google Scholar] [CrossRef] [PubMed]

- Rogalski, A.; Sizov, F. Terahertz detectors and focal plane arrays. Opto-Electron. Rev. 2011, 19, 346–404. [Google Scholar] [CrossRef]

- Ryu, M.W.; Lee, J.S.; Park, K.; Park, W.-K.; Han, S.-T.; Kim, K.R. Photoresponse enhancement of plasmonic terahertz wave detector based on asymmetric silicon MOSFETs with antenna integration. Jpn. J. Appl. Phys. 2014, 53, 04EJ05-1–04EJ05-4. [Google Scholar] [CrossRef]

- Öjefors, E.; Pfeiffer, U.R.; Lisauskas, A.; Roskos, H.G. A 0.65 THz focal-plane array in a quarter-micron CMOS process technology. IEEE J. Solid-State Circuits 2009, 44, 1968–1976. [Google Scholar] [CrossRef]

- Boppel, S.; Lisauskas, A.; Mundt, M.; Seliuta, D.; Minkevičius, L.; Kašalynas, I.; Valušis, G.; Mittendorff, M.; Winnerl, S.; Knozer, V.; et al. CMOS integrated antenna-coupled field-effect transistors for the detection of radiation from 0.2 to 4.3 THz. IEEE Trans. Microw. Theory Tech. 2012, 60, 3834–3843. [Google Scholar] [CrossRef]

- Al Hadi, R.; Grzyb, J.; Heinemann, B.; Pfeiffer, U.R. A terahertz detector array in a SiGe HBT technology. IEEE J. Solid-State Circuits 2013, 48, 2002–2010. [Google Scholar] [CrossRef]

- Han, R.; Zhang, Y.; Coquillat, D.; Videlier, H.; Knap, W.; Brown, E.; O, K.K. A 280-GHz schottky diode detector in 130-nm digital CMOS. IEEE J. Solid-State Circuits 2011, 46, 2602–2612. [Google Scholar] [CrossRef]

- Al Hadi, R.; Sheery, H.; Grzyb, J.; Zhao, Y.; Förster, W.; Keller, H.M.; Cathelin, A.; Kaiser, A.; Pfeiffer, U.R. A 1 k-pixel video camera for 0.7–1.1 terahertz imaging applications in 65-nm CMOS. IEEE J. Solid-State Circuits 2012, 47, 2999–3012. [Google Scholar] [CrossRef]

- Károlyi, G.; Gergelyi, D.; Földesy, P. Sub-THz sensor array with embedded signal processing in 90 nm CMOS technology. IEEE Sens. J. 2013, 14, 2432–2441. [Google Scholar] [CrossRef]

- Boukhayma, A.; Dupret, A.; Rostaing, J.-P.; Enz, C. A low-noise CMOS THz imager based on source modulation and an in-pixel high-Q passive switched-capacitor n-path filter. Sensors 2016, 16, 325. [Google Scholar] [CrossRef] [PubMed]

- Yang, J.-R.; Lee, W.-J.; Ryu, M.-W.; Kim, K.-R.; Han, S.-T. Parasitic antenna effect in terahertz plasmon detector array for real-time imaging system. Jpn. J. Appl. Phys. 2015, 54, 102001-1–102001-6. [Google Scholar] [CrossRef]

- Wu, C.-Y.; Chen, W.-M.; Kuo, L.-T. A CMOS power-efficient low-noise current-mode front-end amplifier for neural sensing recording. IEEE Trans. Biomed. Circuits Syst. 2013, 7, 107–114. [Google Scholar] [CrossRef] [PubMed]

- Yang, J.-R.; Lee, W.-J.; Han, S.-T. Signal-conditioning block of a 1 × 200 CMOS detector array for a terahertz real-time imaging system. Sensors 2016, 16, 319. [Google Scholar] [CrossRef] [PubMed]

- Knap, W.; Dyakonov, M.; Coquillat, D.; Teppe, F.; Dyakonova, N.; Łusakowski, J.; Karpierz, K.; Sakowicz, M.; Valusis, G.; Seliuta, D.; et al. Field effect transistors for terahertz detection: Physics and first imaging applications. J. Infrared Millim. Terahertz Waves 2009, 30, 1319–1337. [Google Scholar] [CrossRef]

- Chang, J.; Abidi, A.A.; Viswanathan, C.R. Flicker noise in CMOS transistors from subthreshold to strong inversion at various temperatures. IEEE Trans. Electron Devices 1994, 41, 1965–1971. [Google Scholar] [CrossRef]

- Razavi, B. RF Microelectronics, 2nd ed.; Pearson: Bergen, NJ, USA, 2012; pp. 52–55. [Google Scholar]

- Tauk, R.; Teppe, F.; Boubanga, S.; Coquillat, D.; Knap, W.; Meziani, Y.M.; Gallon, C.; Boeuf, F.; Skotnichi, T.; Fenouillet-Beranger, C.; et al. Plasma wave detection of terahertz radiation by silicon field effects transistors: Responsivity and noise equivalent power. Appl. Phys. Lett. 2006, 89, 253511-1–253511-3. [Google Scholar] [CrossRef]

- Mallya, S.M.; Nevin, J.H. Design procedures for a fully differential folded-cascode CMOS operational amplifier. IEEE J. Solid-State Circuits 1989, 24, 1737–1740. [Google Scholar] [CrossRef]

- Chan, P.K.; Ng, L.S.; Siek, L.; Lau, K.T. Designing CMOS folded-cascode operational amplifier with flicker noise minimization. Microelectron. J. 2001, 32, 69–73. [Google Scholar] [CrossRef]

- Han, S.-T.; Torrezan, A.C.; Sirigiri, J.R.; Shapiro, M.A.; Temkin, R.J. Real-time, T-ray, imaging using a sub-terahertz gyrotron. J. Korean Phys. Soc. 2012, 60, 1857–1861. [Google Scholar] [CrossRef]

- Xu, L.-J.; Guan, J.-N.; Bai, X.; Mao, H.-P. A novel CMOS multi-band THz detector with embedded ring antenna. J. Infrared Millim. Terahertz Waves 2017, 38, 1189–1205. [Google Scholar] [CrossRef]

- Cui, Y.; Fu, W.; Guan, X.; Hu, M.; Yan, Y.; Liu, S. Experiment studies on two-dimension terahertz raster scan imaging. J. Infrared Millim. Terahertz Waves 2012, 33, 513–521. [Google Scholar] [CrossRef]

| Transistors | Width [μm] | Length [μm] | Operation |

|---|---|---|---|

| M1 & M2 | 0.3 | 0.24 | Detector core |

| M3 & M4 | 1.0 | 0.35 | Transconductance stage |

| M5 & M6 | 1.0 | 0.35 | Dummy structure |

| M7 & M8 | 18.0 | 1.0 | Additional gain and isolation |

| M9 & M10 | 1.0 | 12.0 | Active load |

| Ref. | Freq. [GHz] | CMOS Technology | Responsivity 1 [kV/W] | NEP [pW/√Hz] |

|---|---|---|---|---|

| [1] | 292 | 0.13 μm | 5 | 8 |

| [2] | 650 | 0.25 μm | 80 | 300 |

| [8] | 280 | 0.13 μm | 250 | 33 |

| [9] | 856 | 65 nm | 140 | 100 |

| [10] | 365 | 90 nm | 1200 | 200 |

| [11] | 270 | 0.13 μm | 300 | 18.7 |

| [22] | 290 | 0.18 μm | 0.7 | 261 |

| This work | 200 | 0.25 μm | 2020 2 | 76 |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yang, J.-R.; Han, S.-T.; Baek, D. Differential CMOS Sub-Terahertz Detector with Subthreshold Amplifier. Sensors 2017, 17, 2069. https://doi.org/10.3390/s17092069

Yang J-R, Han S-T, Baek D. Differential CMOS Sub-Terahertz Detector with Subthreshold Amplifier. Sensors. 2017; 17(9):2069. https://doi.org/10.3390/s17092069

Chicago/Turabian StyleYang, Jong-Ryul, Seong-Tae Han, and Donghyun Baek. 2017. "Differential CMOS Sub-Terahertz Detector with Subthreshold Amplifier" Sensors 17, no. 9: 2069. https://doi.org/10.3390/s17092069

APA StyleYang, J.-R., Han, S.-T., & Baek, D. (2017). Differential CMOS Sub-Terahertz Detector with Subthreshold Amplifier. Sensors, 17(9), 2069. https://doi.org/10.3390/s17092069