An Input-Parallel-Output-Series Switched-Capacitor Three-level Boost Converter with a Three-Loop Control Strategy

Abstract

:1. Introduction

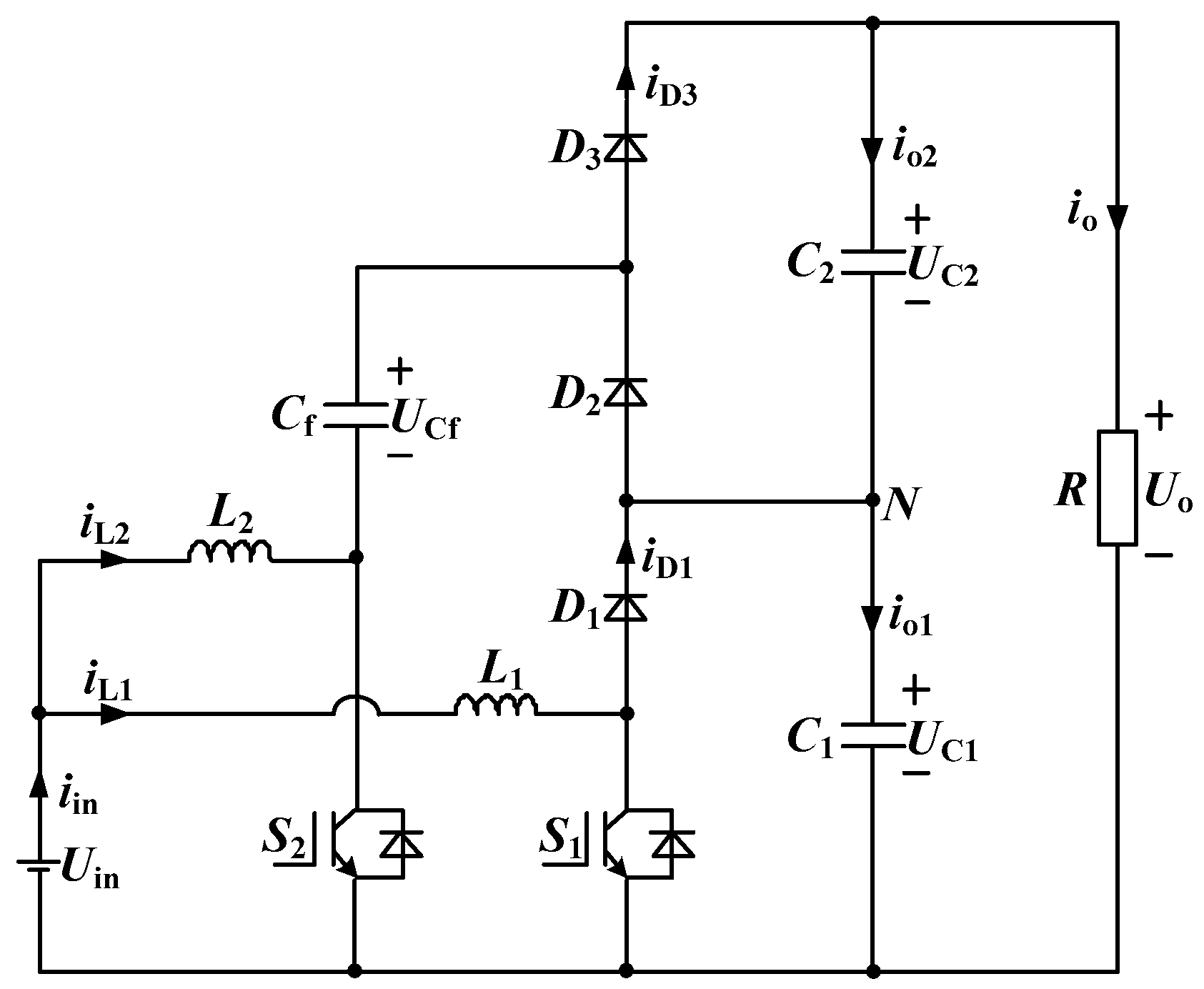

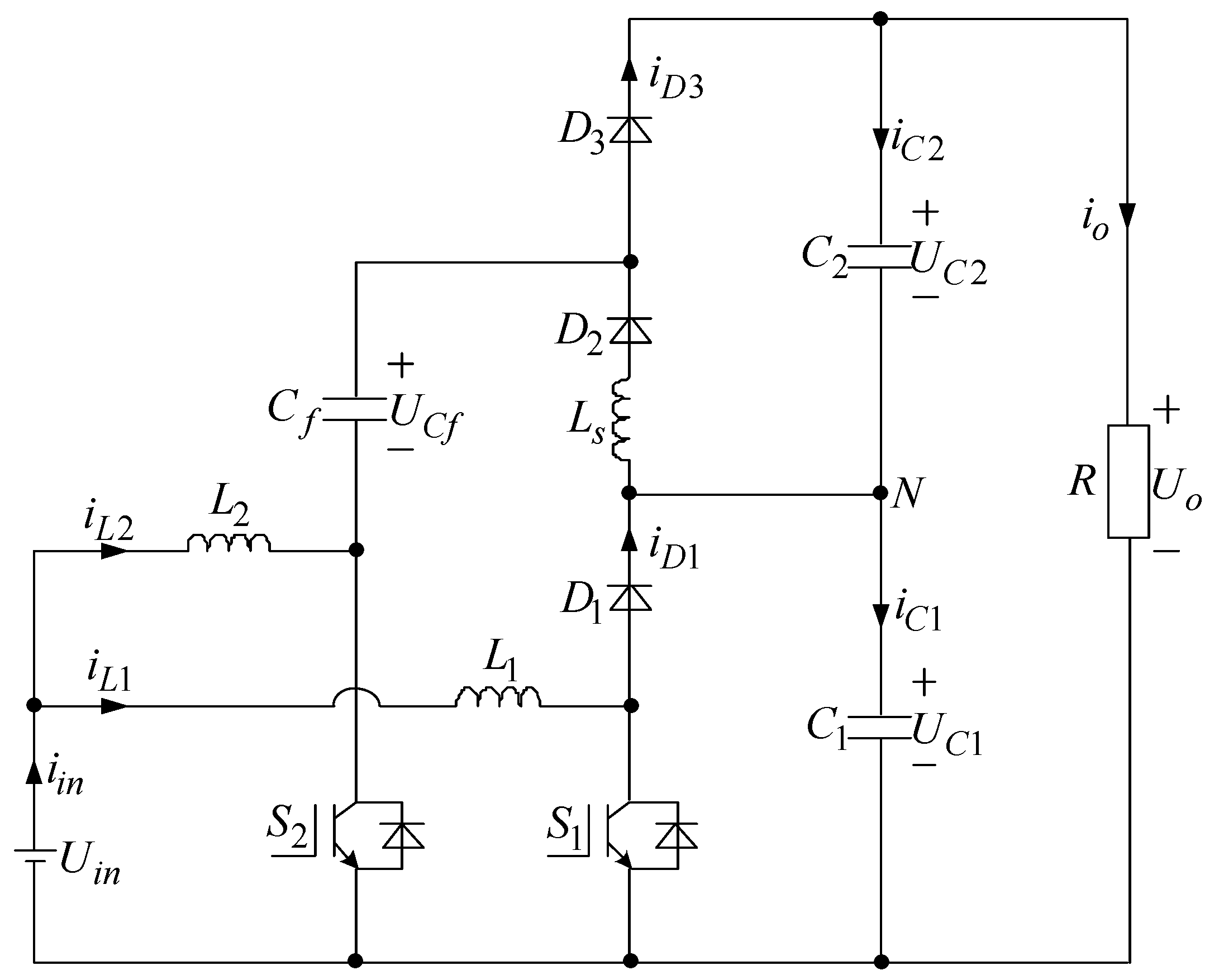

2. IPOS-SC-TLB Converter

2.1. Topology Derivation

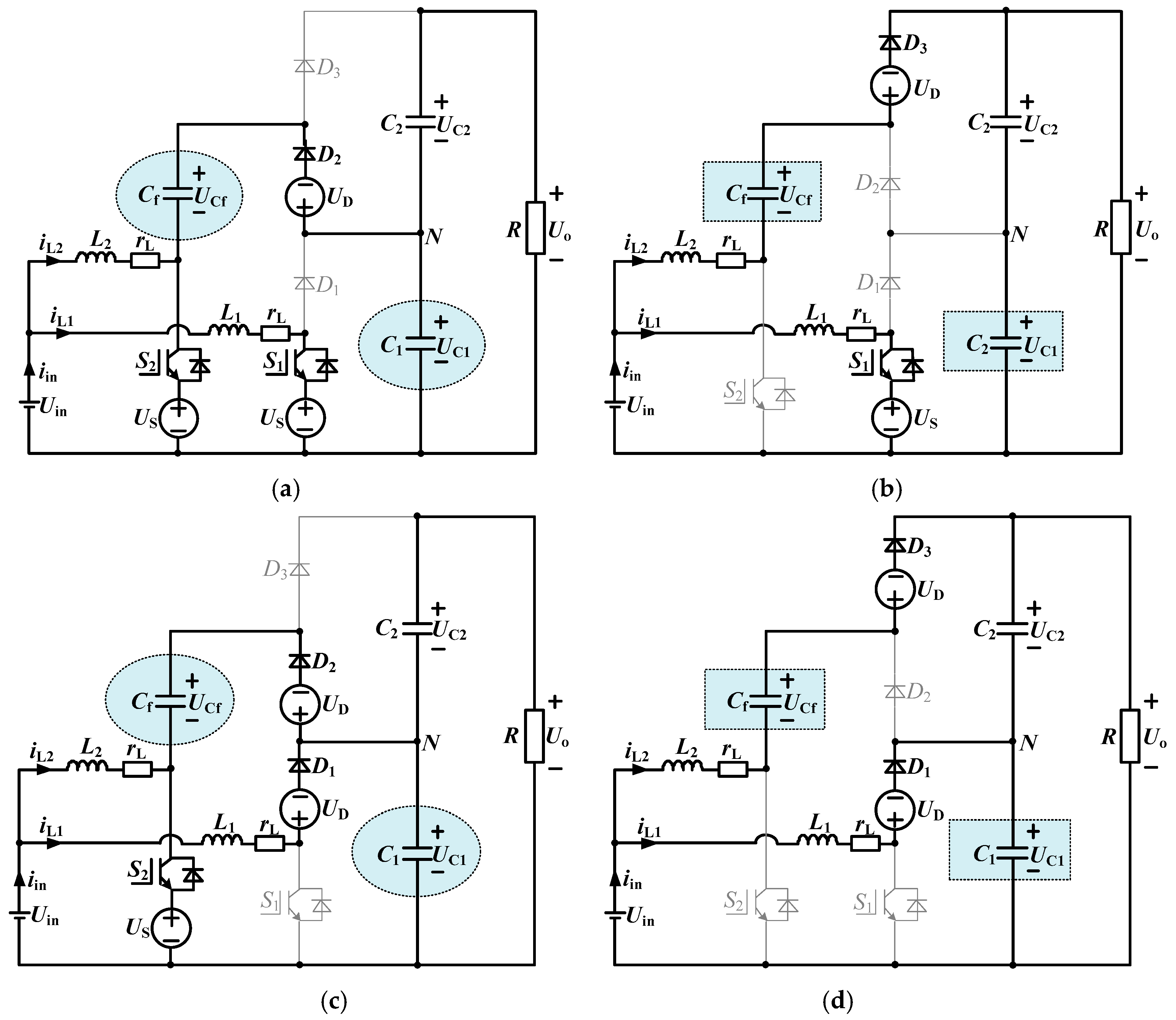

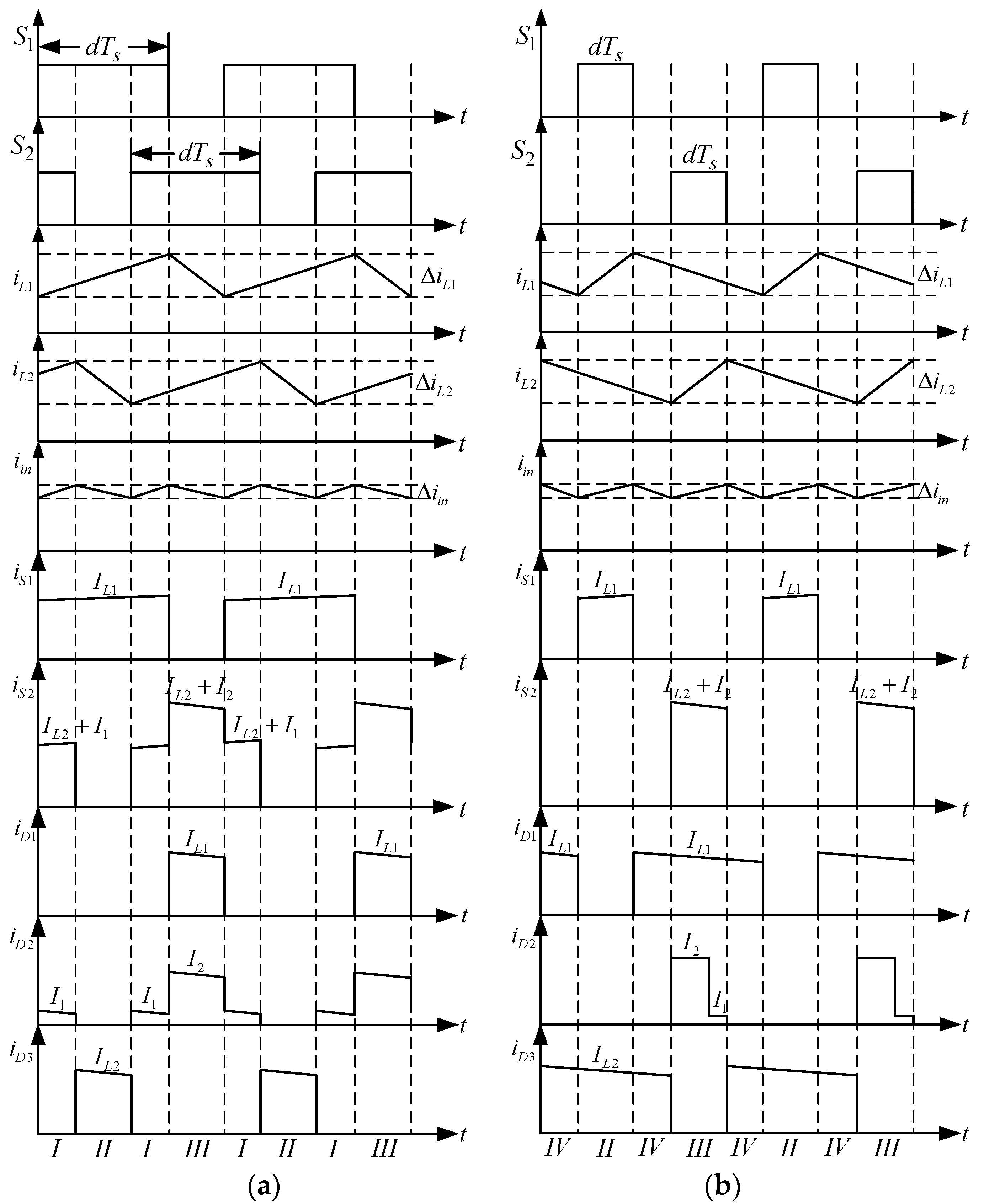

2.2. Operating Principle

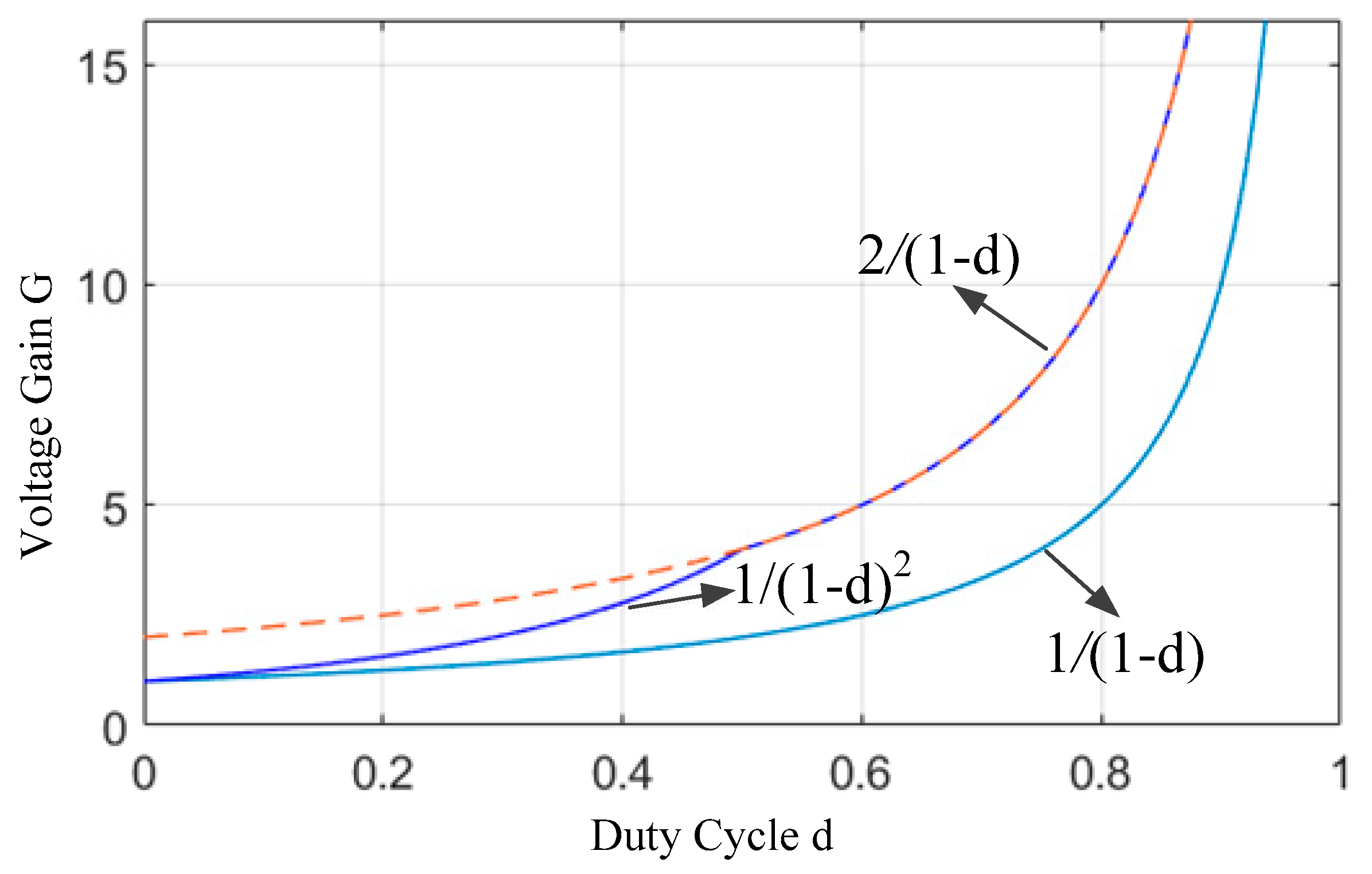

3. Performance Analysis

3.1. Component Stress

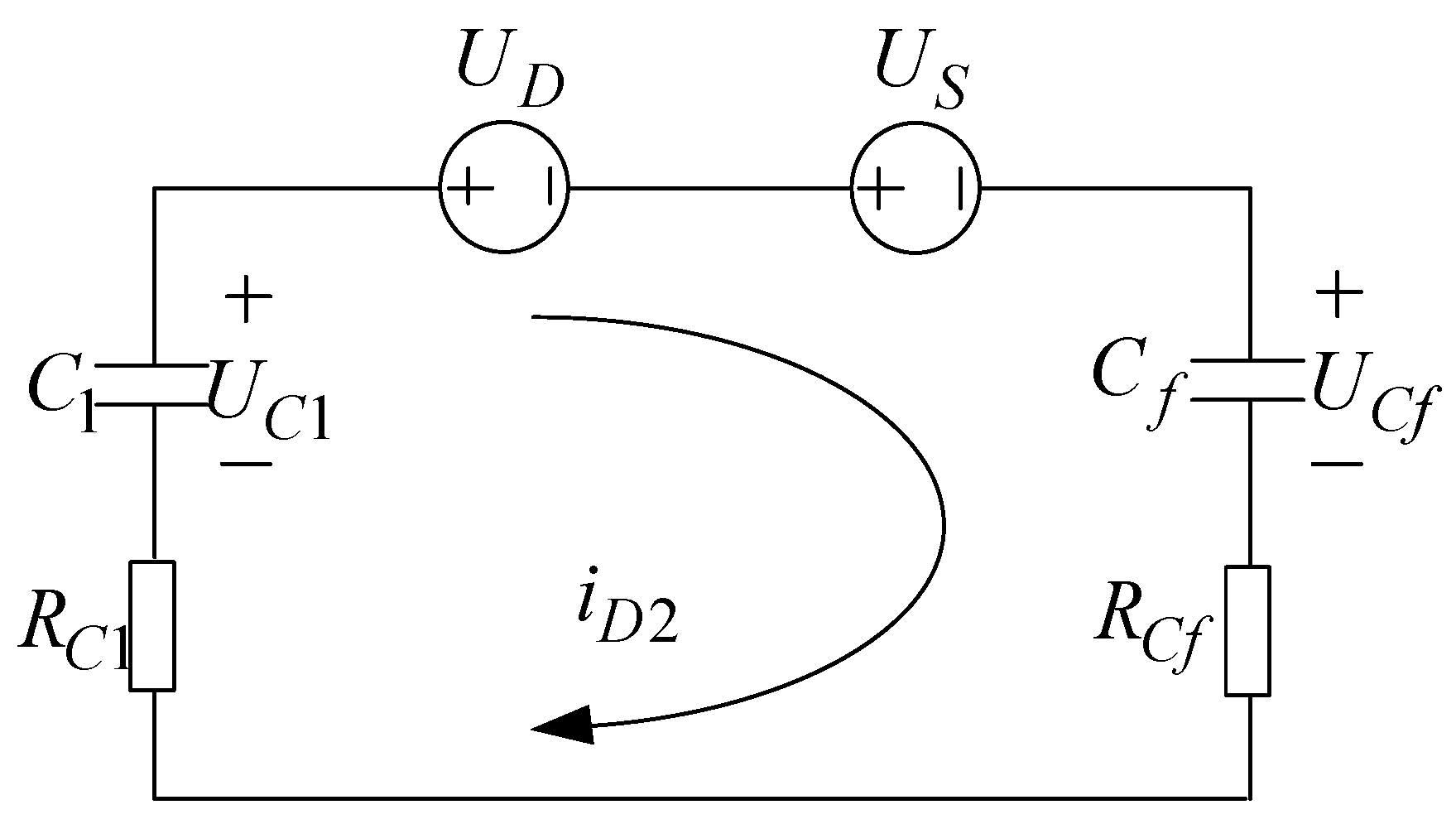

3.2. Switched-Capacitor Network

3.3. Ripple Analysis

3.4. Inrush Current Suppression

3.5. Comparative Analysis

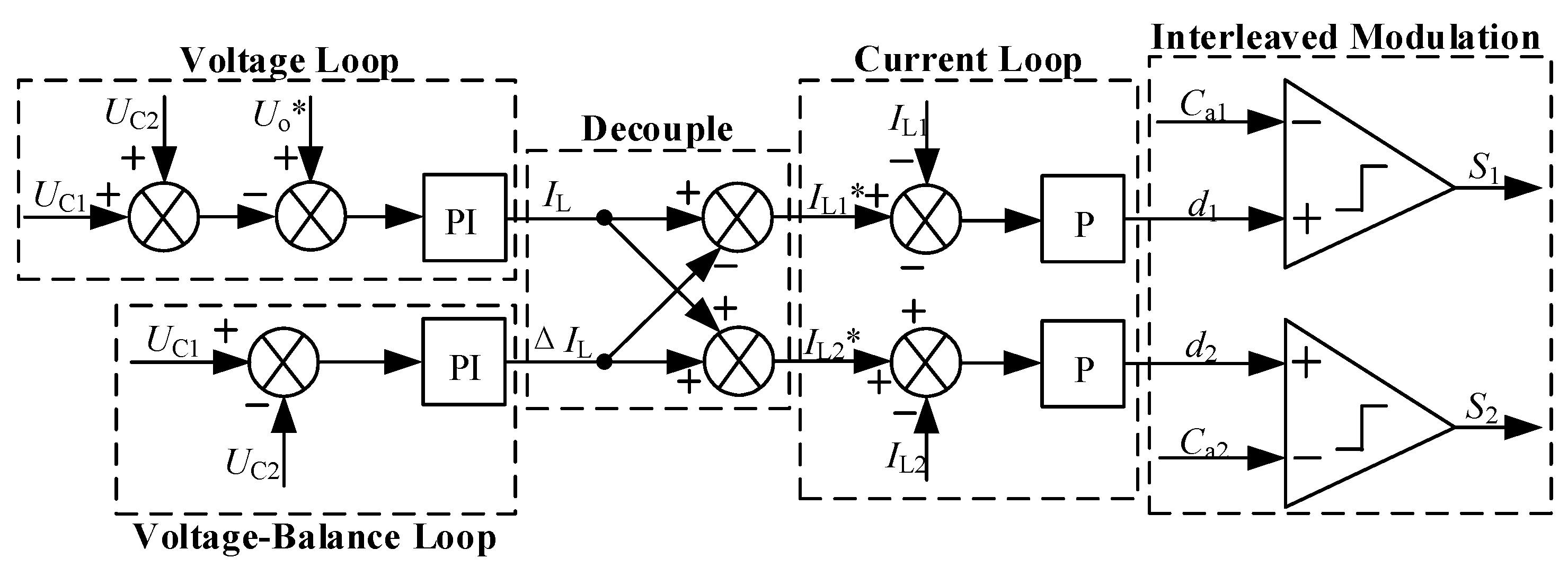

4. Three-Loop Control Strategy

4.1. Voltage Imbalance Mechanism

4.2. Three-Loop Control Strategy

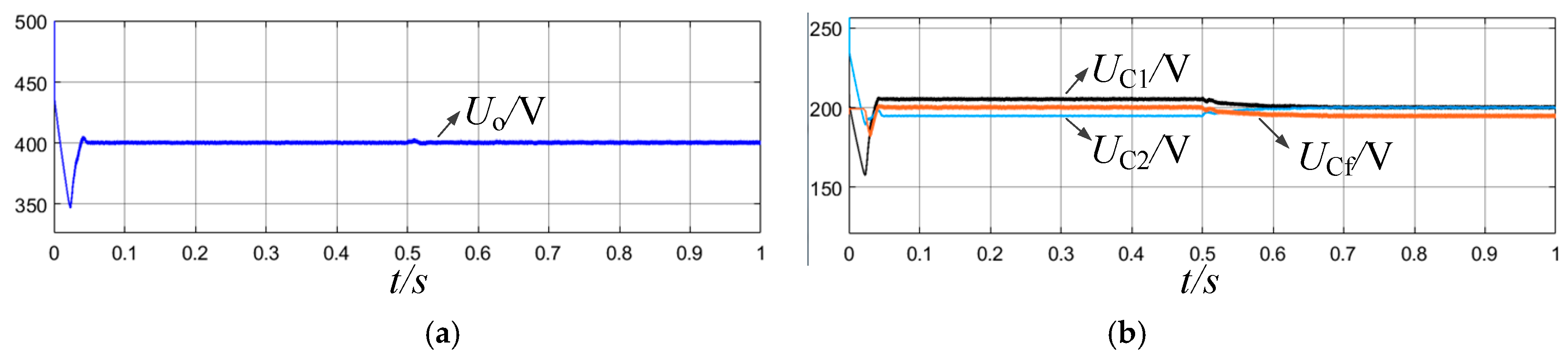

5. Simulation and Experimental Verification

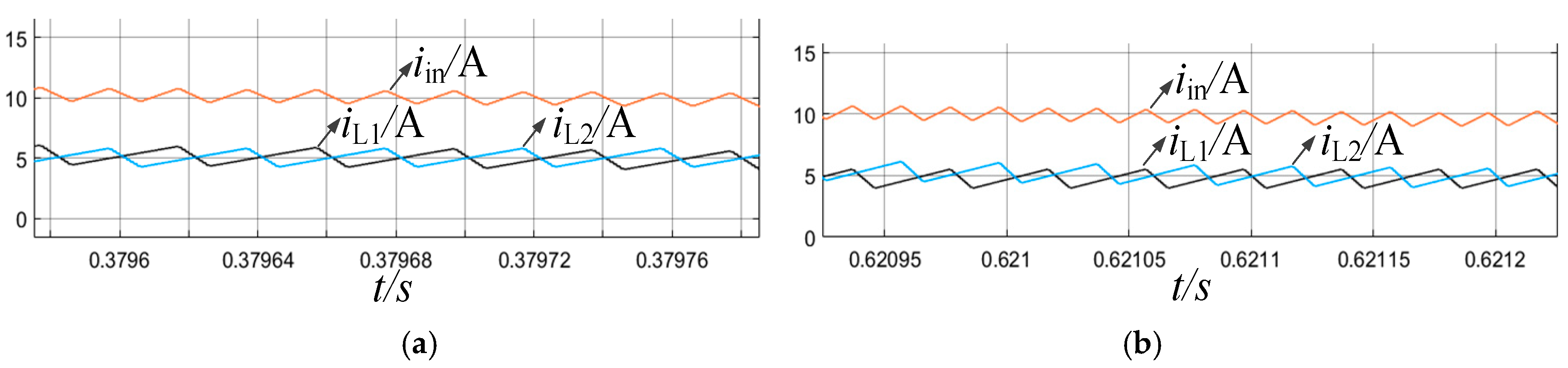

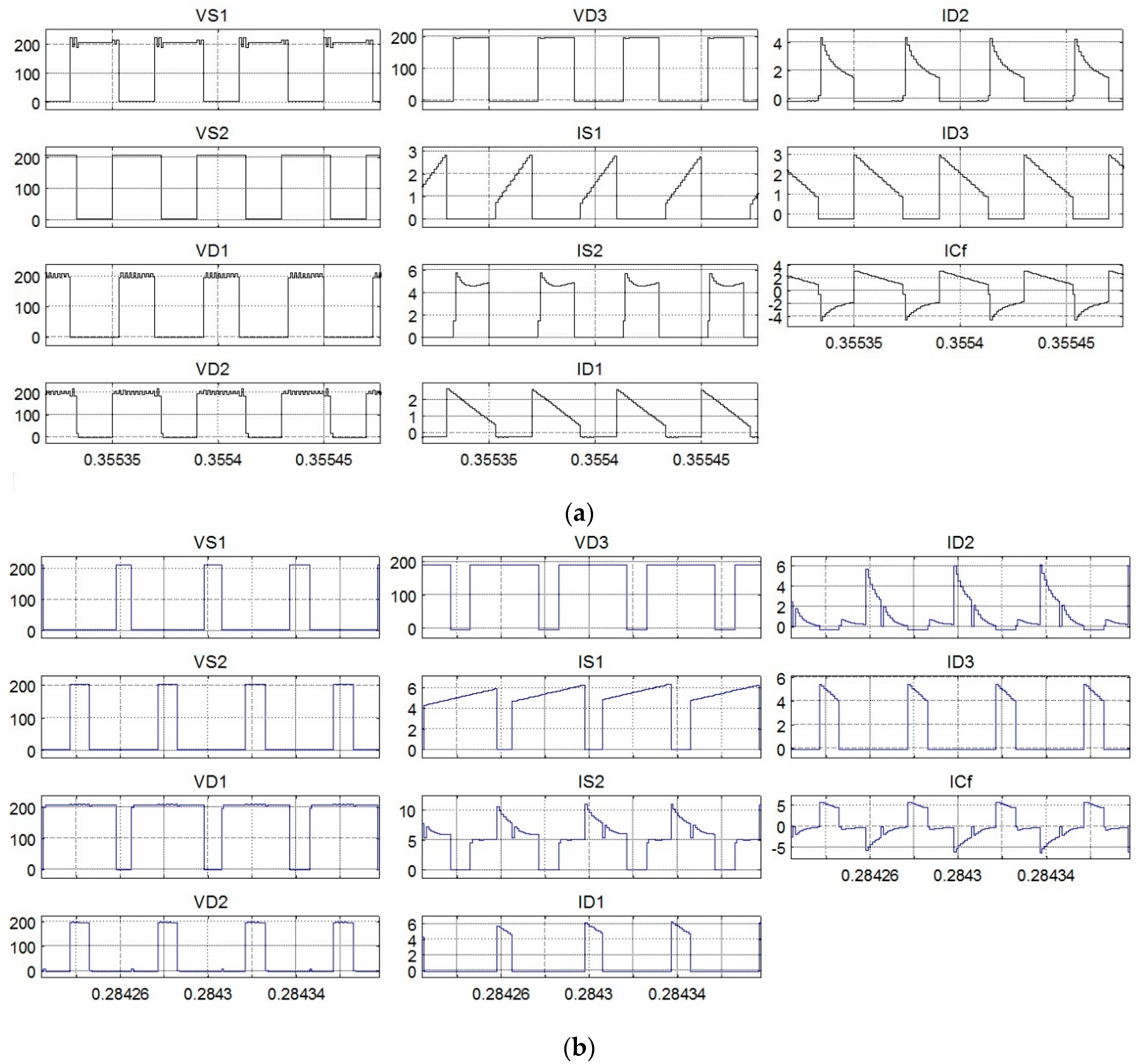

5.1. Simulation Verification

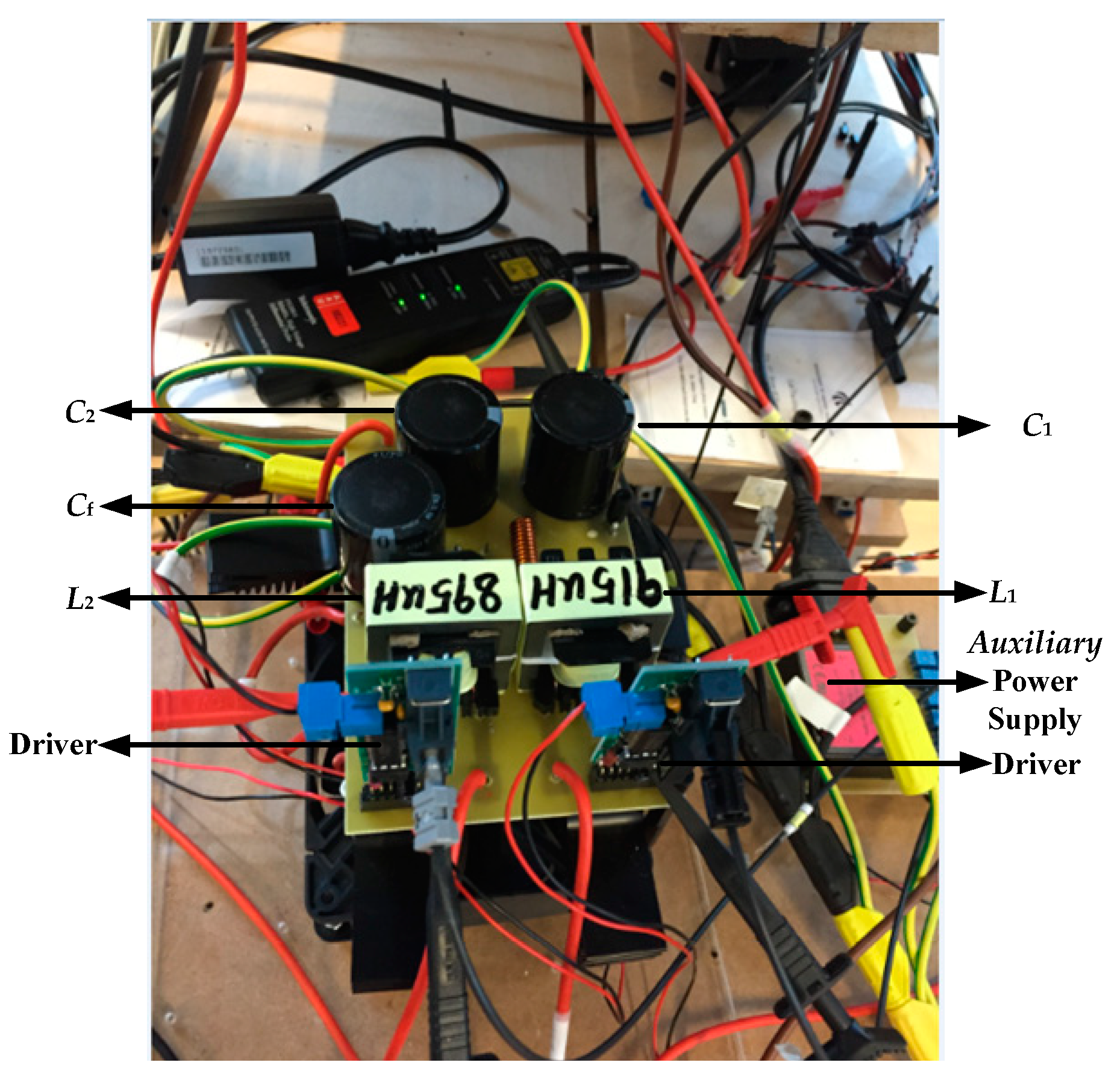

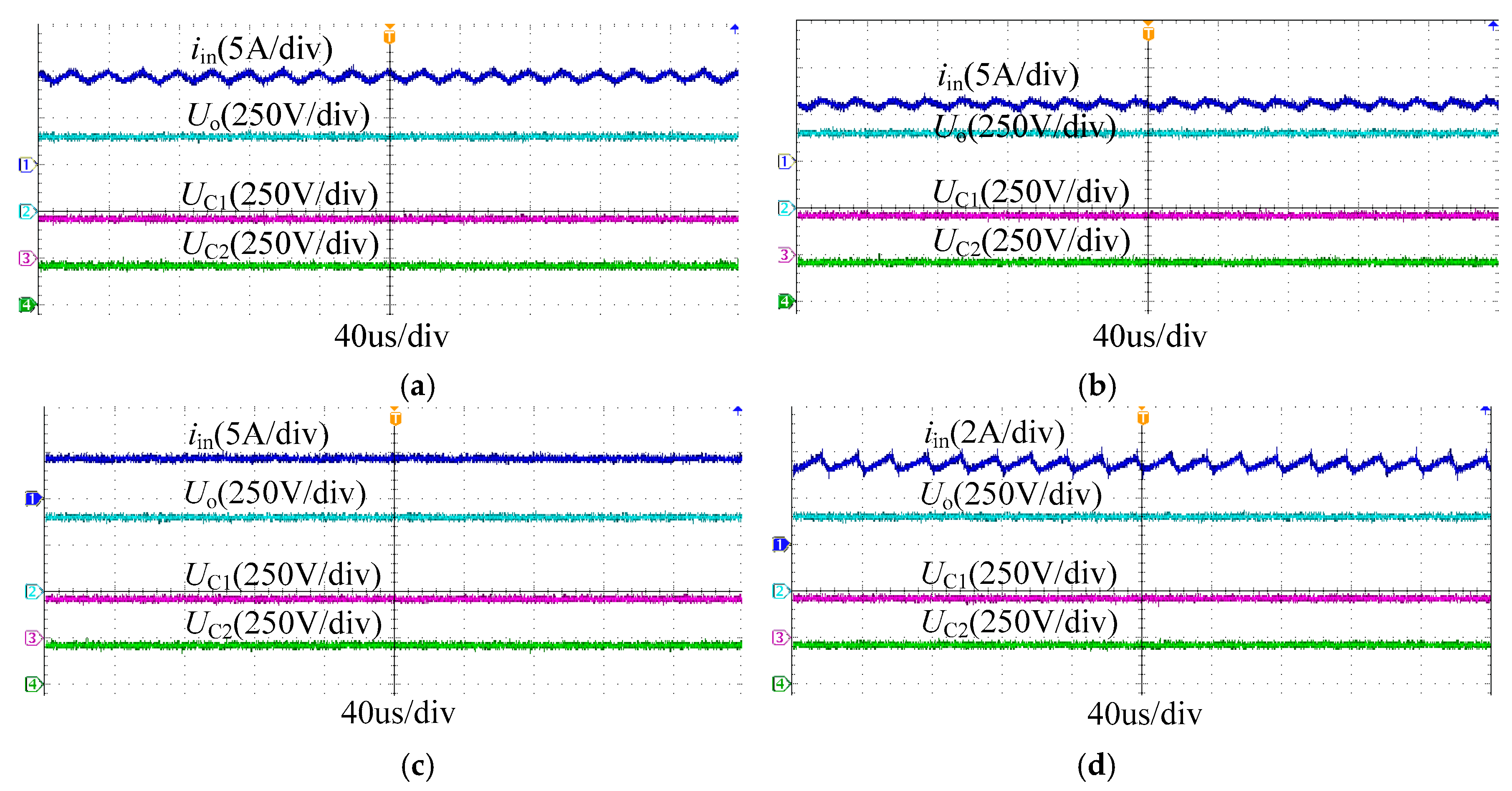

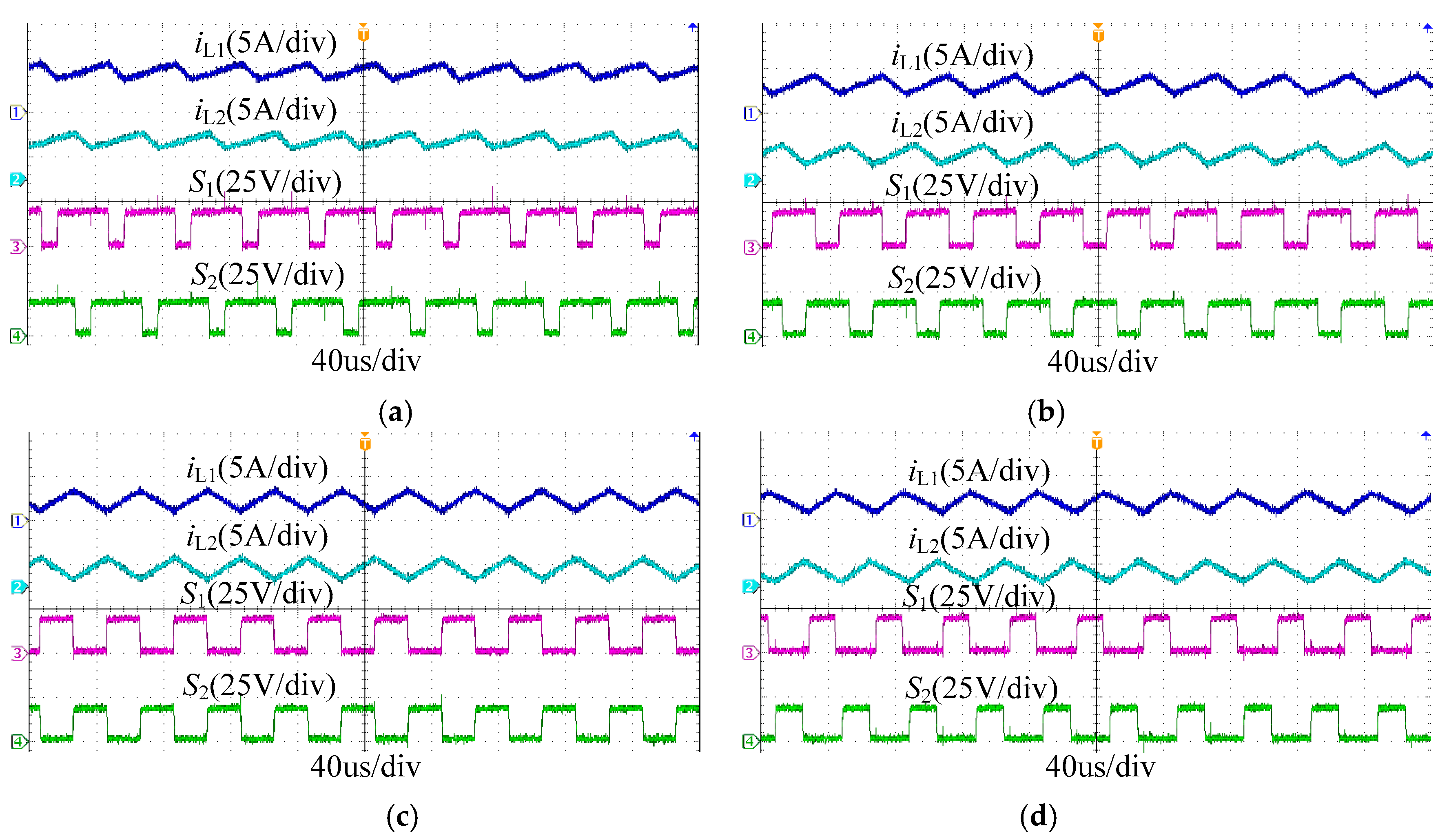

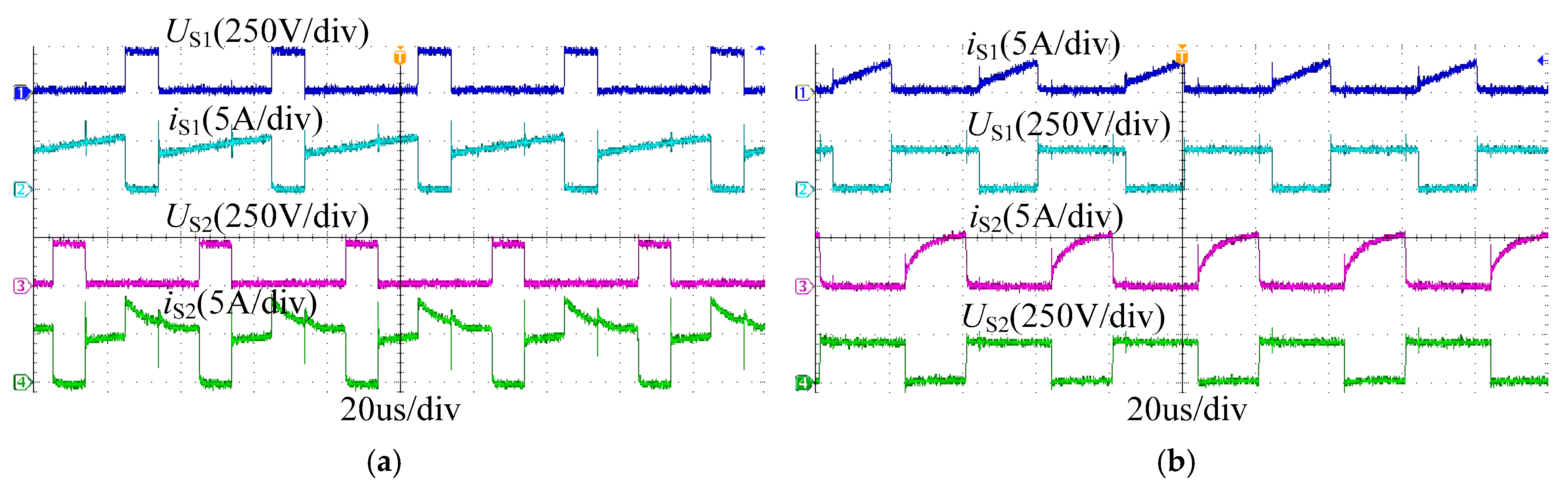

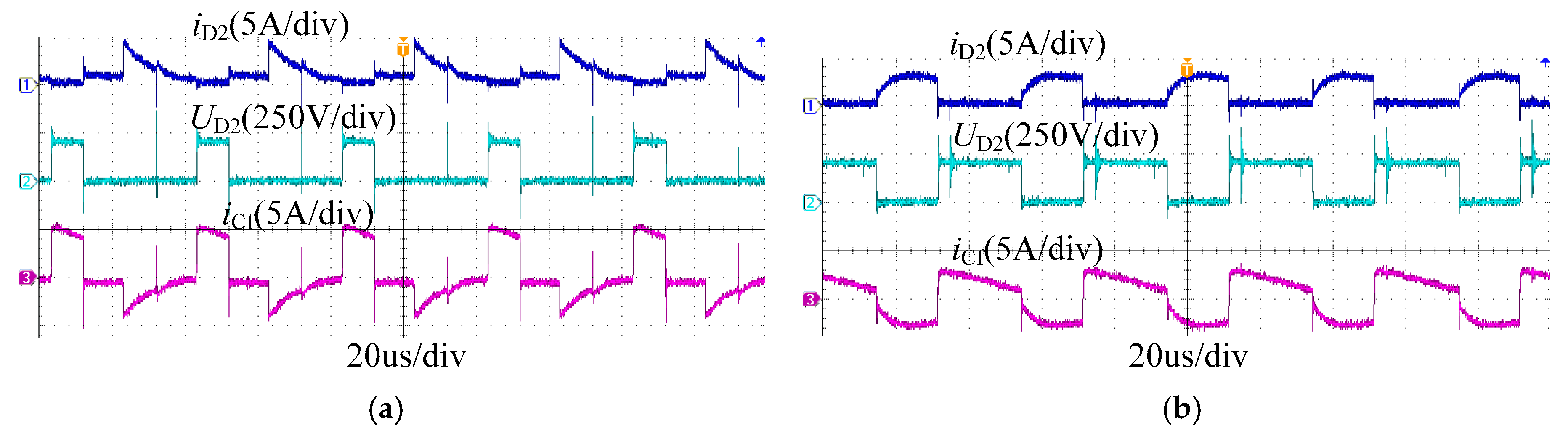

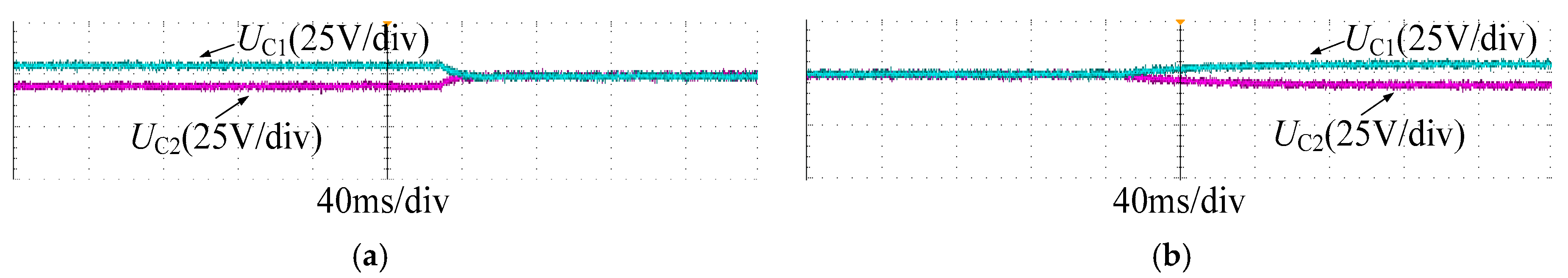

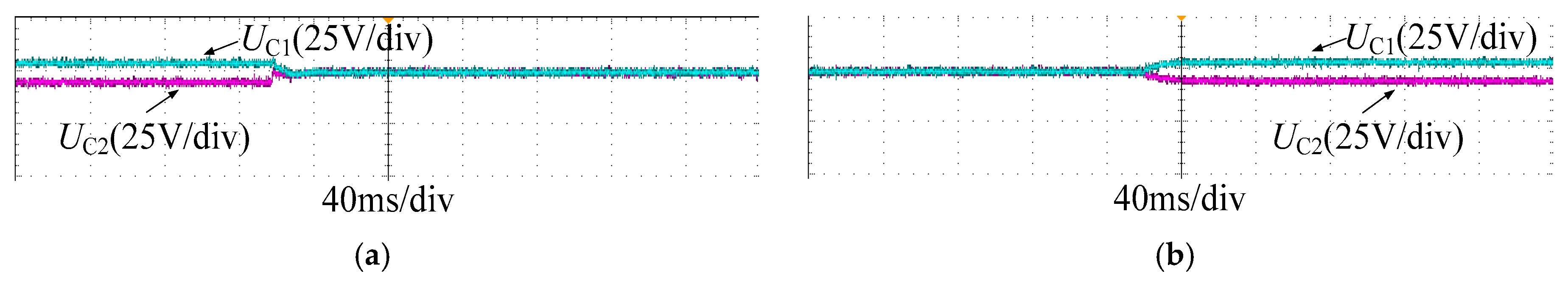

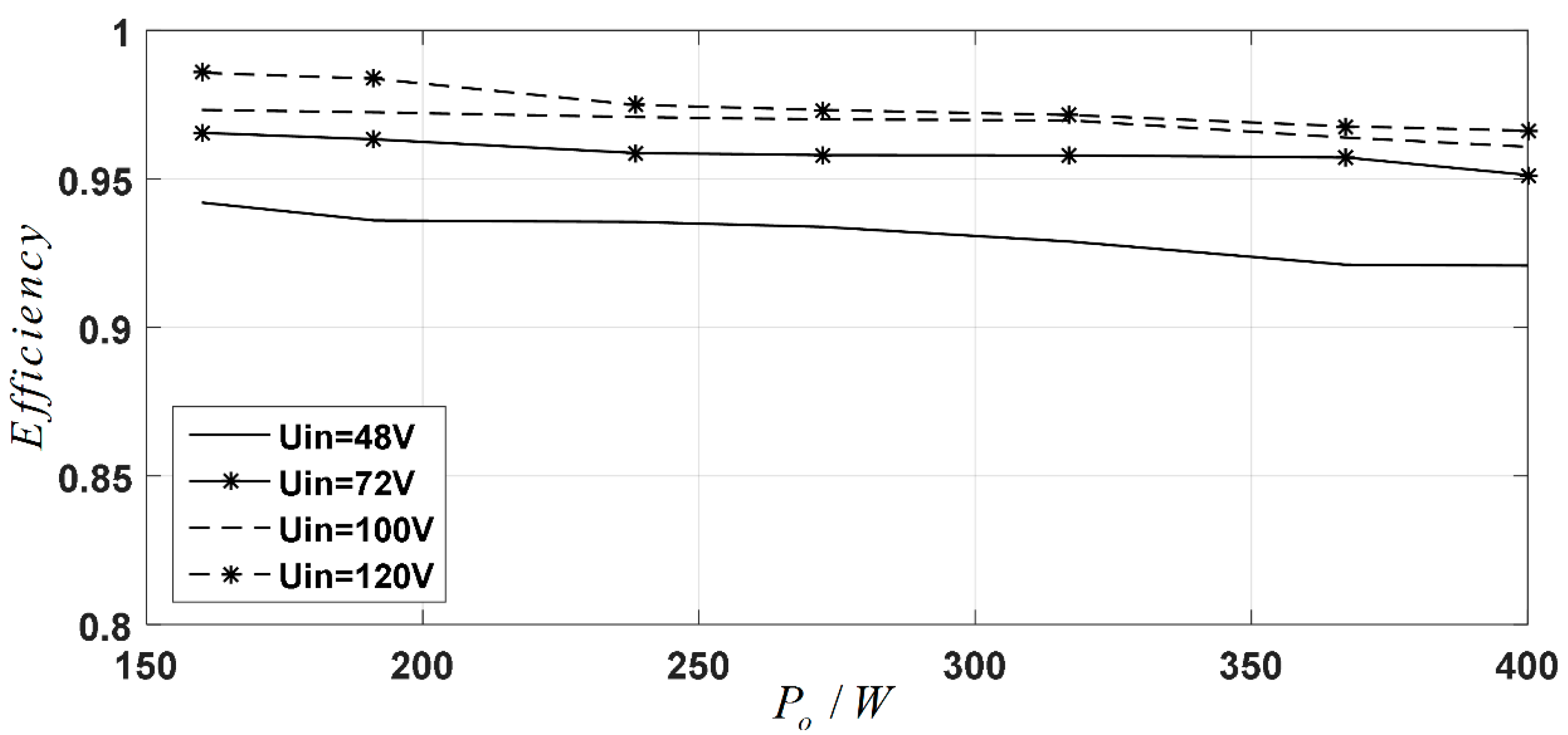

5.2. Experimental Verification

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

Nomenclature

| List of Abbreviations | |

| IPOS-SC-TLB | input-parallel-output-series switched-capacitor three-level boost |

| HVDC | high voltage direct current |

| SI | serial-interleaved |

| PI | parallel-interleaved |

| SI-TLB | serial-interleaved three-level boost |

| PIB | parallel-interleaved boost |

| SI-FC-TLB | serial-interleaved flying-capacitor three-level boost |

| PI-FC-TLB | parallel-interleaved flying-capacitor three-level boost |

| PI-SFC-TLB | parallel-interleaved symmetric flying-capacitor three-level boost |

| SC-TLB | switched-capacitor three-level boost |

| IPOS-TLB1 | input-parallel-output-series three-level boost 1 |

| IPOS-TLB2 | input-parallel-output-series three-level boost 2 |

| List of Symbols | |

| Uin | average input voltage |

| Uo, Io | average output voltage and average output current |

| Uo* | output voltage reference |

| UC1, UC2, UCf | average voltages of capacitors C1, C2, Cf |

| ΔU | voltage difference between C1 and Cf, |

| iL1, iL2 | currents of inductors L1, L2 |

| IL1, IL2 | average currents of inductors L1, L2 |

| IL1*, IL2* | reference currents of inductors L1, L2 |

| ΔiL1, ΔiL2 | current ripples of inductors L1, L2 |

| Δiin | input current ripple |

| ID1, ID2, ID3 | average currents of diodes D1, D2, D3 |

| IS1, IS2 | average currents of switches S1, S2 |

| d | duty cycle |

| d1 | duty cycle of boost 1 |

| d2 | duty cycle of boost 2 |

| Δd | duty cycle difference |

References

- Yaramasu, V.; Wu, B.; Sen, P.C.; Kouro, S.; Narimani, M. High-power Wind Energy Conversion Systems: State-of-the-art and Emerging Technologies. Proc. IEEE 2015, 103, 740–788. [Google Scholar] [CrossRef]

- Yaramasu, V.; Wu, B. Predictive Control of a Three-Level Boost Converter and an NPC Inverter for High-Power PMSG-Based Medium Voltage Wind Energy Conversion Systems IEEE Trans. Power Electron. 2014, 29, 5308–5322. [Google Scholar] [CrossRef]

- Parastar, A.; Seok, J.-K. High Power Step-Up Modular Resonant DC/DC Converter for Offshore Wind Energy Systems. IEEE Energy Convers. Congr. Expos. (ECCE) 2014, 3341–3348. [Google Scholar] [CrossRef]

- Yaramasu, V.; Wu, B.; Rivera, M.; Rodriguez, J. A New Power Conversion System for Megawatt PMSG Wind Turbines Using Four-Level Converters and a Simple Control Scheme Based on Two-Step Model Predictive Strategy-Part I: Modeling and Theoretical Analysis. IEEE J. Emerg. Sel. Top. Power Electron. 2014, 2, 3–13. [Google Scholar] [CrossRef]

- Paez, J.D.; Frey, D.; Maneiro, J.; Bacha, S.; Dworakowski, P. Overview of DC-DC Converters Dedicated to HVDC Grids. IEEE Trans. Power Deliv. 2018. [Google Scholar] [CrossRef]

- Xia, C.; Gu, X.; Shi, T.; Yan, Y. Neutral-Point Potential Balancing of Three-Level Inverters in Direct-Driven Wind Energy Conversion System. IEEE Trans. Energy Convers. 2011, 26, 18–29. [Google Scholar] [CrossRef]

- Chen, J.; Wang, C.; Li, J.; Jiang, C.; Duan, C. A Nonisolated Three-Level Bidirectional DC-DC Converter. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 1566–1570. [Google Scholar]

- Hou, S.; Chen, J.; Sun, T.; Bi, X. Multi-input Step-Up Converters Based on the Switched-Diode-Capacitor Voltage Accumulator. IEEE Trans. Power Electron. 2016, 31, 381–393. [Google Scholar] [CrossRef]

- Zhou, H.; Zhou, J.; Hu, B.; Tong, C. A New Interleaved Three-level Boost Converter and Neutral-point Potential Balancing. In Proceedings of the 2013 2nd International Symposium on Instrumentation and Measurement, Sensor Network and Automation (IMSNA), Toronto, ON, Canada, 23–24 December 2013. [Google Scholar]

- Zhang, Y.; Sun, J.-T.; Wang, Y.-F. Hybrid Boost Three-Level DC-DC Converter With High Voltage Gain for Photovoltaic Generation Systems. IEEE Trans. Power Electron. 2013, 28, 3659–3664. [Google Scholar] [CrossRef]

- Andrade, A.M.S.S.; Martins, M.L.D.S. Quadratic-Boost with Stacked Zeta Converter for High Voltage Gain Applications. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 1787–1796. [Google Scholar] [CrossRef]

- Jin, K.; Yang, M.; Ruan, X.; Xu, M. Three-Level Bidirectional Converter for Fuel-Cell/Battery Hybrid Power System. IEEE Trans. Ind. Electron. 2010, 57, 1976–1986. [Google Scholar] [CrossRef]

- Rahul, J.R.; Kirubakaran, A.; Vijayakumar, D. A New Multilevel DC-DC Boost Converter for Fuel Cell based Power System. In Proceedings of the 2012 IEEE Students’ Conference on Electrical, Electronics and Computer Science (SCEECS), Bhopal, India, 1–2 March 2012. [Google Scholar]

- Hegazy, O.; Mierlo, J.V.; Lataire, P. Analysis, Modeling, and Implementation of A Multidevice Interleaved DC/DC Converter for Fuel Cell Hybrid Electric Vehicles IEEE Trans. Power Electron. 2012, 27, 4445–4458. [Google Scholar] [CrossRef]

- Ni, L.; Patterson, D.J.; Hudgins, J.L. High Power Current Sensorless Bidirectional 16-Phase Interleaved DC-DC Converter f or Hybrid Vehicle Application. IEEE Trans. Power Electron. 2012, 27, 1141–1151. [Google Scholar] [CrossRef]

- Rivera, S.; Wu, B.; Kouro, S.; Yaramasu, V.; Wang, J. Electric Vehicle Charging Station Using A Neutral-point Clamped Converter with Bipolar DC Bus. IEEE Trans. Ind. Electron. 2015, 62, 1999–2009. [Google Scholar] [CrossRef]

- Tan, L.; Wu, B.; Yaramasu, V.; Rivera, S.; Guo, X. Effective Voltage Balance Control for Bipolar-DC-Bus Fed EV Charging Station with Three-Level DC-DC Fast Charger. IEEE Trans. Ind. Electron. 2016, 63, 4031–4041. [Google Scholar] [CrossRef]

- Adam, G.P.; Gowaid, I.A.; Finney, S.J.; Holliday, D.; Williams, B.W. Review of DC-DC Converters for Multi-terminal HVDC Transmission Networks. IET Power Electron. 2016, 9, 281–296. [Google Scholar] [CrossRef] [Green Version]

- Chen, J.; Hou, S.; Deng, F.; Chen, Z. An Interleaved Five-Level Boost Converter with Voltage-Balance Control. J. Power Electron. 2016, 16, 1735–1742. [Google Scholar] [CrossRef]

- Kakigano, H.; Miura, Y.; Ise, T. Distribution Voltage Control for DC Microgrids Using Fuzzy Control and Gain-Scheduling Technique. IEEE Trans. Power Electron. 2013, 28, 2246–2258. [Google Scholar] [CrossRef]

- Jang, Y.; Jovanovic, M.M. Interleaved Boost Converter with Intrinsic Voltage-Doubler Characteristic for Universal-Line PFC Front End. IEEE Trans. Power Electron. 2007, 22, 1394–1401. [Google Scholar] [CrossRef]

- Zhou, L.-W.; Zhu, B.-X.; Luo, Q.-M.; Chen, S. Interleaved Non-isolated High Step-up DC-DC Converter Based on the Diode-capacitor Multiplier. IET Power Electron. 2014, 7, 390–397. [Google Scholar] [CrossRef]

- Franco, L.C.; Pfitscher, L.L.; Gules, R. A New High Static Gain Nonisolated DC-DC Converter. In Proceedings of the 34th Annual Power Electronics Specialist Conference IEEE, Acapulco, Mexico, 15–19 June 2003. [Google Scholar]

- Kajangpan, K.; Neammenee, B. High Gain Double Interleave Technique with Maximum Peak Power Tracking for Wind Turbine Converter. In Proceedings of the 2009 6th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology Pattaya, Chonburi, Thailand, 6–9 May 2009. [Google Scholar]

- Forest, F.; Huselstein, J.J.; Martiré, T.; Flumian, D.; Meynard, T.A.; Abdelli, Y.; Lienhardt, A.M. A Nonreversible 10-kW High Step-Up Converter Using a Multicell Boost Topology. IEEE Trans. Power Electron. 2018, 33, 151–160. [Google Scholar] [CrossRef]

- Rosas-Caro, J.C.; Ramirez, J.M.; Peng, F.Z.; Valderrabano, A. A DC-DC Multilevel Boost Converter. IET Power Electron. 2010, 3, 129–137. [Google Scholar] [CrossRef]

- Parastar, A.; Kang, Y.C.; Seok, J.-K. Multilevel Modular DC-DC Power Converter for High-Voltage DC-Connected Offshore Wind Energy Applications. IEEE Trans. Ind. Electron. 2015, 62, 2879–2890. [Google Scholar] [CrossRef]

- Zhang, X.; Green, T.C. The Modular Multilevel Converter for High Step-Up Ratio DC-DC Conversion. IEEE Trans. Ind. Electron. 2015, 62, 4925–4936. [Google Scholar] [CrossRef]

- Ferreira, J.A. The Multilevel Modular DC Converter. IEEE Trans. Power Electron. 2013, 28, 4460–4465. [Google Scholar] [CrossRef]

- Zhang, X.; Green, T.C. The New Family of High Step Ratio Modular Multilevel DC-DC Converters. In Proceedings of the 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015. [Google Scholar]

- Hagar, A.A.; Lehn, P.W. Comparative Evaluation of a New Family of Transformerless Modular DC-DC Converters for High-Power Applications. IEEE Trans. Power Deliv. 2014, 29, 444–452. [Google Scholar] [CrossRef]

- Filsoof, K.; Lehn, P.W. A Bidirectional Modular Multilevel DC-DC Converter of Triangular Topology. IEEE Trans. Power Electron. 2015, 30, 54–64. [Google Scholar] [CrossRef]

- Athab, H.; Yazdani, A.; Wu, B. A Transformerless DC-DC Converter with Large Voltage Ratio for MV DC Grids. IEEE Trans. Power Deliv. 2014, 29, 1877–1885. [Google Scholar] [CrossRef]

- Chen, W.; Huang, A.Q.; Li, C.; Wang, G.; Gu, W. Analysis and Comparison of Medium Voltage High Power DC-DC Converters for Offshore Wind Energy Systems. IEEE Trans. Power Electron. 2013, 28, 2014–2023. [Google Scholar] [CrossRef]

- Mohan, T.; Undeland, M.; Robbins, W.P. Power Electronics—Converters, Applications, and Design; John Wiley & Sons Inc.: Hoboken, NJ, USA, 2003. [Google Scholar]

- Erickson, R.W.; Maksimovic, D. Fundamentals of Power Electronics, 2nd ed.; Kluwer Academic Publisher: Norwell, MA, USA, 2001. [Google Scholar]

| Structure | Voltage Level | Function | Control |

|---|---|---|---|

| SI | U0, U1, … Un−1 | Divide voltage | Voltage-balance |

| PI | Un−1 | Shunt current | Current-balance |

| Topology | L | S | D | C | DS | G (d ≤ 0.5) | G (d > 0.5) | UVPS | UVPD | UVPC | IVPS1 | IVPS2 | IVPD | Current Ripple | Self-Balance | Same Ground |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SC-TLB | 1 | 1 | 3 | 3 | 1 | 2/(1 − d) | 0.5Uo | 0.5Uo | 0.5Uo | dIin | - | Io | Large | Yes | Yes | |

| SI-TLB | 2 | 2 | 2 | 2 | 2 | 1/(1 − d) | 0.5Uo | 0.5Uo | 0.5Uo | dIin | dIin | Io | Small | No | No | |

| SI-FC-TLB | 2 | 2 | 2 | 2 | 2 | 1/(1 − d) | 0.5Uo | 0.5Uo | 0.5Uo | dIin | dIin | Io | Small | No | Yes | |

| PI-FC-TLB | 2 | 2 | 2 | 2 | 1 | 1/(1 − d)2 | 2/(1 − d) | 0.5Uo | Uo | Uo | 0.5dIin | 0.5dIin | Io | Small | Yes | Yes |

| PI-SFC-TLB | 2 | 2 | 4 | 3 | 1 | 2/(1 − d) | 0.5Uo | Uo | Uo | (1 + d)Iin/4 | (1 + d)Iin/4 | 0.5Io | Small | Yes | Yes | |

| IPOS-TLB1 | 2 | 2 | 2 | 2 | 1 | 1/(1 − d)2 | 2/(1 − d) | 0.5Uo | Uo | 0.5Uo | 0.5dIin | 0.5dIin | Io | Small | No | Yes |

| IPOS-TLB2 | 2 | 2 | 2 | 2 | 2 | (1 + d)/(1 − d) | Uo/(1 + d) | Uo/(1 + d) | Uo/(1 + d) | 0.5dIin | 0.5dIin | Io | Small | No | No | |

| Proposed | 2 | 2 | 3 | 3 | 1 | 2/(1 − d) | 0.5Uo | 0.5Uo | 0.5Uo | 0.5dIin | 0.5Iin | Io | Small | Yes | Yes | |

| Components | Parameters |

|---|---|

| Input voltage Uin | 48 V–120 V |

| Output voltage Uo Switching frequency fs | 400 V 25 kHz |

| Output power Po | 400 W |

| Switches S1, S2 | G80N60, 2.4 V voltage drop |

| Diodes D1, D2 | DSEP30-06B, 2.0 V voltage drop |

| Inductors L1, L2 | 915 μH, 895 μH, 0.1 ohm equivalent series resistance |

| Capacitors C1, C2, Cf | 470 μF, 0.28 ohm equivalent series resistance |

| Driver | A3120 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, J.; Wang, C.; Li, J. An Input-Parallel-Output-Series Switched-Capacitor Three-level Boost Converter with a Three-Loop Control Strategy. Energies 2018, 11, 2631. https://doi.org/10.3390/en11102631

Chen J, Wang C, Li J. An Input-Parallel-Output-Series Switched-Capacitor Three-level Boost Converter with a Three-Loop Control Strategy. Energies. 2018; 11(10):2631. https://doi.org/10.3390/en11102631

Chicago/Turabian StyleChen, Jianfei, Caisheng Wang, and Jian Li. 2018. "An Input-Parallel-Output-Series Switched-Capacitor Three-level Boost Converter with a Three-Loop Control Strategy" Energies 11, no. 10: 2631. https://doi.org/10.3390/en11102631