Robust Control of Shunt Active Power Filters: A Dynamical Model-Based Approach with Verified Controllability

Abstract

:1. Introduction

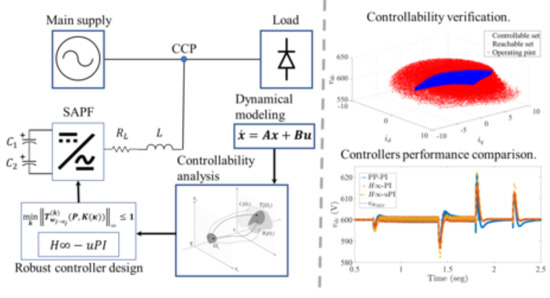

2. TLSC SAPF Dynamical Modeling

3. Control Structure Design, Performance Indices, and Controllability Verification

3.1. Control Structure Design

3.2. Performance Indices

3.3. Controllability Index

4. Results

4.1. Controllability Verification and Controllability Index Computation

4.2. Controllers Synthesis and Performance Evaluation

4.3. TLSC SAPF Compensation Performance

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Appendix A. Set-Theoretic Approach for the Controllability Verification

| Algorithm A1: Controllability verification algorithm |

| Input: Output: , , and

|

References

- Tofoli, F.; Sanhueza, S.; de Oliveira, A. On the study of losses in cables and transformers in nonsinusoidal conditions. IEEE Trans. Power Deliv. 2006, 21, 971–978. [Google Scholar] [CrossRef]

- Artemenko, M.; Batrak, L.; Polishchuk, S.; Mykhalskyi, V.; Shapoval, I. Minimization of cable losses in three-phase four-wire systems by means of instantaneous compensation with shunt active filters. In Proceedings of the 2013 IEEE XXXIII International Scientific Conference, Electronics and Nanotechnology (ELNANO), Kiev, Ukraine, 16–19 April 2013; pp. 359–362. [Google Scholar] [CrossRef]

- Said, D.; Nor, K. Effects of harmonics on distribution transformers. In Proceedings of the 2008 AUPEC’08 Australasian Universities, Power Engineering Conference, Sydney, Australia, 14–17 December 2008; pp. 1–5. [Google Scholar]

- Liu, R.; Mi, C.; Gao, D. Modeling of Eddy-Current Loss of Electrical Machines and Transformers Operated by Pulsewidth-Modulated Inverters. IEEE Trans. Magn. 2008, 44, 2021–2028. [Google Scholar] [CrossRef]

- Thapar, A.; Saha, T.; Dong, Z.Y. Investigation of power quality categorisation and simulating it’s impact on sensitive electronic equipment. In Proceedings of the 2004 IEEE Power Engineering Society General Meeting, San Francisco, CA, USA, 12–16 June 2004; Volume 1, pp. 528–533. [Google Scholar] [CrossRef] [Green Version]

- Pindado, R.; Rodríguez, P.; Pou, J.; Candela, I. Controller for Three-Phase Four-Wire Shunt Active Power Filter by DC-Bus Energy Regulation. Renew. Energy Power Qual. J. 2004, 1, 371–378. [Google Scholar] [CrossRef]

- Rafi, F.H.M.; Hossain, M.; Rahman, M.S.; Taghizadeh, S. An overview of unbalance compensation techniques using power electronic converters for active distribution systems with renewable generation. Renew. Sustain. Energy Rev. 2020, 125, 109812. [Google Scholar] [CrossRef]

- Khadkikar, V.; Chandra, A.; Singh, B. Digital signal processor implementation and performance evaluation of split capacitor, four-leg and three H-bridge-based three-phase four-wire shunt active filters. IET Power Electron. 2011, 4, 463–470. [Google Scholar] [CrossRef]

- Cao, W.; Liu, K.; Wu, M.; Xu, S.; Zhao, J. An Improved Current Control Strategy Based on Particle Swarm Optimization and Steady-State Error Correction for SAPF. IEEE Trans. Ind. Appl. 2019, 55, 4268–4274. [Google Scholar] [CrossRef]

- Pandove, G.; Singh, M. Robust Repetitive Control Design for a Three-Phase Four Wire Shunt Active Power Filter. IEEE Trans. Ind. Inform. 2019, 15, 2810–2818. [Google Scholar] [CrossRef]

- Zhang, Y.; Dai, K.; Chen, X.; Kang, Y.; Dai, Z. Stability Analysis of SAPF by Viewing DFT as Cluster of BPF for Selective Harmonic Suppression and Resonance Damping. IEEE Trans. Ind. Appl. 2019, 55, 1598–1607. [Google Scholar] [CrossRef]

- Mu, X.; Wang, J.; Wu, W.; Blaabjerg, F. A Modified Multifrequency Passivity-Based Control for Shunt Active Power Filter with Model-Parameter-Adaptive Capability. IEEE Trans. Ind. Electron. 2018, 65, 760–769. [Google Scholar] [CrossRef]

- Xu, C.; Dai, K.; Chen, X.; Peng, L.; Zhang, Y.; Dai, Z. Parallel Resonance Detection and Selective Compensation Control for SAPF with Square-Wave Current Active Injection. IEEE Trans. Ind. Electron. 2017, 64, 8066–8078. [Google Scholar] [CrossRef]

- Muñoz-Galeano, N.; Orts-Grau, S.; Seguí-Chilet, S.; Gimeno-Sales, F.J.; López-Lezama, J.M. Deterministic Algorithm for Selective Shunt Active Power Compensators According to IEEE Std. 1459. Energies 2017, 10, 1791. [Google Scholar] [CrossRef] [Green Version]

- Bacha, S.; Munteanu, I.; Bratcu, A. General Control Principles of Power Electronic Converters. In Power Electronic Converters Modeling and Control; Advanced Textbooks in Control and Signal Processing; Springer: London, UK, 2014; pp. 179–186. [Google Scholar] [CrossRef]

- Hägglund, T. The one-third rule for PI controller tuning. Comput. Chem. Eng. 2019, 127, 25–30. [Google Scholar] [CrossRef]

- Apkarian, P.; Noll, D. Optimization-Based Control Design Techniques and Tools. In Encyclopedia of Systems and Control; Springer: London, UK, 2015; pp. 1–12. [Google Scholar] [CrossRef] [Green Version]

- Apkarian, P.; Noll, D. The H∞ Control Problem is Solved. Aerosp. Lab 2017, 1–11. [Google Scholar] [CrossRef]

- Apkarian, P.; Dao, M.N.; Noll, D. Parametric Robust Structured Control Design. IEEE Trans. Autom. Control 2015, 60, 1857–1869. [Google Scholar] [CrossRef] [Green Version]

- Panigrahi, R.; Subudhi, B. Performance Enhancement of Shunt Active Power Filter Using a Kalman Filter-Based H-∞ Control Strategy. IEEE Trans. Power Electron. 2016, 32, 2622–2630. [Google Scholar] [CrossRef]

- Huang, L.; Xin, H.; Dörfler, F. H-∞-Control of Grid-Connected Converters: Design, Objectives and Decentralized Stability Certificates. IEEE Trans. Smart Grid 2020. [Google Scholar] [CrossRef]

- Bouzid, A.M.; Sicard, P.; Cheriti, A.; Bouhamida, M.; Benghanem, M. Structured H-∞ design method of PI controller for grid feeding connected voltage source inverter. In Proceedings of the 2015 IEEE 3rd International Conference on Control, Engineering & Information Technology (CEIT), Tlemcen, Algeria, 25–27 May 2015; pp. 1–6. [Google Scholar]

- Li, X.; Zhang, Z. Study on the output controllability of BUCK-BOOST Converter. In Proceedings of the 2017 IEEE International Conference on Mechatronics and Automation (ICMA), Takamatsu, Japan, 6–9 August 2017; pp. 107–112. [Google Scholar]

- Kalman, R. On the general theory of control systems. IRE Trans. Autom. Control 1959, 4, 110. [Google Scholar] [CrossRef]

- Bhattacharyya, D.; Pati, K.C. Controllability analysis for switched linear system model of DC-DC flyback converter using controllability transition approach. Int. J. Control 2020, 1–9. [Google Scholar] [CrossRef]

- Osorio, J.C.C. Una Aproximación al Diseño y Control Total de Planta Usando Controlabilidad de Estado. Doctorado en Ingeniería—Sistemas Energéticos Línea de Investigación: Diseño y Control de Procesos Químicos. Ph.D. Thesis, Universidad Nacional de Colombia Sede Medellín, Antioquia, Colombia, 2013. [Google Scholar]

- García, P. Efecto de las Condiciones Iniciales Sobre la Controlabilidad de Estado en Procesos por Lotes. Magister en Ingeniería Química. Master’s Thesis, Universidad Nacional de Colombia, Sede Medellín, Facultad de Minas, Antioquia, Colombia, 2012. [Google Scholar]

- Alzate, A.; Gómez, L.; Alvarez, H. Diseño Simultáneo de Procesos y su control usando Teoría de Conjuntos. Prospect 2015, 13, 12–23. [Google Scholar] [CrossRef] [Green Version]

- Calderón, C.; Gómez, L.; Alvarez, H. Nonlinear state space controllability: Set theory vs differential geometry. In Proceedings of the Congreso Latinoamericano de Control Automático, Lima, Peru, 23–26 October 2012. [Google Scholar]

- Gómez, L.; Botero, H.; Alvarez, H.; di Sciascio, F. Análisis de la Controlabilidad de Estado de Sistemas Irreversibles Mediante Teoría de Conjuntos. Rev. Iberoam. Automática Informática Industrial {RIAI} 2015, 12, 145–153. [Google Scholar] [CrossRef] [Green Version]

- Escobar, G.; Valdez, A.; Torres-Olguin, R.; Martinez-Montejano, M. A Model-Based Controller for a Three-Phase Four-Wire Shunt Active Filter with Compensation of the Neutral Line Current. IEEE Trans. Power Electron. 2007, 22, 2261–2270. [Google Scholar] [CrossRef]

- Orts-Grau, S.; Gimeno-Sales, F.; Segui-Chilet, S.; Abellan-Garcia, A.; Alcaniz, M.; Masot-Peris, R. Selective Shunt Active Power Compensator Applied in Four-Wire Electrical Systems Based on IEEE Std. 1459. IEEE Trans. Power Deliv. 2008, 23, 2563–2574. [Google Scholar] [CrossRef]

- Orts-Grau, S.; Gimeno-Sales, F.; Abellan-Garcia, A.; Segui-Chilet, S.; Alfonso-Gil, J. Improved Shunt Active Power Compensator for IEEE Standard 1459 Compliance. IEEE Trans. Power Deliv. 2010, 25, 2692–2701. [Google Scholar] [CrossRef] [Green Version]

- Choi, W.H.; Lam, C.S.; Wong, M.C.; Han, Y.D. Analysis of DC-Link Voltage Controls in Three-Phase Four-Wire Hybrid Active Power Filters. IEEE Trans. Power Electron. 2013, 28, 2180–2191. [Google Scholar] [CrossRef]

- Sun, Z.; Zhang, Z.; Tsao, T.C. Trajectory tracking and disturbance rejection for linear time-varying systems: Input/output representation. Syst. Control Lett. 2009, 58, 452–460. [Google Scholar] [CrossRef]

- Montero, M.; Cadaval, E.; Gonzalez, F. Comparison of Control Strategies for Shunt Active Power Filters in Three-Phase Four-Wire Systems. IEEE Trans. Power Electron. 2007, 22, 229–236. [Google Scholar] [CrossRef]

- Reginatto, R.; Ramos, R. On electrical power evaluation in dq coordinates under sinusoidal unbalanced conditions. IET Gener. Transm. Distrib. 2014, 8, 976–982. [Google Scholar] [CrossRef] [Green Version]

- Po-Ngam, S. The simplified control of three-phase four-leg shunt active power filter for harmonics mitigation, load balancing and reactive power compensation. In Proceedings of the 2014 11th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology (ECTI-CON), Nakhon Ratchasima, Thailand, 14–17 May 2014; pp. 1–6. [Google Scholar]

- Orts, S.; Gimeno-Sales, F.; Abellan, A.; Segui-Chilet, S.; Alcaniz, M.; Masot, R. Achieving Maximum Efficiency in Three-Phase Systems with a Shunt Active Power Compensator Based on IEEE Std. 1459. IEEE Trans. Power Deliv. 2008, 23, 812–822. [Google Scholar] [CrossRef]

- Tang, Y.; Loh, P.C.; Wang, P.; Choo, F.H.; Gao, F.; Blaabjerg, F. Generalized Design of High Performance Shunt Active Power Filter with Output LCL Filter. IEEE Trans. Ind. Electron. 2012, 59, 1443–1452. [Google Scholar] [CrossRef]

- Apkarian, P.; Noll, D. Nonsmooth H-∞ Synthesis. IEEE Trans. Autom. Control 2006, 51, 71–86. [Google Scholar] [CrossRef] [Green Version]

- Gómez, L. Una Aproximación al Control de los Procesos por Lotes. Ph.D. Thesis, Facultad de Ingeniería, Universidad Nacional de San Juan, San Juan, Argentina, 2009. [Google Scholar]

- Alzate, A. Metodología Para el Diseño Simultáneo de Equipo y su Sistema de Control Robusto. Master’s Thesis, Universidad Nacional de Colombia, Medellín, Colombia, 2013. [Google Scholar]

- Zouidi, A.; Fnaiech, F.; Al-Haddad, K. Voltage source Inverter Based three-phase shunt active Power Filter: Topology, Modeling and Control Strategies. In Proceedings of the 2006 IEEE International Symposium on Industrial Electronics, Montreal, QC, Canada, 9–13 July 2006; Volume 2, pp. 785–790. [Google Scholar] [CrossRef]

- IEEE Standards 519-2014. IEEE Recommended Practice and Requirements for Harmonic Control in Electric Power Systems; IEEE: Piscataway, NJ, USA, 2014. [Google Scholar]

- Louganski, K.; Lai, J.S. Current Phase Lead Compensation in Single-Phase PFC Boost Converters with a Reduced Switching Frequency to Line Frequency Ratio. IEEE Trans. Power Electron. 2007, 22, 113–119. [Google Scholar] [CrossRef]

- Vilanova, R.; Alfaro, V.M. Control {PID} robusto: Una visión panorámica. Rev. Iberoam. Automática Informática Ind. {RIAI} 2011, 8, 141–158. [Google Scholar] [CrossRef] [Green Version]

- Zeng, F.P.; Tan, G.H.; Wang, J.Z.; Ji, Y.C. Novel single-phase five-level voltage-source inverter for the shunt active power filter. IET Power Electron. 2010, 3, 480–489. [Google Scholar] [CrossRef]

- Danyali, S.; Hosseini, S.; Gharehpetian, G. New Extendable Single-Stage Multi-input DC-DC/AC Boost Converter. IEEE Trans. Power Electron. 2014, 29, 775–788. [Google Scholar] [CrossRef]

- Li, X.; Zhang, B.; Qiu, D.; Wang, D. New PWM strategy for nine-switch inverters with minimum number of semiconductor switching. In Proceedings of the 2014 International Electronics and Application Conference and Exposition (PEAC), Shanghai, China, 5–8 November 2014; pp. 406–410. [Google Scholar] [CrossRef]

- Li, X.; Zhang, B.; Qiu, D. Three-mode pulse-width modulation of a three-phase four-wire inverter. IET Power Electron. 2015, 8, 1483–1489. [Google Scholar] [CrossRef]

- Urrea-Quintero, J.H.; Hernández, H.; Ochoa, S. Towards a controllability analysis of multiscale systems: Application of the set-theoretic approach to a semi-batch emulsion polymerization process. Comput. Chem. Eng. 2020, 106833. [Google Scholar] [CrossRef]

- Sontag, E. Mathematical Control Theory; Texts in Applied Mathematics; Springer: New York, NY, USA, 1998. [Google Scholar]

- Tempo, R.; Calafiore, G.; Dabbene, F. Randomized Algorithms for Analysis and Control of Uncertain Systems: With Applications; Springer: London, UK, 2013. [Google Scholar]

| Requirement | Values | ||

|---|---|---|---|

| Min | Nominal | Max | |

| Input DC-link voltage range | 550 V | 600 V | 650 V |

| Rated grid voltage (line-to-neutral rms) | 119 V | 120 V | 121 V |

| Input power range | 0 W | – | 1.5 kW |

| output power range | 0 W | – | 1.5 kVA |

| VSI switching frequency | 20 kHz | ||

| Rated grid frequency | 49.9 Hz | 50 Hz | 50.1 Hz |

| THD (voltage) [45] | – | <5% | – |

| THD (current) [45] | – | <5% | – |

| Load | 100 VA | – | 1.5 kVA |

| Steady-State TLSC SAPF efficiency | 90% | 95% | 98% |

| Control Loop | PP | -PI | -uPI | |||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Soft | Hard | Soft | Hard | |||||||

| −1.7 | ||||||||||

| −1.79 | −4.73 | −8.5 | ||||||||

| −1.81 | −1.23 | −1.42 | ||||||||

| Performance Indices | |||||

|---|---|---|---|---|---|

| Control Loop | Controller Type | IAE | ITAE | IAU | |

| PP-PI | |||||

| -PI | |||||

| -uPI | |||||

| PP-PI | |||||

| -PI | |||||

| -uPI | |||||

| PP-PI | |||||

| -PI | |||||

| -uPI | |||||

| PP-PI | |||||

| -PI | |||||

| -uPI | |||||

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Urrea-Quintero, J.-H.; Muñoz-Galeano, N.; López-Lezama, J.M. Robust Control of Shunt Active Power Filters: A Dynamical Model-Based Approach with Verified Controllability. Energies 2020, 13, 6253. https://doi.org/10.3390/en13236253

Urrea-Quintero J-H, Muñoz-Galeano N, López-Lezama JM. Robust Control of Shunt Active Power Filters: A Dynamical Model-Based Approach with Verified Controllability. Energies. 2020; 13(23):6253. https://doi.org/10.3390/en13236253

Chicago/Turabian StyleUrrea-Quintero, Jorge-Humberto, Nicolás Muñoz-Galeano, and Jesús M. López-Lezama. 2020. "Robust Control of Shunt Active Power Filters: A Dynamical Model-Based Approach with Verified Controllability" Energies 13, no. 23: 6253. https://doi.org/10.3390/en13236253