A Parameter Optimization Design Method for Single-Phase Dual Active Bridge AC-DC Converter

Abstract

:1. Introduction

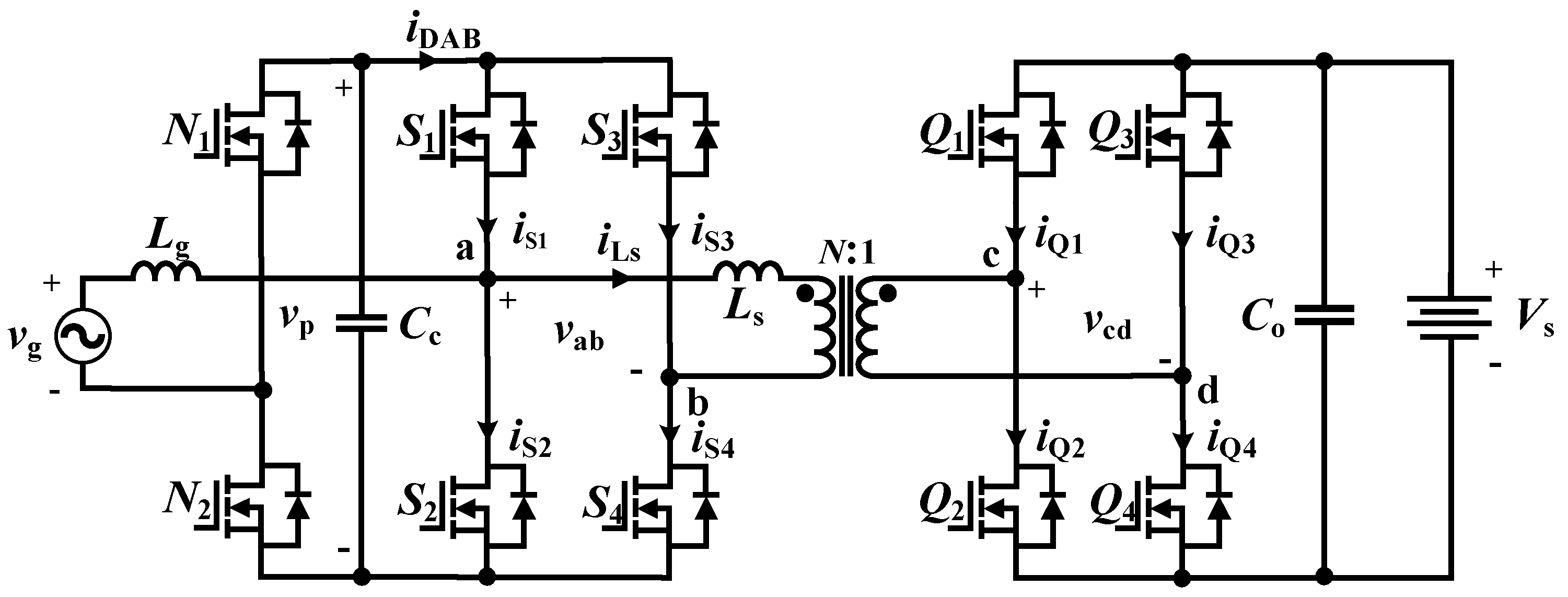

2. Parameter Optimization Design Framework for DAB AC-DC Converter

2.1. Multi-Timescale Steady-State Analysis of the DAB AC-DC Converter

2.2. Parameter Optimization Design Framework

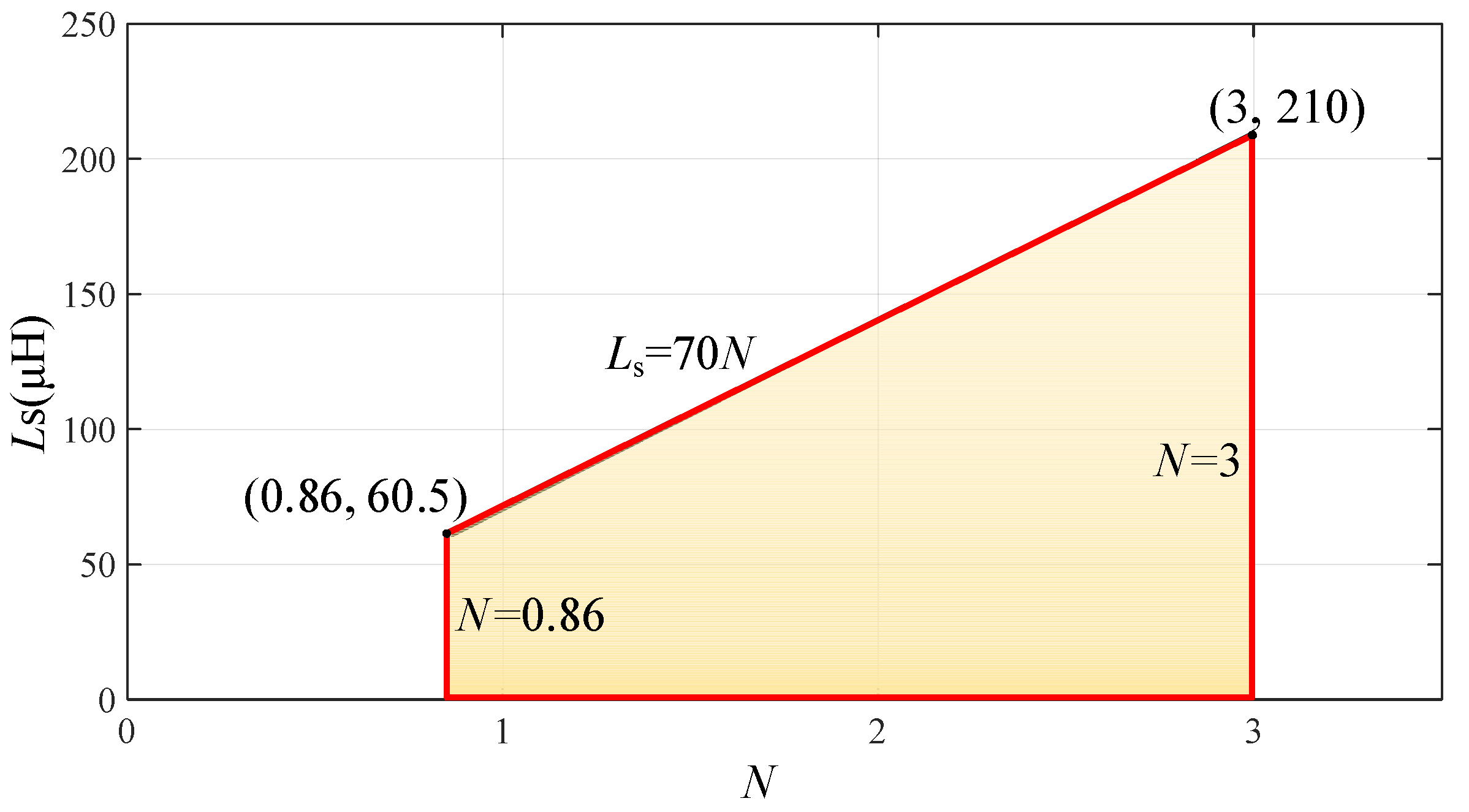

3. Safe Design Space for Parameters

3.1. Transmission Power Constraints

3.2. Current Stress Constraints

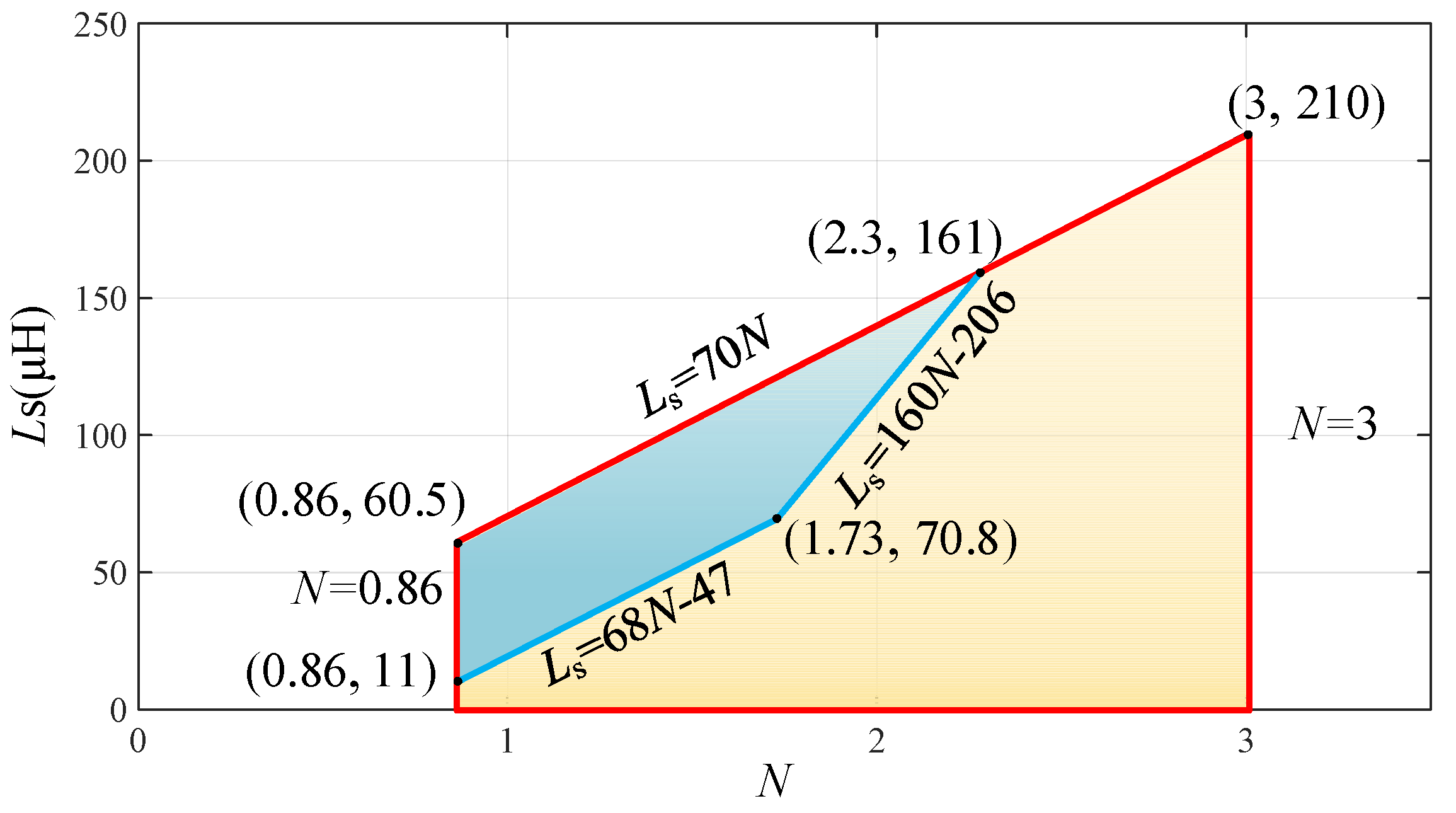

4. Optimization Design Space for Parameters

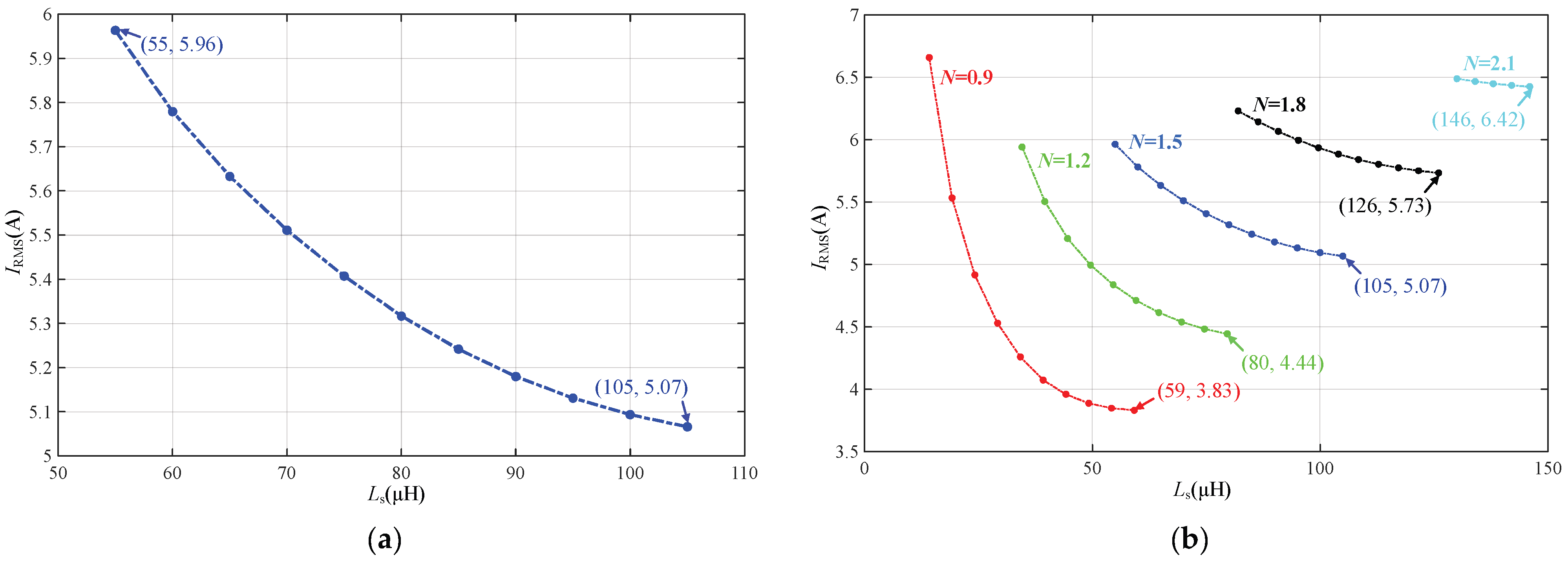

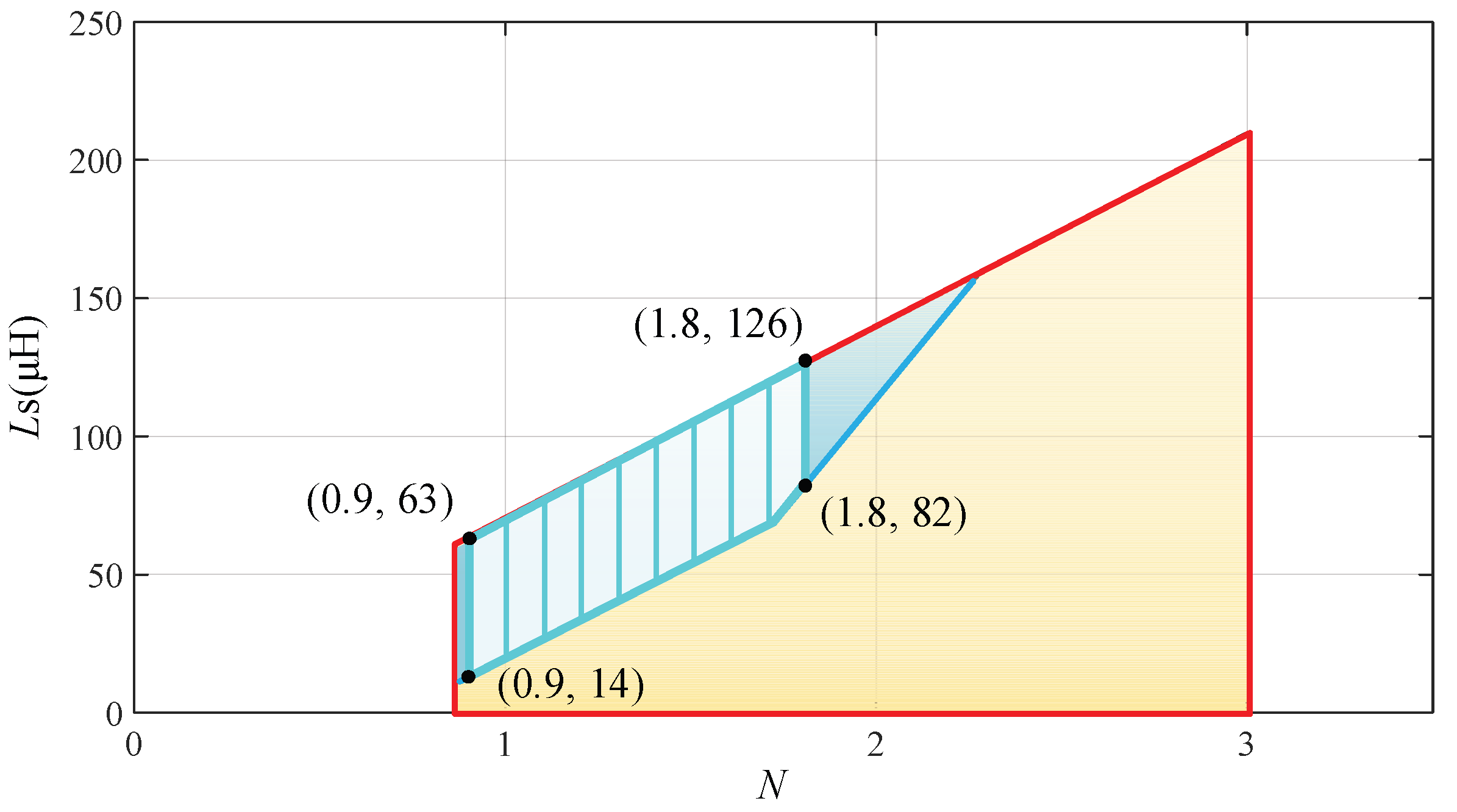

4.1. Parameter Optimization Design Based on Conduction Loss

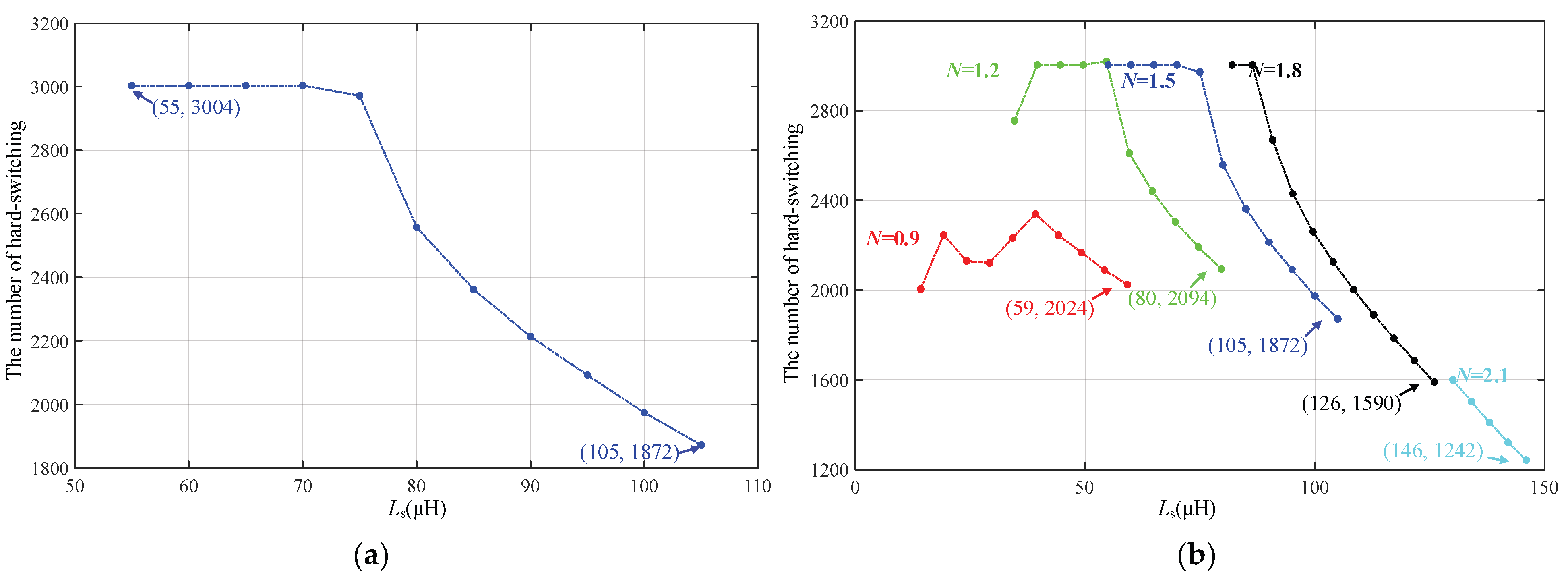

4.2. Parameter Optimization Design Based on Switching Loss

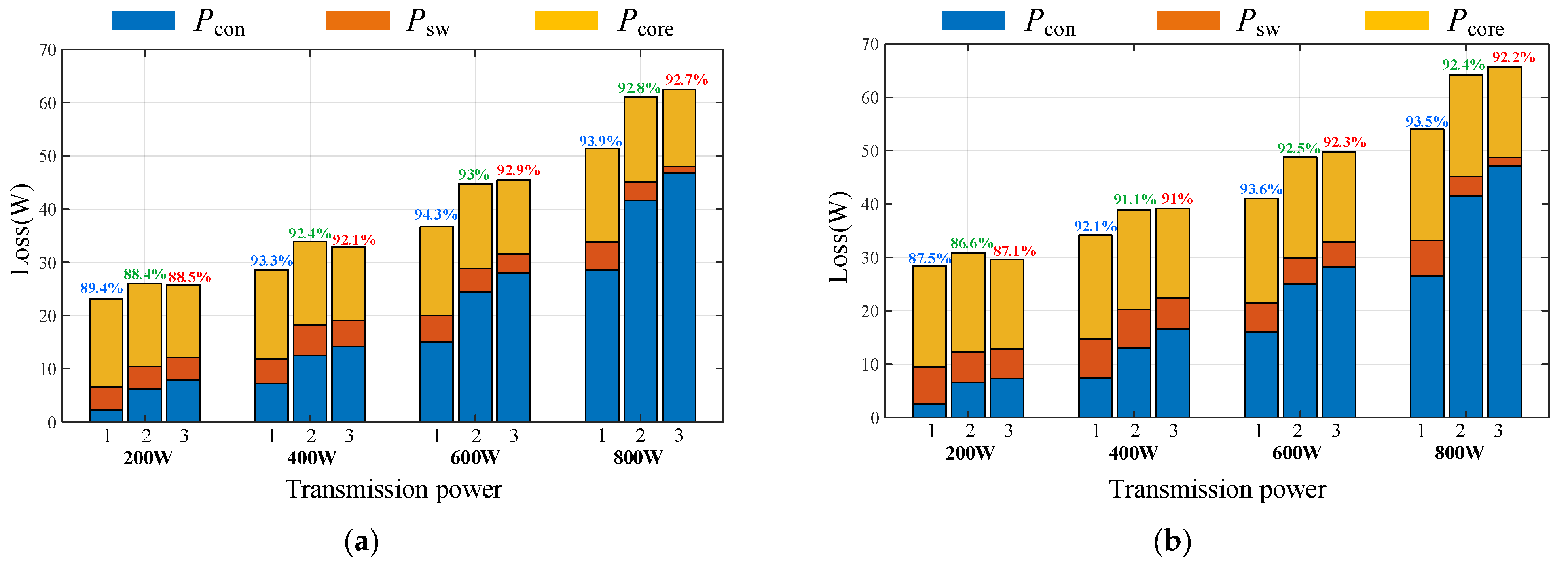

5. Loss Analysis to Determine Parameter Optimization Results

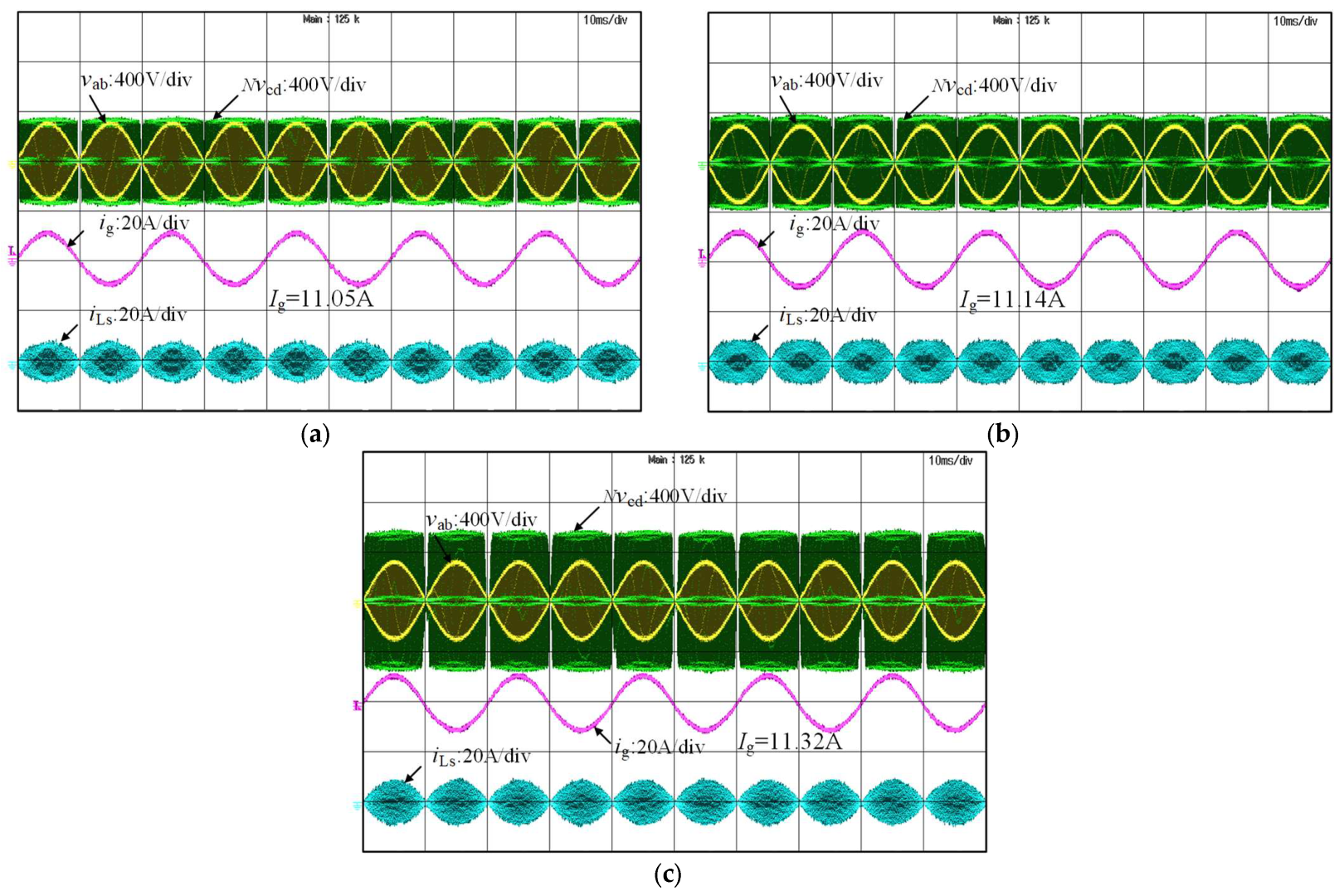

6. Experimental Verification

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Appendix A

- (1)

- Conduction losses

- (2)

- Switching losses

- (3)

- Core losses

References

- Everts, J.; Krismer, F.; Van den Keybus, J.; Driesen, J.; Kolar, J.W. Optimal ZVS modulation of single-phase single-stage bidirectional DAB ac–dc converters. IEEE Trans. Power Electron. 2014, 29, 3954–3970. [Google Scholar] [CrossRef]

- Zengin, S.; Boztepe, M. A novel current modulation method to eliminate low-frequency harmonics in single-stage dual active bridge AC–DC converter. IEEE Trans. Ind. Electron. 2020, 67, 1048–1058. [Google Scholar] [CrossRef]

- Jauch, F.; Biela, J. Combined phase-shift and frequency modulation of a dual-active-bridge AC–DC converter with PFC. IEEE Trans. Power Electron. 2016, 31, 8387–8397. [Google Scholar] [CrossRef]

- Sun, X.; Wang, H.; Qi, L.; Liu, F. Research on single-stage highfrequency-link SST topology and its optimization control. IEEE Trans. Power Electron. 2020, 35, 8701–8711. [Google Scholar] [CrossRef]

- Everts, J. Design and Optimization of an Efficient (96.1%) and Compact (2 kW/dm3) Bidirectional Isolated Single-Phase Dual Active Bridge AC-DC Converter. Energies 2016, 9, 799. [Google Scholar] [CrossRef]

- Yilmaz, M.; Krein, P.T. Review of Battery Charger Topologies, Charging Power Levels, and Infrastructure for Plug in Electric and Hybrid Vehicles. IEEE Trans. Power Electron. 2013, 28, 2151–2169. [Google Scholar] [CrossRef]

- Belkamel, H.; Kim, H.; Choi, S. Interleaved Totem-Pole ZVS Converter Operating in CCM for Single-Stage Bidirectional AC–DC Conversion with High-Frequency Isolation. IEEE Trans. Power Electron. 2021, 36, 3486–3495. [Google Scholar] [CrossRef]

- Weise, N.D.; Castelino, G.; Basu, K.; Mohan, N. A single-stage dualactive-bridge-based soft switched ac–dc converter with open-loop power factor correction and other advanced features. IEEE Trans. Power Electron. 2014, 29, 4007–4016. [Google Scholar] [CrossRef]

- Sha, D.; Zhang, D.; Zhang, J. A Single-Stage Dual-Active-Bridge AC–DC Converter Employing Mode Transition Based on Real-Time Calculation. IEEE Trans. Power Electron. 2021, 36, 10081–10088. [Google Scholar] [CrossRef]

- Li, X.; Wu, F.; Yang, G.; Liu, H. Improved Modulation Strategy for Single-Phase Isolated Quasi-Single-Stage AC–DC Converter to Improve Current Characteristics. IEEE Trans. Power Electron. 2020, 35, 4296–4308. [Google Scholar] [CrossRef]

- Li, J.; Yuan, L.; Gu, Q.; Sun, J.; Duan, R. A loss model-based efficiency optimization method for dual active-bridge DC-DC converters. J. Electrotechnol. 2017, 32, 66–76. [Google Scholar]

- Krismer, F. Modeling and optimization of bidirectional dual active bridge DC-DC converter topologies. Ph.D. Thesis, Zurich Federal Institute of Technology, Zurich, Switzerland, 2010. [Google Scholar]

- Biao, Z.; Qiang, S. Theory and Application Techniques of Dual Active Full-Bridge DC-DC Converters; Science Press: Beijing, China, 2017; pp. 7–10. [Google Scholar]

- Das, D.; Basu, K. Optimal design of a dual-active-bridge DC-DC converter. IEEE Trans Ind Electron 2021, 68, 12034–12045. [Google Scholar] [CrossRef]

- Wang, S.; Zheng, Z.; Li, Y. Optimal Design Methodology of Bidirectional Dual Active Bridge Series Resonant DC/DC Converter. In Proceedings of the 2019 IEEE 13th International Conference on Power Electronics and Drive Systems (PEDS), Toulouse, France, 9–12 July 2019; pp. 1–5. [Google Scholar]

- Zhang, Y.; Yang, G.; Li, J.; Kong, Z.; Zhu, X. A Modulation Scheme with Full Range ZVS and Natural Power Factor Correction for Bridgeless Single-Stage Isolated AC–DC Converter. IEEE Trans. Power Electron. 2023, 38, 195–205. [Google Scholar] [CrossRef]

- Biao, Z.; Song, Q.; Liu, W.; Liu, G.; Zhao, Y. Universal High-Frequency-Link Characterization and Practical Fundamental-Optimal Strategy for Dual-Active-Bridge DC-DC Converter Under PWM Plus Phase-Shift Control. IEEE Trans. Power Electron. 2015, 30, 6488–6494. [Google Scholar]

- Christopher, H.; Karoline, V.; Sebastian, Z.; Uwe, S.D. Electric vehicle route planning using real-world charging infrastructure in Germany. eTransportation 2021, 10, 100143. [Google Scholar]

- Mou, D.; Luo, Q.; Wei, Y.; Li, J.; Hou, N.; Long, T.; Li, Y. A periodic-steady-state analysis model in time-domain for dual active bridge converter. IEEE Trans Power Electron 2022, 37, 4121–4132. [Google Scholar] [CrossRef]

- Mallik, A.; Khaligh, A. Maximum Efficiency Tracking of an Integrated Two-Staged AC–DC Converter Using Variable DC-Link Voltage. IEEE Trans. Ind. Electron. 2018, 65, 8408–8421. [Google Scholar] [CrossRef]

- Steinmetz, C.P. On the law of hysteresis. AIEE Trans. 1892, 9, 3–64, Reprinted in Proc. IEEE 1984, 72, 196–221. [Google Scholar] [CrossRef]

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| Input Voltage vg | 110 Vrms | Output voltage Vs | 360~400 V |

| Line frequency fg | 50 Hz | Switching frequency fs | 100 kHz |

| Rated power PN | 800 W | MOSFET | SCT3060AL |

| Group I | Group II | Group III |

|---|---|---|

| N = 0.9:1 Ls = 65 μH | N = 1:1 Ls = 55 μH | N = 1.5:1 Ls = 107 μH |

|  |  |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yu, C.; Luo, Q. A Parameter Optimization Design Method for Single-Phase Dual Active Bridge AC-DC Converter. Energies 2024, 17, 1955. https://doi.org/10.3390/en17081955

Yu C, Luo Q. A Parameter Optimization Design Method for Single-Phase Dual Active Bridge AC-DC Converter. Energies. 2024; 17(8):1955. https://doi.org/10.3390/en17081955

Chicago/Turabian StyleYu, Chengyang, and Quanming Luo. 2024. "A Parameter Optimization Design Method for Single-Phase Dual Active Bridge AC-DC Converter" Energies 17, no. 8: 1955. https://doi.org/10.3390/en17081955