Investigation of 1200 V SiC MOSFETs’ Surge Reliability

Abstract

:1. Introduction

2. Materials and Methods

2.1. The Reverse Conduction Characteristics of SiC Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET)

2.2. Setup of the Surge Current Tests

3. Results

4. Discussion

4.1. Analysis of Test Result

4.1.1. Comparison of Devices’ Characteristics before and after the Surge Reliability Tests

4.1.2. Static Characteristic Variation of the Tested Device

4.2. Analysis of Failure Mechanism

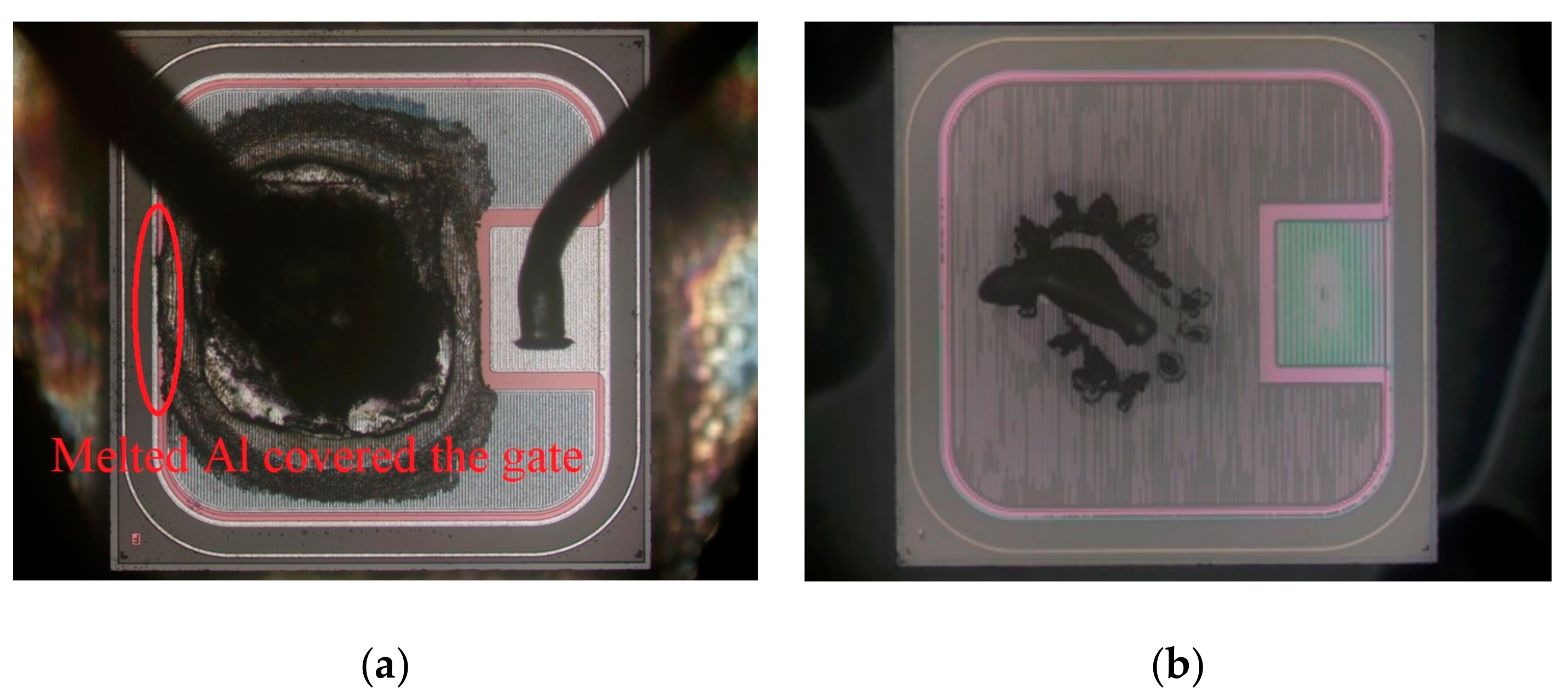

4.2.1. Aluminum Melted and Diffused into the Interlayer Dielectric

4.2.2. Ohmic Contact Layer Disappeared

4.2.3. Al Penetrated into SiC

4.3. Analysis of Simulation Result

4.3.1. Simulation Setting

4.3.2. Surge Simulation Results and Analysis

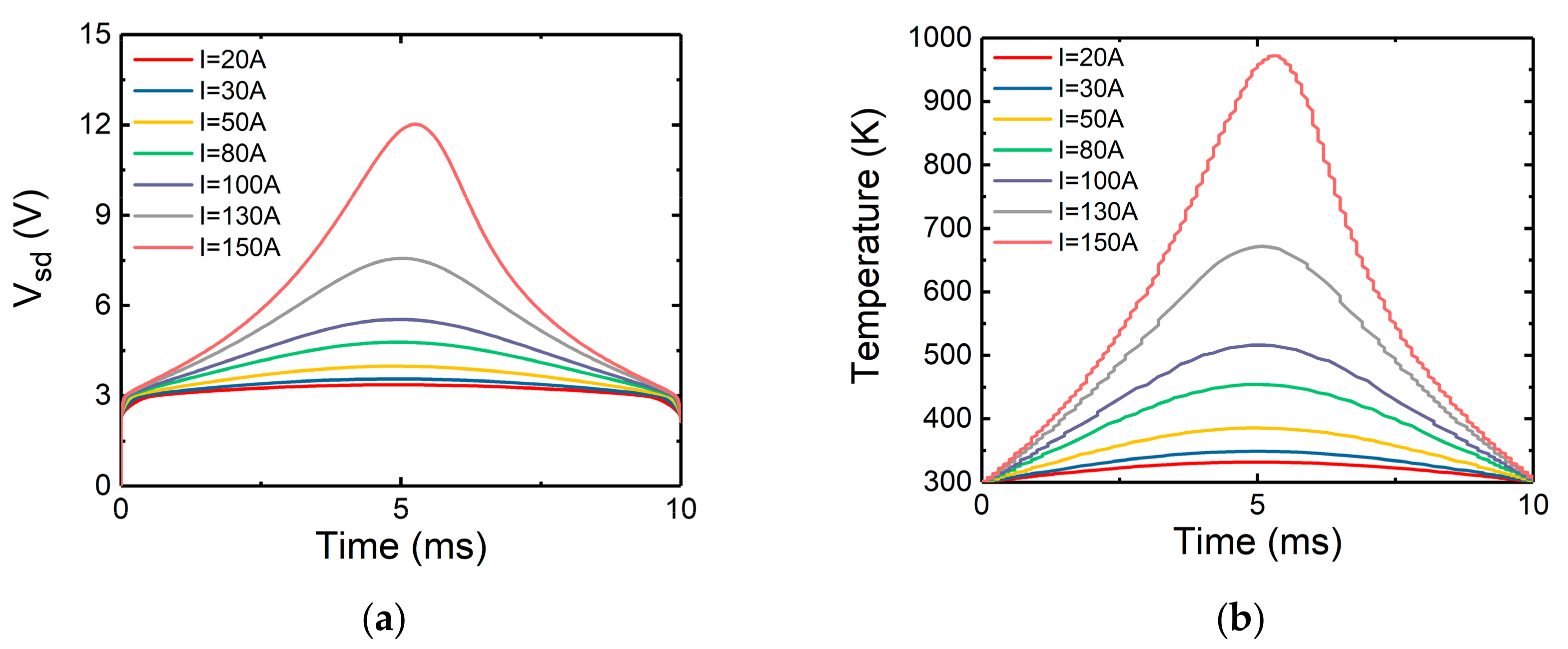

The Channel Non-Conducting Mode

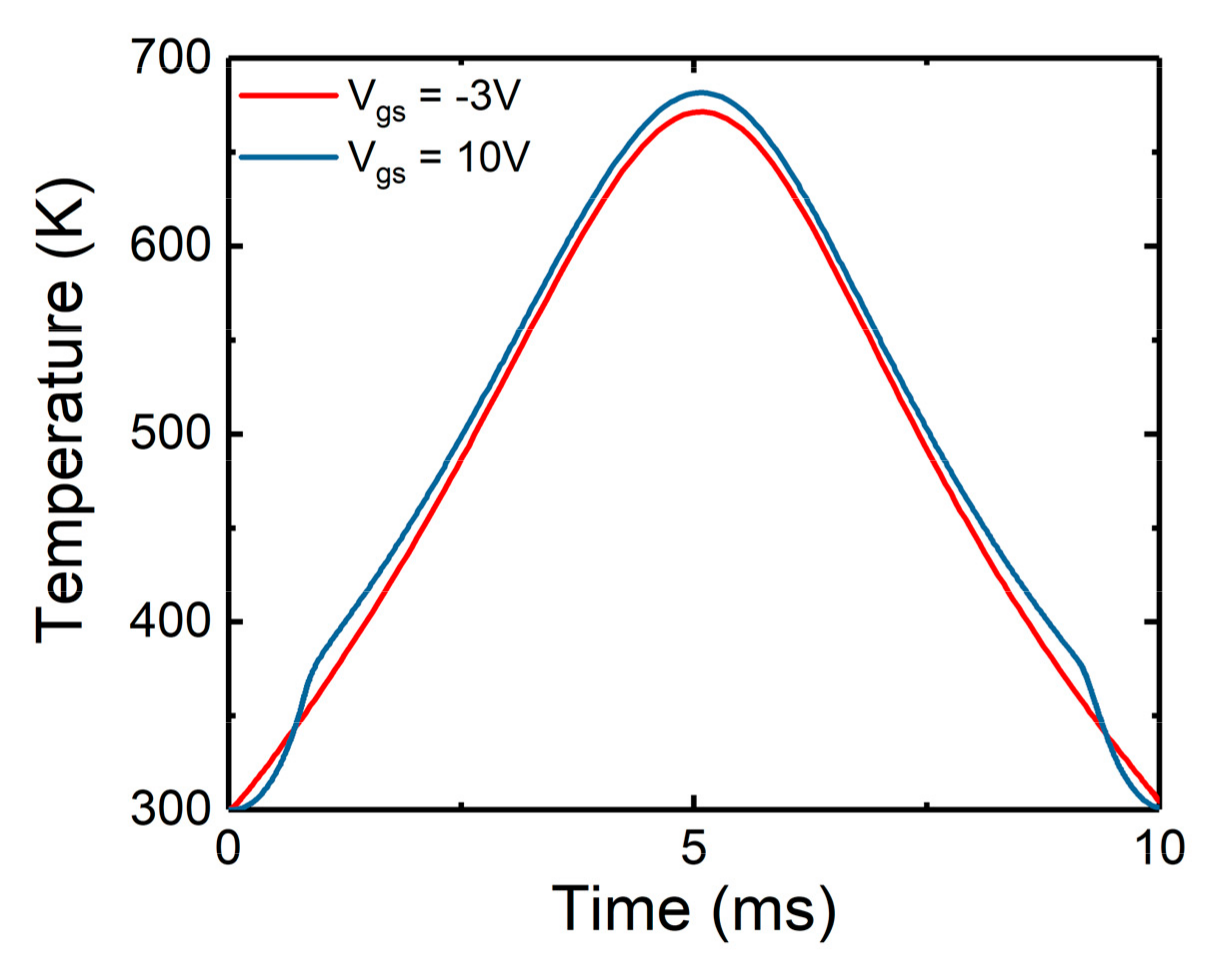

The Channel Conduction Mode

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Chow, T.P.; Tyagi, R. Wide bandgap compound semiconductors for superior high-voltage power devices. In Proceedings of the 5th International Symposium on Power Semiconductor Devices and ICs, Monterey, CA, USA, 18–20 May 1993; pp. 84–88. [Google Scholar] [CrossRef]

- Chow, T.P.; Tyagi, R. Wide bandgap compound semiconductors for superior high-voltage unipolar power devices. IEEE Trans. Electron. Devices 1994, 8, 1481–1483. [Google Scholar] [CrossRef]

- Chow, T.P.; Si, C.; Ga, N. High-voltage power switching devices. Mater. Sci. Forum 2000, 338, 1155–1160. [Google Scholar] [CrossRef]

- Casady, J.B.; Johnson, R.W. Status of silicon carbide (SiC) as a wide-bandgap semiconductor for high-temperature applications: A review. Solid-State Electron. 1996, 39, 1409–1422. [Google Scholar] [CrossRef]

- Saremi, M. modeling and Simulation of the Programmable Metallization Cells (pmcs) and Diamond-Based Power Devices. Ph.D. Thesis, Arizona State University, Tempe Campus, AZ, USA, 2017. [Google Scholar]

- Aminbeidokhti, A.; Dimitrijev, S.; Hanumanthappa, A.K.; Moghadam, H.A.; Haasmann, D.; Han, J.; Xu, X. Gate-voltage independence of electron mobility in power AlGaN/GaN HEMTs. IEEE Trans. Electron Devices 2016, 63, 1013–1019. [Google Scholar] [CrossRef]

- Aminbeidokhti, A.; Dimitrijev, S.; Hanumanthappa, A.K.; Moghadam, H.A.; Haasmann, D.; Han, J.; Xu, X. The power law of phonon-limited electron mobility in the 2-D electron gas of AlGaN/GaN heterostructure. IEEE Trans. Electron. Devices 2016, 63, 2214–2218. [Google Scholar] [CrossRef]

- Kimoto, T.; Kosugi, H.; Suda, J.; Kanzaki, Y.; Matsunami, H. Design and fabrication of resurf MOSFETs on 4H-SiC and 6H-SiC. IEEE Trans. Electron. Devices 2005, 52, 112–117. [Google Scholar] [CrossRef]

- Wondrak, W.; Held, R.; Niemann, E.; Schmid, U. SiC devices for advanced power and high-temperature applications. IEEE Trans. Ind. Electron. 2001, 48, 307–308. [Google Scholar] [CrossRef]

- Palanisamy, S.; Fichtner, S.; Lutz, J.; Basler, T.; Rupp, R. Various structures of 1200V SiC MPS diode models and their simulated surge current behavior in comparison to measurement. In Proceedings of the 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Prague, Czech Republic, 12–16 June 2016; pp. 235–238. [Google Scholar] [CrossRef]

- Kowalsky, J.; Simon, T.; Geske, M.; Basler, T.; Lutz, J. Surge Current Behaviour of Different IGBT Designs. In Proceedings of the PCIM Europe 2015, International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 19–21 May 2015; pp. 1–10. [Google Scholar]

- Basler, T.; Lutz, J.; Jakob, R.; Brückner, T. Surge current capability of IGBTs. In Proceedings of the International Multi-Conference on Systems, Sygnals & Devices, Chemnitz, Germany, 20–23 March 2012; pp. 1–6. [Google Scholar] [CrossRef]

- Basler, T.; Lutz, J.; Jakob, R. IGBTs conducting diode-like surge currents. In Proceedings of the 2014 IEEE 26th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Waikoloa, HI, USA, 15–19 June 2014; pp. 103–106. [Google Scholar] [CrossRef]

- Radhakrishnan, R.; Cueva, N.; Witt, T.; Woodin, R.L. Analysis of forward surge performance of sic schottky diodes. Mater. Sci. Forum 2018, 924, 621–624. [Google Scholar] [CrossRef]

- Hilsenbeck, J.; Treu, M.; Rupp, R.; Rüschenschmidt, K.; Kern, R.; Holz, M. Investigations on surge current capability of SiC schottky diodes by implementation of new pad metallizations. Mater. Sci. Forum 2010, 645, 673–676. [Google Scholar] [CrossRef]

- Banu, V.; Godignon, P.; Jordá, X.; Alexandru, M.; Millan, J. SiC schottky diode surge current analysis and application design using behavioral SPICE models. In Proceedings of the CAS 2012 (International Semiconductor Conference), Sinaia, Romania, 15–17 October 2012; pp. 359–362. [Google Scholar] [CrossRef]

- León, J.; Perpiñà, X.; Banu, V.; Montserrat, J.; Berthou, M.; Vellvehí, M.; Jordà, X. Temperature effects on the ruggedness of SiC schottky diodes under surge current. Microelectron. Reliab. 2014, 54, 2207–2212. [Google Scholar] [CrossRef]

- Hofstetter, P.; Bakran, M.M. Predicting Failure of SiC MOSFETs under short circuit and surge current conditions with a single thermal model. In Proceedings of the IEEE 20th European Conference on Power Electronics and Applications (EPE’18 ECCE Europe), Riga, Latvia, 17–21 September 2018; pp. 1–9. [Google Scholar]

- Sadik, D.P.; Heinig, S.; Jacobs, K.; Johannesson, D.; Lim, J.K.; Nawaz, M.; Dijkhuizen, F.; Bakowski, M.; Norrga, S.; Nee, H.P. Investigation of the surge current capability of the body diode of SiC MOSFETs for HVDC applications. In Proceedings of the European Conference on Power Electronics & Applications, Karlsruhe, Germany, 5–9 September 2016; pp. 1–10. [Google Scholar] [CrossRef]

- Rodrigues, R.; Zhang, Y.; Jiang, T.; Aeloiza, E.; Cairoli, P. Surge current capability of SiC MOSFETs in AC distribution systems. In Proceedings of the IEEE 6th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Atlanta, GA, USA, 31 October–2 November 2018; pp. 331–337. [Google Scholar]

- Carastro, F.; Mari, J.; Zoels, T.; Rowden, B.; Losee, P.; Stevanovic, L. Investigation on diode surge forward current ruggedness of Si and SiC power modules. In Proceedings of the European Conference on Power Electronics & Applications, Karlsruhe, Germany, 5–9 September 2016; pp. 1–10. [Google Scholar] [CrossRef]

- Shan, Y.; Yunfei, G.; Shuairong, D.; Xiong, X.; Gang, D. Comparative Investigation of Surge Current Capabilities of Si IGBT and SiC MOSFET for Pulsed Power Application. IEEE Trans. Plasma Sci. 2018, 1–6. [Google Scholar] [CrossRef]

- Hofstetter, P.; Bakran, M.M. Comparison of the surge current ruggedness between the body diode of sic mosfets and si diodes for igbt. In Proceedings of the 10th International Conference on Integrated Power Electronics Systems (CIPS 2018), Stuttgart, Germany, 20–22 March 2018; pp. 1–7. [Google Scholar]

- Jiang, X.; Zhai, D.; Chen, J.; Yuan, F.; Li, Z.; He, Z.; Wang, J. Comparison study of surge current capability of body diode of SiC MOSFET and SiC schottky diode. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018; pp. 845–849. [Google Scholar]

- Yamamoto, S.; Nakao, Y.; Tomita, N.; Nakata, S.; Yamakawa, S. Development of 3.3 kV SiC-MOSFET:Suppression of forward voltage degradation of the body diode. Mater. Sci. Forum 2014, 4, 778–780. [Google Scholar] [CrossRef]

- Imaizumi, M.; Miura, N. Characteristics of 600, 1200, and 3300 V planar SiC-MOSFETs for energy conversion applications. IEEE Trans. Electron. Devices 2014, 62, 390–395. [Google Scholar] [CrossRef]

- Hull, B.; Allen, S.; Zhang, S.; Gajewski, D.; Pala, V.; Richmond, J.; Ryu, S.; O’Loughlin, M.; Van, B.E.; Cheng, L.; et al. Reliability and stability of SiC power mosfets and nextgeneration SiC MOSFETs. In Proceedings of the IEEE Workshop on Wide Bandgap Power Devices and Applications, Knoxville, TN, USA, 13–15 October 2014; pp. 139–142. [Google Scholar] [CrossRef]

- Sadik, D.; Lim, J.; Ranstad, P.; Nee, H. Investigation of long-term parameter variations of SiC power MOSFETs. In Proceedings of the 17th European Conference on Power Electronics and Applications, Geneva, Switzerland, 8–10 September 2015; pp. 1–10. [Google Scholar] [CrossRef]

- Callanan, R.; Rice, J.; Palmour, J. Third quadrant behavior of SiC MOSFETs. In Proceedings of the 28th Annual IEEE Applied Power Electronics Conference and Exposition, Long Beach, CA, USA, 17–21 March 2013; pp. 1250–1253. [Google Scholar] [CrossRef]

- Hunger, T.; Schilling, O.; Wolter, F. Numerical and experimental study on surge current limitations of wire-bonded power diodes. In Proceedings of the PCIM Europe 2007, Nuremburg, Germany, 22–24 May 2007. [Google Scholar]

- Schroder, D.K. Semiconductor Material and Device Characterization; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2006; pp. 370–372. [Google Scholar] [CrossRef]

- Heinze, B.; Lutz, J.; Rupp, R.; Holz, M. Surge current ruggedness of silicon carbide Schottky and merged-PiN-Schottky Diodes. In Proceedings of the 20th International Symposium on Power Semiconductor Devices, Orlando, FL, USA, 18–22 May 2008; pp. 245–248. [Google Scholar] [CrossRef]

- Silber, D.; Robertson, M.J. Thermal effects on the forward characteristic of silicon PiN diodes at high pulse currents. Solid State Electron. 1973, 16, 1337–1346. [Google Scholar] [CrossRef]

- Fichtner, S.; Lutz, J.; Basler, T.; Rupp, R.; Gerlach, R. Electro-thermal simulations and experimental results on the surge current capability of 1200 V SiC MPS diodes. In Proceedings of the International Conference on Integrated Power Electronics Systems, Nuremberg, Germany, 25–27 February 2014; pp. 1–5, ISBN 978-3-8007-3578-5. [Google Scholar]

- Berger, W.M.; Keen, R.S.; Schnable, G.L. Reliability phenomena in aluminum metalizations on silicon dioxide. In Proceedings of the 4th Symposium on the Physics of Failure in Electronics, Chicago, IL, USA, 16–18 November 1965; pp. 1–31. [Google Scholar] [CrossRef]

- Black, J.R. Electromigration of Al-Si alloy films. In Proceedings of the 15th International Reliability Physics Symposium, San Diego, CA, USA, 18–20 April 1978; pp. 257–261. [Google Scholar] [CrossRef]

- Tanimoto, S.; Ohashi, H. Reliability issues of SiC power MOSFETs toward high junction temperature operation. Phys. Status Solidi A 2009, 206, 2417–2430. [Google Scholar] [CrossRef]

- Roccaforte, F.; Via, F.L.; Raineri, V. Ohmic Contacts to SIC. Int. J. High Speed Electron. Syst. 2005, 15, 781–820. [Google Scholar] [CrossRef]

- Kakanakov, R.; Kassamakova-Kolaklieva, L.; Hristeva, N.; Lepoeva, G.; Zekentes, K. Thermally stable low resistivity ohmic contacts for high power and high temperature SiC device applications. In Proceedings of the 23rd International Conference on Microelectronics. Proceedings (Cat. No. 02TH8595), Nis, Yugoslavia, 12–15 May 2002. [Google Scholar] [CrossRef]

- HKelek, E.; Robinson, G.Y. Aluminum/nickel silicide contacts on silicon. Thin Solid Films 1978, 53, 135–140. [Google Scholar] [CrossRef]

- Bartur, M.; Nicolet, M.A. Thermal oxidation of nickel disilicide. Appl. Phys. Lett. 1982, 40, 175–177. [Google Scholar] [CrossRef] [Green Version]

| Region | Numerical Value | Unit |

|---|---|---|

| Doping concentration in P−well region | Surface , internal peak 1 | cm−3 |

| Depth of P−well region | 0.5 | |

| Doping concentration in N− drift region | cm−3 | |

| Depth of N- drift region | 10 | |

| Doping concentration in N++ substrate region | cm−3 | |

| Depth of N++ substrate region | 170 | |

| Doping concentration in N+ region | cm−3 | |

| Depth of N+ region | 0.2 | |

| Doping concentration in P+ region | cm−3 | |

| Length of channel | 0.96 | |

| Thickness of gate oxide layer | 0.05 | |

| Length of junction field-effect transistor (JFET) region | 2.4 |

| Vds (V) | Rds(on) (mΩ) | Ids (A)/ Body Diode IF (A) | Vgs (V) | Vth (V) | |

|---|---|---|---|---|---|

| SCT10N120 | 1200 | 500 | 12/12 | −10/25 | 5.5 |

| C2M0080120D | 1200 | 80 | 36/36 | −5/20 | 2.8 |

| C2M0160120D | 1200 | 160 | 19/19 | −5/20 | 3 |

| LSIC1MO120E0160 | 1200 | 160 | 22/22 | −5/20 | 3.6 |

| SCT3160KLGC11 | 1200 | 160 | 17/17 | −4/22 | 5 |

| Ids (A)/ Body Diode IF (A) | Rds(on) (mΩ) | Maximum Surge Current (A) | Maximum Surge Current/Rated Current | |

|---|---|---|---|---|

| SCT10N120 | 12/12 | 500 | 61 | 5 |

| C2M0080120D | 36/36 | 80 | 155 | 4.3 |

| C2M0160120D | 19/19 | 160 | 105 | 5.5 |

| LSIC1MO120E0160 | 22/22 | 160 | 95 | 4.3 |

| SCT3160KLGC11 | 17/17 | 160 | 42 | 2.5 |

| Device | Rgs (Ω) | Rds (Ω) |

|---|---|---|

| Before the tests | >100 M | >100 M |

| SCT10N120, after tests | 0.4 | 14 k |

| C2M0160120D, after tests | 0.08 | >100 M |

| Model | Model Used in Simulation | Notes |

|---|---|---|

| Carrier Statistics Models | Fermi-Dirac | Reduced carrier concentrations in heavily doped regions (statistical approach). |

| Bandgap Narrowing(BGN) | Important in heavily doped regions. Critical for bipolar gain. Use Klaassen Model. | |

| Mobility Models | Lombardi (CVT) Model | Complete model including N, T, E//, and E┴ effects. * |

| Recombination Models | Shockley-Read-Hall(SRH) | Uses fixed minority carrier lifetimes. |

| Auger | Direct transition of three carriers. Important at high current densities. | |

| Impact Ionization Model | Selberherr’s Model (Impact selb) | Recommended for most cases. Includes temperature dependent parameters. |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, H.; Wang, J.; Ren, N.; Xu, H.; Sheng, K. Investigation of 1200 V SiC MOSFETs’ Surge Reliability. Micromachines 2019, 10, 485. https://doi.org/10.3390/mi10070485

Li H, Wang J, Ren N, Xu H, Sheng K. Investigation of 1200 V SiC MOSFETs’ Surge Reliability. Micromachines. 2019; 10(7):485. https://doi.org/10.3390/mi10070485

Chicago/Turabian StyleLi, Huan, Jue Wang, Na Ren, Hongyi Xu, and Kuang Sheng. 2019. "Investigation of 1200 V SiC MOSFETs’ Surge Reliability" Micromachines 10, no. 7: 485. https://doi.org/10.3390/mi10070485