Analysis of the Sensing Margin of Silicon and Poly-Si 1T-DRAM

Abstract

:1. Introduction

2. Simulation Method

3. Results and Discussion

3.1. Transient Characteristics of Silicon and poly-Si 1T-DRAM

3.2. The Effect of Grain Size on Sensing Margin Characteristics

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Ranica, R.; Villaret, A.; Malinge, P.; Mazoyer, P.; Lenoble, D.; Candelier, P.; Jacquet, F.; Masson, P.; Bouchakour, R.; Fournel, R.; et al. A One Transistor Cell on Bulk Substrate (1T-Bulk) for Low-Cost and High Density EDRAM. In Proceedings of the Digest of Technical Papers, 2004 Symposium on VLSI Technology, Honolulu, HI, USA, 15–17 June 2004; pp. 128–129. [Google Scholar] [CrossRef]

- Rodriguez, N.; Gamiz, F.; Cristoloveanu, S. A-RAM Memory Cell: Concept and Operation. IEEE Electron Device Lett. 2010, 31, 972–974. [Google Scholar] [CrossRef]

- Rodriguez, N.; Cristoloveanu, S.; Gamiz, F. Novel Capacitorless 1T-DRAM Cell for 22-Nm Node Compatible With Bulk and SOI Substrates. IEEE Trans. Electron Devices 2011, 58, 2371–2377. [Google Scholar] [CrossRef]

- Jeong, H.; Song, K.-W.; Park, I.H.; Kim, T.-H.; Lee, Y.S.; Kim, S.-G.; Seo, J.; Cho, K.; Lee, K.; Shin, H.; et al. A New Capacitorless 1T DRAM Cell: Surrounding Gate MOSFET With Vertical Channel (SGVC Cell). IEEE Trans.Nanotechnol. 2007, 6, 352–357. [Google Scholar] [CrossRef]

- Lee, M.; Moon, T.; Kim, S. Floating Body Effect in Partially Depleted Silicon Nanowire Transistors and Potential Capacitor-Less One-Transistor DRAM Applications. IEEE Trans. Nanotechnol. 2012, 11, 355–359. [Google Scholar] [CrossRef]

- Bawedin, M.; Cristoloveanu, S.; Flandre, D. A Capacitorless 1T-DRAM on SOI Based on Dynamic Coupling and Double-Gate Operation. IEEE Electron Device Lett. 2008, 29, 795–798. [Google Scholar] [CrossRef]

- Giusi, G.; Iannaccone, G. Junction Engineering of 1T-DRAMs. IEEE Electron Device Lett. 2013, 34, 408–410. [Google Scholar] [CrossRef]

- Song, K.; Jeong, H.; Lee, J.; Hong, S.; Tak, N.; Kim, Y.; Cho, Y.; Joo, H.; Kim, S.; Song, H.; et al. 55 Nm Capacitor-Less 1T DRAM Cell Transistor with Non-Overlap Structure. In Proceedings of the 2008 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008; pp. 797–800. [Google Scholar] [CrossRef]

- Lee, C.-W.; Yan, R.; Ferain, I.; Kranti, A.; Akhvan, N.D.; Razavi, P.; Yu, R.; Colinge, J.P. Nanowire Zero-Capacitor DRAM Transistors with and without Junctions. In Proceedings of the 10th IEEE International Conference on Nanotechnology, Seoul, Korea, 17–20 August 2010; pp. 242–245. [Google Scholar] [CrossRef]

- Wan, J.; Le Royer, C.; Zaslavsky, A.; Cristoloveanu, S. A Compact Capacitor-Less High-Speed DRAM Using Field Effect-Controlled Charge Regeneration. IEEE Electron Device Lett. 2012, 33, 179–181. [Google Scholar] [CrossRef]

- Ansari, M.H.R.; Navlakha, N.; Lin, J.-T.; Kranti, A. Doping Dependent Assessment of Accumulation Mode and Junctionless FET for 1T DRAM. IEEE Trans. Electron Devices 2018, 65, 1205–1210. [Google Scholar] [CrossRef]

- Ansari, M.H.R.; Navlakha, N.; Lin, J.-T.; Kranti, A. 1T-DRAM with Shell-Doped Architecture. IEEE Trans. Electron Devices 2019, 66, 428–435. [Google Scholar] [CrossRef]

- Lee, W.; Choi, W.Y. A Novel Capacitorless 1T DRAM Cell for Data Retention Time Improvement. IEEE Trans. Nanotechnol. 2011, 10, 462–466. [Google Scholar] [CrossRef]

- Biswas, A.; Dagtekin, N.; Grabinski, W.; Bazigos, A.; Le Royer, C.; Hartmann, J.-M.; Tabone, C.; Vinet, M.; Ionescu, A. Investigation of Tunnel Field-Effect Transistors as a Capacitor-Less Memory Cell. Appl. Phys. Lett. 2014, 104, 092108. [Google Scholar] [CrossRef]

- Lin, J.-T.; Huang, K.-D.; Jheng, B.-T. Performances of a Capacitorless 1T-DRAM Using Polycrystalline Silicon Thin-Film Transistors With Trenched Body. IEEE Electron Device Lett. 2008, 29, 1222–1225. [Google Scholar]

- Kim, M.; Cho, W. Capacitorless 1T-DRAM on Crystallized Poly-Si TFT. J. Nanosci. Nanotechnol. 2011, 11, 5608–5611. [Google Scholar] [CrossRef] [PubMed]

- Han, J.-W.; Ryu, S.-W.; Kim, D.-H.; Kim, C.-J.; Kim, S.; Moon, D.-I.; Choi, S.-J.; Choi, Y.-K. Fully Depleted Polysilicon TFTs for Capacitorless 1T-DRAM. IEEE Electron Device Lett. 2009, 30, 742–744. [Google Scholar]

- Baek, M.-H.; Lee, S.-H.; Kwon, D.W.; Seo, J.Y.; Park, B.-G. Hole Trapping Phenomenon at the Grain Boundary of Thin Poly-Si Floating-Body MOSFET and Its Capacitor-Less DRAM Application. J. Nanosci. Nanotechnol. 2017, 17, 2906–2990. [Google Scholar] [CrossRef]

- Jang, T.; Baek, M.-H.; Kim, H.; Park, B.-G. An Analysis of Hole Trapping at Grain Boundary or Poly-Si Floating-Body. J. Nanosci. Nanotechnol. 2018, 18, 6584–6587. [Google Scholar] [CrossRef] [PubMed]

- Chen, Y.-T.; Sun, H.-C.; Huang, C.-F.; Wu, T.-Y.; Liu, C.W.; Hsu, Y.-J.; Chen, J.-S. Capacitorless 1T Memory Cells Using Channel Traps at Grain Boundaries. IEEE Electron Device Lett. 2010, 31, 1125–1127. [Google Scholar] [CrossRef]

- Colalongo, L.; Valdinoci, M.; Baccarani, G.; Migliorato, P.; Tallarida, G.; Reita, C. Numerical Analysis of Poly-TFTs under off Conditions. Solid-State Electron. 1997, 41, 627–633. [Google Scholar] [CrossRef]

- Kim, H.-J.; Kang, I.-M.; Cho, S.-J.; Sun, W.-K.; Shin, H.-S. Analysis of operation characteristics of junctionless poly-Si 1T-DRAM in accumulation mode. Semicond. Sci. Technol. 2019, 34, 105007. [Google Scholar] [CrossRef]

- Ram, M.S.; Abdi, D.B. Single Grain Boundary Dopingless PNPN Tunnel FET on Recrystallized Polysilicon: Proposal and Theoretical Analysis. IEEE J. Electron Devices Soc. 2015, 3, 291–296. [Google Scholar] [CrossRef]

| Write “1” | Write “0” | Read | Hold | |

|---|---|---|---|---|

| Vg (V) | −2 | 0 | 0.6 (Silicon 1T-DRAM) 0.7 (Poly-Si 1T-DRAM) − | 0 |

| Vd (V) | 2 | −1.5 | 0.1 | 0 |

| Time (ns) | 500 | 150 | 10 | − |

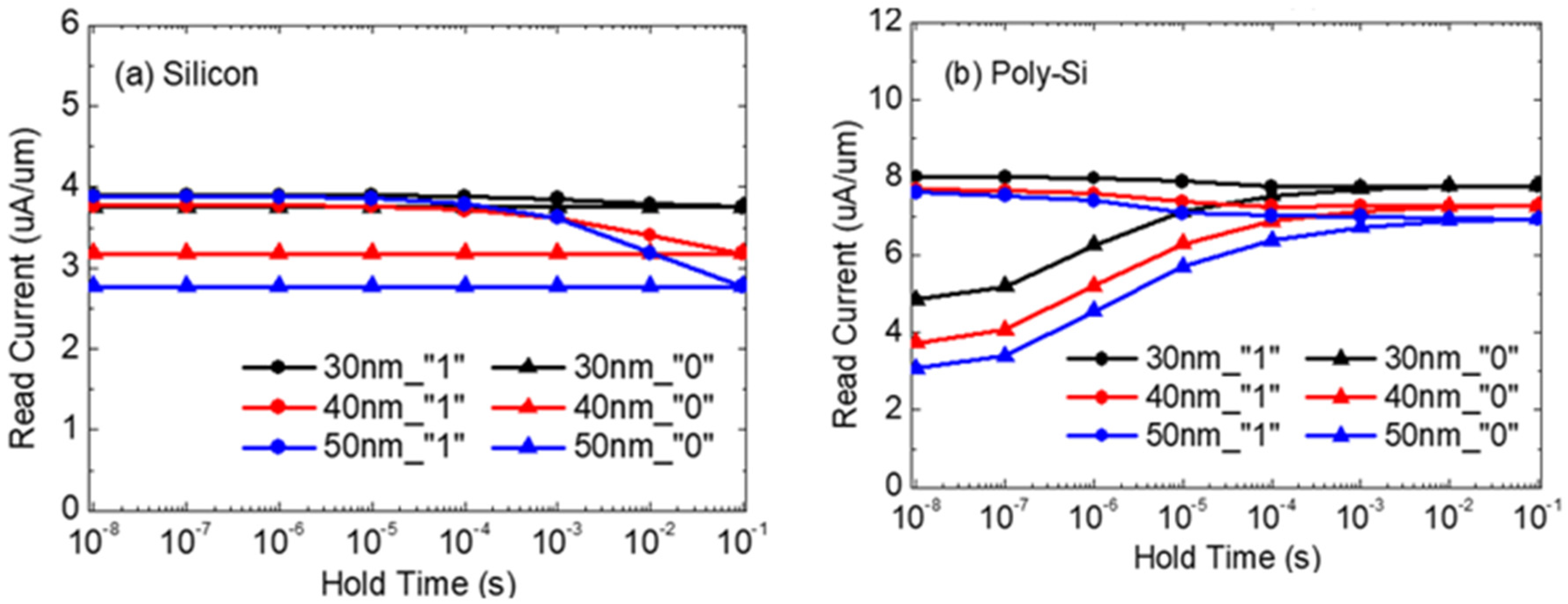

| Tbody | Sensing Margin of Silicon 1T- DRAM (uA/um) | Sensing Margin of Poly-Si 1T- DRAM (uA/um) |

|---|---|---|

| 30 nm | 0.15 | 3.16 |

| 40 nm | 0.59 | 3.96 |

| 50 nm | 1.11 | 4.54 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, H.; Yoo, S.; Kang, I.-M.; Cho, S.; Sun, W.; Shin, H. Analysis of the Sensing Margin of Silicon and Poly-Si 1T-DRAM. Micromachines 2020, 11, 228. https://doi.org/10.3390/mi11020228

Kim H, Yoo S, Kang I-M, Cho S, Sun W, Shin H. Analysis of the Sensing Margin of Silicon and Poly-Si 1T-DRAM. Micromachines. 2020; 11(2):228. https://doi.org/10.3390/mi11020228

Chicago/Turabian StyleKim, Hyeonjeong, Songyi Yoo, In-Man Kang, Seongjae Cho, Wookyung Sun, and Hyungsoon Shin. 2020. "Analysis of the Sensing Margin of Silicon and Poly-Si 1T-DRAM" Micromachines 11, no. 2: 228. https://doi.org/10.3390/mi11020228