Fabrication and Electrical Characterization of High Aspect Ratio Through-Silicon Vias with Polyimide Liner for 3D Integration

Abstract

:1. Introduction

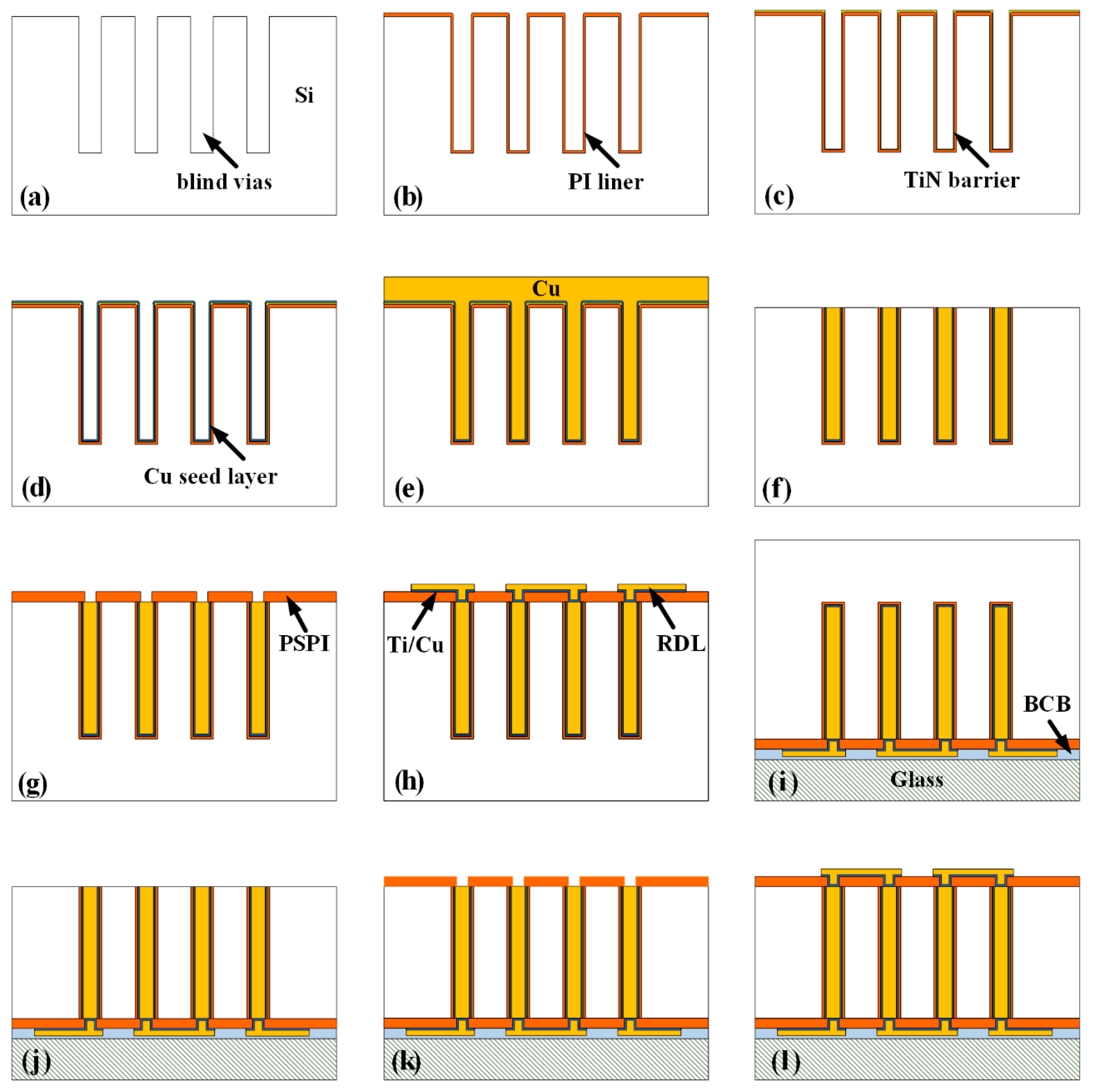

2. Process Design

2.1. Vacuum-Assisted Spin Coating of PI

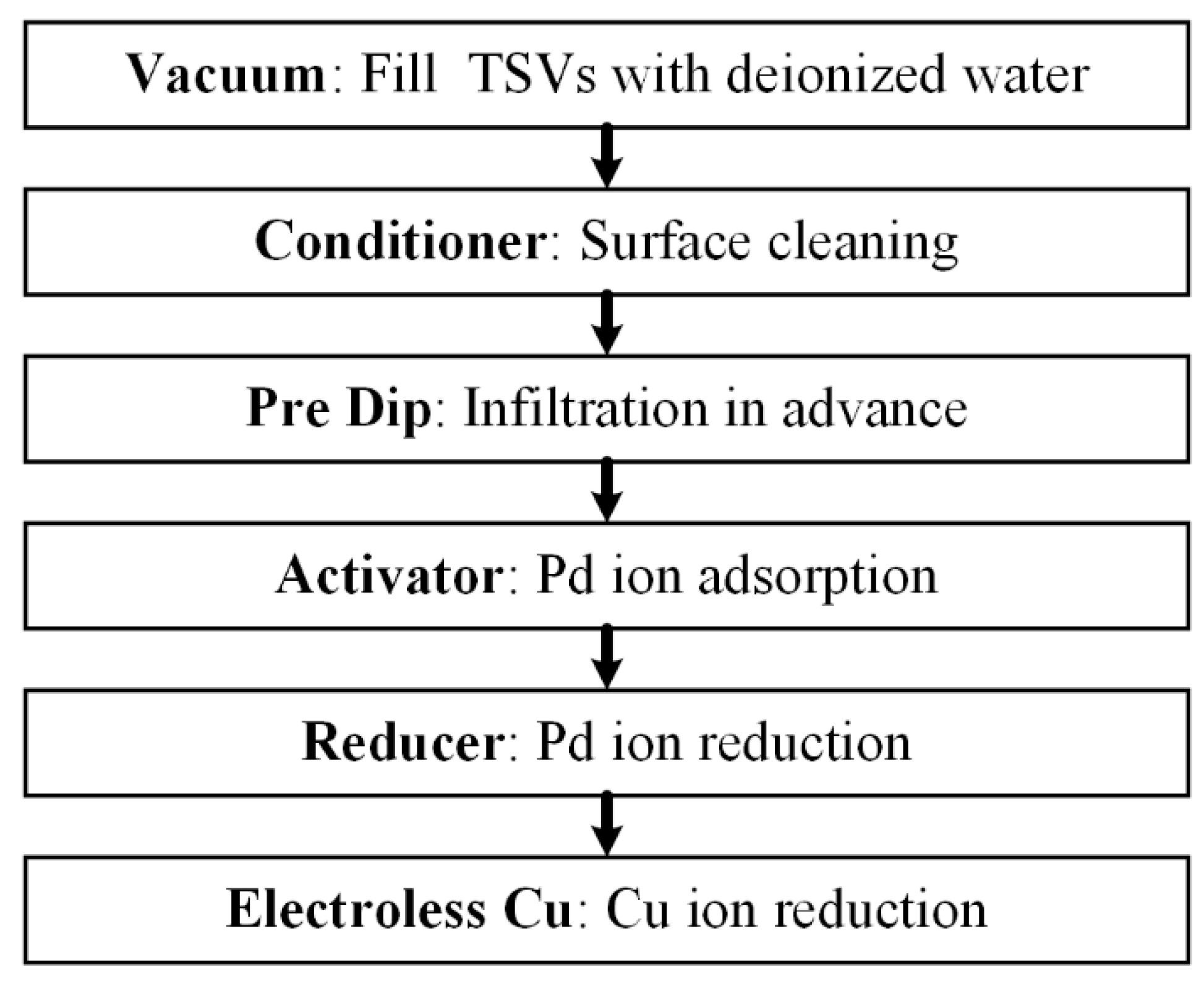

2.2. Electroless Plating of Cu

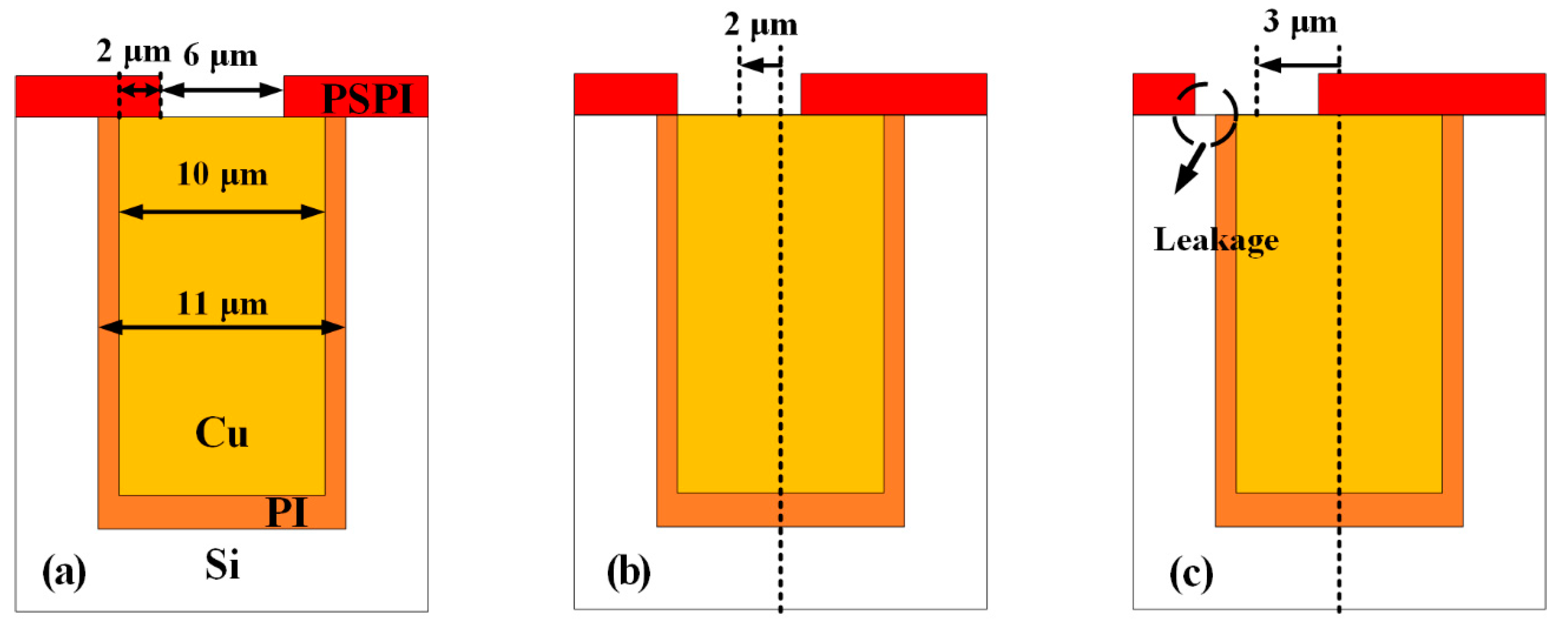

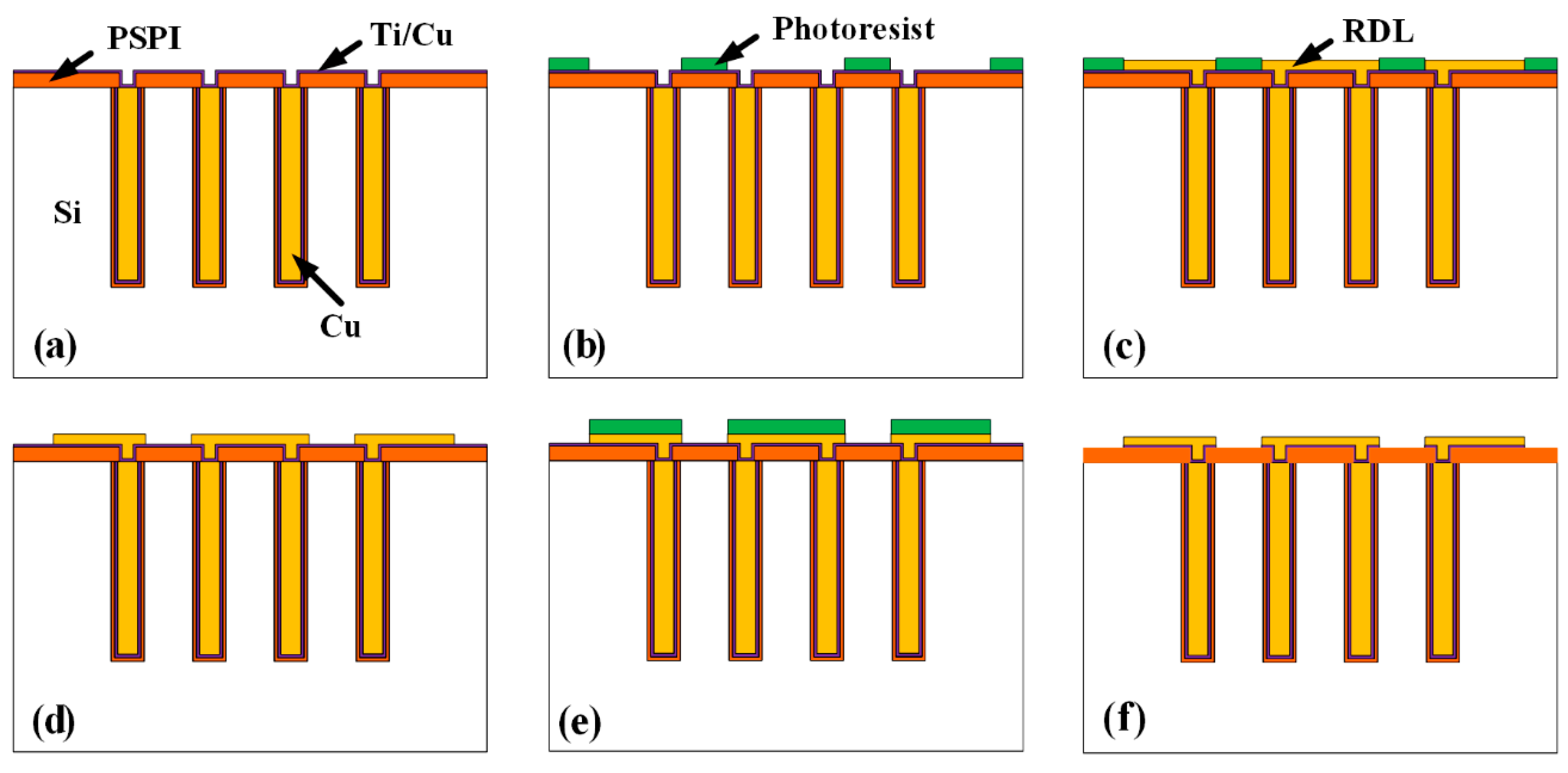

2.3. Fabrication of PSPI Insulating Layer and Cu RDLs

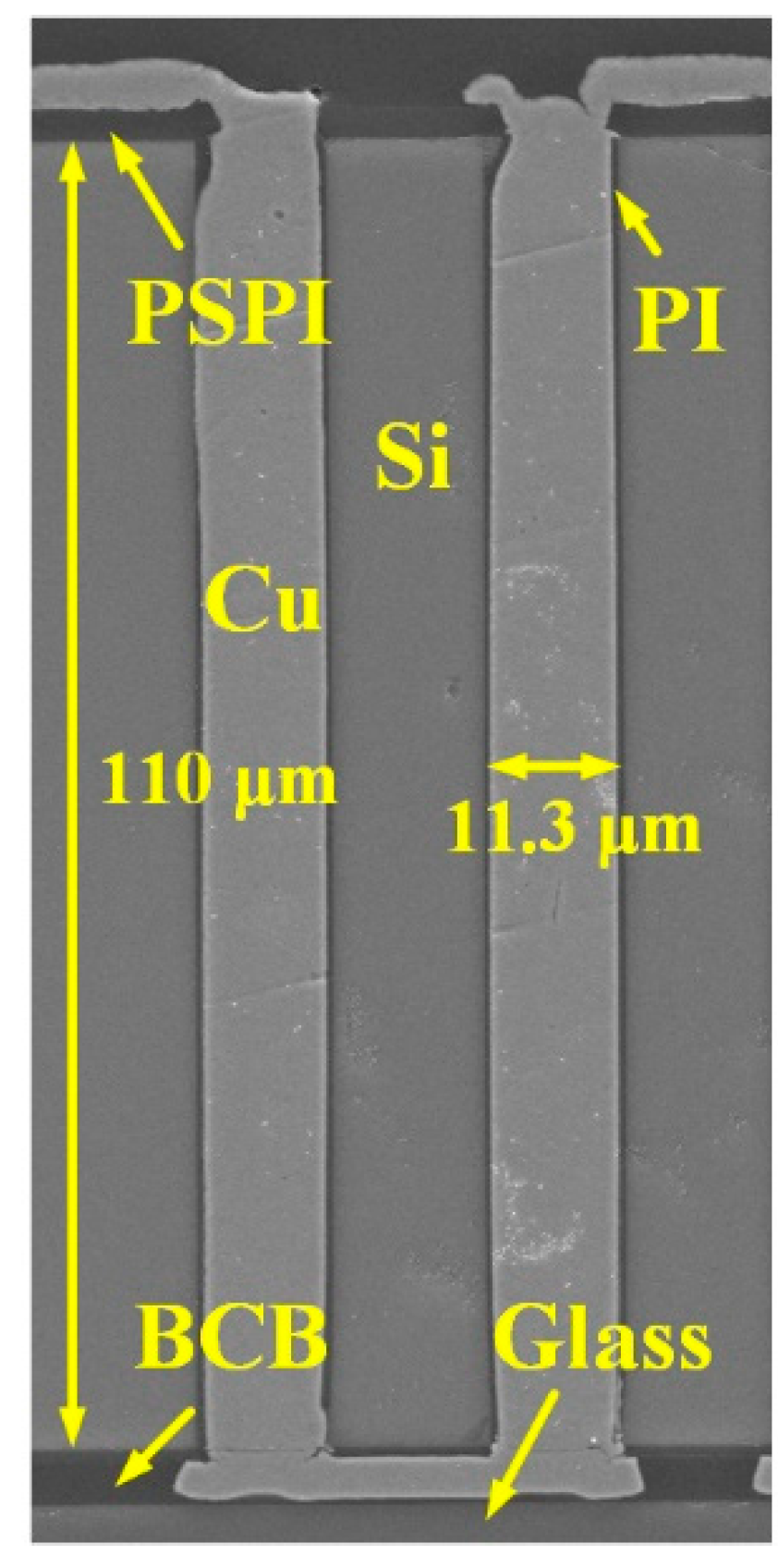

3. Fabrication

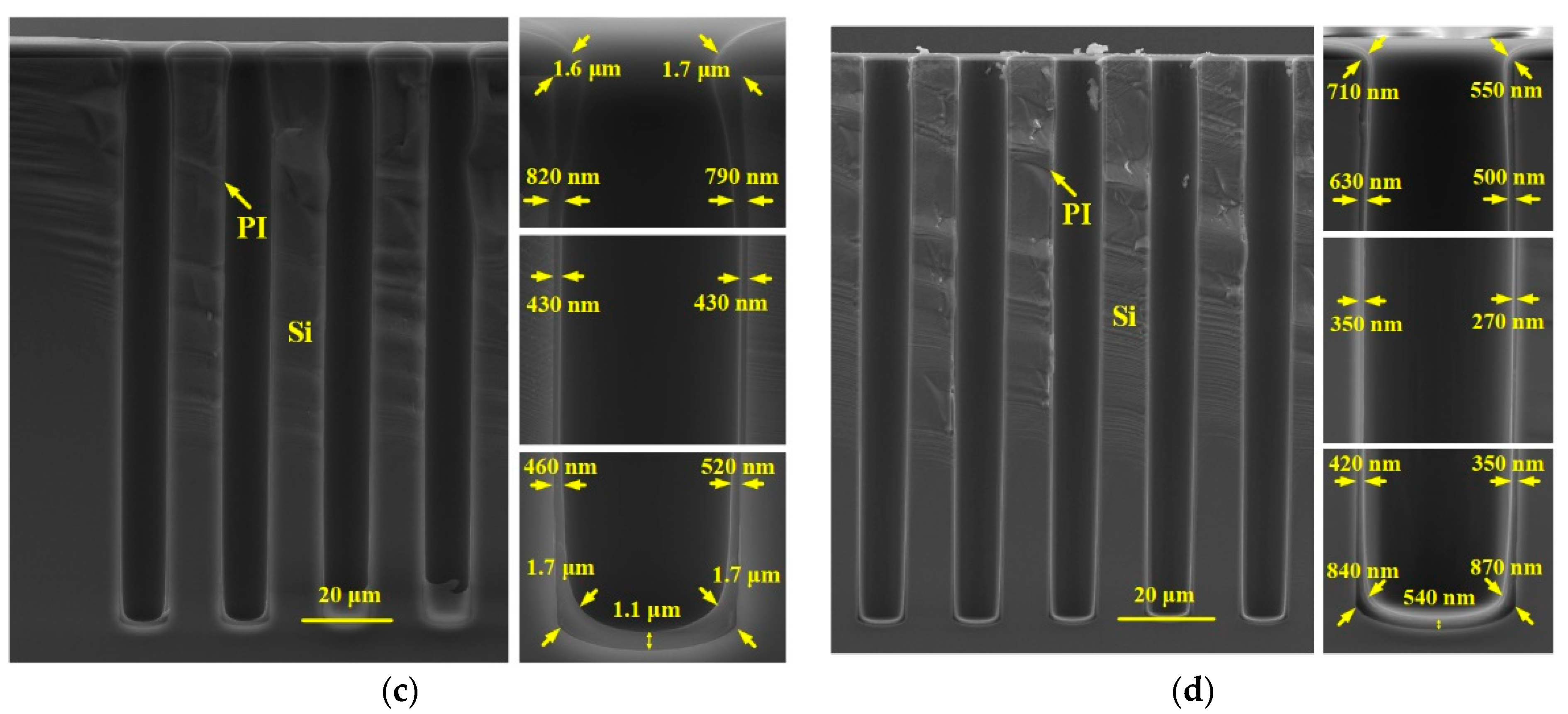

3.1. Deposition of PI Liner

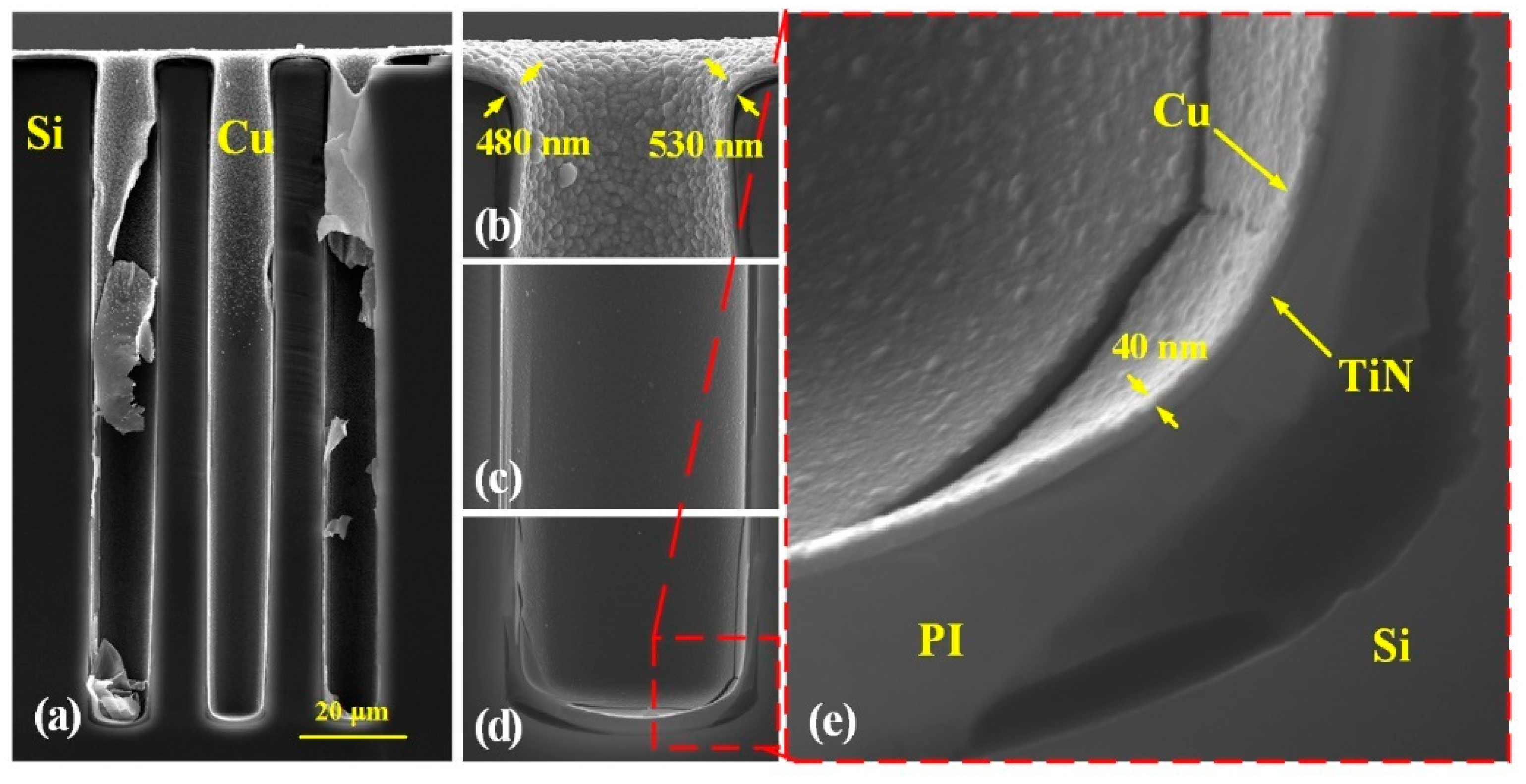

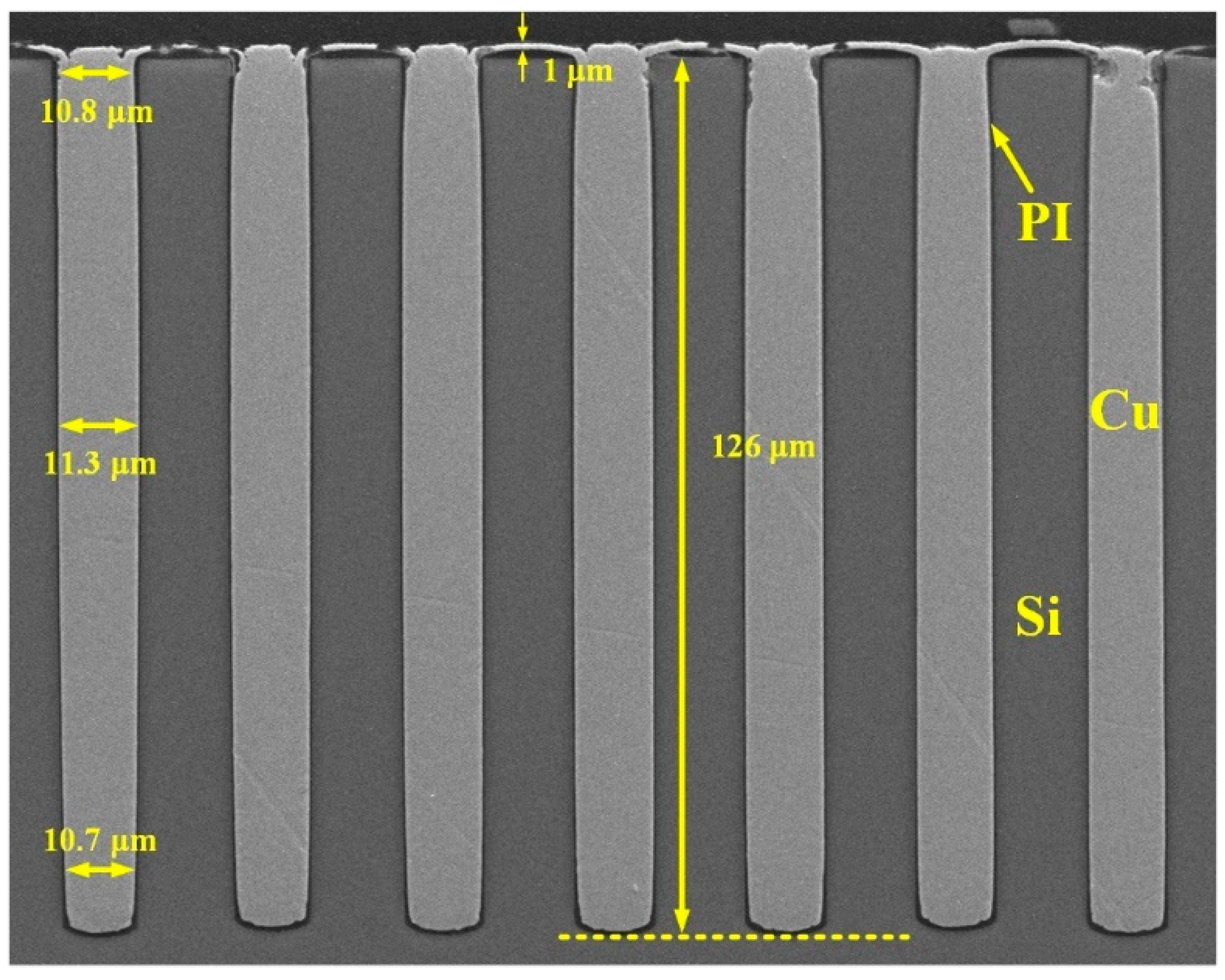

3.2. Deposition of Cu Seed Layer

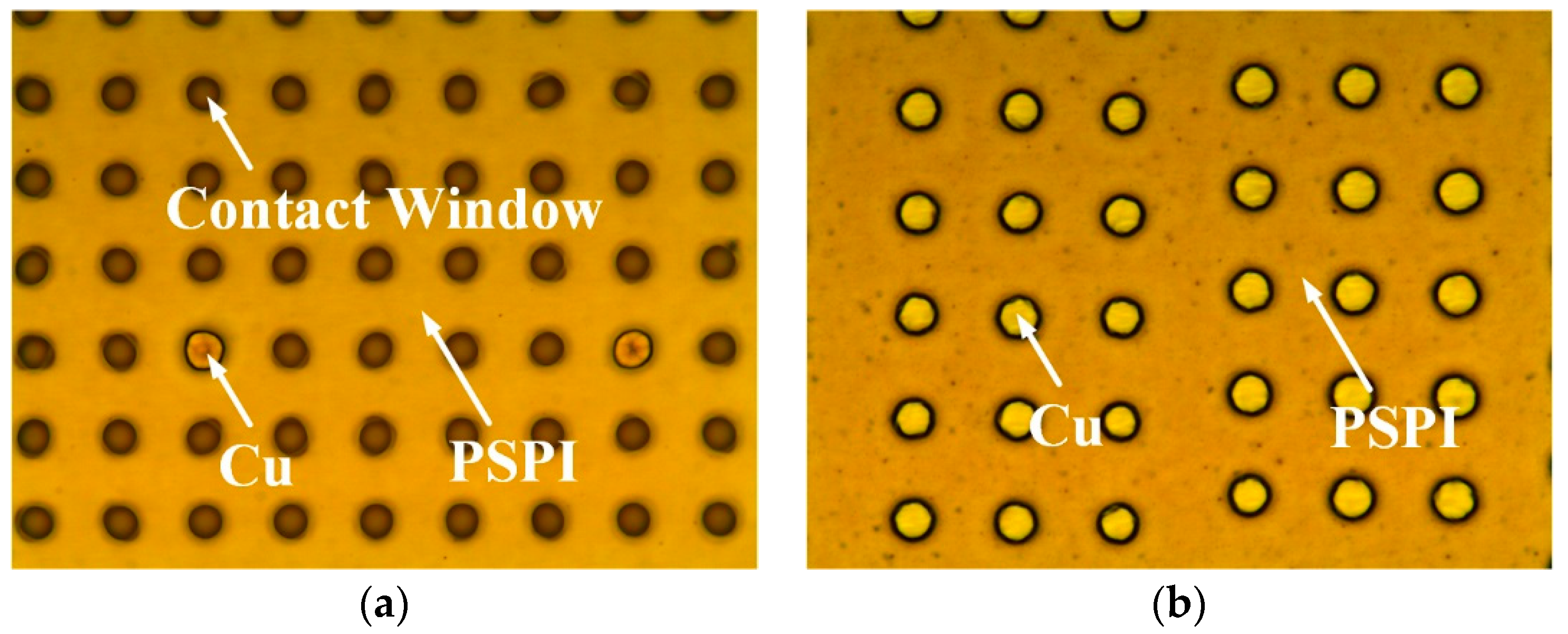

3.3. Fabrication of PSPI Insulating Layer in Field Area

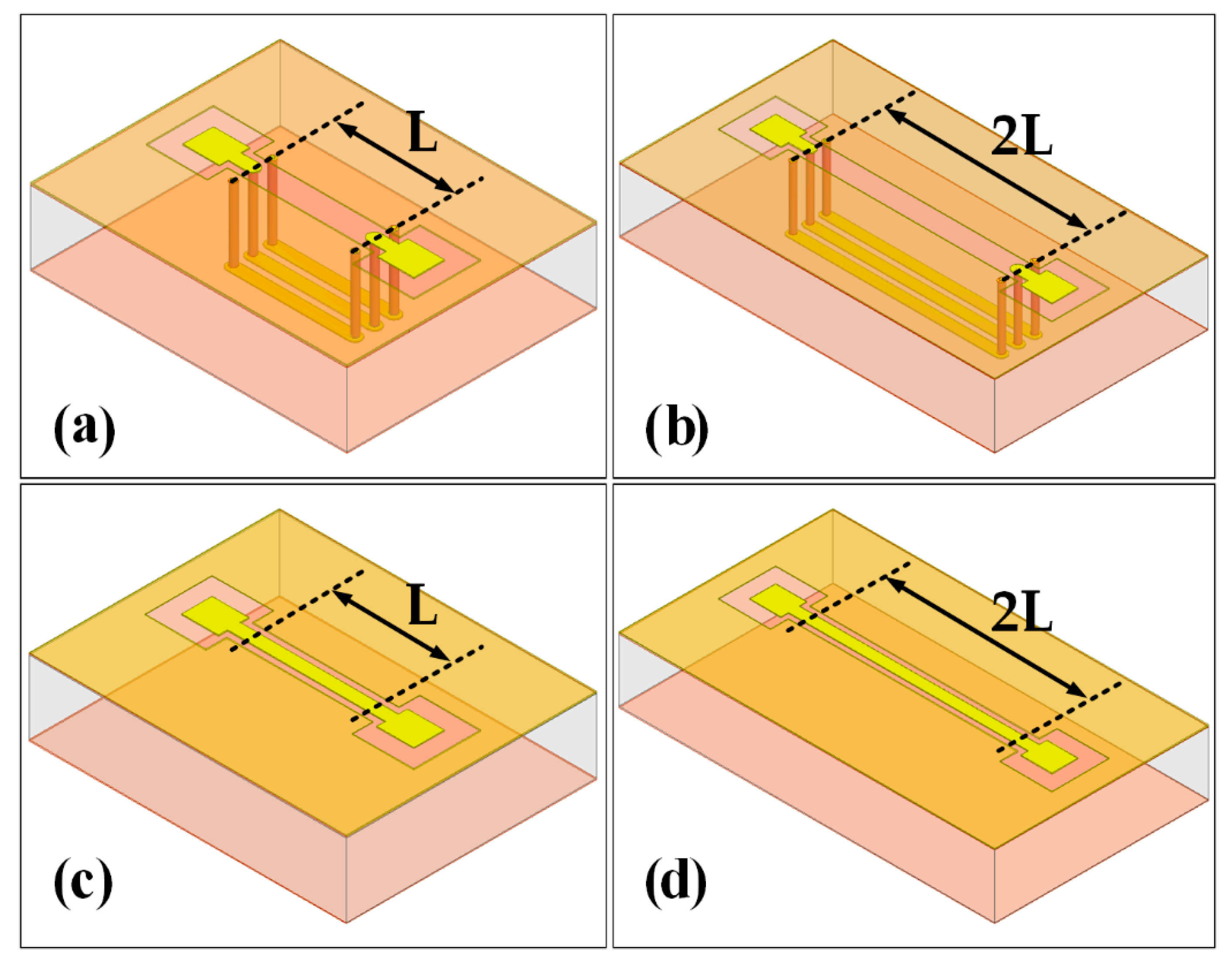

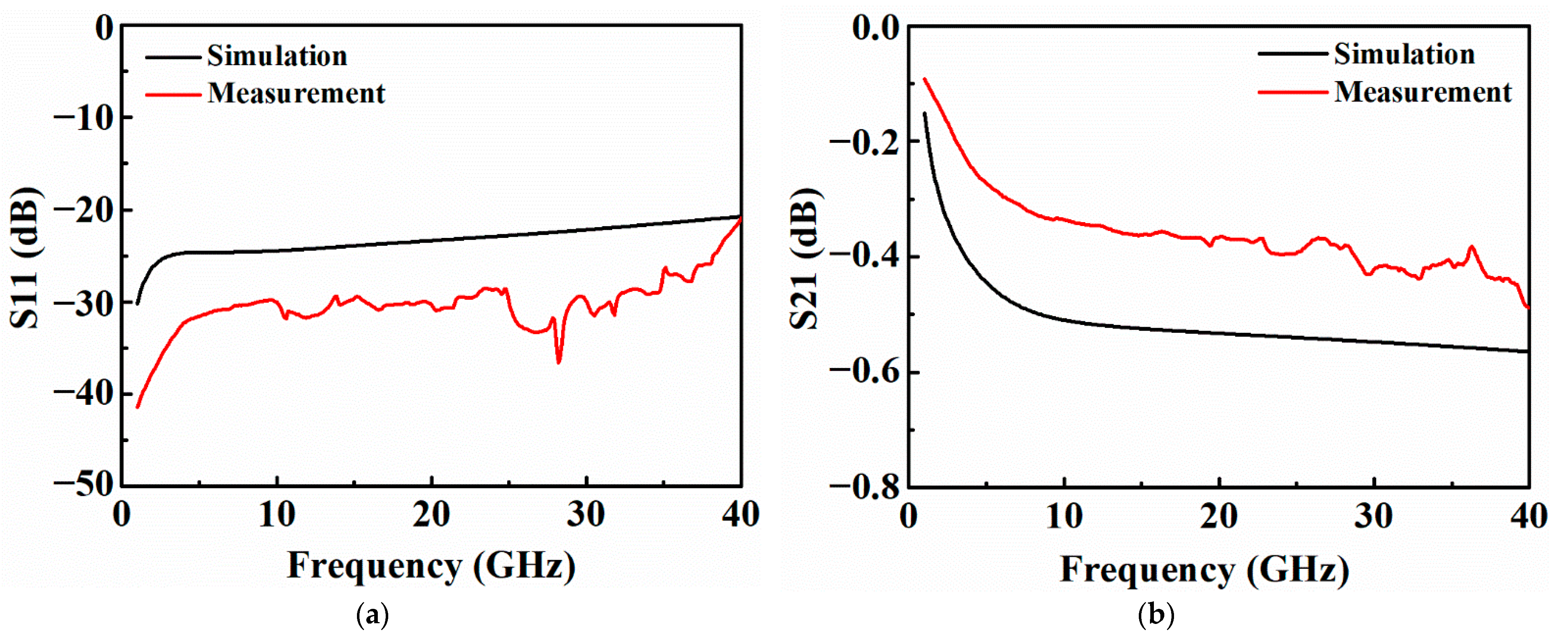

4. Electrical Characterizations

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Hisamoto, D.; Lee, W.C.; Kedzierski, J.; Takeuchi, H.; Asano, K.; Kuo, C.; Anderson, E.; King, T.J.; Bokor, J.; Hu, C.M. FinFET-a Self-Aligned Double-Gate MOSFET Scalable to 20 nm. IEEE Trans. Electron Devices 2000, 47, 2320–2325. [Google Scholar]

- Chan, V.W.C.; Chan, P.C.H. Fabrication of Gate-All-Around Transistors Using Metal Induced Lateral Crystallization. IEEE Electron Device Lett. 2001, 22, 80–82. [Google Scholar] [CrossRef]

- Wong, H. On the CMOS Device Downsizing, More Moore, More than Moore, and More-than-Moore for More Moore. In Proceedings of the 32nd IEEE International Conference on Microelectronics (MIEL), Niš, Serbia, 12–14 September 2021; pp. 9–15. [Google Scholar]

- Meindl, J.D.; Davis, J.A.; Zarkesh-Ha, P.; Patel, C.S.; Martin, K.P.; Kohl, P.A. Interconnect Opportunities for Gigascale Integration. IBM J. Res. Dev. 2002, 46, 245–263. [Google Scholar] [CrossRef]

- Karnik, T.; Somasekhar, D.; Borkar, S. Microprocessor System Applications and Challenges for Through-Silicon-Via-Based Three-Dimensional Integration. IET Comput. Digit. Technol. 2011, 5, 205–212. [Google Scholar] [CrossRef]

- Shen, W.-W.; Chen, K.-N. Three-Dimensional Integrated Circuit (3D IC) Key Technology: Through-Silicon Via (TSV). Nanoscale Res. Lett. 2017, 12, 56. [Google Scholar] [CrossRef] [Green Version]

- Joyner, J.W.; Zarkesh-Ha, P.; Meindl, J.D. Global Interconnect Design in a Three-Dimensional System-on-a-Chip. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2004, 12, 367–372. [Google Scholar] [CrossRef]

- Wang, Z. 3-D Integration and Through-Silicon Vias in MEMS and Microsensors. J. Microelectromech. Syst. 2015, 24, 1211–1244. [Google Scholar] [CrossRef]

- Sunohara, M.; Tokunaga, T.; Kurihara, T.; Higashi, M. Silicon Interposer with TSVs (Through Silicon Vias) and Fine Multilayer Wiring. In Proceedings of the 58th IEEE Electronic Components and Technology Conference, Orlando, FL, USA, 27–30 May 2008; pp. 847–852. [Google Scholar]

- He, H.; Lu, J.J.Q.; Xu, Z.; Gu, X. TSV Density Impact on 3D Power Delivery with High Aspect Ratio TSVs. In Proceedings of the 24th IEEE Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC), Saratoga Springs, NY, USA, 14–16 May 2013; pp. 70–74. [Google Scholar]

- Wang, Z. Microsystems Using Three-Dimensional Integration and TSV Technologies: Fundamentals and Applications. Microelectron. Eng. 2019, 210, 35–64. [Google Scholar] [CrossRef]

- Yong, Z.; Li, H.; Zhang, W. Fabrication of Dielectric Insulation Layers in TSV by Different Processes. In Proceedings of the 16th IEEE Electronics Packaging Technology Conference (EPTC), Marina Bay Sands, Singapore, 3–5 December 2014; pp. 684–687. [Google Scholar]

- Shi, Y.; He, L.; Guang, F.; Li, L.; Xin, Z.; Liu, R. A Review: Preparation, Performance, and Applications of Silicon Oxynitride Film. Micromachines 2019, 10, 552. [Google Scholar] [CrossRef] [Green Version]

- Yan, Y.; Ding, Y.; Fukushima, T.; Lee, K.-W.; Koyanagi, M. Study of Vacuum-Assisted Spin Coating of Polymer Liner for High-Aspect-Ratio Through-Silicon-Via Applications. IEEE Trans. Compon. Packag. Manuf. 2016, 6, 501–509. [Google Scholar] [CrossRef]

- Huang, C.; Wu, K.; Wang, Z. Low-Capacitance Through-Silicon-Vias with Combined Air/SiO2 Liners. IEEE Trans. Electron Devices 2016, 63, 739–745. [Google Scholar] [CrossRef]

- Ding, Y.; Yan, Y.; Chen, Q.; Wang, S.; Su, R.; Dang, H. Analytical Solution on Interfacial Reliability of 3-D Through-Silicon-Via (TSV) Containing Dielectric Liner. Microelectron. Reliab. 2014, 54, 1384–1391. [Google Scholar] [CrossRef]

- Li, L.; Tuan, C.-C.; Moon, K.-S.; Zhang, G.; Sun, R.; Soc, I.C. Formation of Polymer Insulation Layer (Liner) on Through Silicon Vias (TSV) with High Aspect Ratio over 5:1 by Direct Spin Coating. In Proceedings of the 66th IEEE Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 31 May–3 June 2016; pp. 1713–1719. [Google Scholar]

- Yan, Y.; Ding, Y.; Chen, Q.; Lee, K.; Fukushima, T.; Koyanagi, M. Vacuum-Assisted-Spin-Coating of Polyimide Liner for High-Aspect-Ratio TSVs Applications. In Proceedings of the IEEE International 3D Systems Integration Conference (3DIC), Sendai, Japan, 31 August–2 September 2015. [Google Scholar]

- Wong, G.H.; Chui, K.J.; Lau, G.K.; Loh, W.L.; Yu, L.H. Through Silicon via (TSV) Scallop Smoothening Technique. In Proceedings of the 16th IEEE Electronics Packaging Technology Conference (EPTC), Marina Bay Sands, Singapore, 3–5 December 2014; pp. 676–678. [Google Scholar]

- Fukushima, T.; Mariappan, M.; Bea, J.; Lee, K.-W.; Koyanagi, M. Low-Temperature and High-Step-Coverage Polyimide TSV Liner Formation by Vapor Deposition Polymerization. In Proceedings of the International Conference on Solid State Devices and Materials, Fukuoka, Japan, 24–27 September 2013; pp. 866–867. [Google Scholar]

- Murugesan, M.; Fukushima, T.; Bea, J.C.; Sato, Y.; Hashimoto, H.; Lee, K.W.; Koyanagi, M. Highly Beneficial Organic Liner with Extremely Low Thermal Stress for Fine Cu-TSV in 3D-Integration. In Proceedings of the 60th Annual IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2014. [Google Scholar]

- Murugesan, M.; Fukushima, T.; Bea, J.C.; Hashimoto, H.; Sato, Y.; Lee, K.W.; Koyanagi, M. Improved C-V, I-V Characteristics for Co-Polymerized Organic Liner in the Through-Silicon-Via for High Frequency Applications by Post Heat Treatment. In Proceedings of the 65th IEEE Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 26–29 May 2015; pp. 73–77. [Google Scholar]

- Mariappan, M.; Fukushima, T.; Bea, J.-C.; Hashimoto, H.; Koyanagi, M. Capacitance Characteristics of Low-k Low-cost CVD Grown Polyimide Liner for High-Density Cu Through-Si-Via in Three-Dimensional LSI. Jpn. J. Appl. Phys. 2016, 55, 4S. [Google Scholar] [CrossRef]

- Yan, Y.Y.; Xiong, M.; Liu, B.; Ding, Y.T.; Chen, Z.M. Low Capacitance and Highly Reliable Blind Through-Silicon-Vias (TSVs) with Vacuum-Assisted Spin Coating of Polyimide Dielectric Liners. Sci. China-Technol. Sci. 2016, 59, 1581–1590. [Google Scholar] [CrossRef]

- Wang, S.W.; Yan, Y.Y.; Cheng, Z.Q.; Chen, Z.M.; Ding, Y.T. Impact of Polyimide Liner on High-Aspect-Ratio Through-Silicon-Vias (TSVs): Electrical Characteristics and Copper Protrusion. Microsyst. Technol. 2017, 23, 3757–3764. [Google Scholar] [CrossRef]

- Xiong, M.; Chen, Z.; Ding, Y.; Kino, H.; Fukushima, T.; Tanaka, T. Development of Eccentric Spin Coating of Polymer Liner for Low-Temperature TSV Technology with Ultra-Fine Diameter. IEEE Electron Device Lett. 2019, 40, 95–98. [Google Scholar] [CrossRef]

- Zhang, Z.; Ding, Y.; Xiao, L.; Cai, Z.; Yang, B.; Chen, Z.; Xie, H. Enabling Continuous Cu Seed Layer for Deep Through-Silicon-Vias With High Aspect Ratio by Sequential Sputtering and Electroless Plating. IEEE Electron Device Lett. 2021, 42, 1520–1523. [Google Scholar] [CrossRef]

- Nishizawa, S.; Arima, R.; Shimizu, T.; Shingubara, S.; Inoue, F. Highly Conformal and Adhesive Electroless Barrier and Cu Seed Formation using Nanoparticle Catalyst for Realizing a High Aspect Ratio Cu-filled TSV. In Proceedings of the IEEE International 3D Systems Integration Conference (3DIC), San Francisco, CA, USA, 2–4 October 2013. [Google Scholar]

- Xiao, L.; Ding, Y.; Su, Y.; Zhang, Z.; Yan, Y.; Chen, Z.; Xie, H. Ultra-Deep Annular Cu Through-Silicon-Vias Fabricated Using Single-Sided Process. IEEE Electron Device Lett. 2022, 43, 426–429. [Google Scholar] [CrossRef]

- Mariappan, M.; Fukushima, T.; Bea, J.C.; Lee, K.-W.; Koyanagi, M. Mechanical Characteristics of Thin Die/Wafers in Three-Dimensional Large-Scale Integrated Systems. IEEE Trans. Semicond. Manuf. 2014, 27, 341–346. [Google Scholar] [CrossRef]

- Luo, X.; Xiao, L.; Wang, X. Crack-Free Fabrication and Electrical Characterization of Coaxial Ultra-Low-Resistivity-Silicon Through-Silicon-Vias. IEEE Trans. Semicond. Manuf. 2020, 33, 103–108. [Google Scholar] [CrossRef]

- Yen, H.-T.; Lin, Y.-L.; Hu, C.; Jan, S.B.; Hsieh, C.-C.; Chen, M.F.; Kuo, C.-W.; Chen, H.-H.; Jeng, M.-C. TSV RF De-Embedding Method and Modeling for 3DIC. In Proceedings of the 23rd Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC), Saratoga Springs, NY, USA, 15–17 May 2012; pp. 394–397. [Google Scholar]

- Thadesar, P.A.; Bakir, M.S. Fabrication and Characterization of Polymer-Enhanced TSVs, Inductors, and Antennas for Mixed-Signal Silicon Interposer Platforms. IEEE Trans. Compon. Packag. Manuf. 2016, 6, 455–463. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, X.; Chen, Z.; Xiao, L.; Hao, Y.; Wang, H.; Ding, Y.; Zhang, Z. Fabrication and Electrical Characterization of High Aspect Ratio Through-Silicon Vias with Polyimide Liner for 3D Integration. Micromachines 2022, 13, 1147. https://doi.org/10.3390/mi13071147

Chen X, Chen Z, Xiao L, Hao Y, Wang H, Ding Y, Zhang Z. Fabrication and Electrical Characterization of High Aspect Ratio Through-Silicon Vias with Polyimide Liner for 3D Integration. Micromachines. 2022; 13(7):1147. https://doi.org/10.3390/mi13071147

Chicago/Turabian StyleChen, Xuyan, Zhiming Chen, Lei Xiao, Yigang Hao, Han Wang, Yingtao Ding, and Ziyue Zhang. 2022. "Fabrication and Electrical Characterization of High Aspect Ratio Through-Silicon Vias with Polyimide Liner for 3D Integration" Micromachines 13, no. 7: 1147. https://doi.org/10.3390/mi13071147