Impact of Nitridation on Bias Temperature Instability and Hard Breakdown Characteristics of SiON MOSFETs

Abstract

:1. Introduction

2. Devices

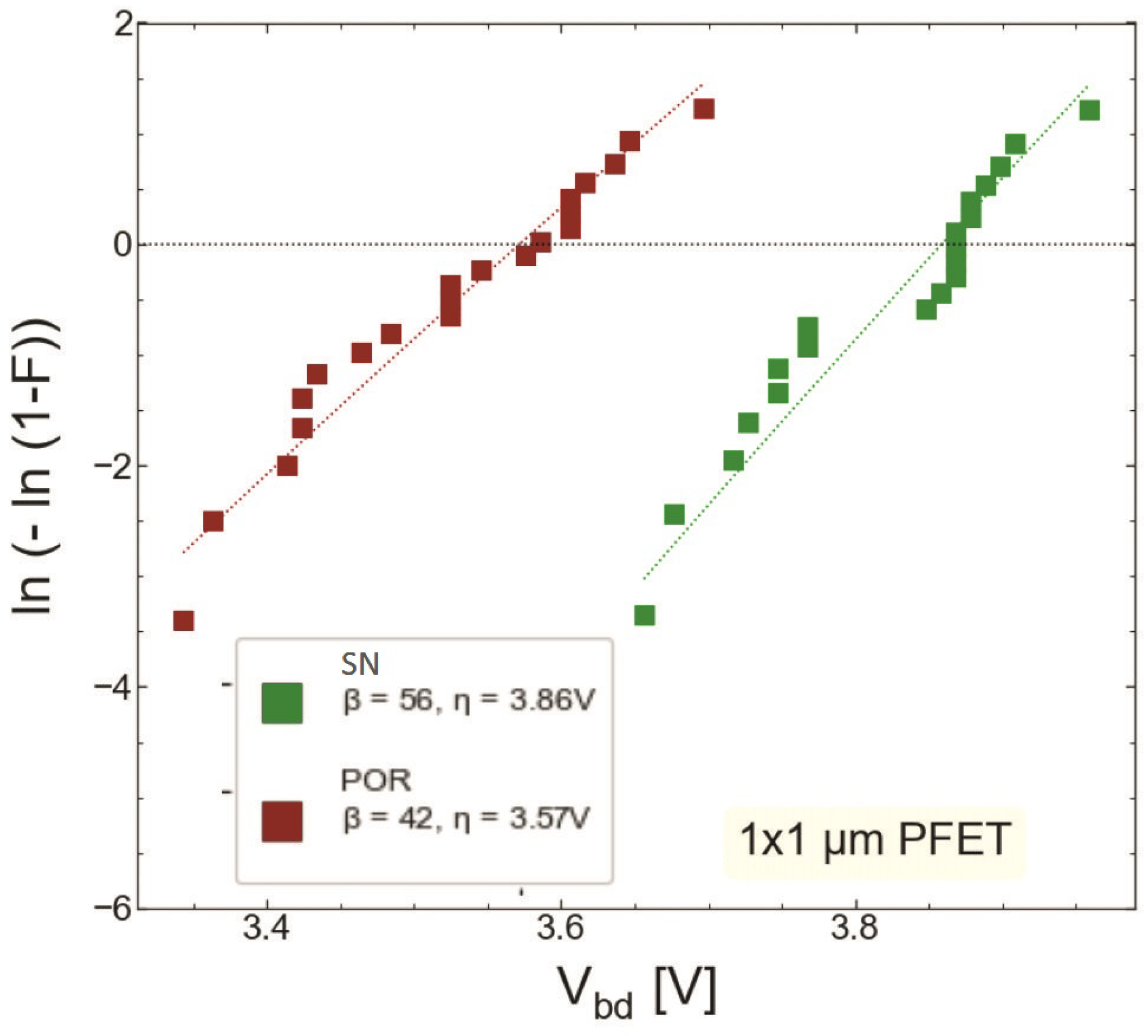

- The process of reference (POR), which includes plasma nitridation at a higher value of the radio frequency (RF) power of 1000 W under a pressure of 20 Torr for 12 s.

- The alternative process with softer nitridation (SN) conducted at a lower RF power of 900 W under a pressure of 20 Torr for 12 s.

3. Experiment and Data Processing

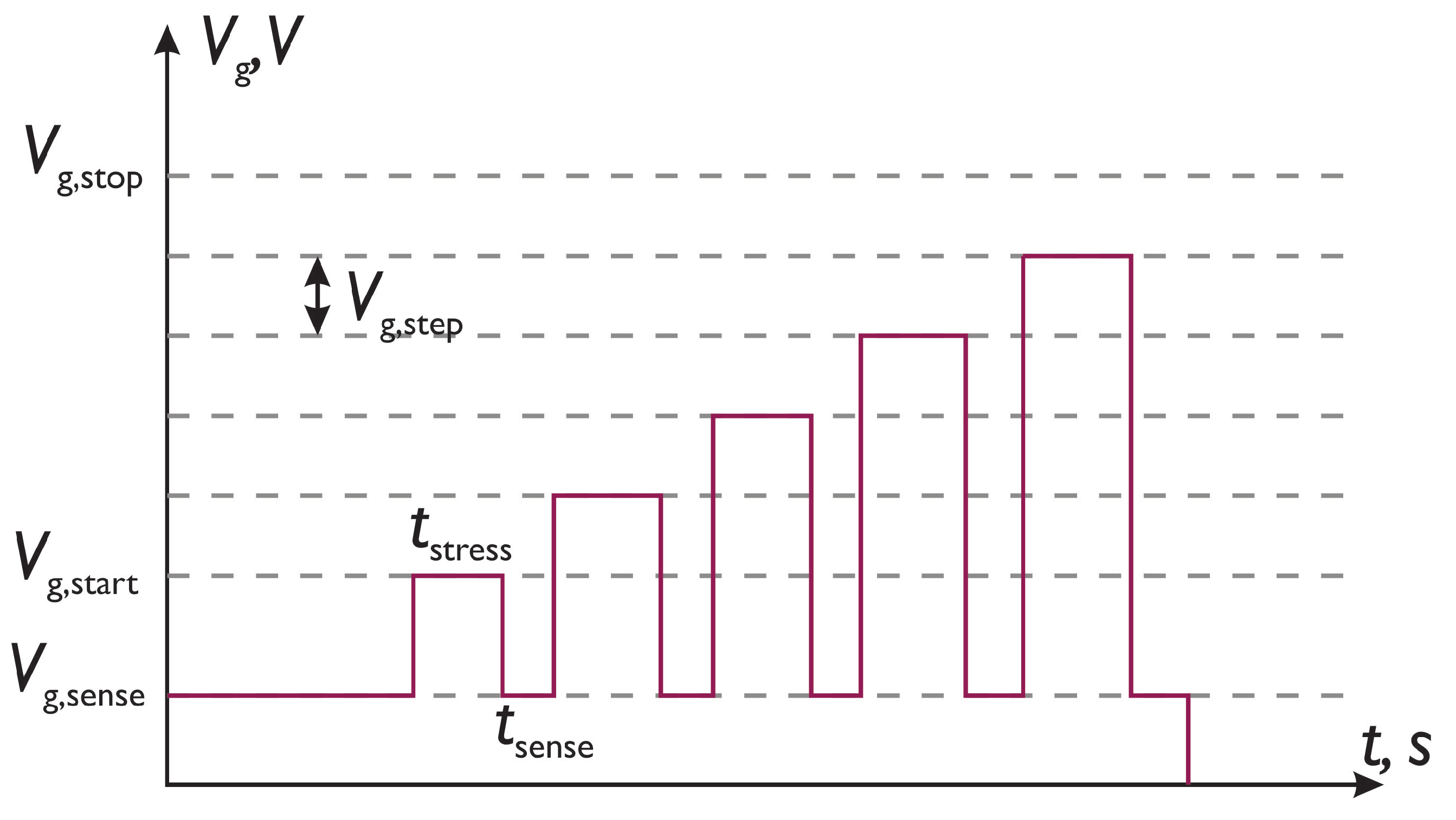

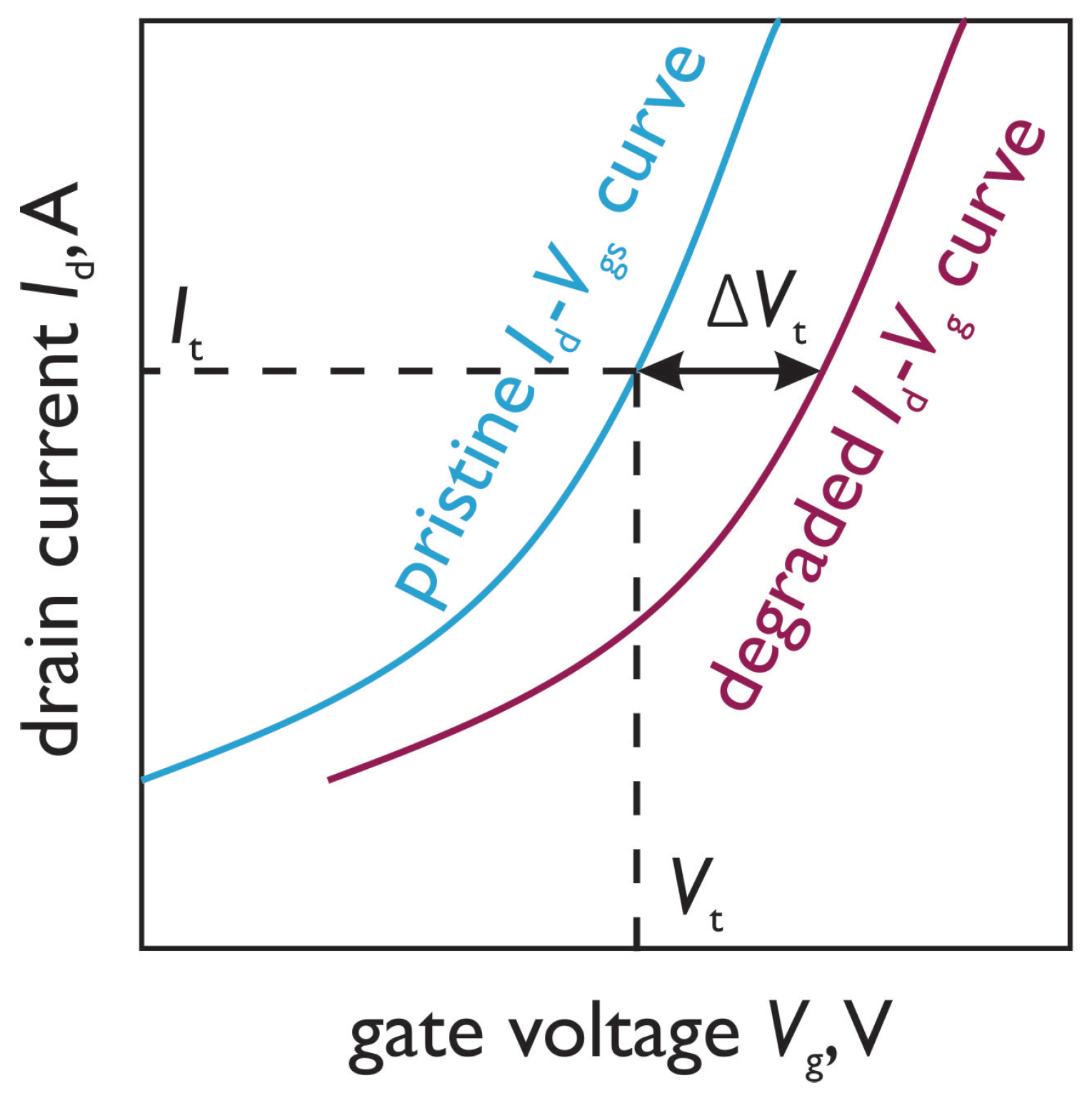

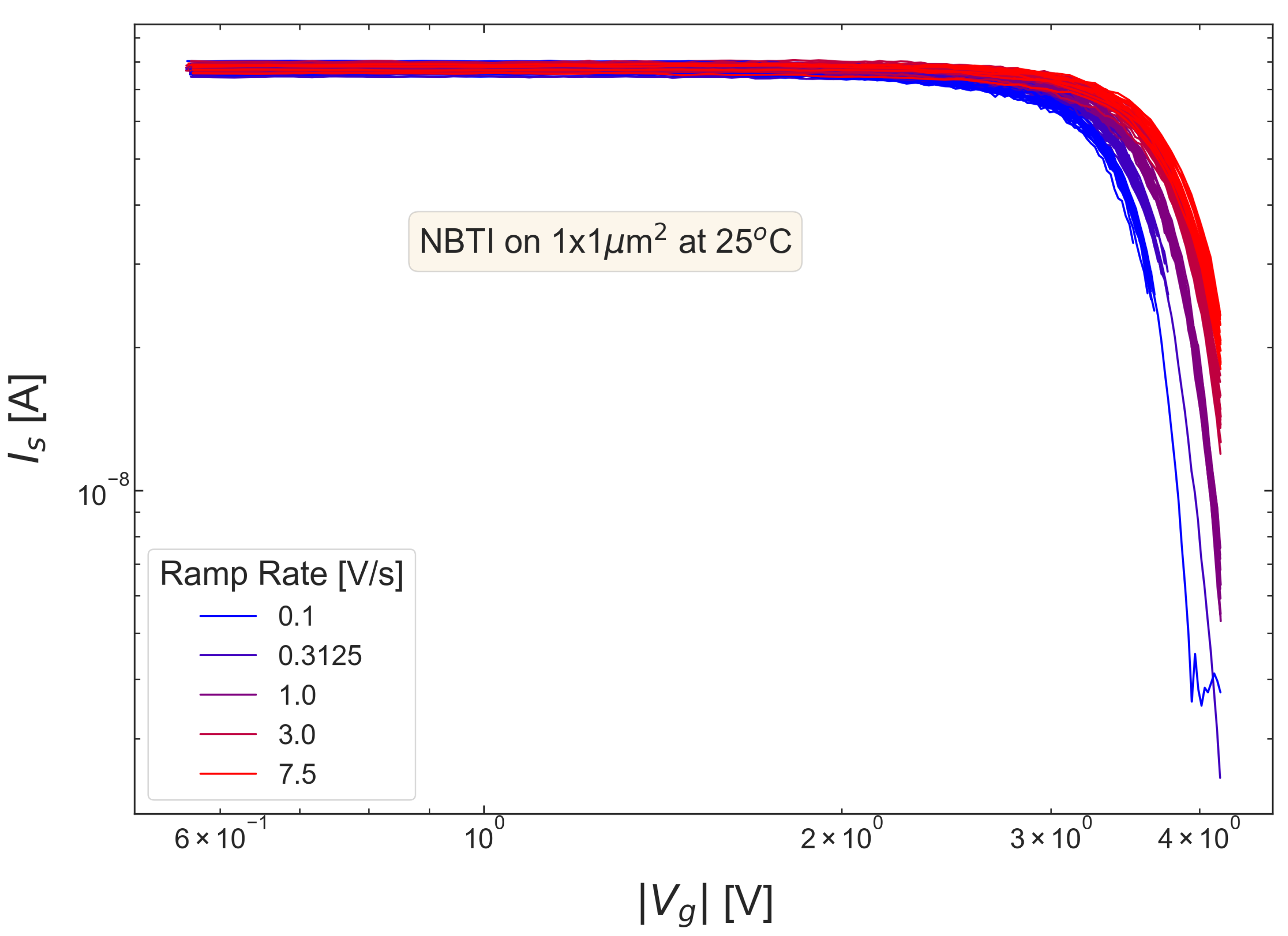

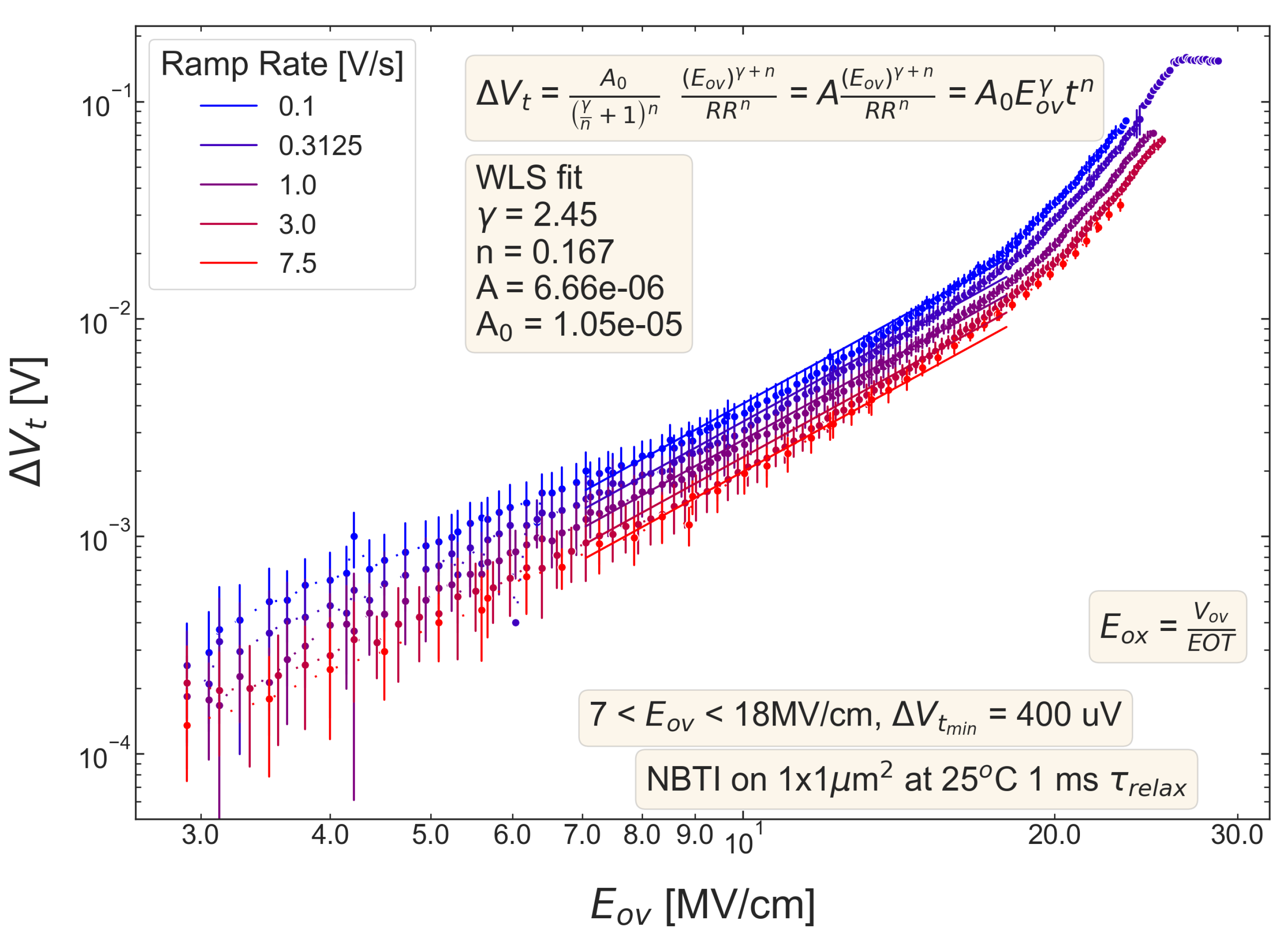

3.1. Bias Temperature Instability

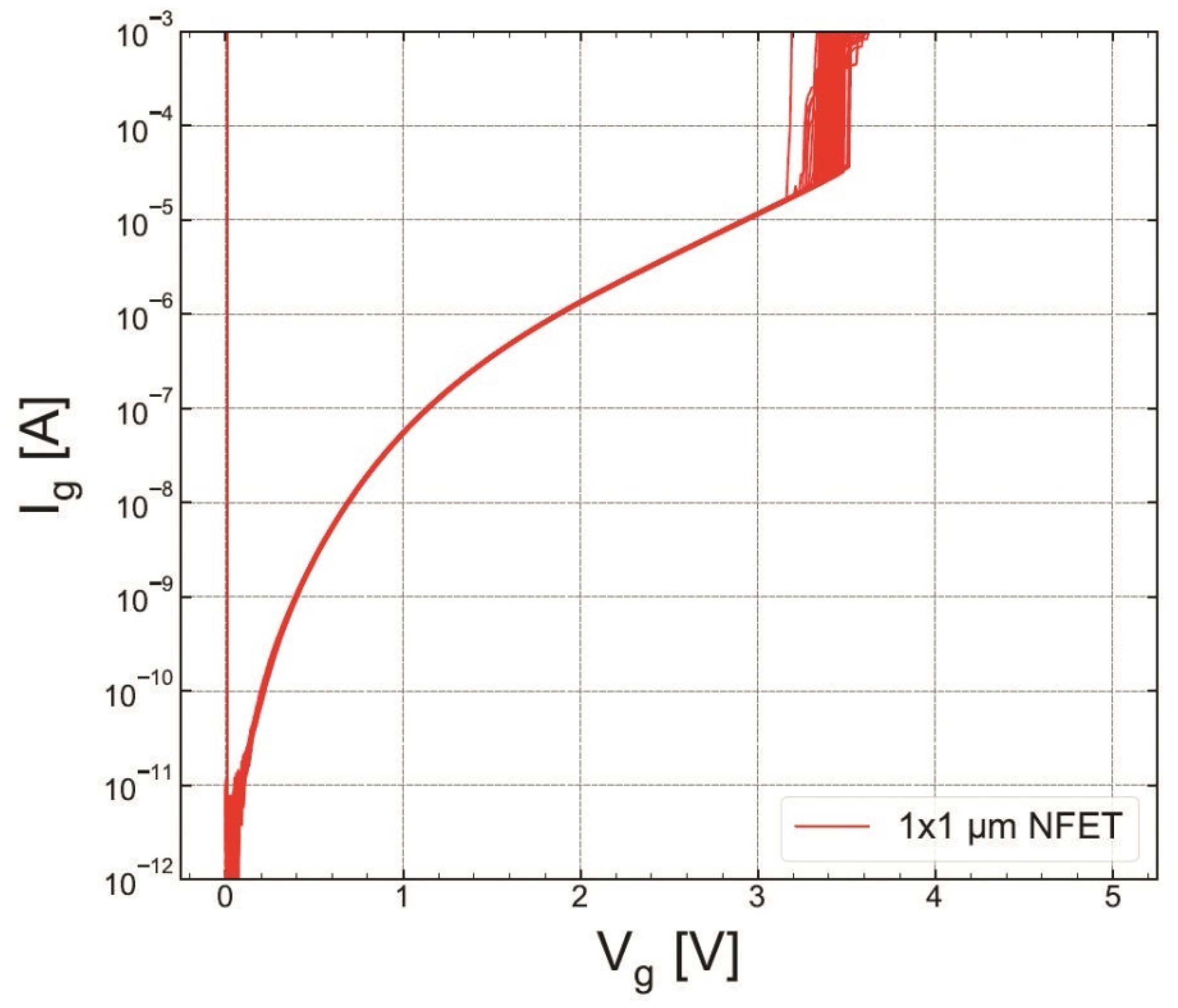

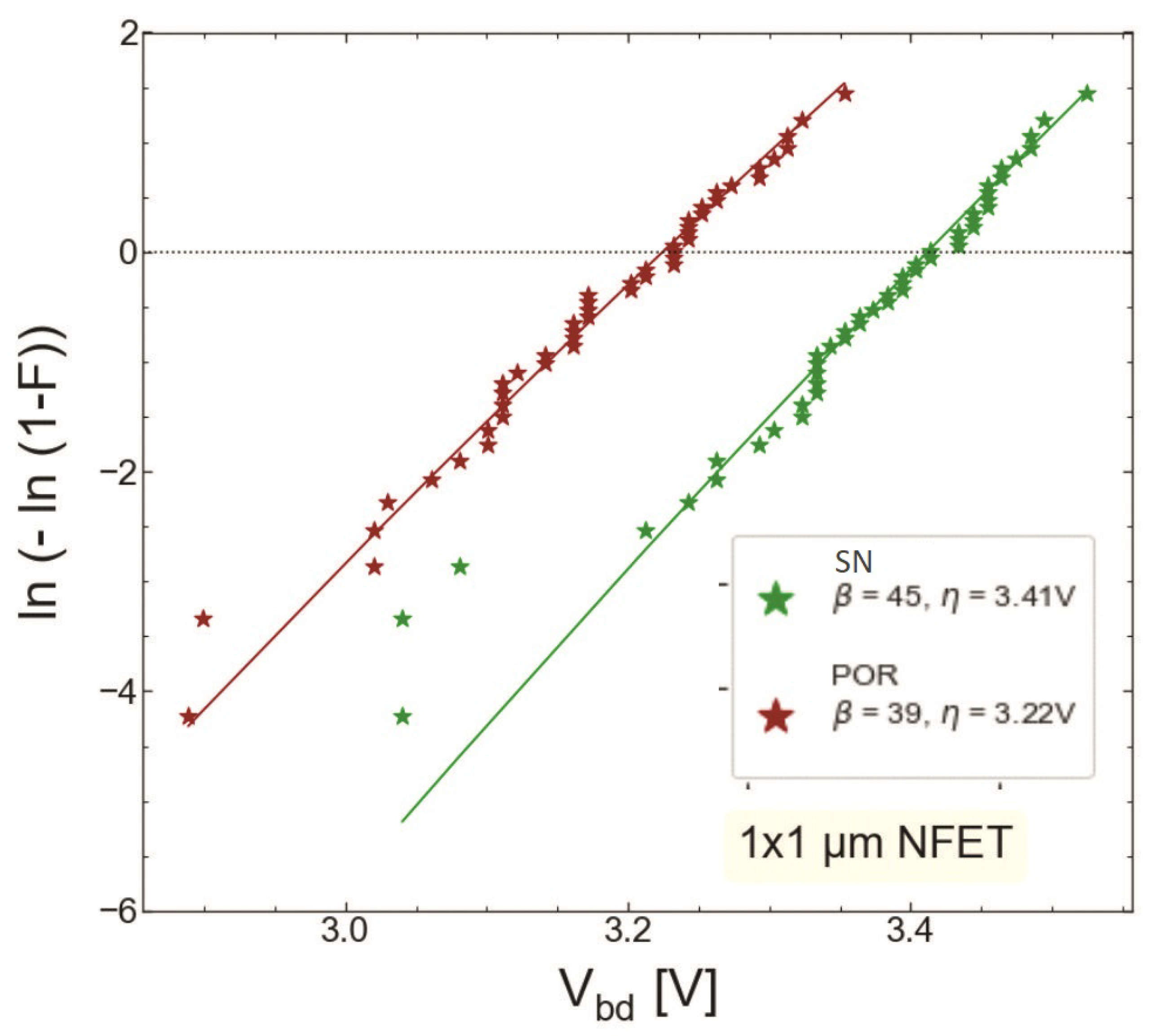

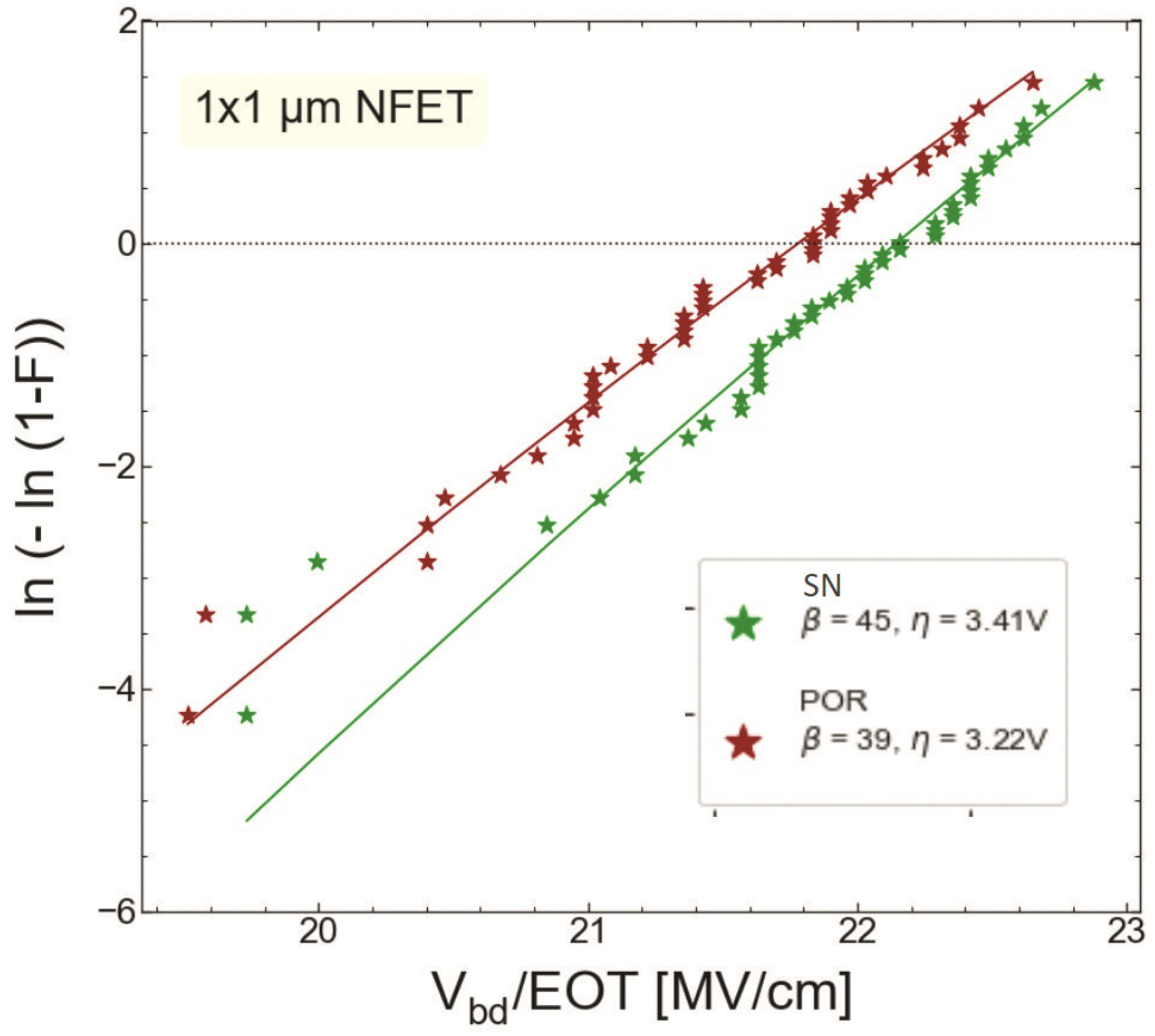

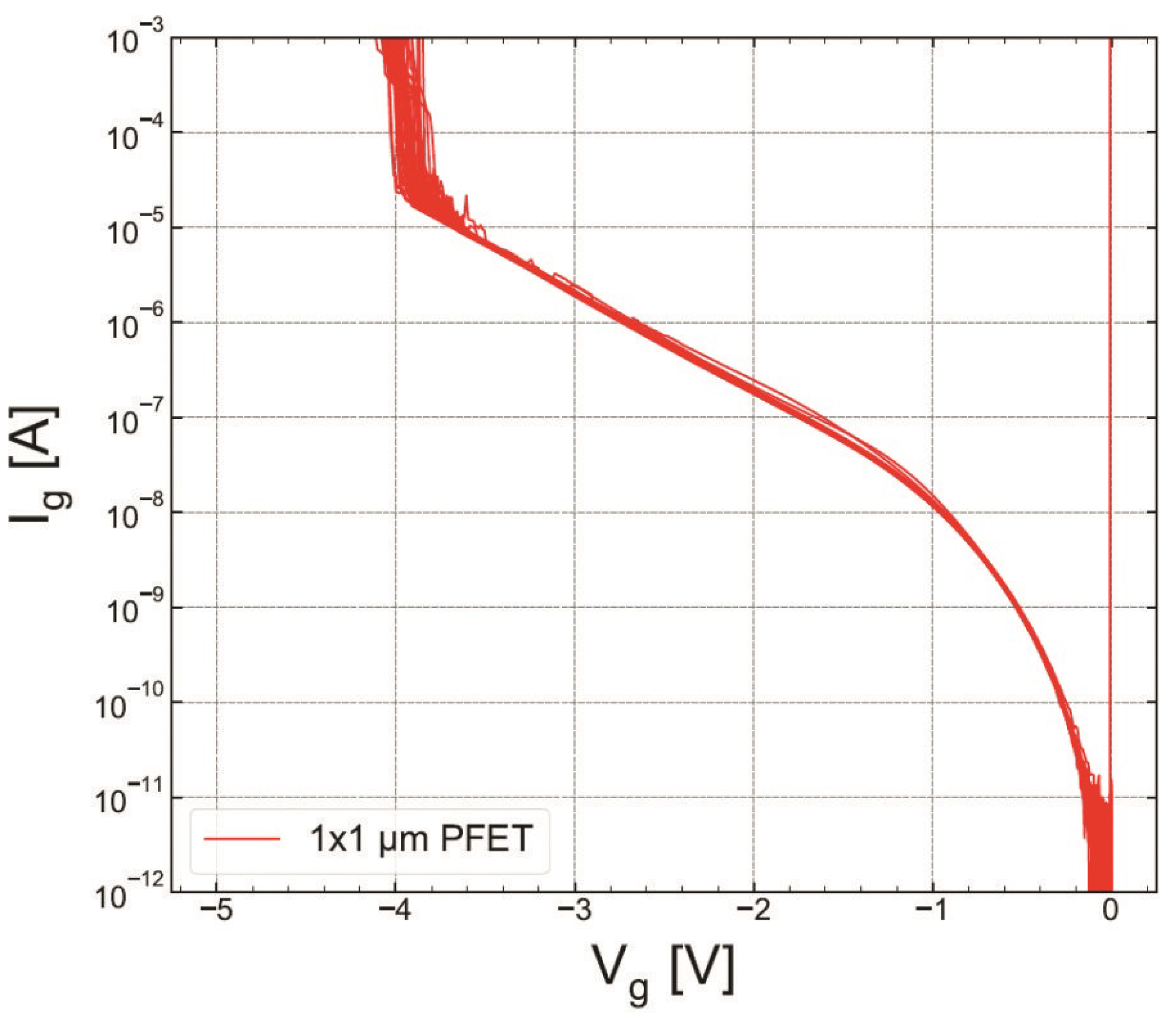

3.2. Hard Breakdown

4. Results and Discussion

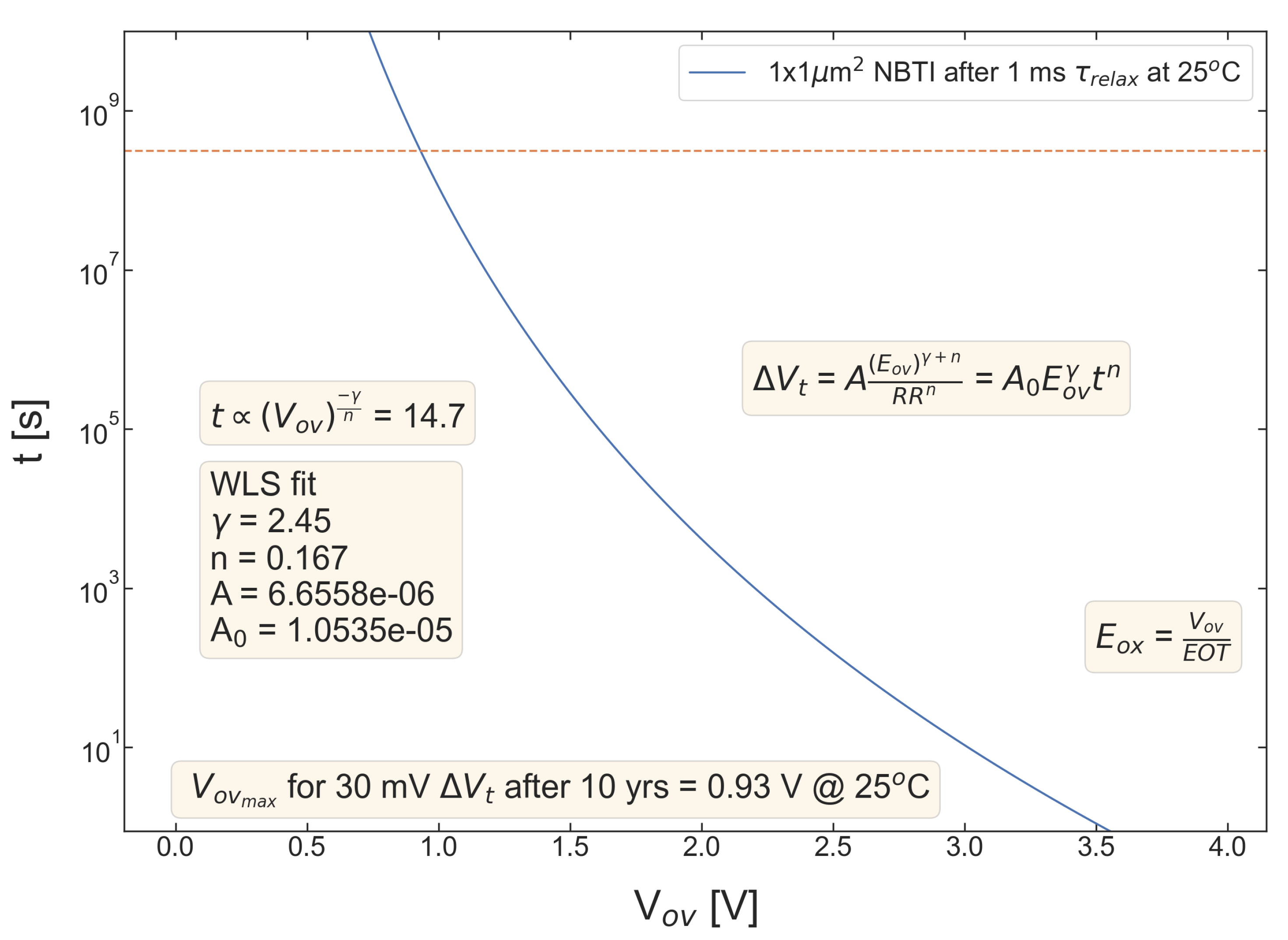

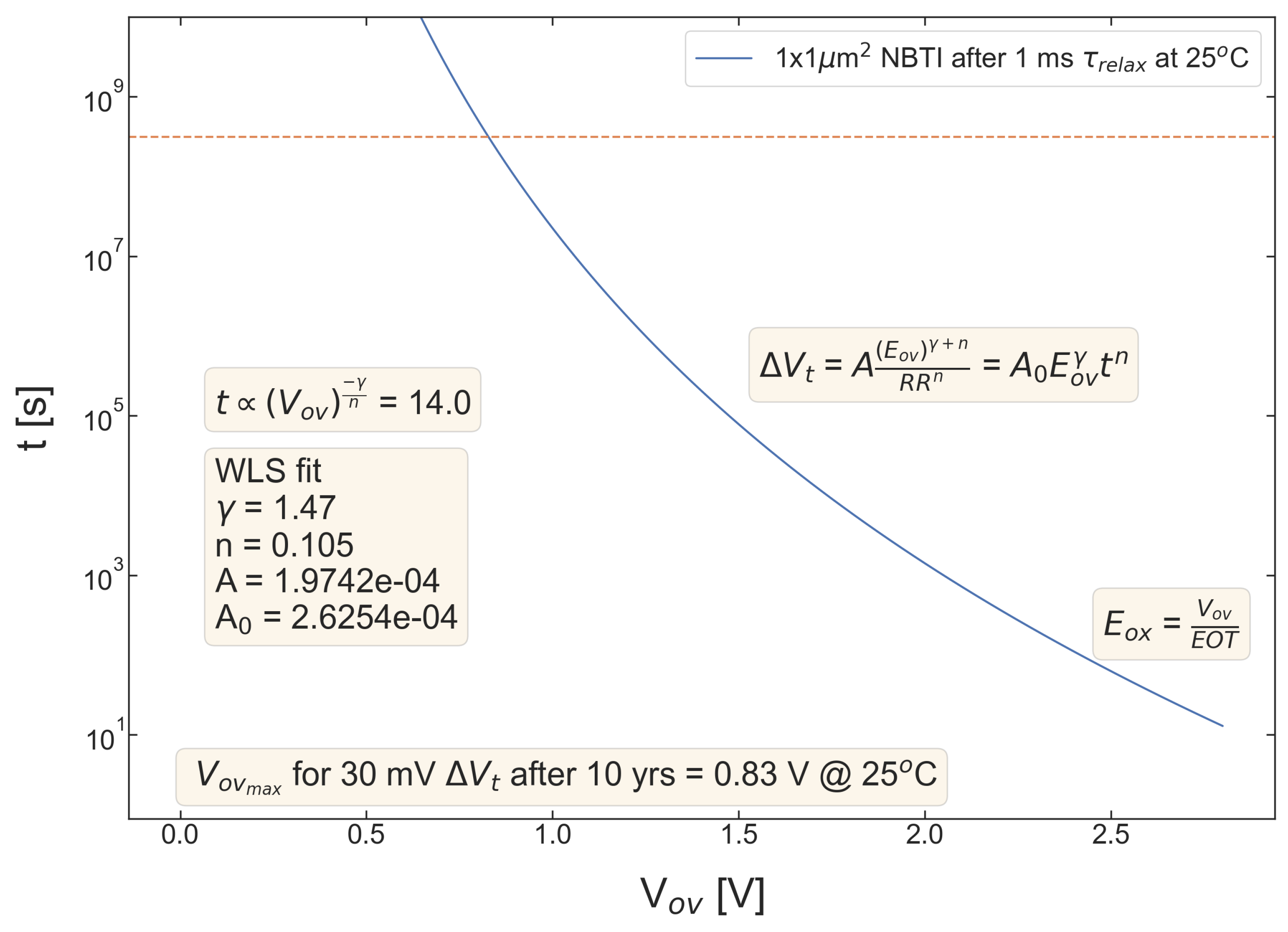

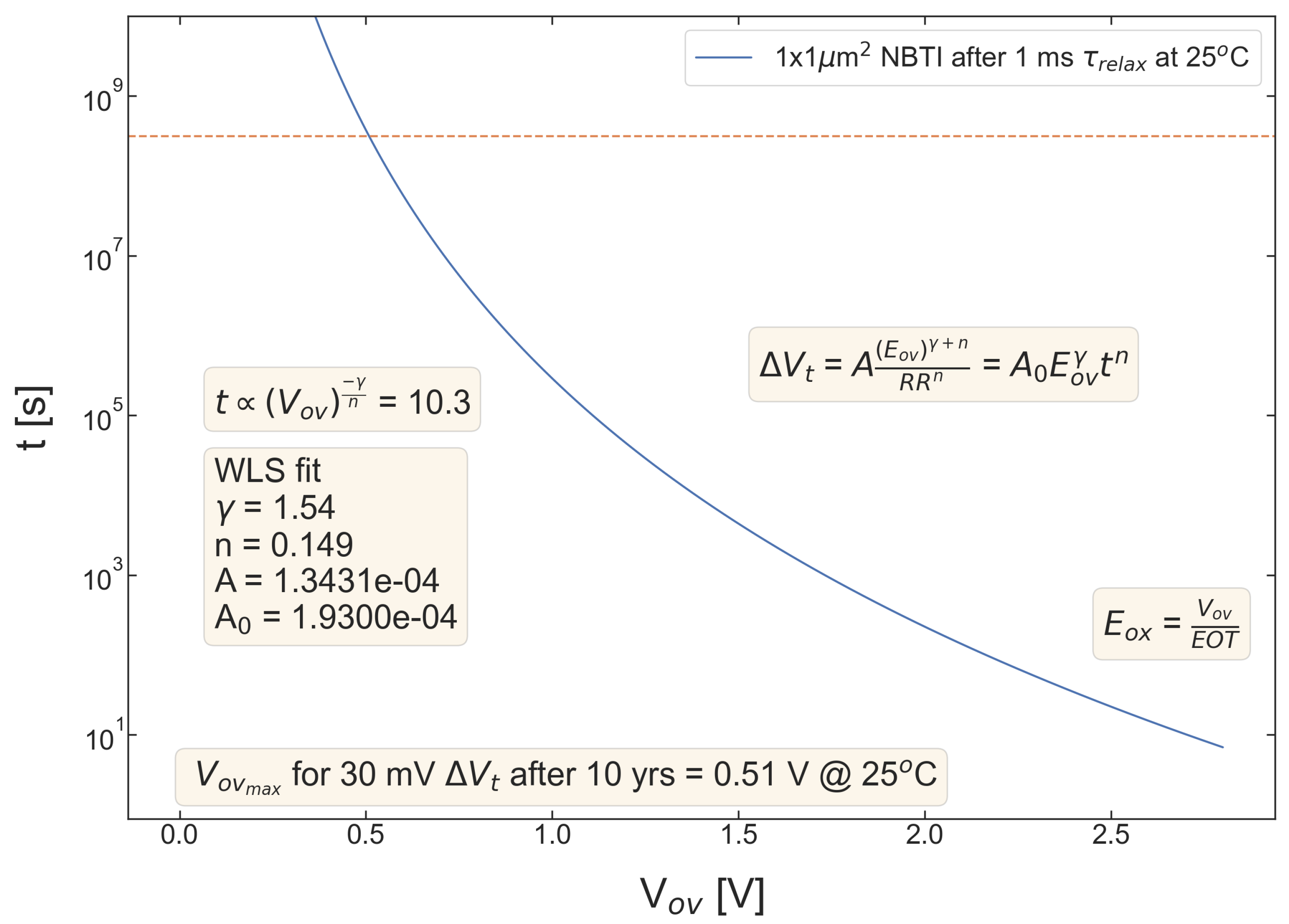

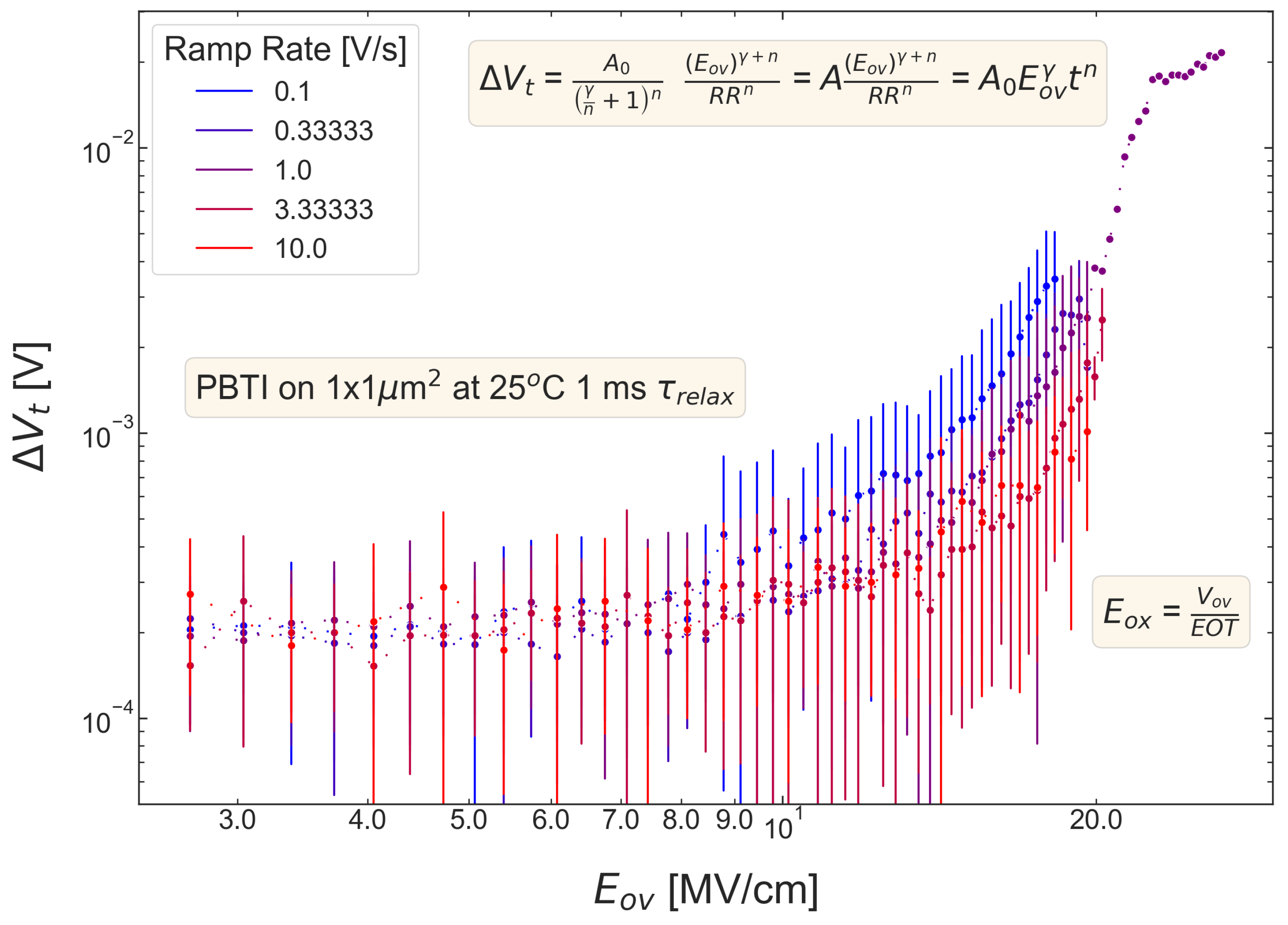

4.1. Bias Temperature Instability

4.2. Hard Breakdown

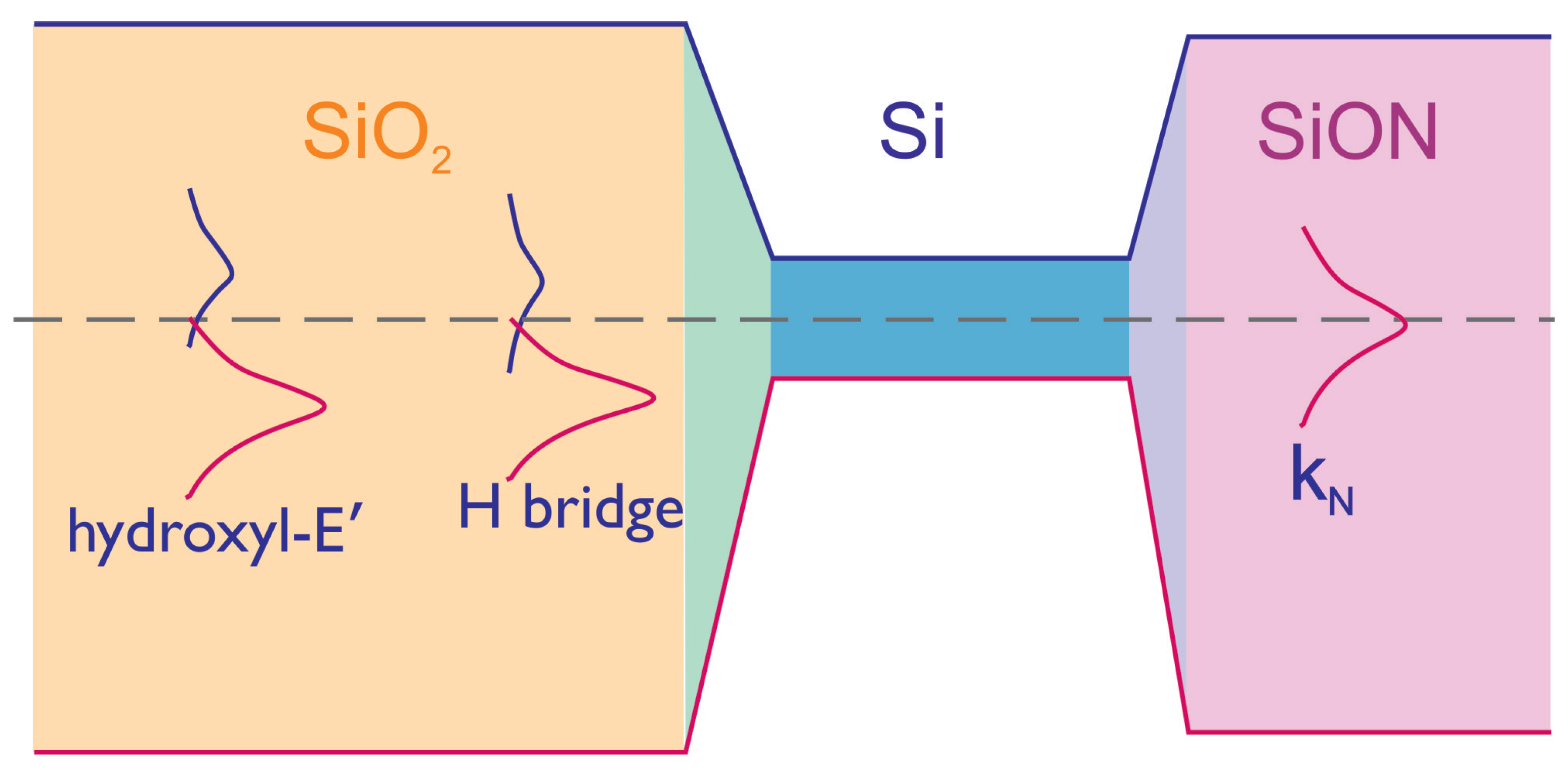

4.3. Interpretation of the Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| BTI | Bias temperature Instability |

| CVS | Constant Voltage Stress |

| eMSM | extended Measure–Stress–Measure (technique) |

| EOL | Equivalent Oxide Thickness |

| HBD | Hard Breakdown |

| HCD | Hot-Carrier Degradation |

| MOSFET | Metal–Oxide–Semiconductor Field Effect Transistor |

| NBTI | Negative Bias Temperature Instability |

| PBTI | Positive Bias Temperature Instability |

| POR | Process of Reference |

| RF | Radio Frequency |

| RVS | Ramped Voltage Stress |

| SN | Soft Nitridation |

| TDDB | Time-Dependent Dielectric Breakdown |

References

- Auth, C.; Allen, C.; Blattner, A.; Bergstrom, D.; Brazier, M.; Bost, M.; Buehler, M.; Chikarmane, V.; Ghani, T.; Glassman, T.; et al. A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors. In Proceedings of the 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 12–14 June 2012; pp. 131–132. [Google Scholar] [CrossRef]

- Ferain, I.; Colinge, C.; Colinge, J.-P. Multigate transistors as the future of classical metal-oxide-semiconductor field-effect transistors. Nature 2011, 479, 310–316. [Google Scholar] [CrossRef] [PubMed]

- Barraud, S.; Lapras, V.; Previtali, B.; Samson, M.P.; Lacord, J.; Martinie, S.; Jaud, M.A.; Athanasiou, S.; Triozon, F.; Rozeau, O.; et al. Performance and design considerations for gate-all-around stacked-NanoWires FETs. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 29.2.1–29.2.4. [Google Scholar] [CrossRef] [Green Version]

- Nagy, D.; Espiñeira, G.; Indalecio, G.; García-Loureiro, A.J.; Kalna, K.; Seoane, N. Benchmarking of FinFET, Nanosheet, and Nanowire FET Architectures for Future Technology Nodes. IEEE Access 2020, 8, 53196–53202. [Google Scholar] [CrossRef]

- Weckx, P.; Ryckaert, J.; Putcha, V.; De Keersgieter, A.; Boemmels, J.; Schuddinck, P.; Jang, D.; Yakimets, D.; Bardon, M.G.; Ragnarsson, L.Å.; et al. Stacked nanosheet fork architecture for SRAM design and device co-optimization toward 3 nm. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 20.5.1–20.5.4. [Google Scholar] [CrossRef]

- Zhang, J.; Frougier, J.; Greene, A.; Miao, X.; Yu, L.; Vega, R.; Montanini, P.; Durfee, C.; Gaul, A.; Pancharatnam, S.; et al. Full Bottom Dielectric Isolation to Enable Stacked Nanosheet Transistor for Low Power and High Performance Applications. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 11.6.1–11.6.4. [Google Scholar] [CrossRef]

- Ritzenthaler, R.; Mertens, H.; Eneman, G.; Simoen, E.; Bury, E.; Eyben, P.; Bufler, F.M.; Oniki, Y.; Briggs, B.; Chan, B.; et al. Comparison of Electrical Performance of Co-Integrated Forksheets and Nanosheets Transistors for the 2 nm Technological Node and Beyond. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–16 December 2021; pp. 26.2.1–26.2.4. [Google Scholar] [CrossRef]

- Ryckaert, J.; Schuddinck, P.; Weckx, P.; Bouche, G.; Vincent, B.; Smith, J.; Sherazi, Y.; Mallik, A.; Mertens, H.; Demuynck, S.; et al. The Complementary FET (CFET) for CMOS scaling beyond N3. In Proceedings of the 2018 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 18–22 June 2018; pp. 141–142. [Google Scholar] [CrossRef]

- Liebmann, L.; Smith, J.; Chanemougame, D.; Gutwin, P. CFET Design Options, Challenges, and Opportunities for 3D Integration. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–16 December 2021; pp. 3.1.1–3.1.4. [Google Scholar] [CrossRef]

- Huard, V.; Denais, M.; Parthasarathy, C. NBTI Degradation: From Physical Mechanisms to Modelling. Microel. Reliab. 2006, 46, 1–23. [Google Scholar] [CrossRef]

- Grasser, T.; Kaczer, B.; Gös, W.; Reisinger, H.; Aichinger, T.; Hehenberger, P.; Wagner, P.J.; Franco, J.; Toledano-Luque, M.; Nelhiebel, M. The Paradigm Shift in Understanding the Bias Temperature Instability: From Reaction-Diffusion to Switching Oxide Traps. IEEE Trans. Electron. Dev. 2011, 58, 3652–3666. [Google Scholar] [CrossRef]

- Degraeve, R.; Groeseneken, G.; Bellens, R.; Ogier, J.L.; Depas, M.; Roussel, P.J.; Maes, H.E. New insights in the relation between electron trap generation and the statistical properties of oxide breakdown. IEEE Trans. Electron. Dev. 1998, 45, 904–911. [Google Scholar] [CrossRef]

- McPherson, J.W.; Khamankar, R.B. Molecular model for intrinsic time-dependent dielectric breakdown in SiO 2 dielectrics and the reliability implications for hyper-thin gate oxide. Semicond. Sci. Technol. 2000, 15, 462. [Google Scholar] [CrossRef]

- Rauch, S.; Rosa, G.L. CMOS Hot Carrier: From Physics to End of Life Projections, and Qualification. In Proceedings of the International Reliability Physics Symposium (IRPS), Garden Grove (Anaheim), CA, USA, 2–6 May 2010. [Google Scholar]

- Bravaix, A.; Huard, V. Hot-Carrier Degradation Issues in Advanced CMOS Nodes. In Proceedings of the European Symposium on Reliability of Electron Devices Failure Physics and Analysis (ESREF), Gaeta, Italy, 11–15 October 2010; pp. 1267–1272. [Google Scholar]

- Tyaginov, S.; Grasser, T. Modeling of hot-carrier degradation: Physics and controversial issues. In Proceedings of the 2012 IEEE International Integrated Reliability Workshop Final Report, South Lake Tahoe, CA, USA, 14–18 October 2012; pp. 206–215. [Google Scholar] [CrossRef]

- Ramey, S.; Ashutosh, A.; Auth, C.; Clifford, J.; Hattendorf, M.; Hicks, J.; James, R.; Rahman, A.; Sharma, V.; Amour, A.S.; et al. Intrinsic transistor reliability improvements from 22 nm tri-gate technology. In Proceedings of the 2013 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 14–18 April 2013; pp. 4C.5.1–4C.5.5. [Google Scholar] [CrossRef]

- Rahman, A.; Dacuna, J.; Nayak, P.; Leatherman, G.; Ramey, S. Reliability Studies of a 10 nm High-performance and Low-power CMOS Technology Featuring 3rd Generation FinFET and 5th Generation HK/MG. In Proceedings of the 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018; pp. 6F.4-1–6F.4-6. [Google Scholar] [CrossRef]

- Bravaix, A.; Guerin, C.; Huard, V.; Roy, D.; Roux, J.; Vincent, E. Hot-carrier Acceleration Factors for Low Power Management in DC-AC Stressed 40 nm NMOS Node at High Temperature. In Proceedings of the International Reliability Physics Symposium (IRPS), Montreal, QC, Canada, 26–30 April 2009; pp. 531–546. [Google Scholar] [CrossRef]

- Guerin, C.; Huard, V.; Bravaix, A. General Framework about Defect Creation at the Si/SiO2 Interface. J. Appl. Phys. 2009, 105, 114513-1–114513-12. [Google Scholar] [CrossRef]

- Tyaginov, S.; Starkov, I.; Triebl, O.; Cervenka, J.; Jungemann, C.; Carniello, S.; Park, J.; Enichlmail, H.; Kernstock, C.; Seebacher, E.; et al. Interface Traps Density-of-states as a Vital Component for Hot-carrier Degradation Modeling. Microelectron. Reliab. 2010, 50, 1267–1272. [Google Scholar] [CrossRef]

- Tyaginov, S.; Starkov, I.; Jungemann, C.; Enichlmair, H.; Park, J.; Grasser, T. Impact of the Carrier Distribution Function on Hot-Carrier Degradation Modeling. In Proceedings of the European Solid-State Device Research Conference (ESSDERC), Helsinki, Finland, 12–16 September 2011; pp. 151–154. [Google Scholar] [CrossRef]

- Tallarico, A.; Reggiani, S.; Magnone, P.; Croce, G.; Depetro, R.; Gattari, P.; Sangiorgi, E.; Fiegna, C. Investigation of the hot carrier degradation in power LDMOS transistors with customized thick oxide. Microelectron. Reliab. 2017, 76–77, 475–479. [Google Scholar] [CrossRef] [Green Version]

- Tallarico, A.N.; Reggiani, S.; Depetro, R.; Torti, A.M.; Croce, G.; Sangiorgi, E.; Fiegna, C. Hot-Carrier Degradation in Power LDMOS: Selective LOCOS- Versus STI-Based Architecture. IEEE J. Electron Devices Soc. 2018, 6, 219–226. [Google Scholar] [CrossRef]

- Joo, M.S.; Yeo, I.S.; Lee, C.H.; Cho, H.J.; Jang, S.A.; Lee, S.K. Effects of nitridation pressure on the characteristics of gate dielectrics annealed in N2O ambient. IEEE Electron Device Lett. 1999, 20, 445–447. [Google Scholar] [CrossRef]

- Mazumder, M.; Teramoto, A.; Komori, J.; Sekine, M.; Kawazu, S.; Mashiko, Y. Effects of N distribution on charge trapping and TDDB characteristics of N/sub 2/O annealed wet oxide. IEEE Trans. Electron Dev. 1999, 46, 1121–1126. [Google Scholar] [CrossRef]

- Chen, Y.; Chien, C.; Lou, J. Dielectric properties of nitric oxide-annealed gate oxides grown on nitrogen-implanted silicon substrates. Thin Solid Films 2006, 513, 264–268. [Google Scholar] [CrossRef]

- Lee, H.; Pilkington, S.J.; Knebel, S.; Voon, H.C.; Loi, C.M.; Ong, M.I.I. The effects of Fluorine implantation and ex-situ Nitrogen anneal on Reliability improvement of 5 V CMOSFETs. In Proceedings of the 2022 IEEE International Conference on Semiconductor Electronics (ICSE), Kuala Lumpur, Malaysia, 15–17 August 2022; pp. 41–44. [Google Scholar] [CrossRef]

- O’Sullivan, B.J.; Ritzenthaler, R.; Dentoni Litta, E.; Simoen, E.; Machkaoutsan, V.; Fazan, P.; Ji, Y.H.; Kim, C.; Spessot, A.; Linten, D.; et al. Overview of Bias Temperature Instability in Scaled DRAM Logic for Memory Transistors. IEEE Trans. Dev. Mater. Reliab. 2020, 20, 258–268. [Google Scholar] [CrossRef]

- O’Connor, R.; Aoulaiche, M.; Pantisano, L.; Shickova, A.; Degraeve, R.; Kaczer, B.; Groeseneken, G. The role of nitrogen in HfSiON defect passivation. In Proceedings of the 2009 IEEE International Reliability Physics Symposium, Montreal, QC, Canada, 26–30 April 2009; pp. 921–924. [Google Scholar] [CrossRef]

- Maheta, V.D.; Olsen, C.; Ahmed, K.; Mahapatra, S. The Impact of Nitrogen Engineering in Silicon Oxynitride Gate Dielectric on Negative-Bias Temperature Instability of p-MOSFETs: A Study by Ultrafast On-The-Fly IDLIN Technique. IEEE Trans. Electron Dev. 2008, 55, 1630–1638. [Google Scholar] [CrossRef]

- Joshi, K.; Hung, S.; Mukhopadhyay, S.; Chaudhary, V.; Nanaware, N.; Rajamohnan, B.; Sato, T.; Bevan, M.; Wei, A.; Noori, A.; et al. HKMG process impact on N, P BTI: Role of thermal IL scaling, IL/HK integration and post HK nitridation. In Proceedings of the 2013 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 14–18 April 2013; pp. 4C.2.1–4C.2.10. [Google Scholar] [CrossRef]

- Garros, X.; Casse, M.; Reimbold, G.; Martin, F.; Leroux, C.; Fanton, A.; Renault, O.; Cosnier, V.; Boulanger, F. Guidelines to improve mobility performances and BTI reliability of advanced high-k/metal gate stacks. In Proceedings of the 2008 Symposium on VLSI Technology, Honolulu, HI, USA, 17–19 June 2008; pp. 68–69. [Google Scholar] [CrossRef]

- Garros, X.; Casse, M.; Fenouillet-Beranger, C.; Reimbold, G.; Martin, F.; Gaumer, C.; Wiemer, C.; Perego, M.; Boulanger, F. Detrimental impact of technological processes on BTI reliability of advanced high-K/metal gate stacks. In Proceedings of the 2009 IEEE International Reliability Physics Symposium, Montreal, QC, Canada, 26–30 April 2009; pp. 362–366. [Google Scholar] [CrossRef]

- Reisinger, H.; Vollertsen, R.P.; Wagner, P.J.; Huttner, T.; Martin, A.; Aresu, S.; Gustin, W.; Grasser, T.; Schlunder, C. A Study of NBTI and Short-Term Threshold Hysteresis of Thin Nitrided and Thick Non-Nitrided Oxides. IEEE Trans. Dev. Mater. Reliab. 2009, 9, 106–114. [Google Scholar] [CrossRef]

- Takasaki, K.; Irino, K.; Aoyama, T.; Momiyama, Y.; Nakanishi, T.; Tamura, Y.; Ito, T. Impact of Nitrogen Profile in Gate Nitrided-Oxide on Deep-Submicron CMOS Performance and Reliability. Fujitsu Sci. Tech. J. 2003, 39, 40–51. [Google Scholar]

- Bury, E.; Chasin, A.; Kaczer, B.; Vandemaele, M.; Tyaginov, S.; Franco, J.; Ritzenthaler, R.; Mertens, H.; Weckx, P.; Horiguchi, N.; et al. Evaluating Forksheet FET Reliability Concerns by Experimental Comparison with Co-integrated Nanosheets. In Proceedings of the 2022 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 27–31 March 2022; pp. 5A.2–1–5A.2–7. [Google Scholar] [CrossRef]

- Vandemaele, M.; Kaczer, B.; Tyaginov, S.; Franco, J.; Bury, E.; Chasin, A.; Makarov, A.; Hellings, G.; Groeseneken, G. Trapping of Hot Carriers in the Forksheet FET Wall: A TCAD Study. IEEE Electron Dev. Lett. 2023, 44, 197–200. [Google Scholar] [CrossRef]

- Hauser, J.R.; Ahmed, K. Characterization of ultra-thin oxides using electrical C-V and I-V measurements. AIP Conf. Proc. 1998, 449, 235–239. [Google Scholar] [CrossRef]

- Kaczer, B.; Franco, J.; Weckx, P.; Roussel, P.J.; Bury, E.; Cho, M.; Degraeve, R.; Linten, D.; Groeseneken, G.; Kukner, H.; et al. The defect-centric perspective of device and circuit reliability—From individual defects to circuits. In Proceedings of the 2015 45th European Solid State Device Research Conference (ESSDERC), Graz, Austria, 14–18 September 2015; pp. 218–225. [Google Scholar]

- Asenov, A. Random Dopant Induced Threshold Voltage Lowering and Fluctuations in sub-0.1 μm MOSFET’s: A 3-D Atomistic Simulation Study. IEEE Trans. Electron. Dev. 1998, 45, 2505–2513. [Google Scholar] [CrossRef] [Green Version]

- Brown, A.R.; Watling, J.R.; Asenov, A.; Bersuker, G.; Zeitzoff, P. Intrinsic Parameter Fluctuations in MOSFETs due to Structural Non-uniformity of High-κ Gate Stack Materials. In Proceedings of the 2005 International Conference On Simulation of Semiconductor Processes and Devices, Tokyo, Japan, 1–3 September 2005; pp. 27–30. [Google Scholar] [CrossRef]

- Brown, A.R.; Watling, J.R.; Asenov, A. Intrinsic Parameter Fluctuations due to Random Grain Orientations in High-κ Gate Stacks. J. Comput. Electron. 2006, 5, 333–336. [Google Scholar] [CrossRef]

- Asenov, A.; Kaya, S.; Davies, J.H. Intrinsic Threshold Voltage fluctuations in Decanano MOSFETs due to Local Oxide Thickness Variations. IEEE Trans. Electron. Dev. 2002, 49, 112–119. [Google Scholar] [CrossRef] [Green Version]

- Tyaginov, S.; Vexler, M.; Shulekin, A.; Grekhov, I. Statistical Analysis of Tunnel Currents in Scaled MOS Structures with a Non-uniform Oxide Thickness Distribution. Solid-State Electron. 2005, 49, 1192–1197. [Google Scholar] [CrossRef]

- Rawat, A.; Harsha Vardhan, P.; Ganguly, U. Nanoscale Transistor Variability Modeling: How Simple Physics Enables a Powerful Prediction Platform. IEEE Nanotechnol. Mag. 2020, 14, 4–16. [Google Scholar] [CrossRef]

- Grasser, T.; Reisinger, H.; Wagner, P.J.; Schanovsky, F.; Goes, W.; Kaczer, B. The Time Dependent Defect Spectroscopy (TDDS) for the Characterization of the Bias Temperature Instability. In Proceedings of the 2010 IEEE International Reliability Physics Symposium, Anaheim, CA, USA, 2–6 May 2010; pp. 16–25. [Google Scholar] [CrossRef]

- Kaczer, B.; Franco, J.; Cho, M.; Grasser, T.; Roussel, P.J.; Tyaginov, S.; Bina, M.; Wimmer, Y.; Procel, L.M.; Trojman, L.; et al. Origins and Implications of Increased Channel hot Carrier Variability in nFinFETs. In Proceedings of the 2015 IEEE International Reliability Physics Symposium, Monterey, CA, USA, 19–23 April 2015; pp. 3B.5.1–3B.5.6. [Google Scholar] [CrossRef] [Green Version]

- Makarov, A.; Kaczer, B.; Chasin, A.; Vandemaele, M.; Bury, E.; Jech, M.; Grill, A.; Hellings, G.; El-Sayed, A.; Grasser, T.; et al. Bi-Modal Variability of nFinFET Characteristics During Hot-Carrier Stress: A Modeling Approach. IEEE Electron Dev. Lett. 2019, 40, 1579–1582. [Google Scholar] [CrossRef]

- Monsieur, F.; Vincent, E.; Ribes, G.; Huard, V.; Bruyere, S.; Roy, D.; Pananakakis, G.; Ghibaudo, G. Evidence for defect-generation-driven wear-out of breakdown conduction path in ultra thin oxides. In Proceedings of the International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 30 March–4 April 2003; pp. 424–431. [Google Scholar] [CrossRef]

- Kerber, A.; Cartier, E.A. Reliability Challenges for CMOS Technology Qualifications with Hafnium Oxide/Titanium Nitride Gate Stacks. IEEE Trans. Dev. Mater. Reliab. 2009, 9, 147–162. [Google Scholar] [CrossRef]

- Kerber, A.; Krishnan, S.A.; Cartier, E.A. Voltage Ramp Stress for Bias Temperature Instability Testing of Metal-Gate/High- k Stacks. IEEE Electron Dev. Lett. 2009, 30, 1347–1349. [Google Scholar] [CrossRef]

- Kaczer, B.; Grasser, T.; Roussel, P.; Martin-Martinez, J.; O’Conner, R.; O’Sillivan, B.; Groeseneken, G. Ubiquitous Relaxation in BTI Stressing New Evaluation and Insights. In Proceedings of the 46th Annual International Reliability Physics Symposium, Phoenix, AZ, USA, 27 April–1 May 2008; pp. 20–27. [Google Scholar] [CrossRef]

- Degraeve, R.; Groeseneken, G.; Bellens, R.; Depas, M.; Maes, H.E. A consistent model for the thickness dependence of intrinsic breakdown in ultra-thin oxides. In Proceedings of the International Electron Devices Meeting, Washington, DC, USA, 10–13 December 1995; pp. 863–866. [Google Scholar] [CrossRef]

- Monsieur, F.; Vincent, E.; Pananakakis, G.; Ghibaudo, G. Wear-out, breakdown occurrence and failure detection in 18–25 A ultrathin oxides. Microelectron. Reliab. 2001, 41, 1035–1039. [Google Scholar] [CrossRef]

- Monsieur, F.; Vincent, E.; Roy, D.; Bruyere, S.; Vildeuil, J.; Pananakakis, G.; Ghibaudo, G. A Thorough Investigation of Progressive Breakdown in Ultra-thin Oxides. Physical Understanding and Application for Industrial Reliability Assessment. In Proceedings of the International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 7–11 April 2002; pp. 45–54. [Google Scholar] [CrossRef]

- Kim, A.; Wu, E.; Li, B.; Linder, B. Transformation of Ramped Current Stress VBDto Constant Voltage Stress TDDB TBD. In Proceedings of the 2019 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 31 March–4 April 2019; pp. 1–5. [Google Scholar] [CrossRef]

- Benard, A. Het Uitzetten van Waarneningen op Waarschijunlijkdeid Papier (The Plotting of Observations or Probability Paper). Stat. Neerl. 1953, 7, 163–173. [Google Scholar] [CrossRef] [Green Version]

- Cartier, E.; DiMaria, D. Hot-Electron Dynamics in SiO2 and the Degradation of the Si/SiO2-interface. Microelectron. Eng. 1993, 22, 207–210. [Google Scholar] [CrossRef]

- DiMaria, D.J.; Cartier, E.; Arnold, D. Impact ionization, trap creation, degradation, and breakdown in silicon dioxide films on silicon. J. Appl. Phys. 1993, 73, 3367–3384. [Google Scholar] [CrossRef]

- Bastos, J.P.; O’Sullivan, B.J.; Franco, J.; Tyaginov, S.; Truijen, B.; Chasin, A.; Degraeve, R.; Kaczer, B.; Ritzenthaler, R.; Capogreco, E.; et al. Bias Temperature Instability (BTI) of High-Voltage Devices for Memory Periphery. In Proceedings of the 2022 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 27–31 March 2022; pp. 1–6. [Google Scholar] [CrossRef]

- Rzepa, G.; Franco, J.; O’Sullivan, B.; Subirats, A.; Simicic, M.; Hellings, G.; Weckx, P.; Jech, M.; Knobloch, T.; Waltl, M.; et al. Comphy—A compact-physics framework for unified modeling of BTI. Microelectron. Reliab. 2018, 85, 49–65. [Google Scholar] [CrossRef]

- Wimmer, Y.; El-Sayed, A.M.; Gös, W.; Grasser, T.; Shluger, A.L. Role of Hydrogen in Volatile Behaviour of Defects in SiO2-Based Electronic Devices. Proc. R. Soc. Lond. A Math. Phys. Eng. Sci. 2016, 472, 20160009. [Google Scholar] [CrossRef]

- Michl, J. Charge Trapping and Variability in CMOS Technologies at Cryogenic Temperatures. Ph.D. Thesis, University of Vienna, Wien, Austria, 2022. [Google Scholar]

- Campbell, J.; Lenahan, P.; Krishnan, A.; Krishnan, S. NBTI: An Atomic-Scale Defect Perspective. In Proceedings of the International Reliability Physics Symposium (IRPS), San Jose, CA, USA, 26–30 March 2006; pp. 442–447. [Google Scholar] [CrossRef]

- Campbell, J.P.; Lenahan, P.M.; Krishnan, A.T.; Krishnan, S. Identification of atomic-scale defect structure involved in the negative bias temperature instability in plasma-nitrided devices. Appl. Phys. Lett. 2007, 91, 133507. [Google Scholar] [CrossRef]

- Campbell, J.; Lenahan, P.; Krishnan, A.; Krishnan, S. Location, Structure, and Density of States of NBTI-Induced Defects in Plasma Nitrided pMOSFETs. In Proceedings of the 2007 IEEE International Reliability Physics Symposium Proceedings. 45th Annual, Phoenix, AZ, USA, 15–19 April 2007; pp. 503–510. [Google Scholar] [CrossRef]

- Reisinger, H.; Grasser, T.; Hofmann, K.; Gustin, W.; Schlünder, C. The impact of recovery on BTI reliability assessments. In Proceedings of the 2010 IEEE International Integrated Reliability Workshop Final Report, South Lake Tahoe, CA, USA, 17–21 October 2010; pp. 12–16. [Google Scholar] [CrossRef]

- Padovani, A.; Gao, D.Z.; Shluger, A.L.; Larcher, L. A Microscopic Mechanism of Dielectric Breakdown in SiO2 Films: An Insight from Multi-scale Modeling. J. Appl. Phys. 2017, 121, 155101. [Google Scholar] [CrossRef] [Green Version]

- Padovani, A.; Torraca, P.L.; Strand, J.; Shluger, A.; Milo, V.; Larcher, L. Towards a Universal Model of Dielectric Breakdown. In Proceedings of the 2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 26–30 March 2023; pp. 1–8. [Google Scholar] [CrossRef]

| Sample | Details | EOT, nMOS | EOT, pMOS | , nMOS | , pMOS | N Content Rank |

|---|---|---|---|---|---|---|

| S #1 | POR | 1.48 nm | 1.37 nm | 0.23 V | −0.22 V | 3 |

| S #2 | SN | 1.54 nm | 1.48 nm | 0.28 V | −0.17 V | 1 |

| S #3 | POR + 2 Å | 1.78 nm | 1.66 nm | 0.29 V | −0.20 V | 2 |

| S #4 | SN − 2 Å | 1.49 nm | 1.34 nm | 0.13 V | −0.27 V | 4 |

| S #5 | SN − 2 Å | 1.47 nm | 1.28 nm | 0.13 V | −0.27 V | 4 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tyaginov, S.; O’Sullivan, B.; Chasin, A.; Rawal, Y.; Chiarella, T.; de Carvalho Cavalcante, C.T.; Kimura, Y.; Vandemaele, M.; Ritzenthaler, R.; Mitard, J.; et al. Impact of Nitridation on Bias Temperature Instability and Hard Breakdown Characteristics of SiON MOSFETs. Micromachines 2023, 14, 1514. https://doi.org/10.3390/mi14081514

Tyaginov S, O’Sullivan B, Chasin A, Rawal Y, Chiarella T, de Carvalho Cavalcante CT, Kimura Y, Vandemaele M, Ritzenthaler R, Mitard J, et al. Impact of Nitridation on Bias Temperature Instability and Hard Breakdown Characteristics of SiON MOSFETs. Micromachines. 2023; 14(8):1514. https://doi.org/10.3390/mi14081514

Chicago/Turabian StyleTyaginov, Stanislav, Barry O’Sullivan, Adrian Chasin, Yaksh Rawal, Thomas Chiarella, Camila Toledo de Carvalho Cavalcante, Yosuke Kimura, Michiel Vandemaele, Romain Ritzenthaler, Jerome Mitard, and et al. 2023. "Impact of Nitridation on Bias Temperature Instability and Hard Breakdown Characteristics of SiON MOSFETs" Micromachines 14, no. 8: 1514. https://doi.org/10.3390/mi14081514