Origin of the High Density of Oxygen Vacancies at the Back Channel of Back-Channel-Etched a-InGaZnO Thin-Film Transistors

Abstract

:1. Introduction

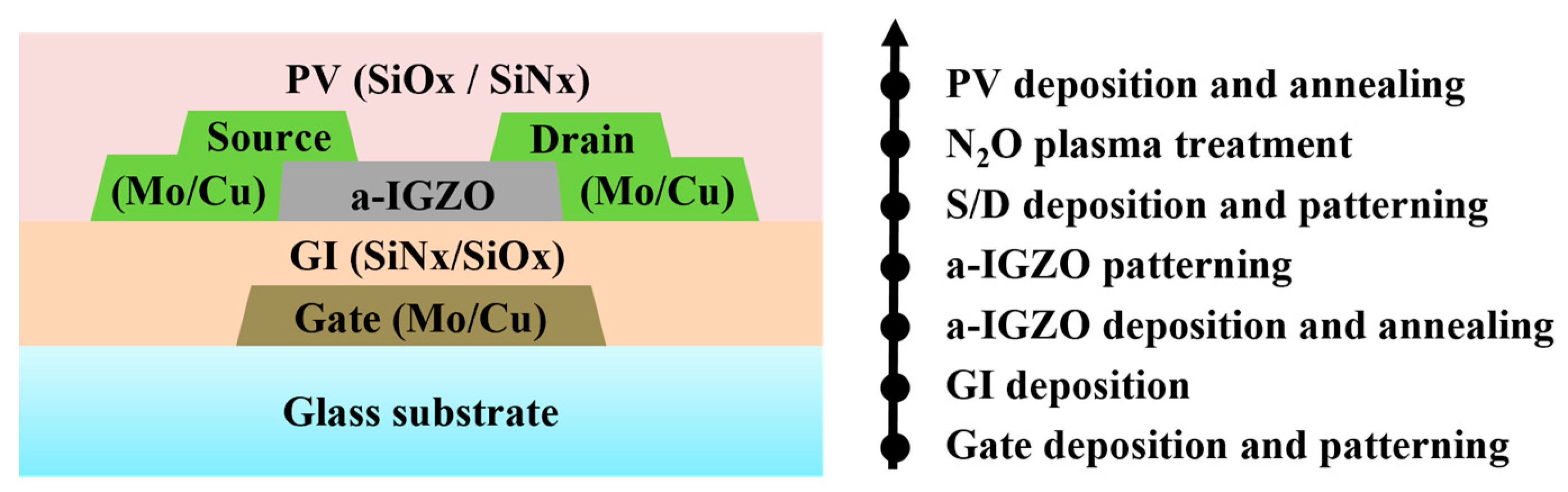

2. Materials and Methods

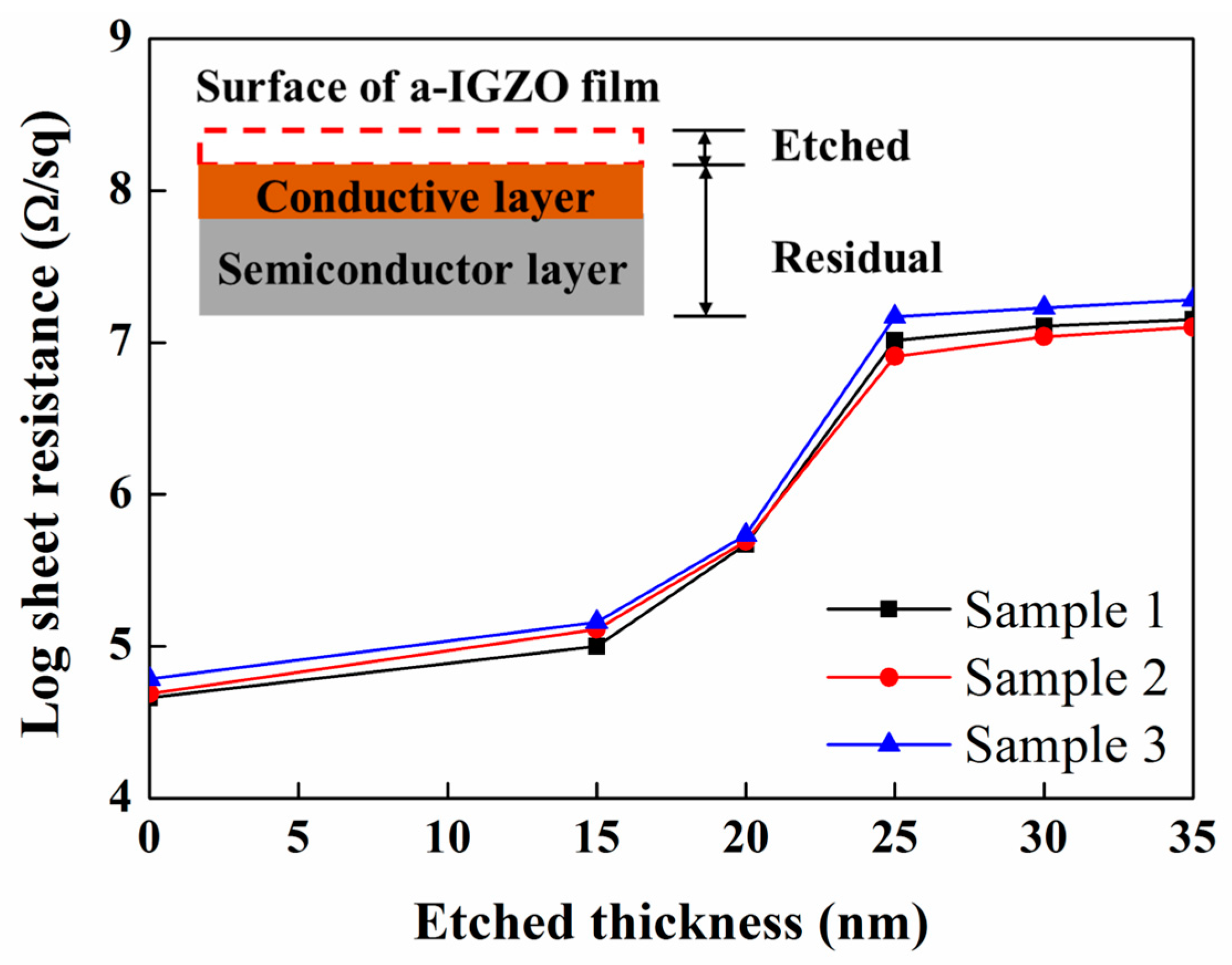

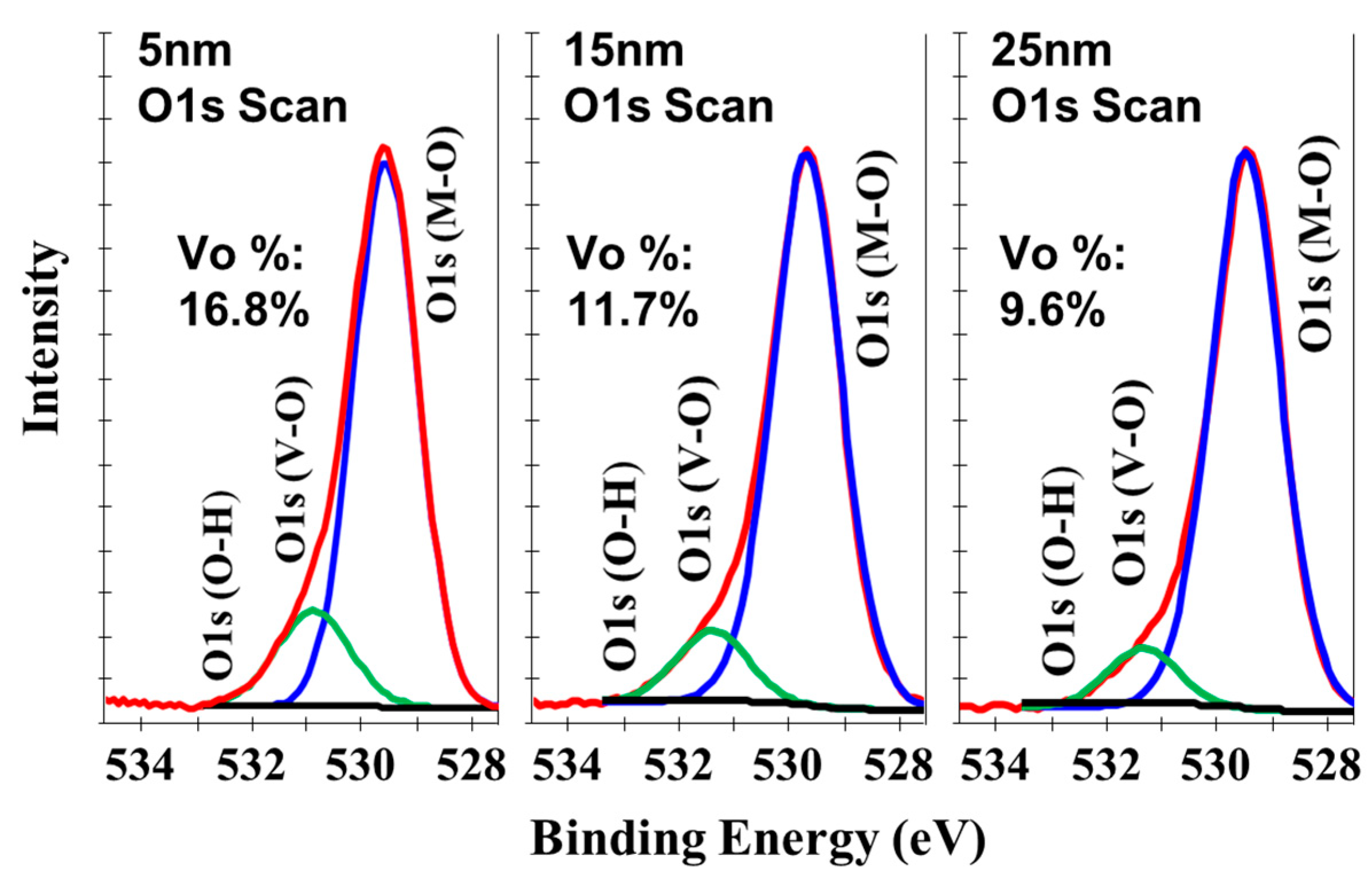

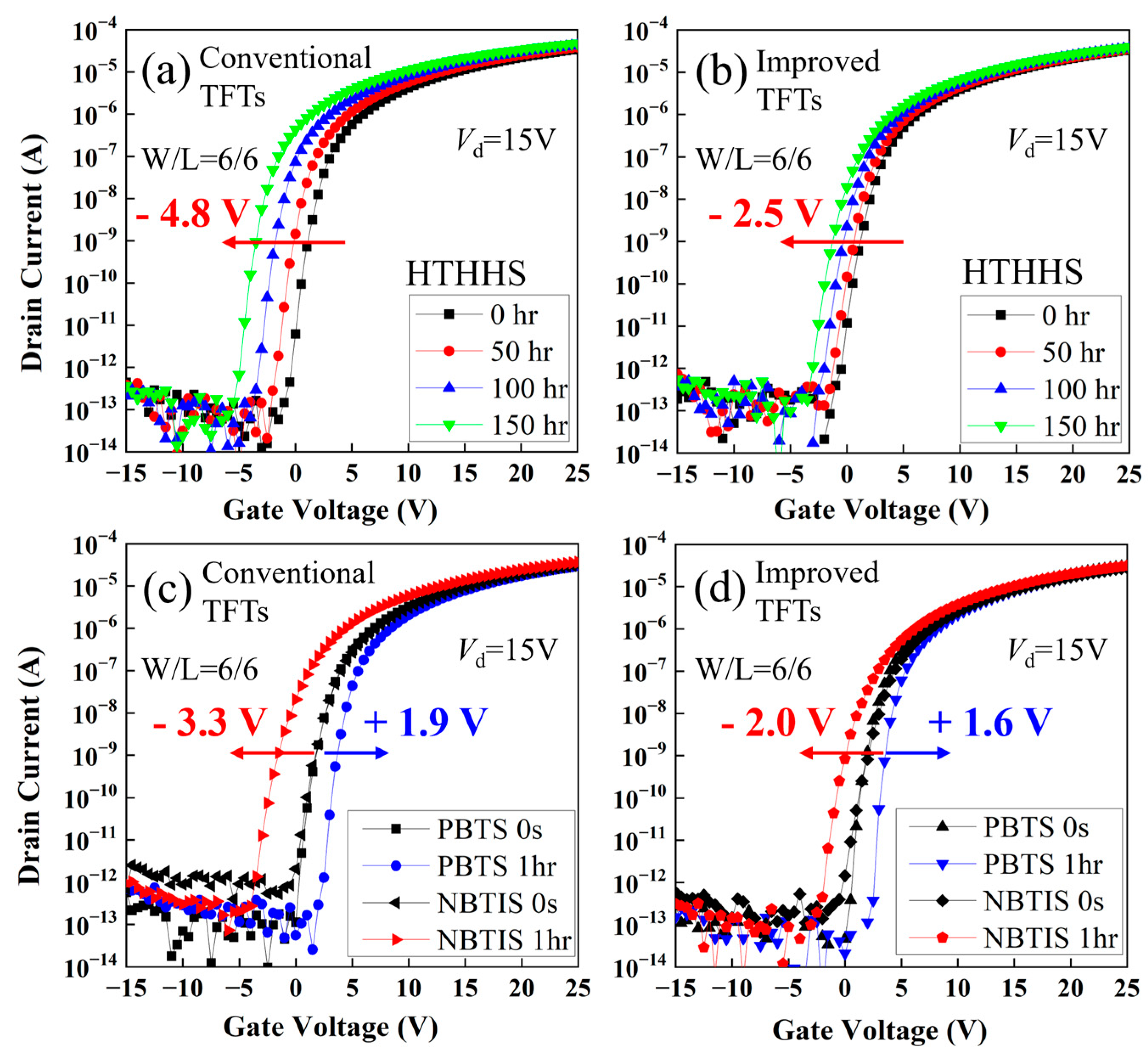

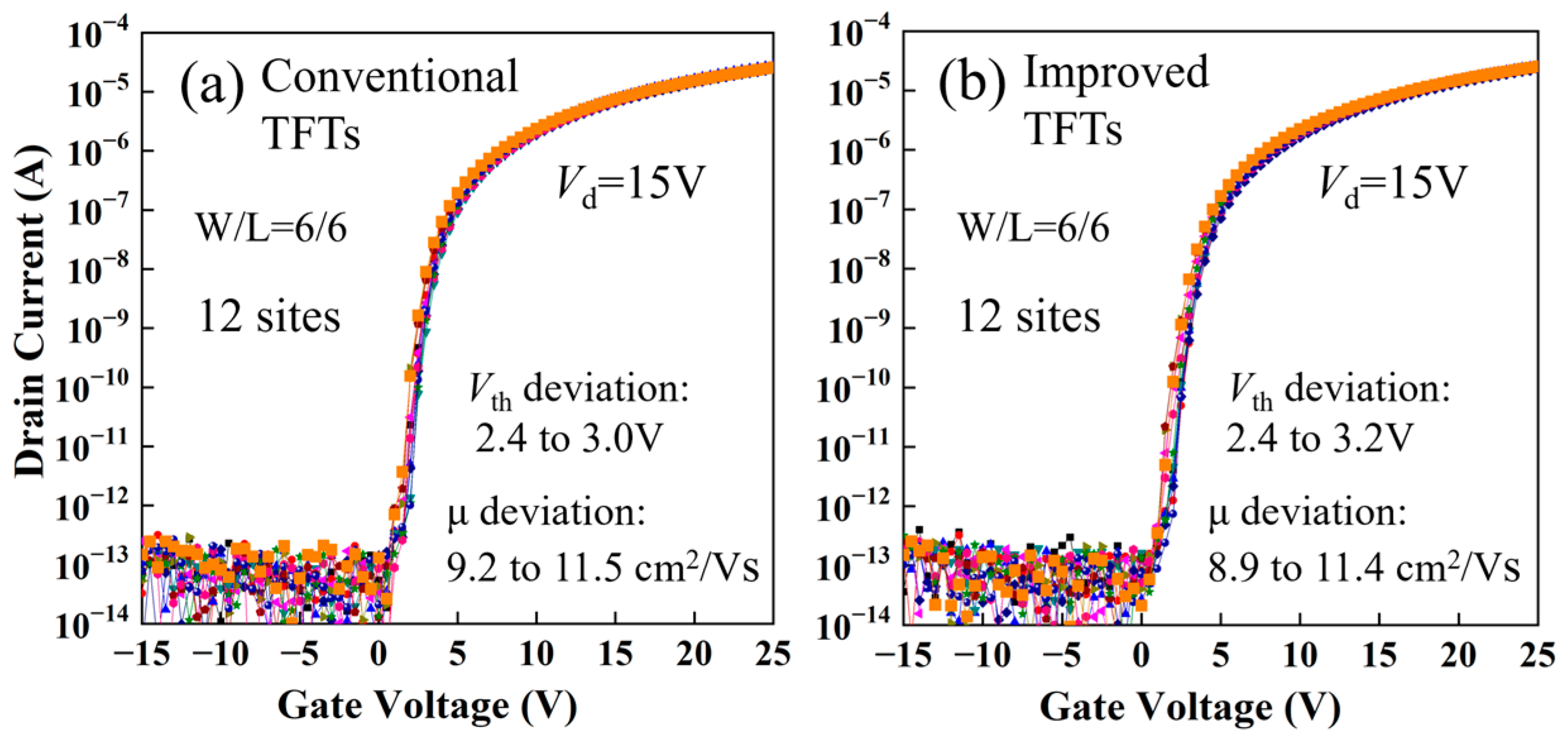

3. Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Kamiya, T.; Nomura, K.; Hosono, H. Present status of amorphous In-Ga-Zn-O thin-film transistors. Sci. Technol. Adv. Mater. 2010, 11, 044305. [Google Scholar] [CrossRef]

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 2004, 432, 488–492. [Google Scholar] [CrossRef]

- Fortunato, E.; Barquinha, P.; Martins, R. Oxide semiconductor thin-film transistors: A review of recent advances. Adv. Mater. 2012, 24, 2945–2986. [Google Scholar] [CrossRef] [PubMed]

- Xiao, X.; Zhang, L.; Shao, Y.; Zhou, X.; He, H.; Zhang, S. Room-Temperature-Processed Flexible Amorphous InGaZnO Thin Film Transistor. ACS Appl. Mater. Interfaces 2018, 10, 25850–25857. [Google Scholar] [CrossRef]

- Song, J.H.; Kwon, D.J.; Kim, S.G.; Roh, N.S.; Park, H.S.; Park, Y.B.; Kim, D.G.; Jeong, C.O.; Kong, H.S.; Kim, C.W.; et al. Advanced four-mask process architecture for the a-Si TFT array manufacturing method. SID Symp. Dig. Tech. Pap. 2002, 33, 1038–1041. [Google Scholar] [CrossRef]

- Ryu, S.H.; Park, Y.C.; Mativenga, M.; Kang, D.H.; Jang, J. Amorphous-InGaZnO4 thin-film transistors with damage-free back channel wet-etch process. ECS Solid State Lett. 2012, 1, Q17–Q19. [Google Scholar] [CrossRef]

- Bae, J.U.K.; Kim, D.H.; Kim, K.; Jung, K.; Shin, W.; Kang, I.; Yeo, S.D. Development of oxide TFT’s structures. SID Symp. Dig. Tech. Pap. 2013, 44, 89–92. [Google Scholar] [CrossRef]

- Zhao, M.; Lan, L.; Xu, H.; Xu, M.; Li, M.; Luo, D.; Wang, L.; Wen, S.; Peng, J. Wet-etch method for patterning metal electrodes directly on amorphous oxide semiconductor films. ECS Solid State Lett. 2012, 1, P82–P84. [Google Scholar] [CrossRef]

- Shin, D.-C.; Park, K.-S.; Park, B.-R.; Choe, H.-H.; Jeon, J.-H.; Lee, K.-W.; Seo, J.-H. A study on the dry etching characteristics of indium gallium zinc oxide and molybdenum by the CCP-RIE system for the 4 mask process. Curr. Appl. Phys. 2011, 11, S45–S48. [Google Scholar] [CrossRef]

- Sung, S.-Y.; Choi, J.H.; Han, U.B.; Lee, K.C.; Lee, J.-H.; Kim, J.-J.; Lim, W.; Pearton, S.J.; Norton, D.P.; Heo, Y.-W. Effects of ambient atmosphere on the transfer characteristics and gate-bias stress stability of amorphous indium gallium zinc oxide thin-film transistors. Appl. Phys. Lett. 2010, 96, 102107. [Google Scholar] [CrossRef]

- Chung, W.-F.; Chang, T.-C.; Li, H.-W.; Chen, C.-W.; Chen, Y.-C.; Chen, S.-C.; Tseng, T.-Y.; Tai, Y.-H. Influence of H2O dipole on subthreshold swing of amorphous indium-gallium-zinc-oxide thin film transistors. Electrochem. Solid-State Lett. 2011, 14, H114–H116. [Google Scholar] [CrossRef]

- Jeong, J.K.; Yang, H.W.; Jeong, J.H.; Mo, Y.-G.; Kim, H.D. Origin of threshold voltage instability in indium-gallium-zinc oxide thin film transistors. Appl. Phys. Lett. 2008, 93, 12. [Google Scholar] [CrossRef]

- Zhou, X.; Shao, Y.; Zhang, L.; Lu, H.; He, H.; Han, D.; Wang, Y.; Zhang, S. Oxygen Interstitial Creation in a-IGZO Thin-Film Transistors under Positive Gate-Bias Stress. IEEE Electron Device Lett. 2017, 38, 1252–1255. [Google Scholar] [CrossRef]

- Chowdhury, M.D.H.; Migliorato, P.; Jang, J. Light induced instabilities in amorphous indium-gallium-zinc-oxide thin-film transistors. Appl. Phys. Lett. 2010, 97, 173506. [Google Scholar] [CrossRef]

- Ryu, B.; Noh, H.-K.; Choi, E.-A.; Chang, K.J. O-vacancy as the origin of negative bias illumination stress instability in amorphous In-Ga-Zn-O thin film transistors. Appl. Phys. Lett. 2010, 97, 022108. [Google Scholar] [CrossRef]

- Lee, K.-H.; Jung, J.S.; Son, K.S.; Park, J.S.; Kim, T.S.; Choi, R.; Jeong, J.K.; Kwon, J.-Y.; Koo, B.; Lee, S. The effect of moisture on the photon-enhanced negative bias thermal instability in Ga–In–Zn–O thin film transistors. Appl. Phys. Lett. 2009, 95, 232106. [Google Scholar] [CrossRef]

- Park, J.; Kim, S.; Kim, C.; Kim, S.; Song, I.; Yin, H.; Kim, K.-K.; Lee, S.; Hong, K.; Lee, J.; et al. High-performance amorphous gallium indium zinc oxide thin-film transistors through N2O plasma passivation. Appl. Phys. Lett. 2008, 93, 053505. [Google Scholar] [CrossRef]

- Liu, X.; Wang, L.L.; Hu, H.; Lu, X.; Wang, K.; Wang, G.; Zhang, S. Performance and stability improvements of back-channel-etched amorphous indium–gallium–zinc thin-film-transistors by CF4+O2 plasma treatment. IEEE Electron. Device Lett. 2015, 36, 911–913. [Google Scholar] [CrossRef]

- Park, Y.C.; Um, J.G.; Mativenga, M.; Jang, J. Enhanced operation of back-channel-etched a-IGZO TFTs by fluorine treatment during source/drain wet-etching. ECS J. Solid State Sci. Technol. 2017, 6, P300–P303. [Google Scholar] [CrossRef]

- Li, W.; Yang, L.; Gao, Z.; Ren, J.; Hu, P.; Li, T.; Liang, L.; Cao, H. Impact of the Source/Drain Electrode Process on the Mobility-Threshold Trade-Off for InSnZnO Thin-Film Transistors. ACS Appl. Electron. Mater. 2023, 5, 1615–1619. [Google Scholar] [CrossRef]

- Park, S.Y.; Song, J.H.; Lee, C.-K.; Son, B.G.; Lee, C.-K.; Kim, H.J.; Choi, R.; Choi, Y.J.; Kim, U.K.; Hwang, C.S.; et al. Improvement in photo-bias stability of high-mobility indium zinc oxide thin-film transistors by oxygen high-pressure annealing. IEEE Electron. Device Lett. 2013, 34, 894–896. [Google Scholar] [CrossRef]

- Park, J.C.; Ahn, S.-E.; Lee, H.-N. High-performance low-cost back-channel-etch amorphous gallium–indium–zinc oxide thin-film transistors by curing and passivation of the damaged back channel. ACS Appl. Mater. Interfaces 2013, 5, 12262–12267. [Google Scholar] [CrossRef]

- Choi, S.-H.; Han, M.-K. Effect of deposition temperature of SiOx passivation layer on the electrical performance of a-IGZO TFTs. IEEE Electron. Device Lett. 2012, 33, 396–398. [Google Scholar] [CrossRef]

- Park, J.; Song, I.; Kim, S.; Kim, S.; Kim, C.; Lee, J.; Lee, H.; Lee, E.; Yin, H.; Kim, K.-K.; et al. Self-aligned top-gate amorphous gallium indium zinc oxide thin film transistors. Appl. Phys. Lett. 2008, 93, 053501. [Google Scholar] [CrossRef]

- Yang, H.; Zhou, X.; Fu, H.; Chang, B.; Min, Y.; Peng, H.; Lu, L.; Zhang, S. Metal reaction-induced bulk-doping effect in forming conductive source-drain regions of self-aligned top-gate amorphous InGaZnO thin-film transistors. ACS Appl. Mater. Interfaces 2021, 13, 11442–11448. [Google Scholar] [CrossRef] [PubMed]

- Omura, H.; Kumomi, H.; Nomura, K.; Kamiya, T.; Hirano, M.; Hosono, H. First-principles study of native point defects in crystalline indium gallium zinc oxide. J. Appl. Phys. 2009, 105, 093712-1–093712-8. [Google Scholar] [CrossRef]

- Li, H.; Guo, Y.; Robertson, J. Hydrogen and the light-induced bias instability mechanism in amorphous oxide semiconductors. Sci. Rep. 2017, 7, 16858. [Google Scholar] [CrossRef]

- Bang, J.; Matsuishi, S.; Hosono, H. Hydrogen anion and subgap states in amorphous In-Ga-Zn-O thin films for TFT applications. Appl. Phys. Lett. 2017, 110, 232105. [Google Scholar] [CrossRef]

- Kang, Y.; Ahn, B.D.; Song, J.H.; Mo, Y.G.; Nahm, H.-H.; Han, S.; Jeong, J.K. Hydrogen Bistability as the Origin of Photo-Bias-Thermal Instabilities in Amorphous Oxide Semiconductors. Adv. Electron. Mater. 2015, 1, 1400006. [Google Scholar] [CrossRef]

- Oh, H.; Yoon, S.-M.; Ryu, M.K.; Hwang, C.-S.; Yang, S.; Park, S.-H.K. Photon-accelerated negative bias instability involving subgap states creation in amorphous In-Ga-Zn-O thin film transistor. Appl. Phys. Lett. 2010, 97, 183502. [Google Scholar] [CrossRef]

| Film | Process | Rs | ||

|---|---|---|---|---|

| IGZO Annealing | S/D Sputtering | S/D Wet Etching | Log Rs (Ω/sq) | |

| film-1 | √ | × | × | ~9 |

| film-2 | √ | × | F-free | ~9 |

| film-3 | √ | × | F-containing | ~9 |

| film-4 | √ | √ | F-free | ~4 |

| film-5 | √ | √ | F-containing | ~7 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ge, S.; Xiao, J.; Li, S.; Yuan, D.; Dong, Y.; Zhang, S. Origin of the High Density of Oxygen Vacancies at the Back Channel of Back-Channel-Etched a-InGaZnO Thin-Film Transistors. Micromachines 2024, 15, 400. https://doi.org/10.3390/mi15030400

Ge S, Xiao J, Li S, Yuan D, Dong Y, Zhang S. Origin of the High Density of Oxygen Vacancies at the Back Channel of Back-Channel-Etched a-InGaZnO Thin-Film Transistors. Micromachines. 2024; 15(3):400. https://doi.org/10.3390/mi15030400

Chicago/Turabian StyleGe, Shimin, Juncheng Xiao, Shan Li, Dong Yuan, Yuhua Dong, and Shengdong Zhang. 2024. "Origin of the High Density of Oxygen Vacancies at the Back Channel of Back-Channel-Etched a-InGaZnO Thin-Film Transistors" Micromachines 15, no. 3: 400. https://doi.org/10.3390/mi15030400