A High-Performance Digital Interface Circuit for a High-Q Micro-Electromechanical System Accelerometer

Abstract

:1. Introduction

2. Materials and Methods

2.1. Materials

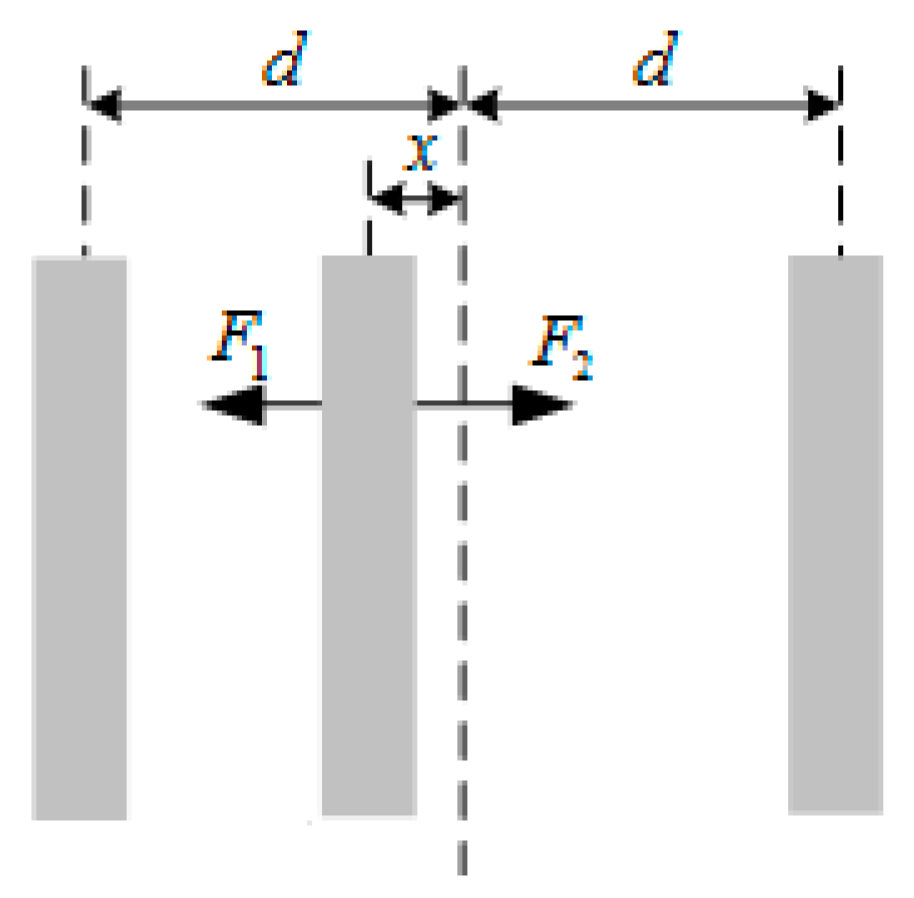

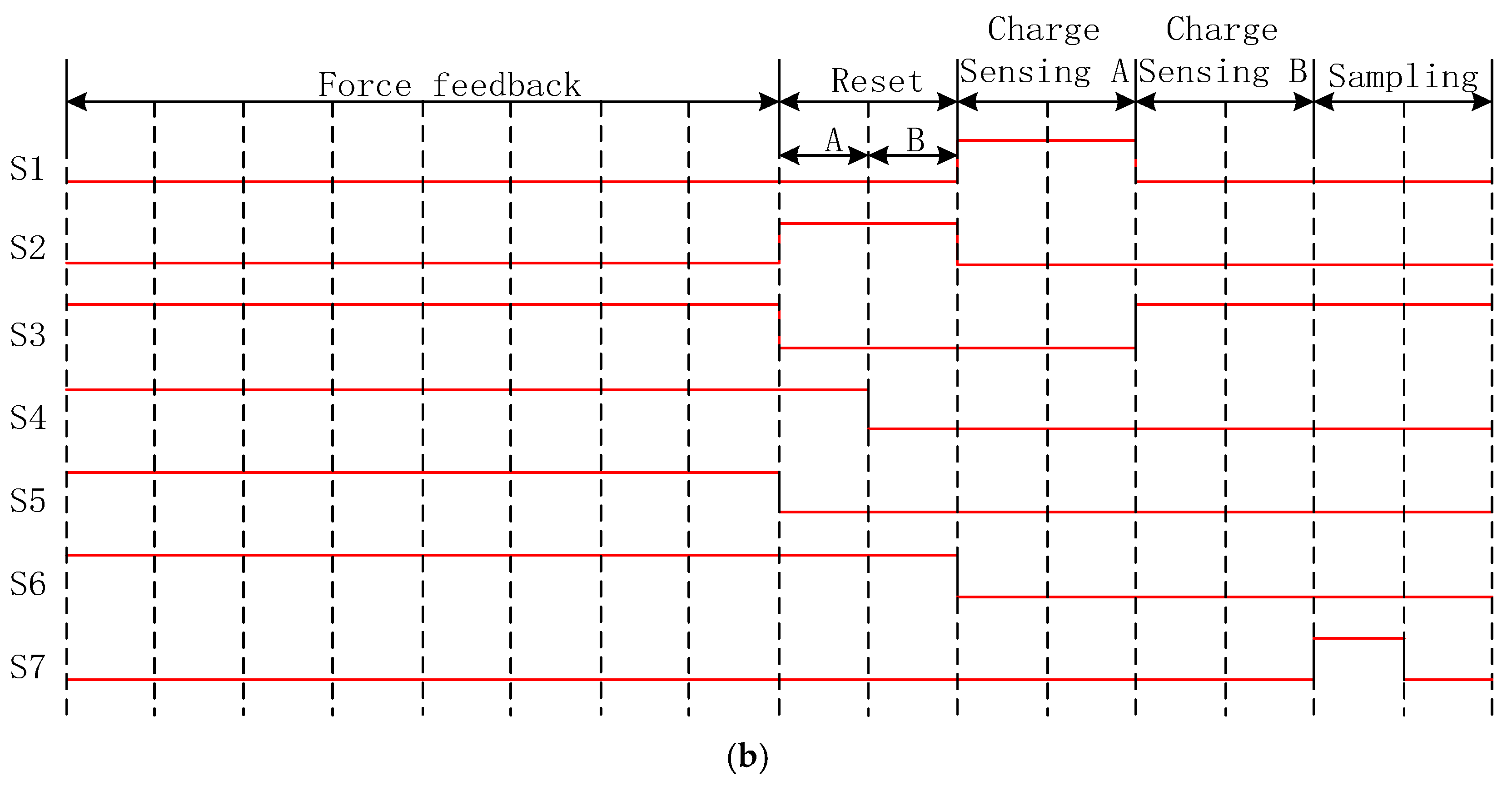

2.2. High-Q Accelerometer Sensitive Element

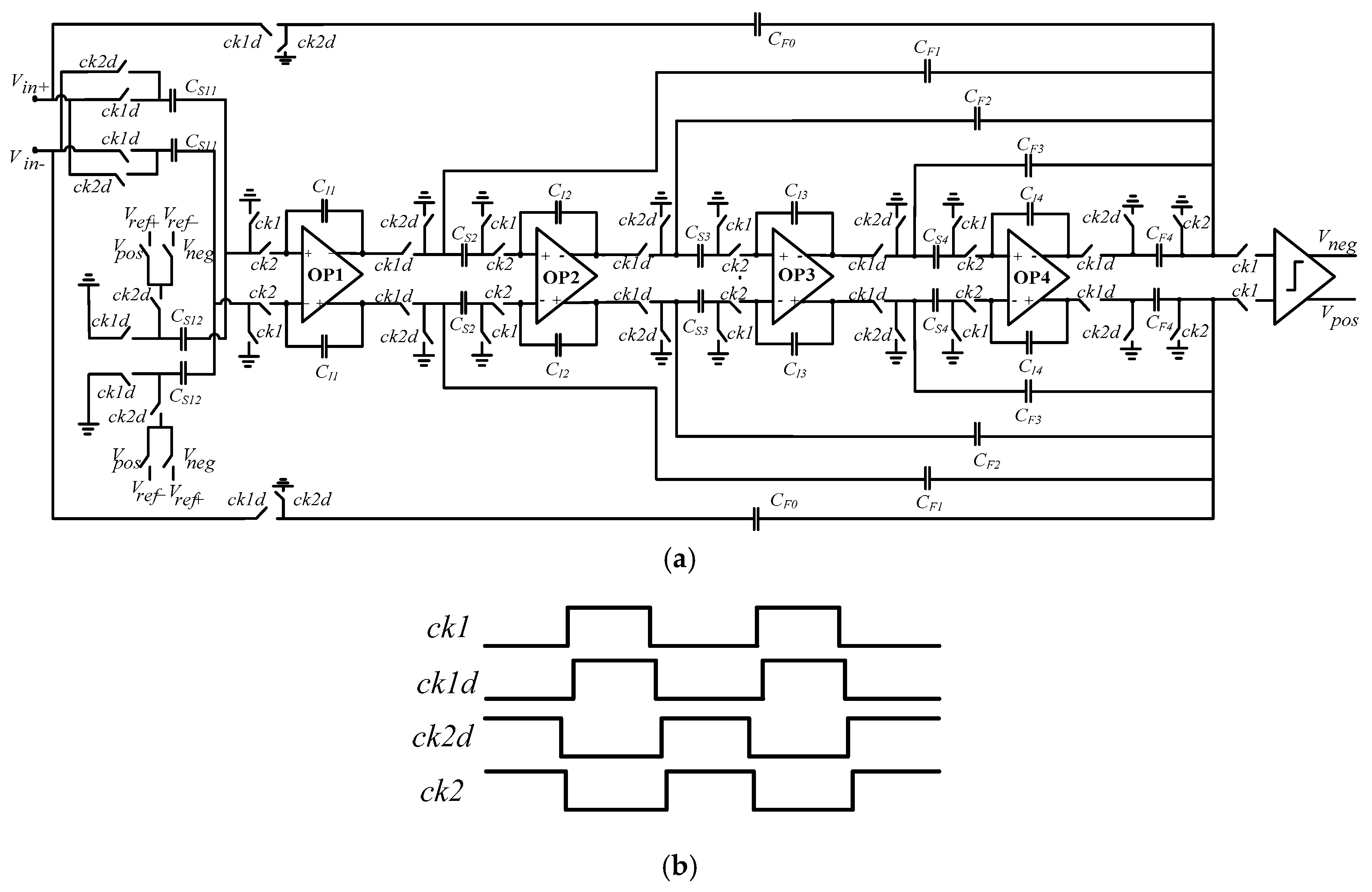

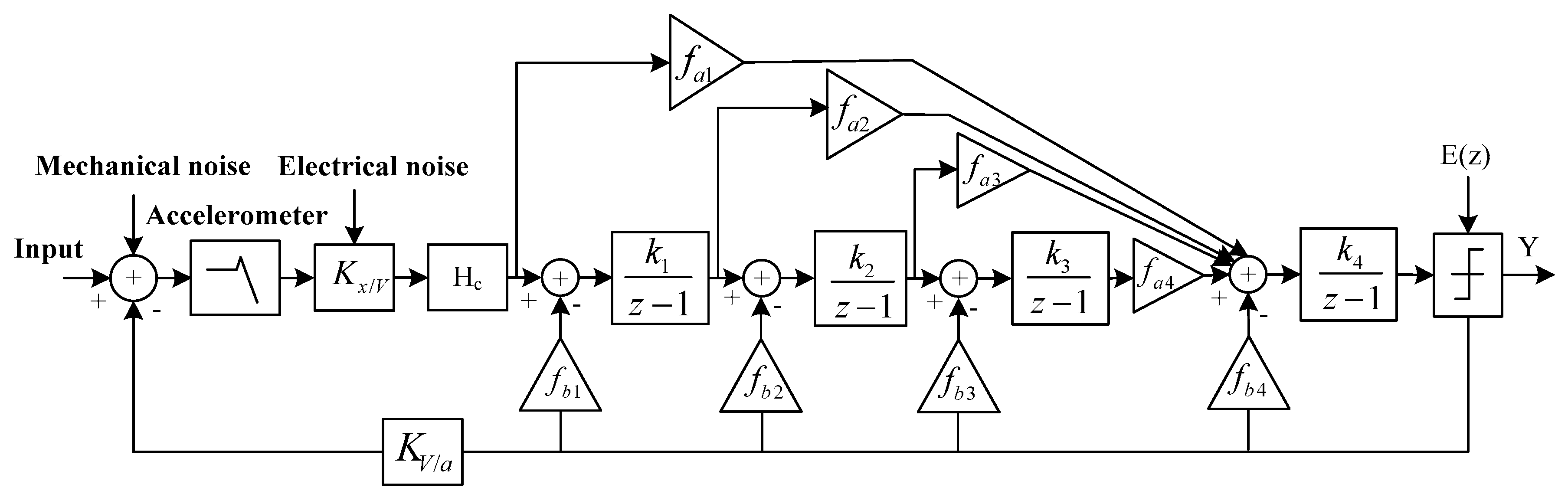

2.3. High-Order Interface Circuit Based on Micro-Accelerometers

3. Result and Discussion

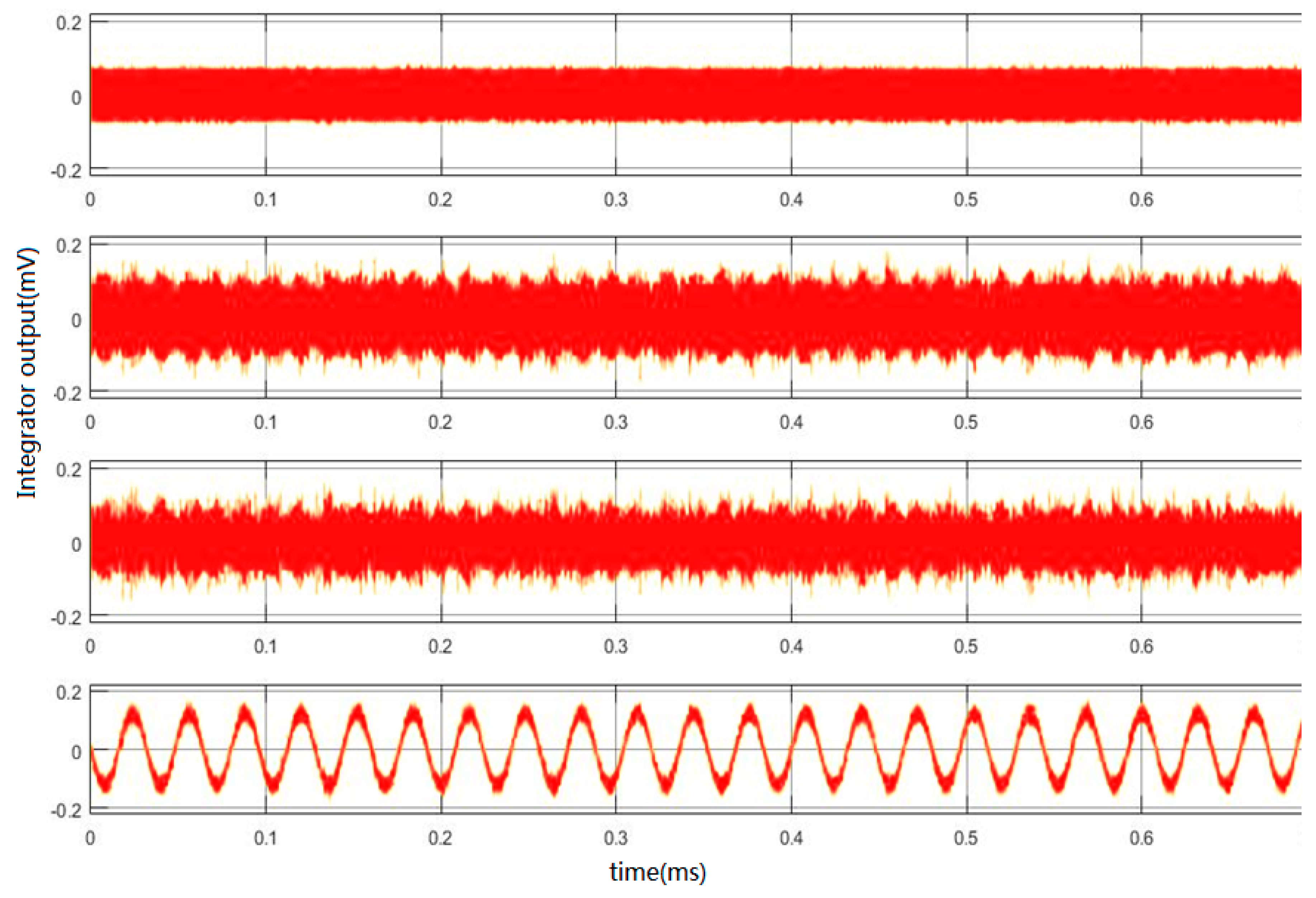

3.1. Noise Characteristics and Stability Analysis of Micro-Accelerometers

3.2. The Test of Digital Micro-Accelerometers

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Song, Z.; Sun, T.; Wu, J. System-Level Simulation and Implementation for a High Q Capacitive Accelerometer with PD Feedback Compensation. Microsyst. Tech. 2014, 21, 2233–2240. [Google Scholar] [CrossRef]

- Wang, Y.M.; Chan, P.K.; Li, H.K.H. A Low-Power Highly-Sensitive Capacitive Accelerometer IC Using Auto-Zero Time-Multiplexed Differential Technique. IEEE Sens. J. 2015, 15, 6179–6191. [Google Scholar] [CrossRef]

- Paavola, M.; Kämäräinen, M.; Laulainen, E. A Micropower-Based Interface ASIC for a Capacitive 3-Axis Micro-Accelerometer. IEEE J. Solid-State Circuits 2009, 44, 3193–3210. [Google Scholar] [CrossRef]

- Dong, Y.F.; Kraft, M.; White, W.R. Higher Order Noise-Shaping Filters for High-Performance Micromachined Accelerometers. IEEE Trans. Instrumen. Meas 2007, 56, 1666–1674. [Google Scholar] [CrossRef]

- Bajdechi, O.; Huijsing, J.H. A 1.8-V ΔΣ modulator interface for an electret microphone with on-chip reference. IEEE J. Solid-State Circuits 2002, 37, 279–285. [Google Scholar] [CrossRef]

- Petkov, V.P.; Balachandran, G.K.; Beintner, J. A Fully Differential Charge-Balanced Accelerometer for Electronic Stability Control. IEEE J. Solid-State Circuits 2014, 49, 262–270. [Google Scholar] [CrossRef]

- Petkov, V.P.; Boser, B.E. A fourth-order ΣΔ interface for micro-machined inertial sensors. IEEE J. Solid-State Circuits 2005, 40, 1602–1609. [Google Scholar] [CrossRef]

- Lajevardi, P.; Petkov, V.P.; Murmann, B. A ΣΔ interface for MEMS accelerometers using electrostatic spring constant modulation for cancellation of bondwire capacitance drift. IEEE J. Solid-State Circuits 2013, 48, 265–275. [Google Scholar] [CrossRef]

- Chiang, C.-T.; Peng, C.-R. A Multi-Level Force-Feedback CTV-Based Analog Sensing Circuits with Delta-Sigma Modulator for CMOS Micro-Accelerometers. In Proceedings of the 2015 IEEE 12th International Conference on Networking, Sensing and Control, Taibei, Taiwan, 9–11 April 2015; IEEE: Piscataway, NJ, USA, 2015. [Google Scholar]

- Huang, F.; Liang, Y. Analysis and design of the system of a total digital Si-gyroscope. Int. J. Mod. Phys. B 2017, 31, 1741008. [Google Scholar] [CrossRef]

- Maria Gomez, J.; Bota, S.A.; Marco, S. Force-Balance Interface Circuit Based on Floating MOSFET Capacitors for Micro-Machined Capacitive Accelerometers. IEEE Trans. Circuits Syst. 2006, 53, 546–552. [Google Scholar] [CrossRef]

- Soen, J.; Voda, A.; Condemine, C. Controller Design for a Closed-Loop Micromachined Accelerometer. Control Eng. Pract. 2007, 15, 57–68. [Google Scholar] [CrossRef]

- Ko, H.; Cho, D. Low Noise Accelerometer Microsystem with Highly Configurable Capacitive Interface. Analog Integr. Circuits Signal Process. 2011, 67, 365–373. [Google Scholar] [CrossRef]

- Xiang, L.; Jian, H.; Wei, C.; Xiao, L.; Liang, Y. A Novel High-Precision Digital Tunneling Magnetic Resistance-Type Sensor for the Nanosatellites’ Space Application. Micromachines 2018, 9, 121–140. [Google Scholar]

- Wu, P.C.; Liu, B.D.; Yeh, C.Y. Design of a 0.6-V 0.2-mW CMOS MEMS Accelerometer. In Proceedings of the 2015 IEEE International Conference on Consumer Electronics—Taiwan, Taipei, Taiwan, 6–8 June 2015; IEEE: Piscataway, NJ, USA, 2015. [Google Scholar]

- Yucetas, M.; Pulkkinen, M.; Kalanti, A. A high-resolution accelerometer with electrostatic damping and improved supply sensitivity. IEEE J. Sens. 2012, 47, 1721–1730. [Google Scholar] [CrossRef]

- Aaltonen, L.; Halonen, K. Continuous-time interface for a micromachined capacitive accelerometer with NEA of 4 g and bandwidth of 300 Hz. Sens. Actuators A 2009, 154, 46–56. [Google Scholar] [CrossRef]

- Amini, B.V.; Abdolvand, R.; Ayazi, F. A 4.5-mW closed-loop micro-gravity CMOS SOI accelerometer. IEEE J. Solid-State Circuits 2006, 41, 2983–2991. [Google Scholar] [CrossRef]

- Pastre, M.; Kayal, M.; Schmid, H.; Huber, A. A 300 Hz 19 b DR capacitive accelerometer based on a versatile front end in a 5th-order ΔΣ loop. In Proceedings of the 2009 Proceedings of ESSCIRC, Athens, Greece, 14–18 September 2009; IEEE: Piscataway, NJ, USA, 2009. [Google Scholar]

| Parameters | Value |

|---|---|

| Sensitivity | 10 pF/g |

| Proof Mass (m) | 6.2 × 10−7 kg |

| Rest Capacitance (C0) | 180 pF |

| Damping Coefficient (b) | 0.01 N/(m·s) |

| Sensing Gap Distance (d) | 2 μm |

| Resonance Frequency (ω0) | 1000 Hz |

| Quality Factor (Q) | >30 |

| Brownian Noise Floor | <60 ng/Hz1/2 |

| ΣΔ Modulator Circuit | |

|---|---|

| Loop Filter Topology | Fourth-Order Switched-Capacitor |

| Integration Capacitor | 10 pF |

| Oversampling Ratio (OSR) | 417 |

| Signal-to-Noise Ratio (SNR) | 108 dB |

| Sampling Frequency | 250 kHz |

| Third Harmonic Distortion | −98 dB |

| Coefficient | k1 | k2 | k3 | k4 | fa1 | fa2 | fa3 | fa4 | fb1 | fb2 | fb3 | fb4 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Value | 0.05 | 0.8 | 0.2 | 0.05 | 0.4 | 0.2 | 0.1 | 0.4 | 0.2 | 0.3 | 0.5 | 0.6 |

| Parameters | [16] | [17] | [18] | [19] | This Work |

|---|---|---|---|---|---|

| Bandwidth (Hz) | 200 | 300 | 500 | 300 | 300 |

| Sensitivity (V/g) | 0.495 | 2.267 | NA | 0.373 | 1.866 |

| Noise floor (μg/Hz1/2) | 2 | 0.3 | 4 | 1.15 | 0.48 |

| Power (mW) | 3.6 | 85.8 | 4.5 | 12 | 10 |

| Process (μm) | 0.35 | 0.7 | 0.5 | 0.6 | 0.35 |

| Supply/Range | 3.6 V/±1.15 g | 5 V/±1.5 g | 3 V/NA | 9 V/±11 g | 5 V/±1 g |

| Figure of Merit (FOM) | 0.51 | 1.49 | 0.80 | 0.80 | 0.28 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, X.; Hu, J.; Liu, X. A High-Performance Digital Interface Circuit for a High-Q Micro-Electromechanical System Accelerometer. Micromachines 2018, 9, 675. https://doi.org/10.3390/mi9120675

Li X, Hu J, Liu X. A High-Performance Digital Interface Circuit for a High-Q Micro-Electromechanical System Accelerometer. Micromachines. 2018; 9(12):675. https://doi.org/10.3390/mi9120675

Chicago/Turabian StyleLi, Xiangyu, Jianping Hu, and Xiaowei Liu. 2018. "A High-Performance Digital Interface Circuit for a High-Q Micro-Electromechanical System Accelerometer" Micromachines 9, no. 12: 675. https://doi.org/10.3390/mi9120675