Structural and Electrical Characterization of Sputter-Deposited Gd0.1Ce0.9O2−δ Thin Buffer Layers at the Y-Stabilized Zirconia Electrolyte Interface for IT-Solid Oxide Cells

Abstract

:1. Introduction

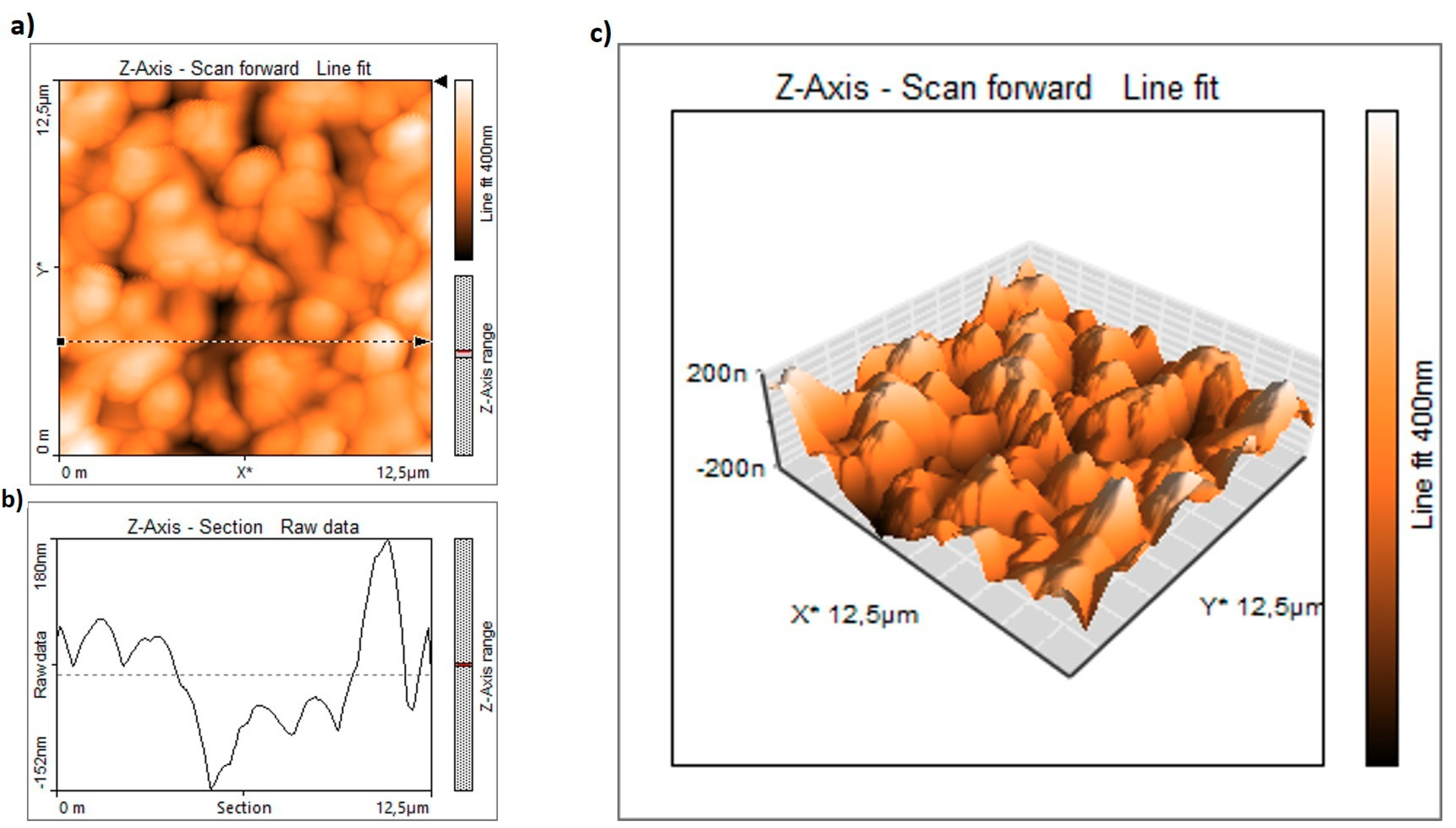

2. Morphological and Crystal Structure Characterization

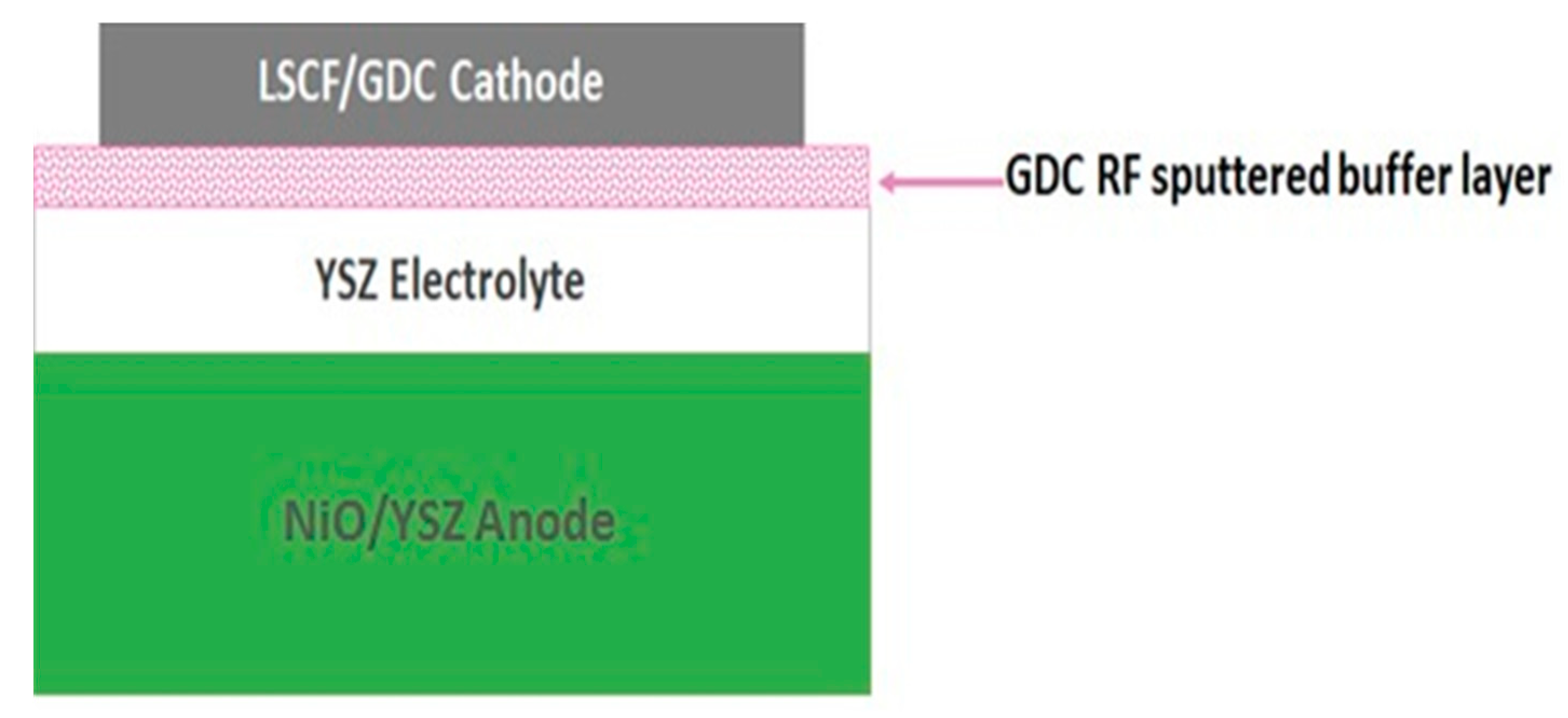

3. Impedentiometric Characterization

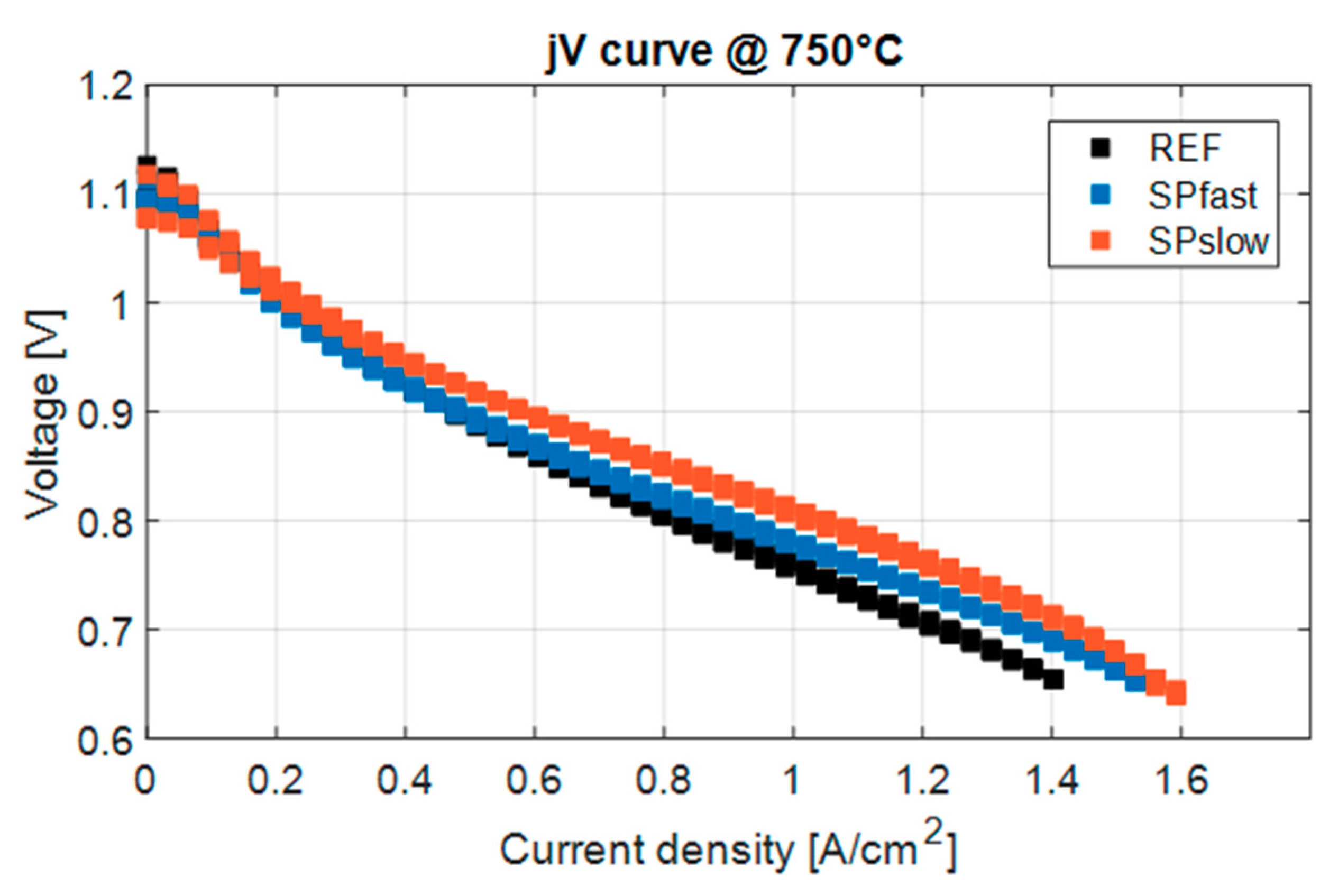

3.1. jV Curves

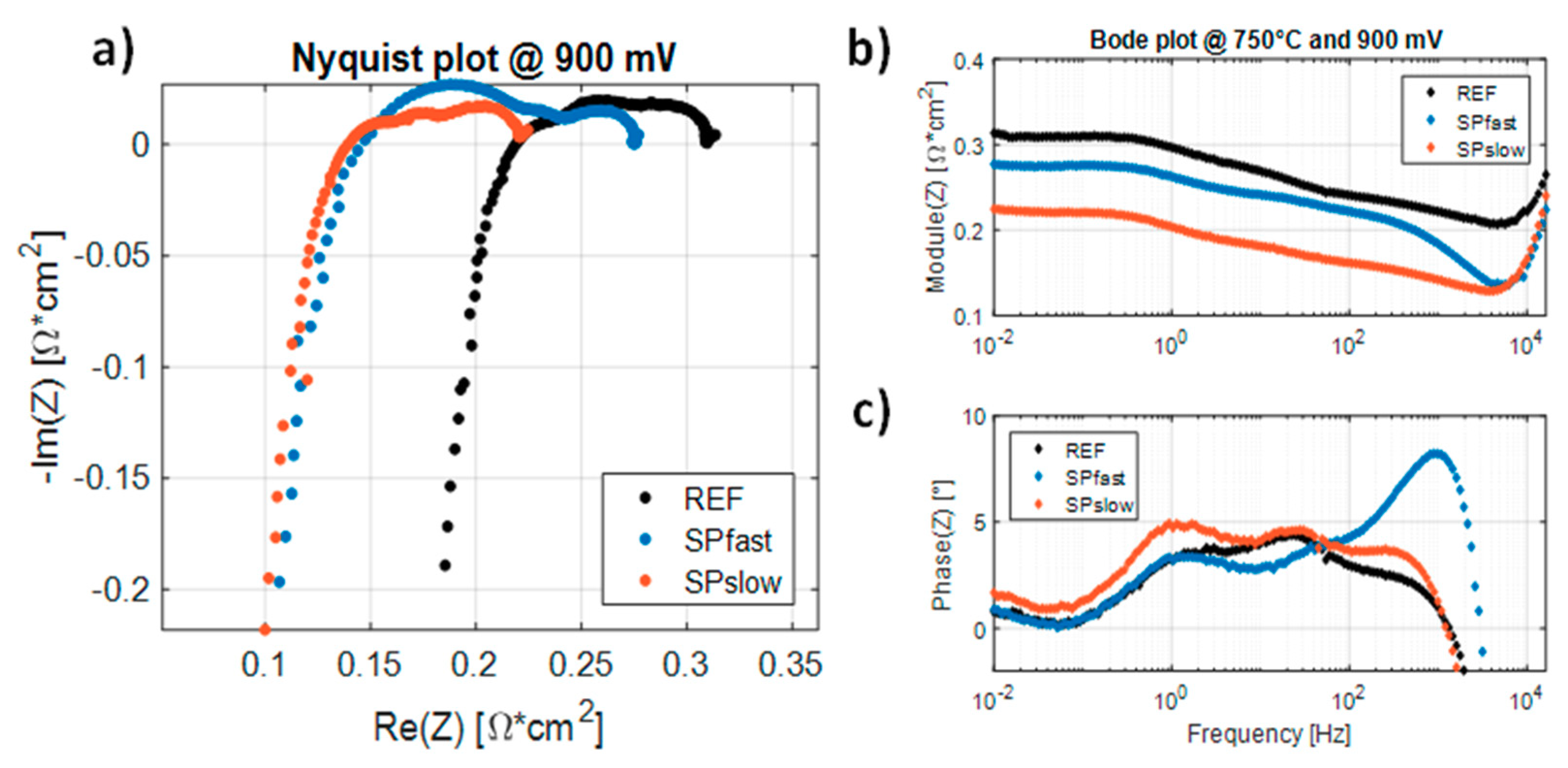

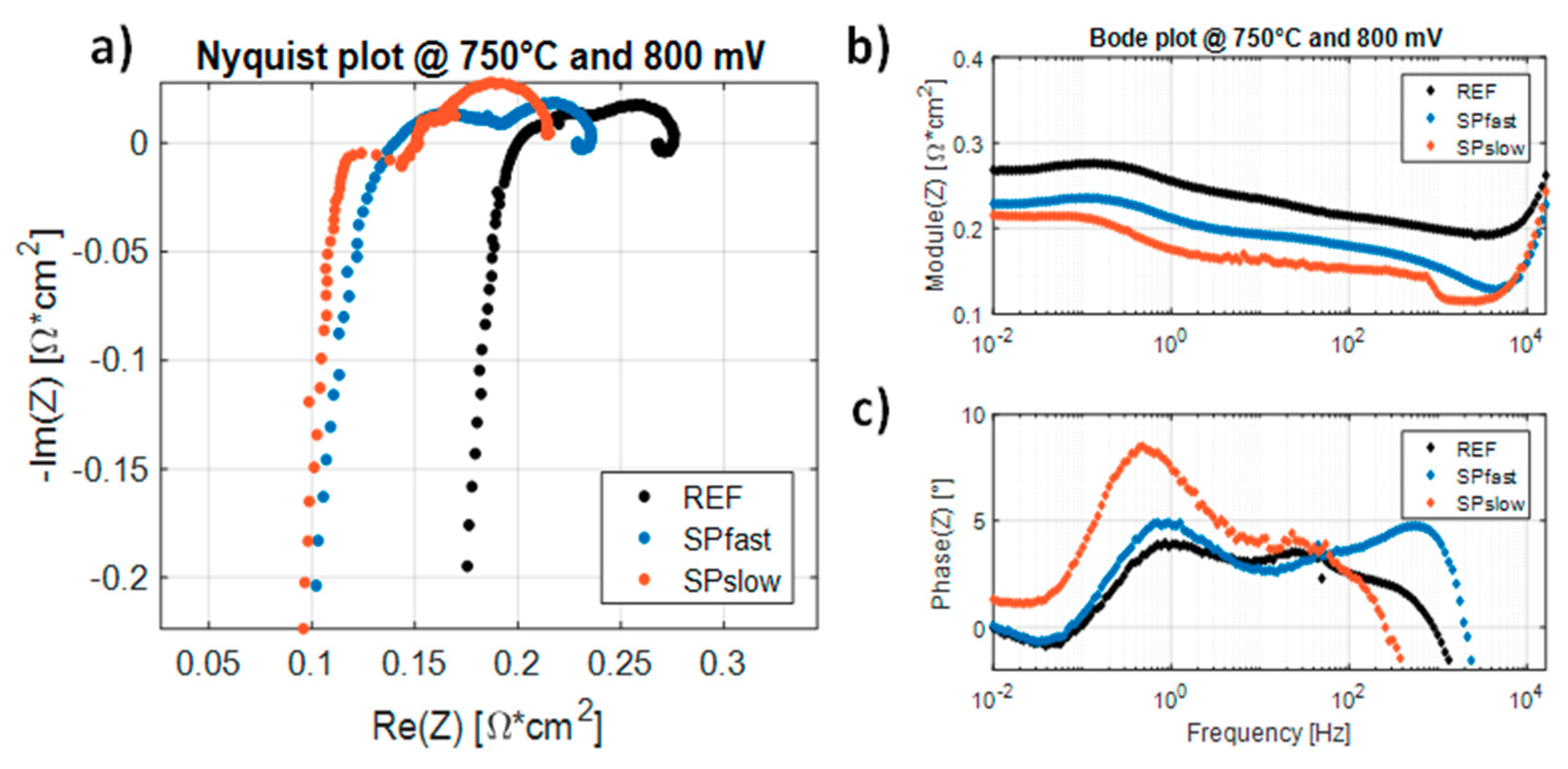

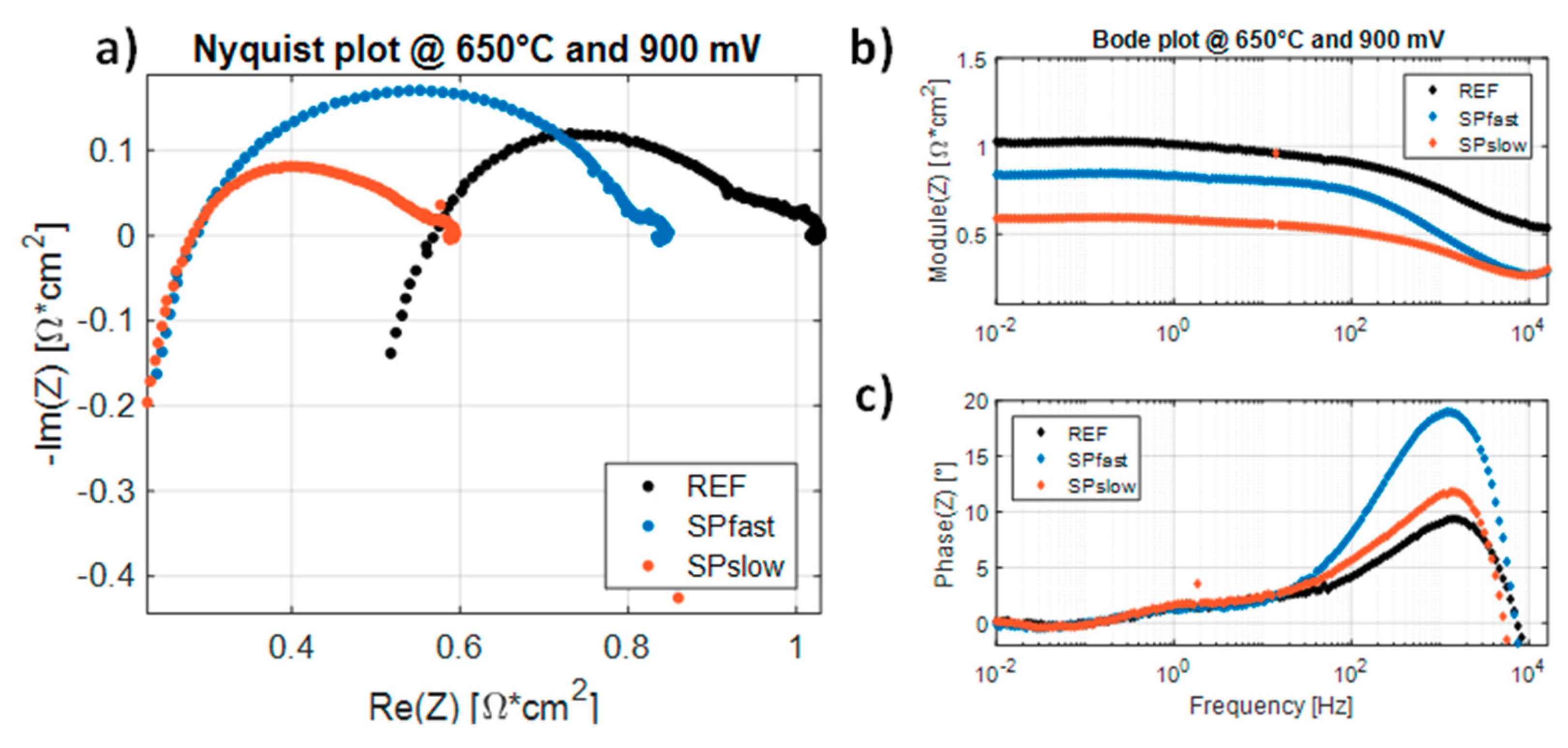

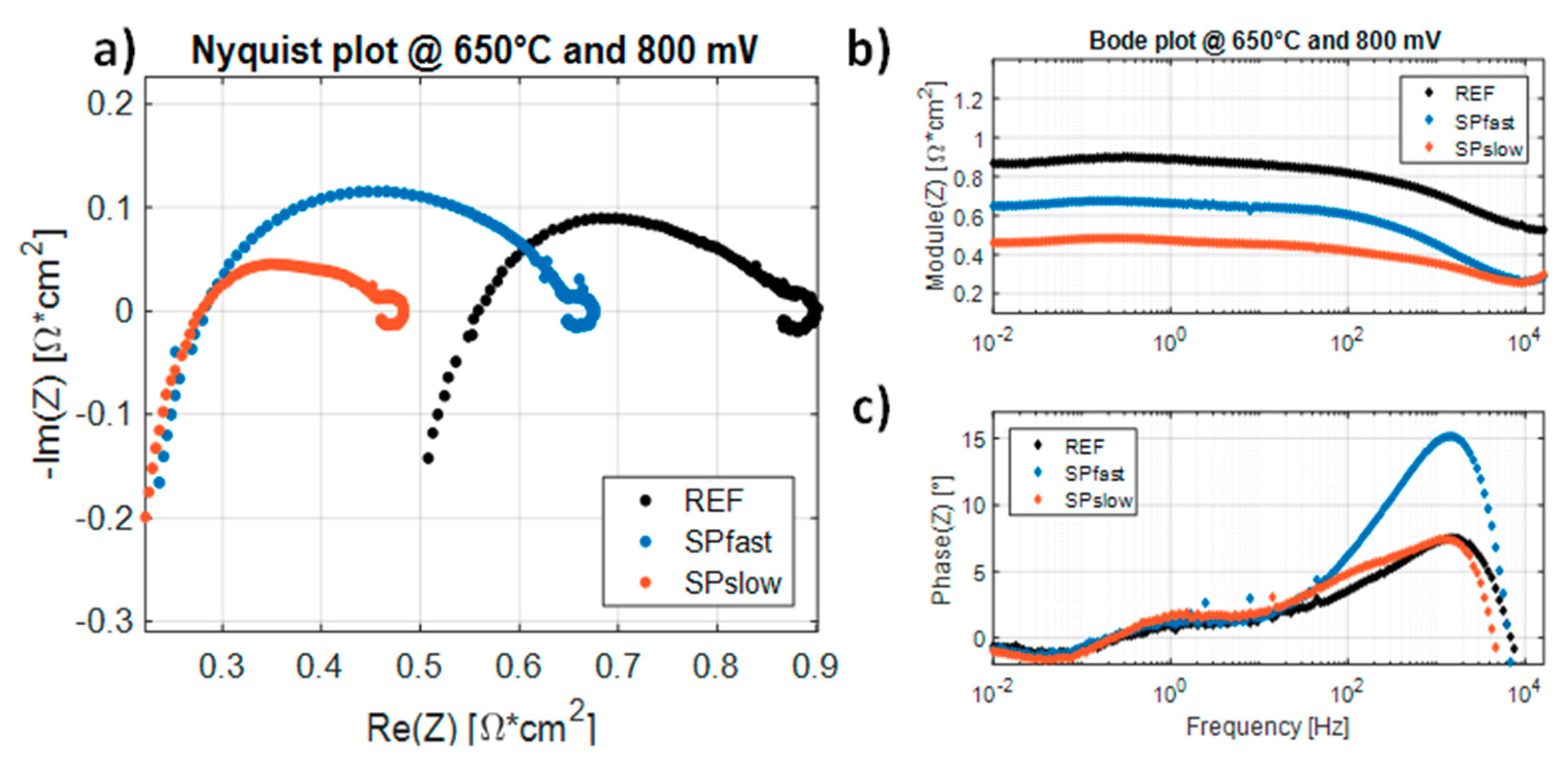

3.2. Electrochemical Impedance Spectroscopy Measurements

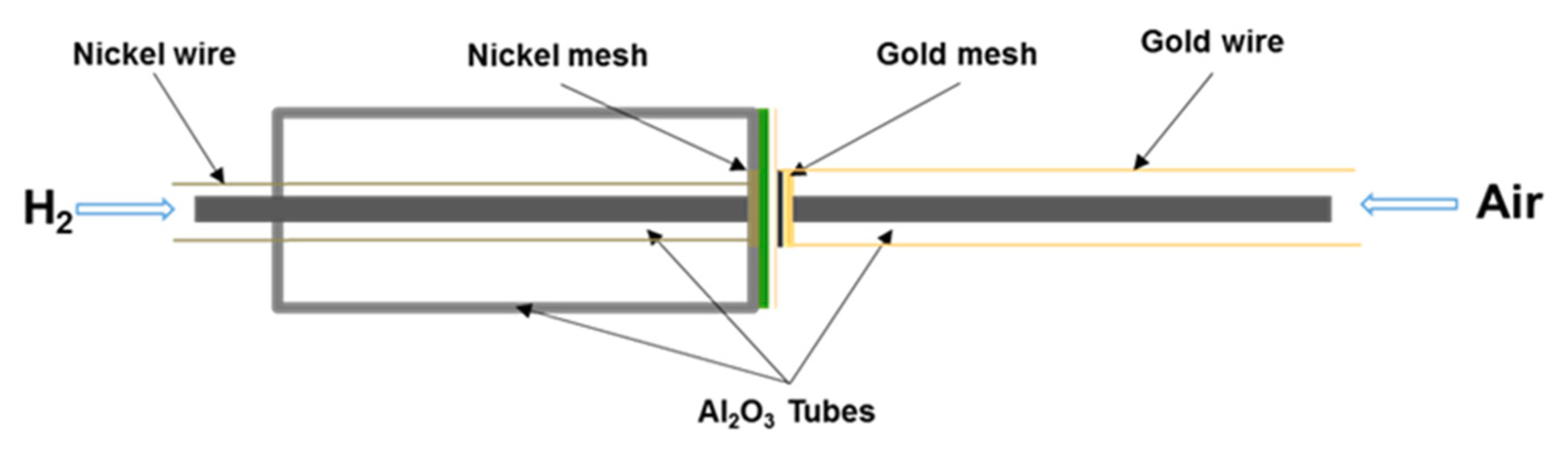

4. Samples Preparation

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Santiso, J.; Burial, M. Deposition and characterization of epitaxial oxide thin films for SOFC. J. Solid State Elettrochem. 2011, 15, 985–1006. [Google Scholar] [CrossRef]

- Huang, H.; Nakamura, M.; Su, P.; Fasching, R.; Saito, Y.; Prinz, F.B. High-Performance Ultrathin Solid Oxide Fuel Cells for Low-Temperature Operation. J. Electrochem. Soc. 2007, 154, B20–B24. [Google Scholar] [CrossRef]

- Knibbe, R.; Hijelm, J.; Menon, M.; Pryds, N.; Sogaard, M.; Wang, H.J.; Neufeld, K. Cathode-Electrolyte Interfaces with CGO Barrier Layers in SOFC. J. Am. Ceram. Soc. 2010, 93, 2877–2883. [Google Scholar] [CrossRef]

- Barfod, R.; Hagen, A.; Ramousse, S.; Hendriksen, P.V.; Mogensen, M. Break Down of Losses in Thin Electrolyte SOFCs. Fuel Cells 2006, 6, 141–145. [Google Scholar] [CrossRef]

- Yokokawa, H.; Sakai, N.; Horita, T.; Yamaji, K.; Brito, M.E.; Kishimoto, H. Thermodynamic and Kinetic Considerations on Degradations in Solid Oxide Fuel Cell Cathodes. J. Alloys Compd. 2008, 452, 41–47. [Google Scholar] [CrossRef]

- Zhou, X.D.; Scarlino, B.; Anderson, H.U. Electrical Conductivity and Stability of Gd- doped Ceria/Y-Doped Zirconia Ceramics and Thin Films. Solid State Ion. 2004, 175, 19–22. [Google Scholar] [CrossRef]

- Wang, C.M.; Azad, S.; Shutthanandan, V.; McCready, D.E.; Peden, C.H.F.; Saraf, L.; Thevuthasan, S. Microstructure of ZrO2–CeO2 Hetero-Multi-Layer Films Grown on YSZ Substrate. Acta Mater. 2005, 53, 1921–1929. [Google Scholar] [CrossRef]

- Shi, D.Q.; Ionescu, M.; McKinnon, J.; Dou, S.X. Growth Orientation and Surface Morphology of CeO2 Films Deposited by PLD Using Different Deposition Atmospheres. Phys. C 2002, 356, 304–310. [Google Scholar] [CrossRef]

- Song, K.; Schmid, H.; Srot, V.; Gilardi, E.; Gregori, G.; Du, K.; Maier, J.; Van Aken, P.A. Cerium reduction at the interface between CeO2 and Y2O3-stabilised ZrO2 and implications for interfacial oxygen non-stoichiometry. APL Mater. 2014, 2, 032104. [Google Scholar] [CrossRef]

- Wu, F.; Pavlovska, A.; Smith, D.J.; Culbertson, R.J.; Wilkens, B.J.; Bauer, E.J. Growth and Structure of Epitaxial CeO2 Films on Yttria-Stabilized ZrO2. Thin Solid Films 2008, 516, 4908–4914. [Google Scholar] [CrossRef]

- Kerman, K.; Lai, B.K.; Ramanathan, S. Free standing oxide alloy electrolytes for low temperature thin film solid oxide fuel cells. J. Power Sources 2012, 202, 120–125. [Google Scholar] [CrossRef]

- Jordan, N.; Assenmacher, W.; Uhlebruck, S.; Haanappel, V.A.C.; Buckremer, H.P.; Stover, D.; Mader, W. Ce0.8Gd0.2O2−δ Protecting Layers Manufactured by Physical Vapor Deposition for IT-SOFC. Solid State Ion. 2008, 179, 919–923. [Google Scholar] [CrossRef]

- Klemensø, T.; Nielsen, J.; Blennow, P.; Persson, Å.H.; Stegk, T.; Christensen, B.H.; Sønderby, S. High performance metal-supported solid oxide fuel cells with Gd-doped ceria barrier layers. J. Power Sources 2011, 196, 9459. [Google Scholar] [CrossRef]

- Coppola, N.; Carapella, G.; Sacco, C.; Orgiani, P.; Galdi, A.; Polverino, P.; Ubaldini, A.; Maritato, L.; Pianese, C. Investigation of Interface diffusion in Sputter deposited Gd0.1Ce0.9O1.95 thin buffer layers on Y-stabilized Zirconia crystalline substrates for Solid Oxide Cells applications. J. Mater. Sci. Eng. 2018, 7, 482. [Google Scholar] [CrossRef]

- Cheng, J.G.; Zha, S.W.; Huang, J.; Liu, X.Q.; Meng, G.Y. Sintering behavior and electrical conductivity of Ce0.9Gd0.1O1.95 powder prepared by the gel-casting process. Mater. Chem. Phys. 2003, 78, 791–795. [Google Scholar] [CrossRef]

- Arndt, B.; Noei, H.; Keller, T.F.; Muller, P.; Vonk, V.; Nenning, A.; Opitz, A.K.; Fleig, J.; Rütt, U.; Stierle, A. Structure and Stability of Gd-doped CeO2 Thin Films on Yttria-Stabilized Zirconia. Thin Solid Films 2016, 603, 56–61. [Google Scholar] [CrossRef]

- Mohamedi-Boulenouar, F.Z.; Guindet, J.; Hammou, A. Influence of water vapour on the electrochemical oxidation of Hydrogen at the Ni/Zirconia interface. In Proceedings of the Fifth International Symposium on Solid Oxide Fuel Cells SOFC-V; Stimming, U., Singhal, S.C., Tagawa, H., Lenhert, W., Eds.; The Electrochemical Society Inc.: Pennington, NJ, USA, 1997; pp. 441–450. [Google Scholar]

| Sample | Heating Ramp | Plateaux Time |

|---|---|---|

| SPfast | Tplateaux = 1000 °C (300 °C/h) | 2 h |

| SPslow | From Troom to T1 = 300 °C (1 °C/min) T1 maintained for 1 h From T1 to Tplateaux = 1050 °C (150 °C/h) | 2 h |

| T = 750 °C | T = 700 °C | T = 650 °C | ||||

|---|---|---|---|---|---|---|

| V = 900 mV | V = 900 mV | V = 900 mV | ||||

| j [mA/cm2] | %Δj [%] | j [mA/cm2] | %Δj [%] | j [mA/cm2] | %Δj [%] | |

| REF | 478.0 | 0 | 318.6 | 0 | 191.1 | 0 |

| SPfast | 477.7 | −0.06 | 318.4 | −0.06 | 191.1 | 0 |

| SPslow | 573.1 | +19.90 | 445.8 | +39.92 | 286.6 | +49.97 |

| V = 800 mV | V = 800 mV | V = 800 mV | ||||

| j [mA/cm2] | %Δj [%] | j [mA/cm2] | j [mA/cm2] | %Δj [%] | j [mA/cm2] | |

| REF | 828.6 | 0 | 541.5 | 0 | 286.6 | 0 |

| SPfast | 891.8 | +7.63 | 573.1 | +5.84 | 318.4 | +11.10 |

| SPslow | 1051.0 | +26.84 | 796.3 | +47.05 | 477.6 | +66.64 |

| T = 750 °C | T = 700 °C | T = 650 °C | ||||

|---|---|---|---|---|---|---|

| V = 900 mV | V = 900 mV | V = 900 mV | ||||

| RHF [mΩ·cm2] | %ΔRHF [%] | RHF [mΩ·cm2] | %ΔRHF [%] | RHF [mΩ·cm2] | %ΔRHF [%] | |

| REF | 219.0 | 0 | 342.8 | 0 | 567.8 | 0 |

| SPfast | 147.3 | −32.72 | 194.8 | −43.15 | 288.5 | −49.20 |

| SPslow | 139.4 | −36.35 | 198.0 | −42.22 | 283.6 | −50.06 |

| V = 800 mV | V = 800 mV | V = 800 mV | ||||

| RHF [mΩ∙cm2] | %ΔRHF [%] | RHF [mΩ∙cm2] | %ΔRHF [%] | RHF [mΩ∙cm2] | %ΔRHF [%] | |

| REF | 199.9 | 0 | 334.3 | 0 | 558.6 | 0 |

| SPfast | 140.8 | −29.57 | 191.0 | −42.85 | 283.4 | −49.27 |

| SPslow | 151.8 | −24.04 | 187.5 | −43.92 | 275.1 | −50.75 |

| T = 750 °C | T = 700 °C | T = 650 °C | ||||

|---|---|---|---|---|---|---|

| V = 900 mV | V = 900 mV | V = 900 mV | ||||

| RLF [mΩ∙cm2] | %ΔRLF [%] | RLF [mΩ∙cm2] | %ΔRLF [%] | RLF [mΩ∙cm2] | %ΔRLF [%] | |

| REF | 313.5 | 0 | 526.2 | 0 | 1029.0 | 0 |

| SPfast | 277.1 | −11.62 | 458.9 | −12.79 | 848.6 | −17.53 |

| SPslow | 224.6 | −28.36 | 331.9 | −36.92 | 593.9 | −42.28 |

| V = 800 mV | V = 800 mV | V = 800 mV | ||||

| RLF [mΩ∙cm2] | %ΔRLF [%] | RLF [mΩ∙cm2] | %ΔRLF [%] | RLF [mΩ∙cm2] | %ΔRLF [%] | |

| REF | 276.2 | 0 | 457.8 | 0 | 901.6 | 0 |

| SPfast | 235.7 | −14.65 | 365.9 | −20.07 | 675.8 | −25.05 |

| SPslow | 215.4 | −22.00 | 281.6 | −38.48 | 483.3 | −46.39 |

| T = 750 °C | T = 700 °C | T = 650 °C | ||||

|---|---|---|---|---|---|---|

| V = 900 mV | V = 900 mV | V = 900 mV | ||||

| RP [mΩ∙cm2] | %ΔRP [%] | RP [mΩ∙cm2] | %ΔRP [%] | RP [mΩ∙cm2] | %ΔRP [%] | |

| REF | 94.5 | 0 | 183.5 | 0 | 461.1 | 0 |

| SPfast | 129.7 | +37.28 | 264.1 | +43.92 | 560.1 | +21.47 |

| SPslow | 85.2 | −9.84 | 133.9 | −27.01 | 310.3 | −32.70 |

| V = 800 mV | V = 800 mV | V = 800 mV | ||||

| RP [mΩ∙cm2] | %ΔRP [%] | RP [mΩ∙cm2] | %ΔRP [%] | RP [mΩ∙cm2] | %ΔRP [%] | |

| REF | 76.3 | 0 | 123.5 | 0 | 343.0 | 0 |

| SPfast | 94.9 | +24.43 | 174.9 | +41.59 | 392.4 | +14.41 |

| SPslow | 63.6 | −16.65 | 94.2 | −23.76 | 208.2 | −39.30 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Coppola, N.; Polverino, P.; Carapella, G.; Sacco, C.; Galdi, A.; Ubaldini, A.; Vaiano, V.; Montinaro, D.; Maritato, L.; Pianese, C. Structural and Electrical Characterization of Sputter-Deposited Gd0.1Ce0.9O2−δ Thin Buffer Layers at the Y-Stabilized Zirconia Electrolyte Interface for IT-Solid Oxide Cells. Catalysts 2018, 8, 571. https://doi.org/10.3390/catal8120571

Coppola N, Polverino P, Carapella G, Sacco C, Galdi A, Ubaldini A, Vaiano V, Montinaro D, Maritato L, Pianese C. Structural and Electrical Characterization of Sputter-Deposited Gd0.1Ce0.9O2−δ Thin Buffer Layers at the Y-Stabilized Zirconia Electrolyte Interface for IT-Solid Oxide Cells. Catalysts. 2018; 8(12):571. https://doi.org/10.3390/catal8120571

Chicago/Turabian StyleCoppola, Nunzia, Pierpaolo Polverino, Giovanni Carapella, Chiara Sacco, Alice Galdi, Alberto Ubaldini, Vincenzo Vaiano, Dario Montinaro, Luigi Maritato, and Cesare Pianese. 2018. "Structural and Electrical Characterization of Sputter-Deposited Gd0.1Ce0.9O2−δ Thin Buffer Layers at the Y-Stabilized Zirconia Electrolyte Interface for IT-Solid Oxide Cells" Catalysts 8, no. 12: 571. https://doi.org/10.3390/catal8120571