Investigation of Program Efficiency Overshoot in 3D Vertical Channel NAND Flash with Randomly Distributed Traps

Abstract

:1. Introduction

2. Materials and Methods

2.1. Classification of Abnormal Program Cell Components

2.1.1. Causal Factors Broadening the Threshold Voltage Distribution

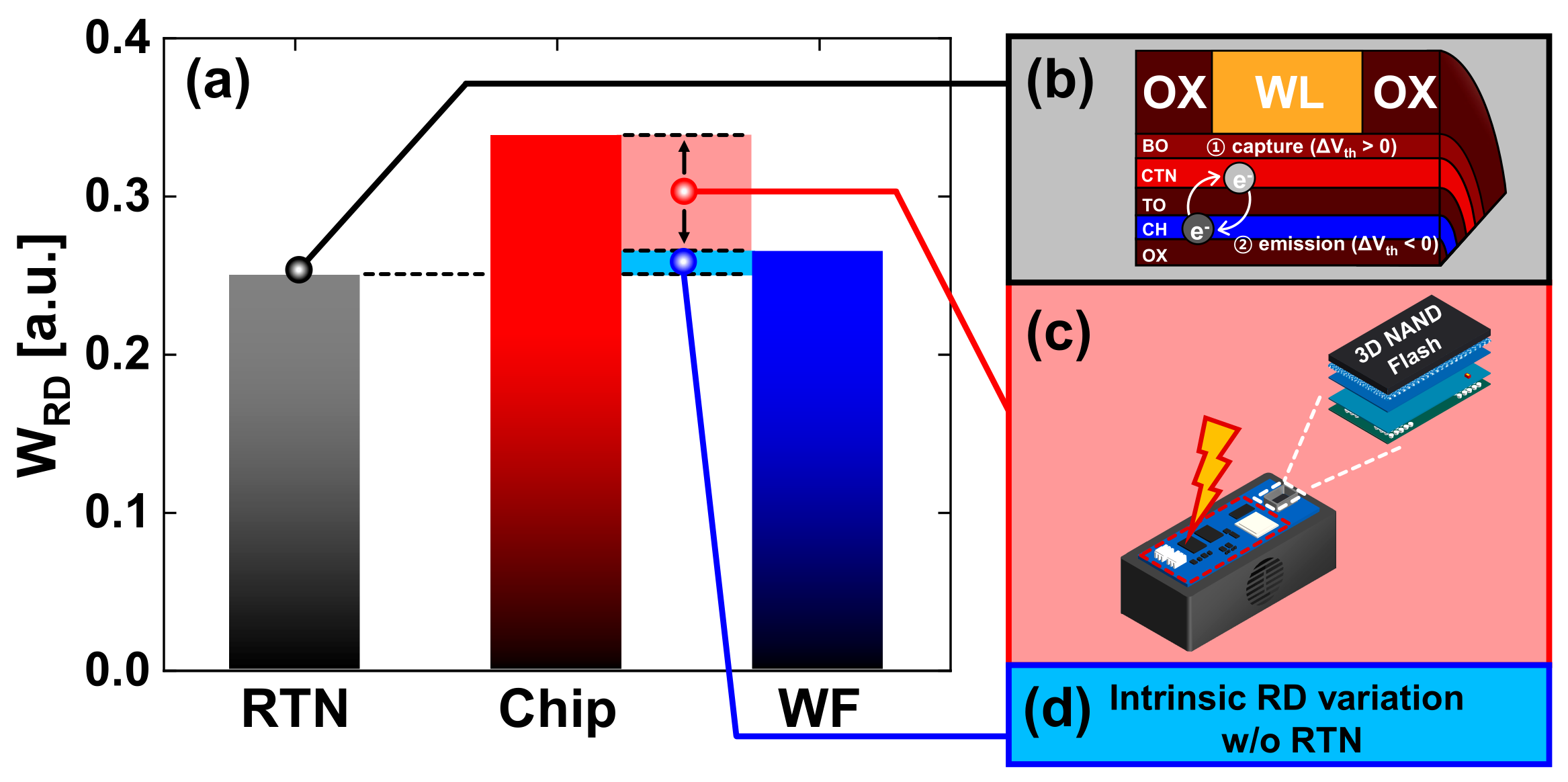

2.1.2. Read Variation Effect on Expansion of Threshold Voltage Distribution

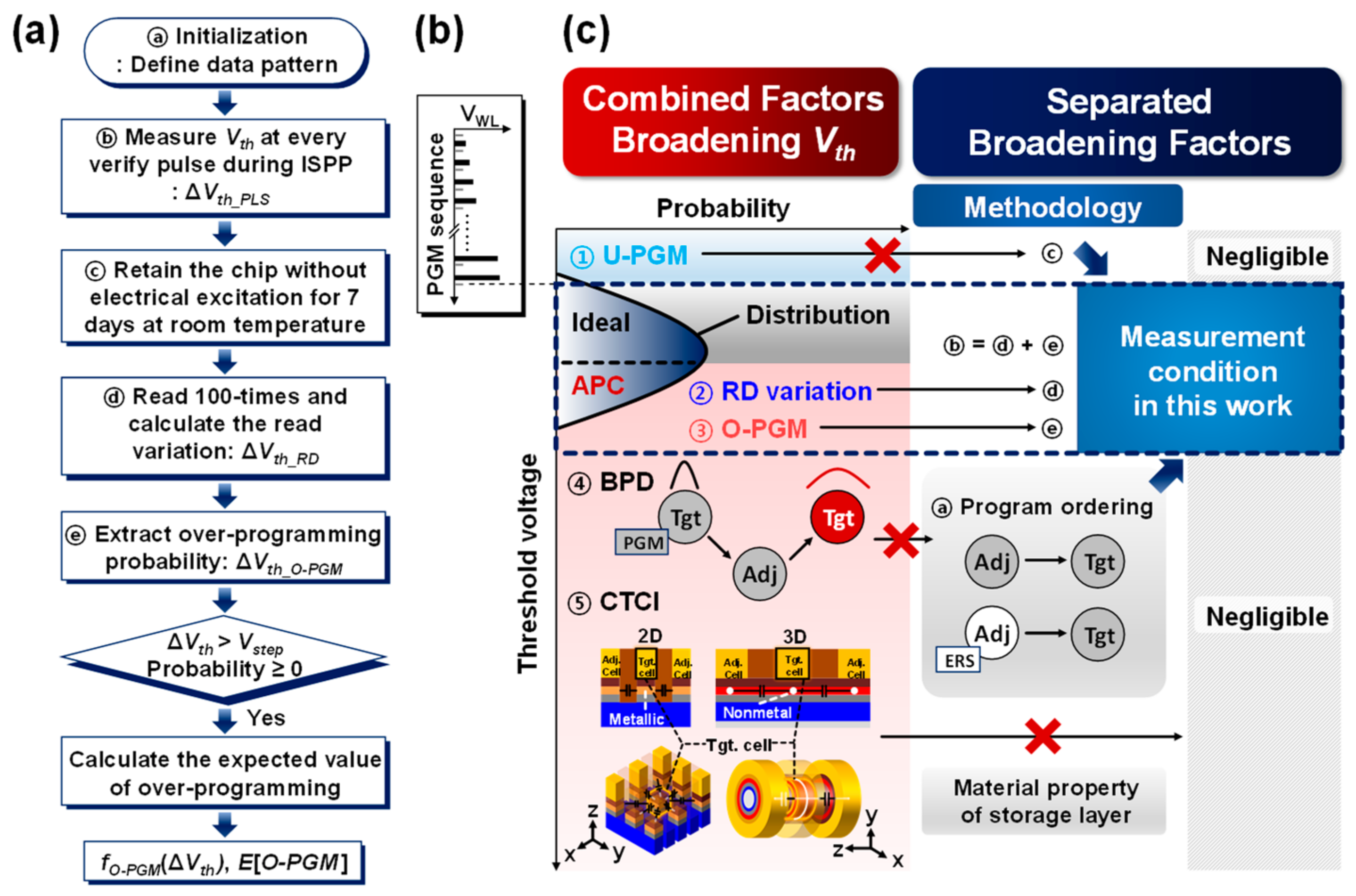

2.2. Characterization of Over−Programming in Abnormal Program Cell

3. Results and Discussion

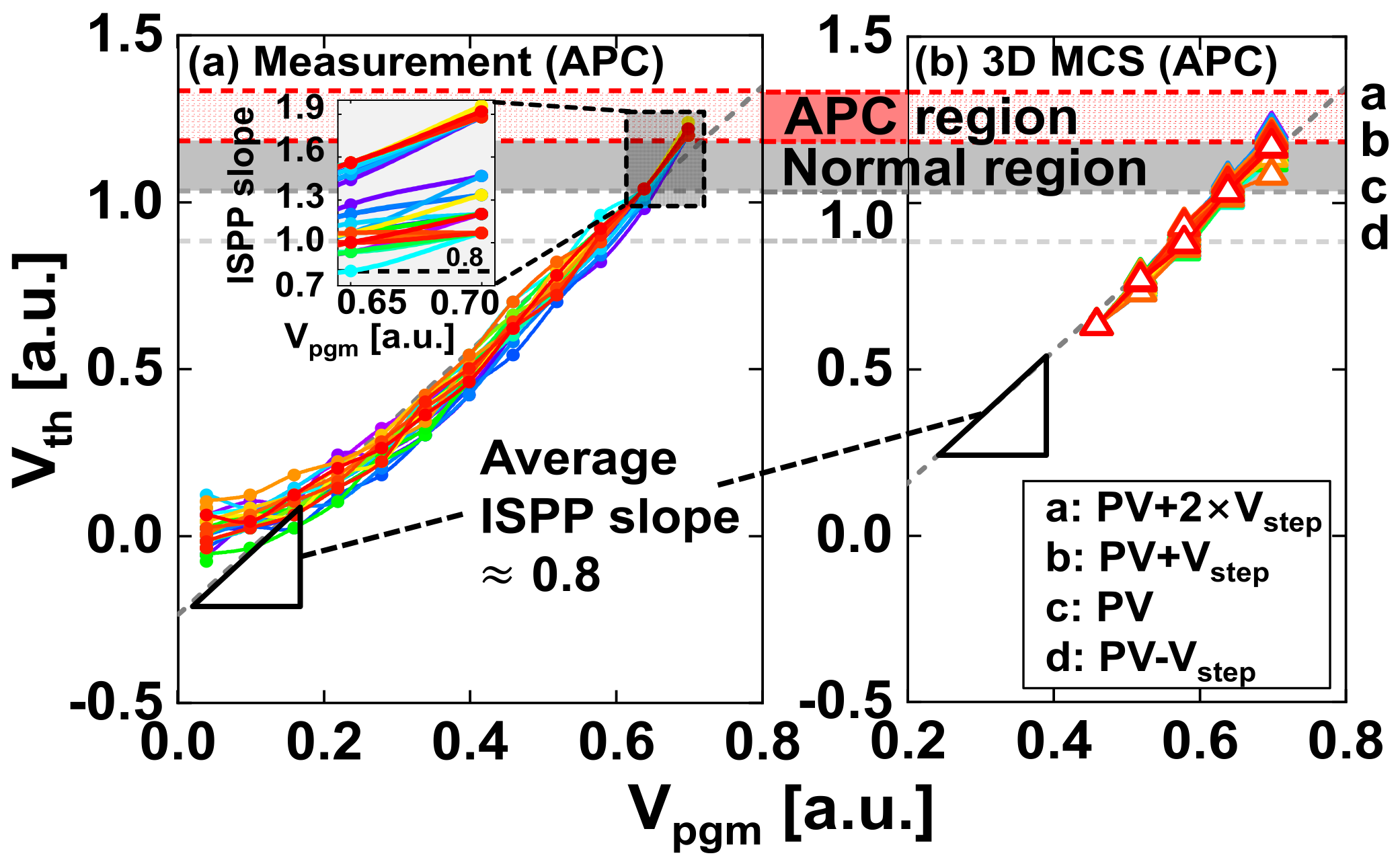

3.1. Extraction of Over−Programming and Dependence on the Program Step Voltage

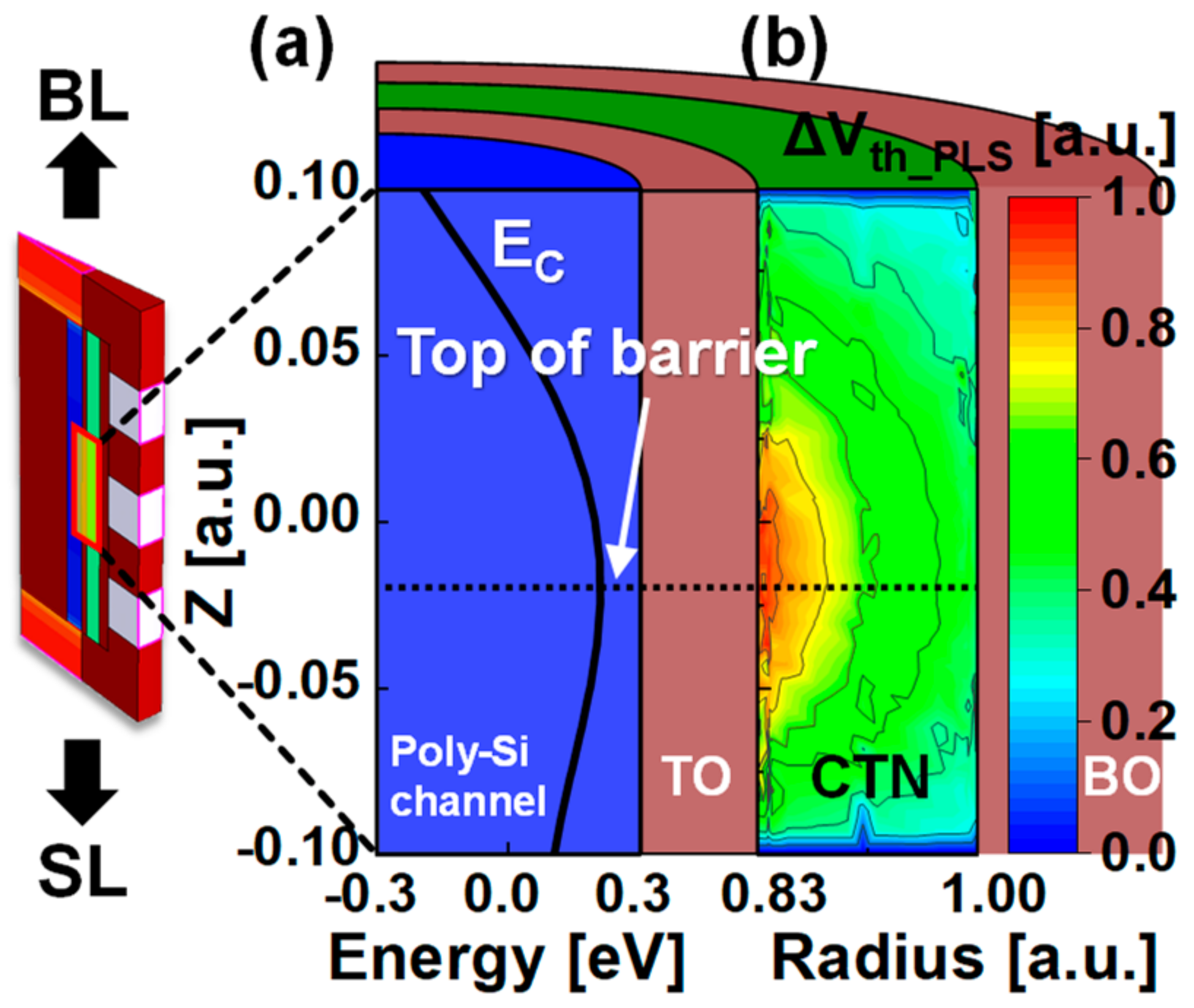

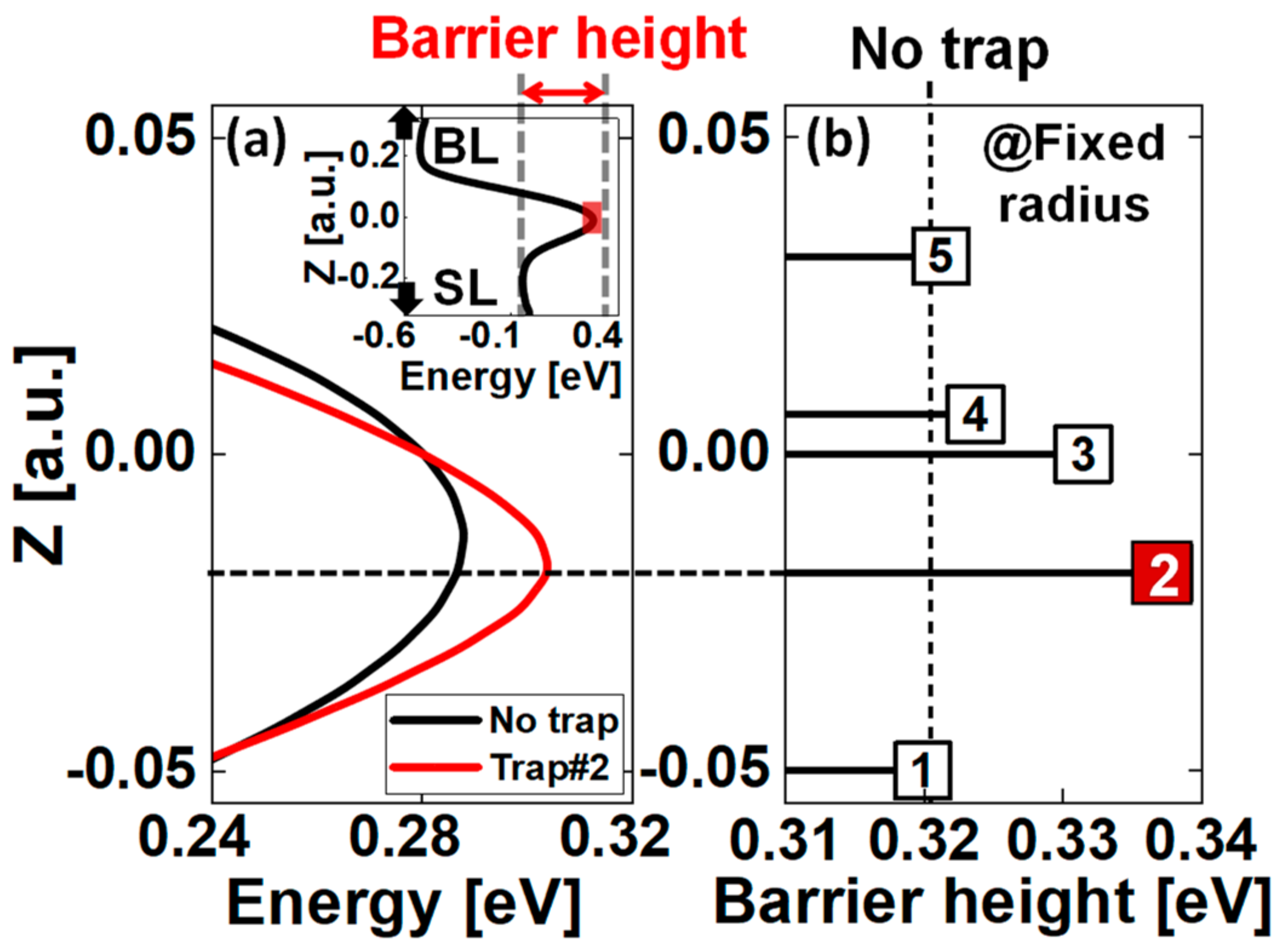

3.2. In−Depth Analysis of Over−Programming

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Choi, E.-S.; Park, S.-K. Device considerations for high density and highly reliable 3D NAND flash cell in near future. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 10–13 December 2012. [Google Scholar]

- Jang, J.; Kim, H.-S.; Cho, W.; Cho, H.; Kim, J.; Shim, S.I.; Jang, Y.; Jeong, J.-H.; Son, B.-K.; Kim, D.W.; et al. Vertical cell array using TCAT (Terabit Cell Array Transistor) technology for ultra high density NAND flash memory. In Proceedings of the IEEE Symposium on VLSI Technology, Kyoto, Japan, 15–17 June 2009. [Google Scholar]

- Katsumata, R.; Kito, M.; Fukuzumi, Y.; Kido, M.; Tanaka, H.; Komori, Y.; Ishiduki, M.; Matsunami, J.; Fujiwara, T.; Nagata, Y.; et al. Pipe-shaped BiCS flash memory with 16 stacked layers and multi-level-cell operation for ultra high density storage devices. In Proceedings of the IEEE Symposium on VLSI Technology, Kyoto, Japan, 15–17 June 2009. [Google Scholar]

- Tanaka, H.; Kido, M.; Yahashi, K.; Oomura, M.; Katsumata, R.; Kito, M.; Fukuzumi, Y.; Sato, M.; Nagata, Y.; Matsuoka, Y.; et al. Bit cost scalable technology with punch and plug process for ultra high density flash memory. In Proceedings of the IEEE Symposium on VLSI Technology, Kyoto, Japan, 12–14 June 2007. [Google Scholar]

- Lee, S.; Lee, Y.-T.; Han, W.-K.; Kim, D.-H.; Kim, M.-S.; Moon, S.-H.; Cho, H.C.; Lee, J.-W.; Byeon, D.-S.; Lim, Y.-H.; et al. A 3.3 V 4 Gb four-level NAND flash memory with 90 nm CMOS technology. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 15–19 February 2004. [Google Scholar]

- Suh, K.-D.; Suh, B.-H.; Lim, Y.-H.; Kim, J.-K.; Choi, Y.-J.; Koh, Y.-N.; Lee, S.-S.; Kwon, S.-C.; Choi, B.-S.; Yum, J.-S.; et al. A 3.3 V 32 Mb NAND flash memory with incremental step pulse programming scheme. IEEE J. Solid-State Circuits 1995, 30, 1149–1156. [Google Scholar]

- Chen, W.-C.; Lue, H.-T.; Hsiao, Y.-H.; Hsu, T.-H.; Lin, X.-W.; Lu, C.-Y. Charge storage efficiency (CSE) effect in modeling the incremental step pulse programming (ISPP) in charge-trapping 3D NAND flash devices. In Proceedings of the IEEE IEDM, Washington, DC, USA, 7–9 December 2015. [Google Scholar]

- Kim, Y.; Seo, J.Y.; Lee, S.-H.; Park, B.-G. A new programming method to alleviate the program speed variation in three-dimensional stacked array NAND flash memory. J. Semicond. Technol. Sci. 2014, 14, 566–571. [Google Scholar] [CrossRef]

- Lue, H.-T.; Hsu, T.-H.; Wang, S.-Y.; Lai, E.-K.; Hsieh, K.-Y.; Liu, R.; Lu, C.-Y. Study of incremental step pulse programming (ISPP) and STI edge effect of BE-SONOS NAND flash. In Proceedings of the IEEE International Reliability Physics Symposium (IRPS), Phoenix, AZ, USA, 27 April–1 May 2008. [Google Scholar]

- Fujiwara, M.; Morooka, T.; Nagashima, S.; Kato, T.; Fukuda, N.; Kariya, N.; Ogura, T.; Kurusu, T.; Shimada, Y.; Ishikawa, T.; et al. 3D semicircular flash memory cell: Novel split-gate technology to boost bit density. In Proceedings of the IEEE IEDM, San Francisco, CA, USA, 7–11 December 2019. [Google Scholar]

- Aiba, Y.; Tanaka, H.; Maeda, T.; Sawa, K.; Kikushima, F.; Miura, M.; Fujisawa, T.; Matsuo, M.; Sanuki, T. Cryogenic operation of 3D flash memory for new applications and bit cost scaling with 6-bit per cell (HLC) and beyond. In Proceedings of the IEEE Electron Devices Technology and Manufacturing Conference (EDTM), Chengdu, China, 8–11 April 2021. [Google Scholar]

- Shibata, N.; Maejima, H.; Isobe, K.; Iwasa, K.; Nakagawa, M.; Fujiu, M.; Shimizu, T.; Honma, M.; Hoshi, S.; Kawaai, T.; et al. A 70 nm 16 Gb 16-level-cell NAND flash memory. IEEE J. Solid-State Circuits 2008, 43, 929–937. [Google Scholar] [CrossRef]

- Xiang, C.; Jin, W.; Bowers, J.E. Silicon nitride passive and active photonic integrated circuits: Trends and prospects. Photon. Res. 2022, 10, A82–A96. [Google Scholar] [CrossRef]

- Dai, D.; Liang, D.; Cheben, P. Next-generation silicon photonics: Introduction. Photon. Res. 2022, 10, NGSP1–NGSP3. [Google Scholar] [CrossRef]

- Massey, J.L. Shift-register synthesis and BCH decoding. IEEE. Trans. Inf. Theory 1969, 15, 122–127. [Google Scholar] [CrossRef]

- Gallager, R.G. Low-density parity-check codes. IRE Trans. Inf. Theory 1962, 8, 21–28. [Google Scholar]

- Amoroso, S.M.; Maconi, A.; Mauri, A.; Compagnoni, C.M.; Greco, E.; Camozzi, E.; Vigano, S.; Tessariol, P.; Ghetti, A.; Spinelli, A.S.; et al. 3D Monte Carlo simulation of the programming dynamics and their statistical variability in nanoscale charge-trap memories. In Proceedings of the IEEE IEDM, San Francisco, CA, USA, 6–8 December 2010. [Google Scholar]

- Compagnoni, C.M.; Spinelli, A.S.; Gusmeroli, R.; Beltrami, S.; Ghetti, A.; Visconti, A. Ultimate accuracy for the NAND flash program algorithm due to the electron injection statistics. IEEE Trans. Electron Devices 2008, 55, 2695–2702. [Google Scholar] [CrossRef]

- Jung, T.-S.; Choi, Y.-J.; Suh, K.-D.; Suh, B.-H.; Kim, J.-K.; Lim, Y.-H.; Koh, Y.-N.; Park, J.-W.; Lee, K.-J.; Park, J.-H.; et al. A 117-mm2 3.3-V only 128-Mb multilevel NAND flash memory for mass storage applications. IEEE J. Solid-State Circuits 1996, 31, 1575–1583. [Google Scholar] [CrossRef]

- Park, K.T.; Kang, M.; Kim, D.; Hwang, S.-W.; Choi, B.Y.; Lee, Y.-T.; Kim, C.; Kim, K. A zeroing cell-to-cell interference page architecture with temporary LSB storing and parallel MSB program scheme for MLC NAND flash memories. IEEE J. Solid-State Circuits 2008, 43, 919–928. [Google Scholar] [CrossRef]

- Jung, T.-S.; Choi, Y.-J.; Suh, K.-D.; Suh, B.-H.; Kim, J.-K.; Lim, Y.-H.; Koh, Y.-N.; Park, J.-W.; Lee, K.-J.; Park, J.-H.; et al. A 3.3 V 128 Mb multi-level NAND flash memory for mass storage applications. In Proceedings of the IEEE ISSCC, San Francisco, CA, USA, 10 February 1996. [Google Scholar]

- Lee, J.-D.; Hur, S.-H.; Choi, J.-D. Effects of floating-gate interference on NAND flash memory cell operation. IEEE Electron Device Lett. 2002, 23, 264–266. [Google Scholar]

- Shim, K.-S.; Choi, E.-S.; Jung, S.-W.; Kim, S.-H.; Yoo, H.-S.; Jeon, K.-S.; Joo, H.-S.; Oh, J.-S.; Jang, Y.-S.; Park, K.-J.; et al. Inherent issues and challenges of program disturbance of 3D NAND flash cell. In Proceedings of the IEEE International Memory Workshop (IMW), Milan, Italy, 20–23 May 2012. [Google Scholar]

- Kim, K.T.; An, S.W.; Jung, H.S.; Yoo, K.-H.; Kim, T.W. The effects of taper-angle on the electrical characteristics of vertical NAND flash memories. IEEE Electron Device Lett. 2017, 38, 1375–1378. [Google Scholar] [CrossRef]

- Park, C.; Yoon, J.-S.; Nam, K.; Jang, H.; Park, M.S.; Baek, R.-H. Quantitative analysis of irregular channel shape effects on charge-trapping efficiency using massive 3D NAND data. Mater. Sci. Semicond. Process. 2023, 157, 107333. [Google Scholar] [CrossRef]

- Mizoguchi, K.; Takahashi, T.; Aritome, S.; Takeuchi, K. Data-retention characteristics comparison of 2D and 3D TLC NAND flash memories. In Proceedings of the IEEE IMW, Monterey, CA, USA, 14–17 May 2017. [Google Scholar]

- Woo, C.; Lee, M.; Kim, S.; Park, J.; Choi, G.-B.; Seo, M.-S.; Noh, K.H.; Kang, M.; Shin, H. Modeling of charge loss mechanisms during the short term retention operation in 3-D NAND flash memories. In Proceedings of the IEEE Symposium on VLSI Technology, Kyoto, Japan, 9–14 June 2019. [Google Scholar]

- Choi, B.; Jang, S.H.; Yoon, J.; Lee, J.; Jeon, M.; Lee, Y.; Han, J.; Lee, J.; Kim, D.M.; Kim, D.H.; et al. Comprehensive evaluation of early retention (fast charge loss within a few seconds) characteristics in tube-type 3-D NAND flash memory. In Proceedings of the IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016. [Google Scholar]

- Nicosia, G.; Mannara, A.; Resnati, D.; Paolucci, G.M.; Tessariol, P.; Spinelli, A.S.; Lacaita, A.L.; Goda, A.; Compagnoni, C.M. Characterization and modeling of temperature effects in 3-D NAND flash arrays—Part II: Random telegraph noise. IEEE Trans. Electron Devices 2018, 65, 3207–3213. [Google Scholar] [CrossRef]

- Kim, S.; Lee, M.; Choi, G.-B.; Lee, J.; Lee, Y.; Cho, M.; Ahn, K.-O.; Kim, J. RTS noise reduction of 1Y-nm floating gate NAND flash memory using process optimization. In Proceedings of the IEEE IRPS, Monterey, CA, USA, 19–23 April 2015. [Google Scholar]

- Jeong, M.-K.; Joe, S.-M.; Seo, C.-S.; Han, K.-R.; Choi, E.; Park, S.-K.; Lee, J.-H. Analysis of random telegraph noise and low frequency noise properties in 3-d stacked NAND flash memory with tube-type poly-Si channel structure. In Proceedings of the IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 12–14 June 2012. [Google Scholar]

- Kurata, H.; Otsuga, K.; Kotabe, A.; Kajiyama, S.; Osabe, T.; Sasago, Y.; Narumi, S.; Tokami, K.; Kamohara, S.; Tsuchiya, O. The impact of random telegraph signals on the scaling of multilevel flash memories. In Proceedings of the IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 15–17 June 2006. [Google Scholar]

- Hsieh, C.-C.; Lue, H.-T.; Hsu, T.-H.; Du, P.-Y.; Chiang, K.-H.; Lu, C.-Y. A Monte Carlo simulation method to predict large-density NAND product memory window from small-array test element group (TEG) verified on a 3D NAND flash test chip. In Proceedings of the Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016. [Google Scholar]

- Jia, X.; Jin, L.; Zhou, W.; Lu, J.; Amoroso, S.M.; Brown, A.R.; Lee, K.-H.; Asenov, P.; Lin, X.-W.; Liu, H.; et al. Investigation of random telegraph noise under different programmed cell Vt levels in charge trap based 3D NAND flash. IEEE Electron Device Lett. 2022, 43, 878–881. [Google Scholar] [CrossRef]

- Resnati, D.; Mannara, A.; Nicosia, G.; Paolucci, G.M.; Tessariol, P.; Spinelli, A.S.; Lacaita, A.L.; Compagnoni, C.M. Characterization and modeling of temperature effects in 3-D NAND flash arrays—Part I: Polysilicon-induced variability. IEEE Trans. Electron Devices 2018, 65, 3199–3206. [Google Scholar] [CrossRef]

- Kang, H.-J.; Jeong, M.-K.; Joe, S.-M.; Seo, J.-H.; Park, S.-K.; Jin, S.H.; Park, B.-G.; Lee, J.-H. Effect of traps on transient bit-line current behavior in word-line stacked NAND flash memory with poly-Si body. In Proceedings of the IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 9–12 June 2014. [Google Scholar]

- Byeon, D.-S.; Lee, S.-S.; Lim, Y.-H.; Kang, D.; Han, W.-K.; Kim, D.-H.; Suh, K.-D. A comparison between 63 nm 8 Gb and 90 nm 4Gb multi-level cell NAND flash memory for mass storage application. In Proceedings of the IEEE Asian Solid-State Circuits Conference, Hsinchu, Taiwan, 1–3 November 2005. [Google Scholar]

- Paolucci, G.M.; Compagnoni, C.M.; Spinelli, A.S.; Lacaita, A.L.; Goda, A. Fitting cells into a narrow VT interval: Physical constraints along the lifetime of an extremely scaled NAND flash memory array. IEEE Trans. Electron Devices 2015, 62, 1491–1497. [Google Scholar] [CrossRef]

- Joe, S.-M.; Yi, J.-H.; Park, S.-K.; Kwon, H.-I.; Lee, J.-H. Position-dependent threshold-voltage variation by random telegraph noise in NAND Flash memory strings. IEEE Electron Device Lett. 2010, 31, 635–637. [Google Scholar]

- Zou, J.; Xu, Q.; Lou, J.; Wang, R.; Huang, R.; Wang, Y. Predictive 3-D modeling of parasitic gate capacitance in gate-all-around cylindrical silicon nanowire MOSFETs. IEEE Trans. Electron Devices 2011, 58, 3379–3387. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Park, C.; Yoon, J.-S.; Nam, K.; Jang, H.; Park, M.; Baek, R.-H. Investigation of Program Efficiency Overshoot in 3D Vertical Channel NAND Flash with Randomly Distributed Traps. Nanomaterials 2023, 13, 1451. https://doi.org/10.3390/nano13091451

Park C, Yoon J-S, Nam K, Jang H, Park M, Baek R-H. Investigation of Program Efficiency Overshoot in 3D Vertical Channel NAND Flash with Randomly Distributed Traps. Nanomaterials. 2023; 13(9):1451. https://doi.org/10.3390/nano13091451

Chicago/Turabian StylePark, Chanyang, Jun-Sik Yoon, Kihoon Nam, Hyundong Jang, Minsang Park, and Rock-Hyun Baek. 2023. "Investigation of Program Efficiency Overshoot in 3D Vertical Channel NAND Flash with Randomly Distributed Traps" Nanomaterials 13, no. 9: 1451. https://doi.org/10.3390/nano13091451