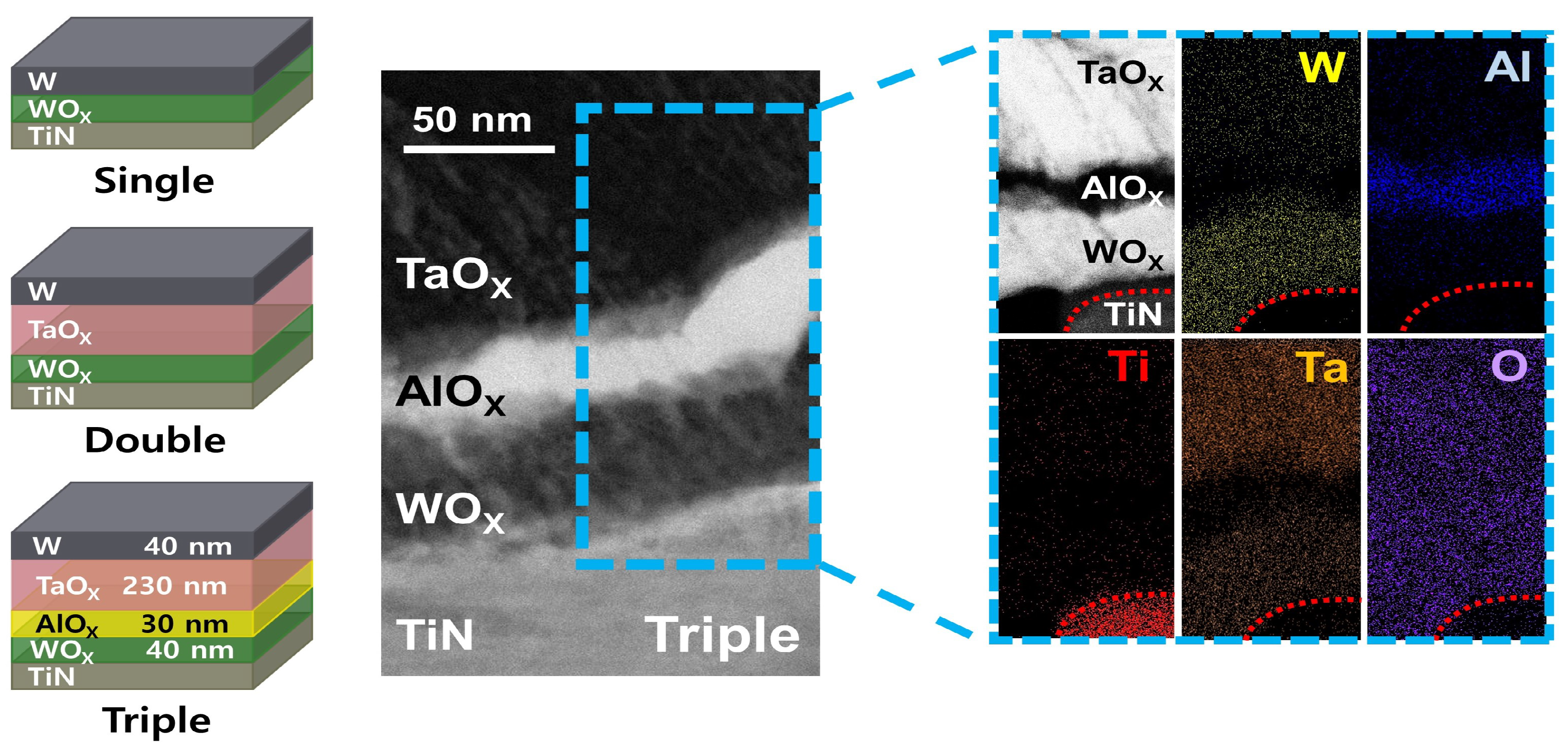

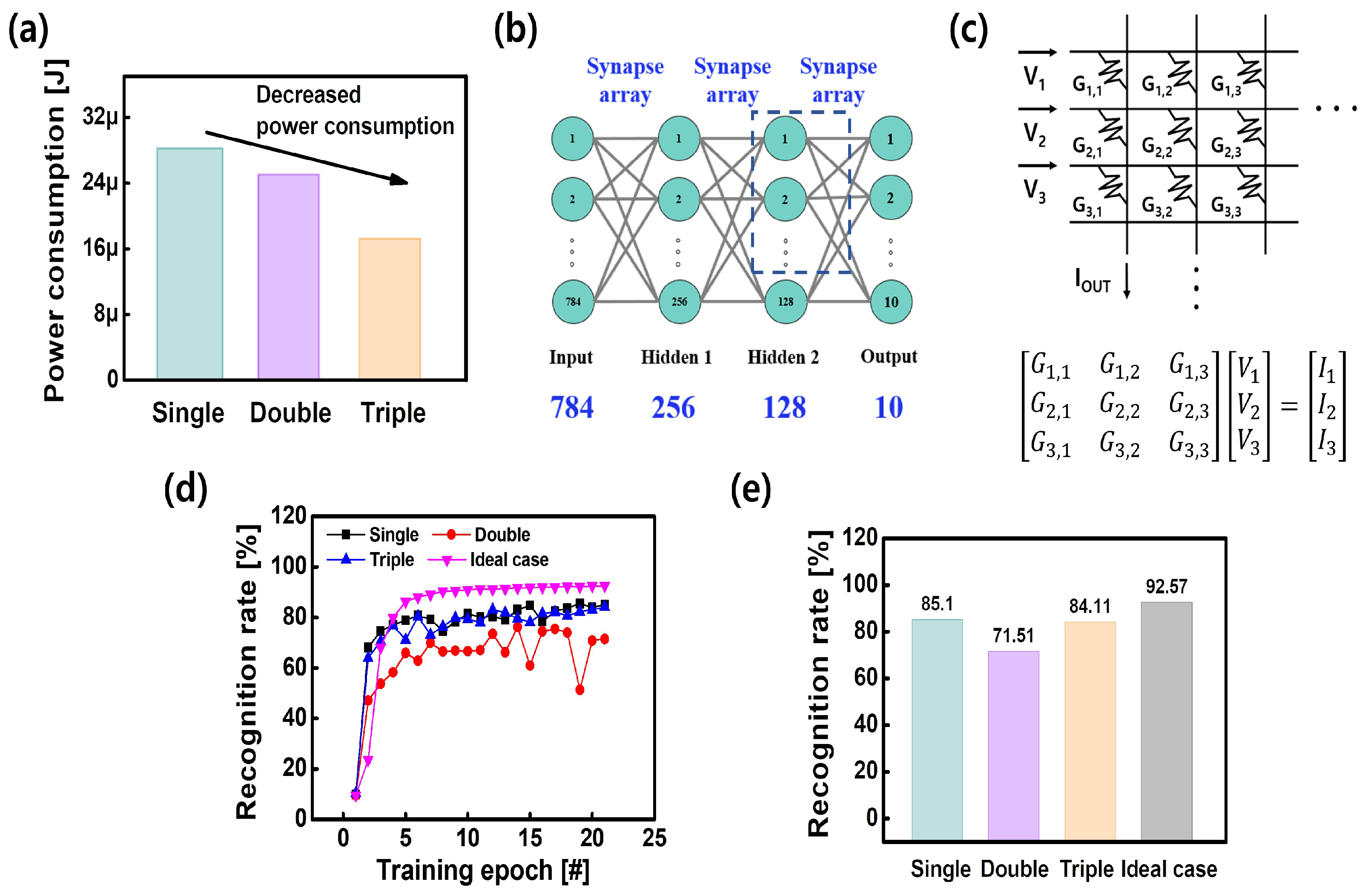

Internal Resistor Effect of Multilayer-Structured Synaptic Device for Low-Power Operation

Abstract

:1. Introduction

2. Materials and Methods

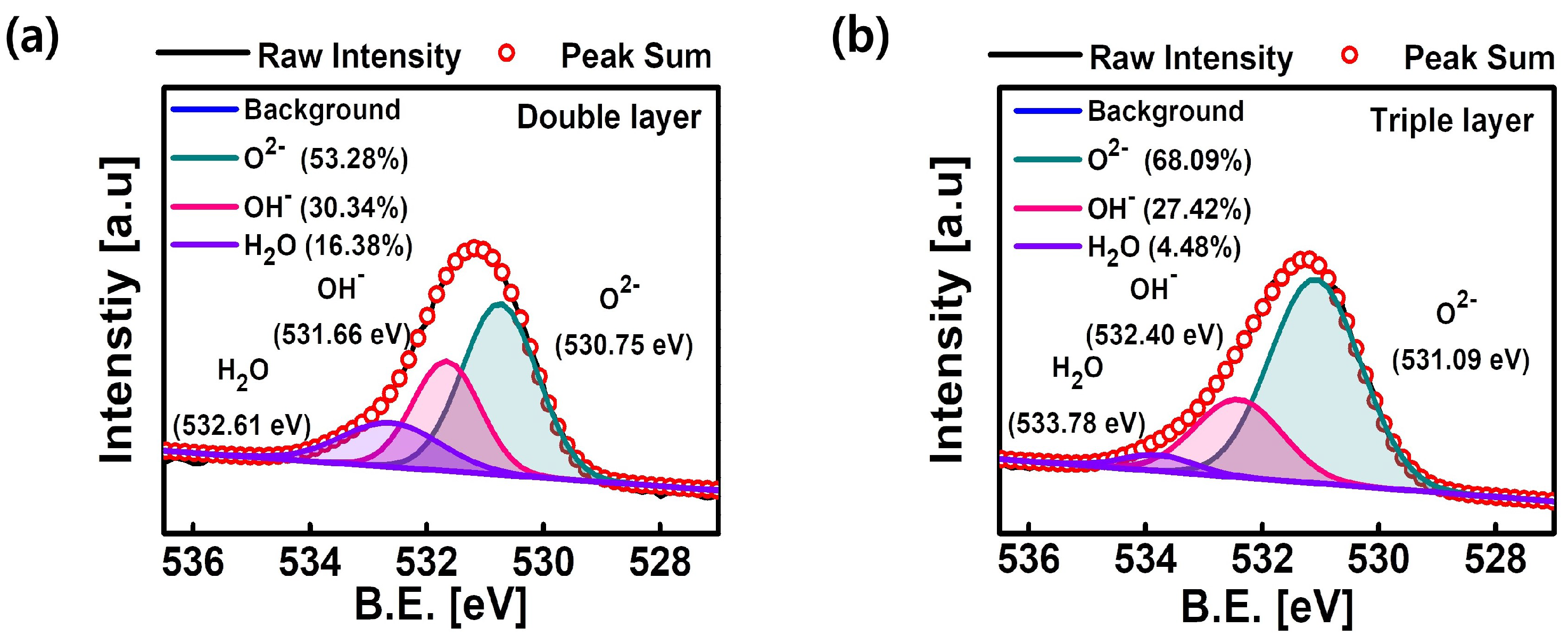

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Correction Statement

References

- Hammad, K.A.I.; Fakharaldien, M.A.I.; Zain, J.; Majid, M. Big data analysis and storage. In Proceedings of the International Conference on Operations Excellence and Service Engineering, Singapore, 6–9 December 2015; pp. 10–11. [Google Scholar]

- Dhanda, N. Big Data Storage and Analysis. Adv. Data Sci. Anal. Concepts Paradig. 2022, 10, 293–312. [Google Scholar]

- Xu, X.; Ding, Y.; Hu, S.X.; Niemier, M.; Cong, J.; Hu, Y.; Shi, Y. Scaling for edge inference of deep neural networks. Nat. Electron. 2018, 1, 216–222. [Google Scholar] [CrossRef]

- Cai, F.; Correll, J.M.; Lee, S.H.; Lim, Y.; Bothra, V.; Zhang, Z.; Flynn, M.P.; Lu, W.D. A fully integrated reprogrammable memristor–CMOS system for efficient multiply–accumulate operations. Nat. Electron. 2019, 2, 290–299. [Google Scholar] [CrossRef]

- Tang, J.; Yuan, F.; Shen, X.; Wang, Z.; Rao, M.; He, Y.; Sun, Y.; Li, X.; Zhang, W.; Li, Y.; et al. Bridging biological and artificial neural networks with emerging neuromorphic devices: Fundamentals, progress, and challenges. Adv. Mater. 2019, 31, 1902761. [Google Scholar] [CrossRef] [PubMed]

- Mead, C. Neuromorphic electronic systems. Proc. IEEE 1990, 78, 1629–1636. [Google Scholar] [CrossRef]

- Indiveri, G.; Liu, S.C. Memory and information processing in neuromorphic systems. Proc. IEEE 2015, 103, 1379–1397. [Google Scholar] [CrossRef]

- Jeong, D.S.; Kim, I.; Ziegler, M.; Kohlstedt, H. Towards artificial neurons and synapses: A materials point of view. Rsc Adv. 2013, 3, 3169–3183. [Google Scholar] [CrossRef]

- Marinella, M.J.; Agarwal, S.; Hsia, A.; Richter, I.; Jacobs-Gedrim, R.; Niroula, J.; Plimpton, S.J.; Ipek, E.; James, C.D. Multiscale co-design analysis of energy, latency, area, and accuracy of a ReRAM analog neural training accelerator. IEEE J. Emerg. Sel. Top. Circuits Syst. 2018, 8, 86–101. [Google Scholar] [CrossRef]

- Kim, S.; Baek, M.H.; Hwang, S.; Jang, T.; Park, K.; Park, B.G. A novel vector-matrix multiplication (VMM) architecture based on NAND memory array. J. Semicond. Technol. Sci. 2020, 20, 242–248. [Google Scholar] [CrossRef]

- Han, G.; Lee, C.; Lee, J.E.; Seo, J.; Kim, M.; Song, Y.; Seo, Y.H.; Lee, D. Alternative negative weight for simpler hardware implementation of synapse device based neuromorphic system. Sci. Rep. 2021, 11, 23198. [Google Scholar] [CrossRef]

- Mohammad, B.; Jaoude, M.A.; Kumar, V.; Al Homouz, D.M.; Nahla, H.A.; Al-Qutayri, M.; Christoforou, N. State of the art of metal oxide memristor devices. Nanotechnol. Rev. 2016, 5, 311–329. [Google Scholar] [CrossRef]

- Zhu, K.; Mahmoodi, M.R.; Fahimi, Z.; Xiao, Y.; Wang, T.; Bukvišová, K.; Kolíbal, M.; Roldan, J.B.; Perez, D.; Aguirre, F.; et al. Memristors with Initial Low-Resistive State for Efficient Neuromorphic Systems. Adv. Intell. Syst. 2022, 4, 2200001. [Google Scholar] [CrossRef]

- Saludes-Tapia, M.; Campabadal, F.; Miranda, E.A.; Gonzalez, M.B. Impact of the W Etching Process on the Resistive Switching Properties of Tin/Ti/Hfo2/W Memristors. Solid-State Electron. 2023, 207, 108718. [Google Scholar] [CrossRef]

- Mohanty, S.K.; Panda, D.; Reddy, K.P.K.; Lee, P.T.; Wu, C.H.; Chang, K.M. Uniform resistive switching and highly stable synaptic characteristics of HfOx sandwiched TaOx-based memristor for neuromorphic system. Ceram. Int. 2023, 49, 16909–16917. [Google Scholar] [CrossRef]

- Basnet, P.; Anderson, E.C.; Athena, F.F.; Chakrabarti, B.; West, M.P.; Vogel, E.M. Asymmetric Resistive Switching of Bilayer HfO x/AlO y and AlO y/HfO x Memristors: The Oxide Layer Characteristics and Performance Optimization for Digital Set and Analog Reset Switching. Acs Appl. Electron. Mater. 2023, 5, 1859–1865. [Google Scholar] [CrossRef]

- Zhu, S.; Sun, B.; Zhou, G.; Guo, T.; Ke, C.; Chen, Y.; Yang, F.; Zhang, Y.; Shao, J.; Zhao, Y. In-Depth Physical Mechanism Analysis and Wearable Applications of HfO x-Based Flexible Memristors. Acs Appl. Mater. Interfaces 2023, 15, 5420–5431. [Google Scholar] [CrossRef] [PubMed]

- Bature, U.I.; Nawi, I.M.; Khir, M.H.M.; Zahoor, F.; Hashwan, S.S.B.; Algamili, A.S.; Abbas, H. Analysis of thermodynamic resistive switching in ZnO-based RRAM device. Phys. Scr. 2023, 98, 035020. [Google Scholar] [CrossRef]

- Kim, S.; Ishii, M.; Lewis, S.; Perri, T.; BrightSky, M.; Kim, W.; Jordan, R.; Burr, G.W.; Sosa, N.; Ray, A.; et al. NVM neuromorphic core with 64k-cell (256-by-256) phase change memory synaptic array with on-chip neuron circuits for continuous in-situ learning. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 17.1.1–17.1.4. [Google Scholar]

- Oh, S.; Kim, T.; Kwak, M.; Song, J.; Woo, J.; Jeon, S.; Yoo, I.K.; Hwang, H. HfZrO x-based ferroelectric synapse device with 32 levels of conductance states for neuromorphic applications. IEEE Electron Device Lett. 2017, 38, 732–735. [Google Scholar] [CrossRef]

- Grenouillet, L.; Francois, T.; Coignus, J.; Vaxelaire, N.; Carabasse, C.; Triozon, F.; Richter, C.; Schroeder, U.; Nowak, E. Performance assessment of BEOL-integrated HfO 2-based ferroelectric capacitors for FeRAM memory arrays. In Proceedings of the 2020 IEEE Silicon Nanoelectronics Workshop (SNW), Honolulu, HI, USA, 13–14 June 2020; pp. 5–6. [Google Scholar]

- Rahaman, S.Z.; Chang, Y.J.; Hsin, Y.C.; Yang, S.Y.; Lee, H.H.; Wang, I.J.; Chen, G.L.; Su, Y.H.; Wei, J.H.; Sheu, S.S.; et al. Process-induced magnetic tunnel junction damage and its recovery for the development of spin–orbit torque magnetic random access memory. J. Magn. Magn. Mater. 2023, 565, 170296. [Google Scholar] [CrossRef]

- Waser, R.; Dittmann, R.; Staikov, G.; Szot, K. Redox-based resistive switching memories–nanoionic mechanisms, prospects, and challenges. Adv. Mater. 2009, 21, 2632–2663. [Google Scholar] [CrossRef]

- Chand, U.; Huang, C.Y.; Kumar, D.; Tseng, T.Y. Metal induced crystallized poly-Si-based conductive bridge resistive switching memory device with one transistor and one resistor architecture. Appl. Phys. Lett. 2015, 107, 203502. [Google Scholar] [CrossRef]

- Baek, I.; Kim, D.; Lee, M.; Kim, H.J.; Yim, E.; Lee, M.; Lee, J.; Ahn, S.; Seo, S.; Lee, J.; et al. Multi-layer cross-point binary oxide resistive memory (OxRRAM) for post-NAND storage application. In Proceedings of the IEEE International Electron Devices Meeting, 2005, IEDM Technical Digest, Washington, DC, USA, 5 December 2005; pp. 750–753. [Google Scholar]

- Sawa, A. Resistive switching in transition metal oxides. Mater. Today 2008, 11, 28–36. [Google Scholar] [CrossRef]

- Luo, Q.; Xu, X.; Gong, T.; Lv, H.; Dong, D.; Ma, H.; Yuan, P.; Gao, J.; Liu, J.; Yu, Z.; et al. 8-Layers 3D vertical RRAM with excellent scalability towards storage class memory applications. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 2.7.1–2.7.4. [Google Scholar] [CrossRef]

- Luo, Q.; Zhang, X.; Yu, J.; Wang, W.; Gong, T.; Xu, X.; Yin, J.; Yuan, P.; Tai, L.; Dong, D.; et al. Memory Switching and Threshold Switching in a 3D Nanoscaled NbOX System. IEEE Electron Device Lett. 2019, 40, 718–721. [Google Scholar] [CrossRef]

- Zhang, W.; Guo, Z.; Dai, Y.; Lei, J.; Wang, J.; Hu, F. Effects of stacking sequence and top electrode configuration on switching behaviors in ZnO-HfO2 hybrid resistive memories. Ceram. Int. 2023, 49, 35973–35981. [Google Scholar] [CrossRef]

- Kim, Y.; Jo, K.J.; Oh, J.S.; Yang, C.W. Bipolar Resistive Switching Characteristics of Ta/TaxMnyOz/Pt Structure for ReRAM Application with Large Resistance Window. Electron. Mater. Lett. 2023, 20, 26–32. [Google Scholar] [CrossRef]

- Das, O.P.; Pandey, S.K. Optical, Compositional and Electrical Properties of Transparent MgO Thin Film for ReRAM Devices. Proc. J. Phys. Conf. Ser. 2023, 2426, 012031. [Google Scholar] [CrossRef]

- Moazzeni, A.; Kordrostami, Z. Switching characteristic of fabricated nonvolatile bipolar resistive switching memory (ReRAM) using PEDOT: PSS/GO. Solid-State Electron. 2022, 188, 108208. [Google Scholar] [CrossRef]

- Lodhi, A.; Saini, S.; Dwivedi, A.; Khandelwal, A.; Tiwari, S.P. Bipolar resistive switching properties of TiO x/graphene oxide doped PVP based bilayer ReRAM. J. Micromech. Microeng. 2022, 32, 044001. [Google Scholar] [CrossRef]

- Mu, S.; Stowe, D. Accurate Elemental Mapping of Semiconductor Devices Using EDS–Deconvolving Overlapping Peaks. Microsc. Microanal. 2023, 29, 107–108. [Google Scholar] [CrossRef]

- Han, G.; Seo, J.; Kim, H.; Lee, D. Role of the electrolyte layer in CMOS-compatible and oxide-based vertical three-terminal ECRAM. J. Mater. Chem. 2023, 11, 5167–5173. [Google Scholar] [CrossRef]

- Kanegami, N.; Nishi, Y.; Kimoto, T. Unique resistive switching phenomena exhibiting both filament-type and interface-type switching in Ti/Pr0. 7Ca0. 3MnO3- δ/Pt ReRAM cells. Appl. Phys. Lett. 2020, 116, 013501. [Google Scholar] [CrossRef]

- Park, J.; Lee, C.; Kwak, M.; Chekol, S.A.; Lim, S.; Kim, M.; Woo, J.; Hwang, H.; Lee, D. Microstructural engineering in interface-type synapse device for enhancing linear and symmetric conductance changes. Nanotechnology 2019, 30, 305202. [Google Scholar] [CrossRef] [PubMed]

- Pershin, Y.V.; Martinez-Rincon, J.; Di Ventra, M. Memory circuit elements: From systems to applications. J. Comput. Theor. Nanosci. 2011, 8, 441–448. [Google Scholar] [CrossRef]

- Rudrapal, K.; Biswas, M.; Jana, B.; Adyam, V.; Chaudhuri, A.R. Tuning resistive switching properties of WO3- x-memristors by oxygen vacancy engineering for neuromorphic and memory storage applications. J. Phys. Appl. Phys. 2023, 56, 205302. [Google Scholar] [CrossRef]

- Lee, C.; Choi, W.; Kwak, M.; Kim, S.; Hwang, H. Impact of electrolyte density on synaptic characteristics of oxygen-based ionic synaptic transistor. Appl. Phys. Lett. 2021, 119, 103503. [Google Scholar] [CrossRef]

- Lee, C.; Choi, W.; Kwak, M.; Kim, S.; Hwang, H. Excellent synapse characteristics of 50 nm vertical transistor with WO x channel for high density neuromorphic system. In Proceedings of the 2021 Symposium on VLSI Technology, Kyoto, Japan, 13–19 June 2021; pp. 1–2. [Google Scholar]

- Mazur, M.; Wojcieszak, D.; Wiatrowski, A.; Kaczmarek, D.; Lubańska, A.; Domaradzki, J.; Mazur, P.; Kalisz, M. Analysis of amorphous tungsten oxide thin films deposited by magnetron sputtering for application in transparent electronics. Appl. Surf. Sci. 2021, 570, 151151. [Google Scholar] [CrossRef]

- Rahimnejad, S.; He, J.H.; Chen, W.; Wu, K.; Xu, G.Q. Tuning the electronic and structural properties of WO 3 nanocrystals by varying transition metal tungstate precursors. RSC Adv. 2014, 4, 62423–62429. [Google Scholar] [CrossRef]

- Rasch, M.J.; Moreda, D.; Gokmen, T.; Le Gallo, M.; Carta, F.; Goldberg, C.; El Maghraoui, K.; Sebastian, A.; Narayanan, V. A flexible and fast PyTorch toolkit for simulating training and inference on analog crossbar arrays. In Proceedings of the 2021 IEEE 3rd International Conference on Artificial Intelligence Circuits and Systems (AICAS), Washington, DC, USA, 6–9 June 2021; pp. 1–4. [Google Scholar]

- Burr, G.W.; Shelby, R.M.; Sebastian, A.; Kim, S.; Kim, S.; Sidler, S.; Virwani, K.; Ishii, M.; Narayanan, P.; Fumarola, A.; et al. Neuromorphic computing using non-volatile memory. Adv. Physics X 2017, 2, 89–124. [Google Scholar] [CrossRef]

| Device | Material | Atomic Ratio (%) | Condition |

|---|---|---|---|

| Double layer WO | W 4f | 30.76 | WO target Ar:O = 20:5 |

| O 1s | 69.24 | ||

| Triple layer WO | W 4f | 29.08 | |

| O 1s | 70.92 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, H.; Han, G.; Cho, S.; Woo, J.; Lee, D. Internal Resistor Effect of Multilayer-Structured Synaptic Device for Low-Power Operation. Nanomaterials 2024, 14, 201. https://doi.org/10.3390/nano14020201

Kim H, Han G, Cho S, Woo J, Lee D. Internal Resistor Effect of Multilayer-Structured Synaptic Device for Low-Power Operation. Nanomaterials. 2024; 14(2):201. https://doi.org/10.3390/nano14020201

Chicago/Turabian StyleKim, Hyejin, Geonhui Han, Seojin Cho, Jiyong Woo, and Daeseok Lee. 2024. "Internal Resistor Effect of Multilayer-Structured Synaptic Device for Low-Power Operation" Nanomaterials 14, no. 2: 201. https://doi.org/10.3390/nano14020201