Data Retention Characterization of Gate-Injected Gold-Nanoparticle Non-Volatile Memory with Low-Damage CF4-Plasma-Treated Blocking Oxide Layer

Abstract

:1. Introduction

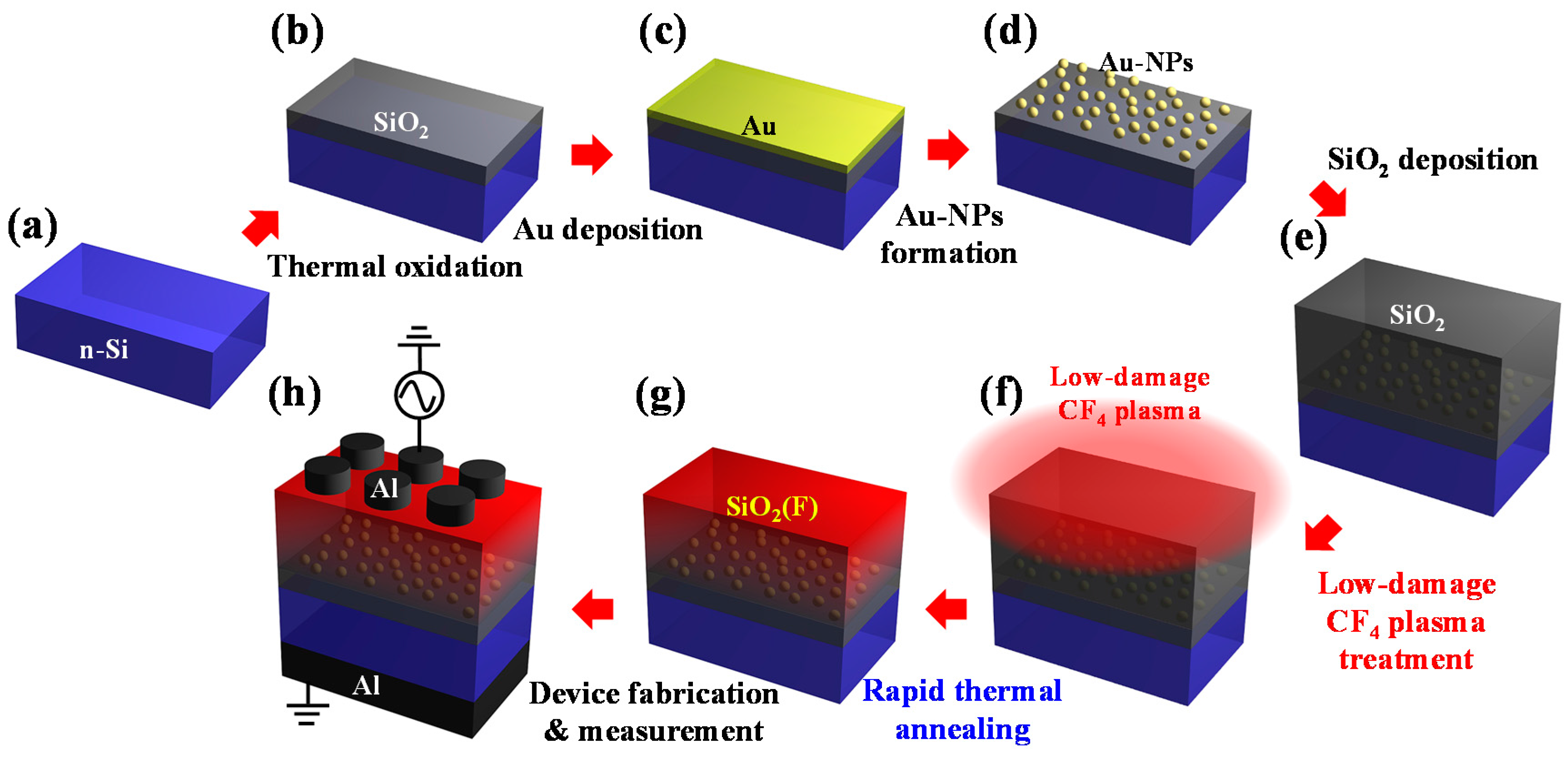

2. Materials and Methods

2.1. Sample Preparation

2.2. Characterization

3. Results and Discussion

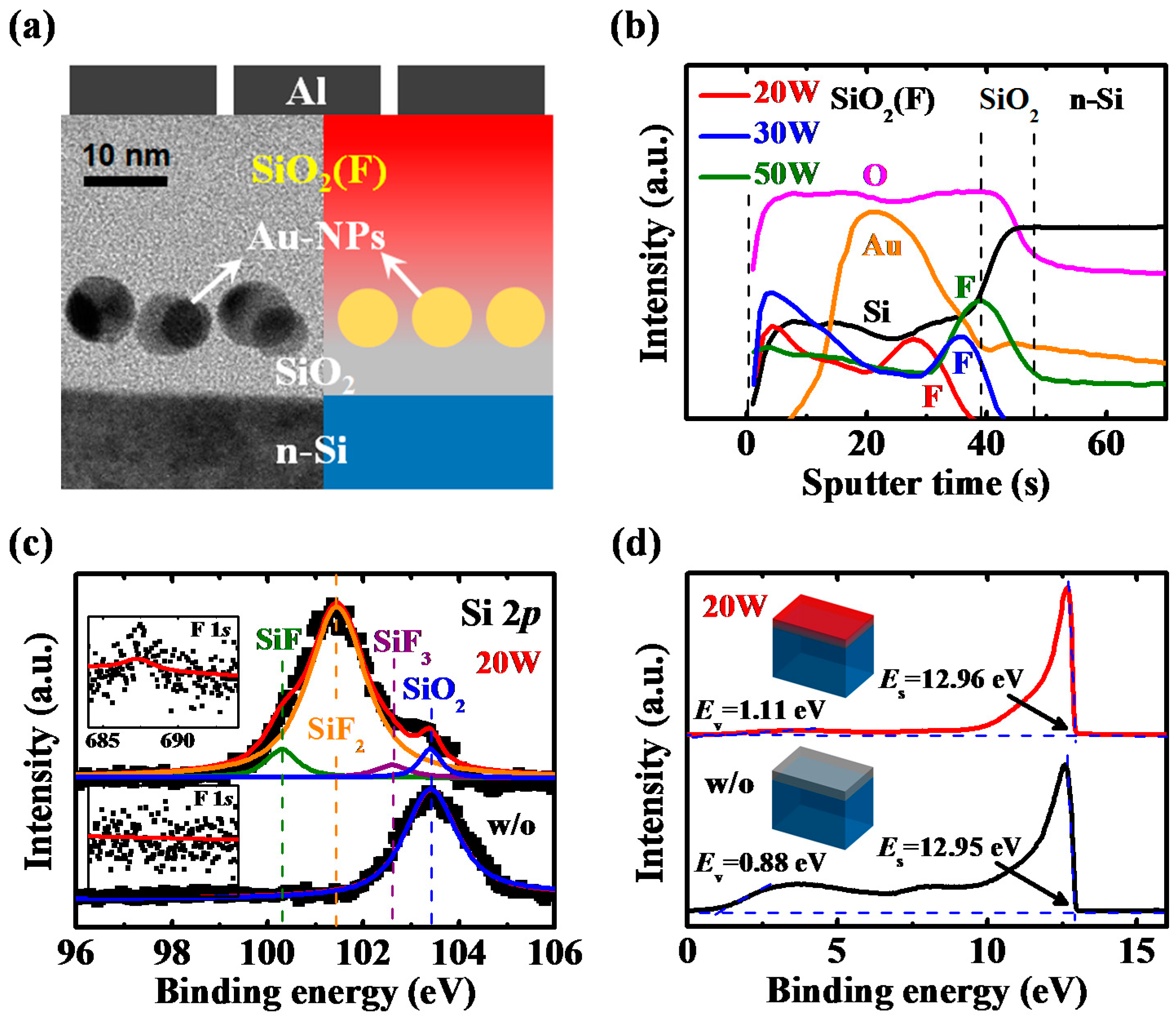

3.1. Material Analysis

3.2. Electrical Characteristics

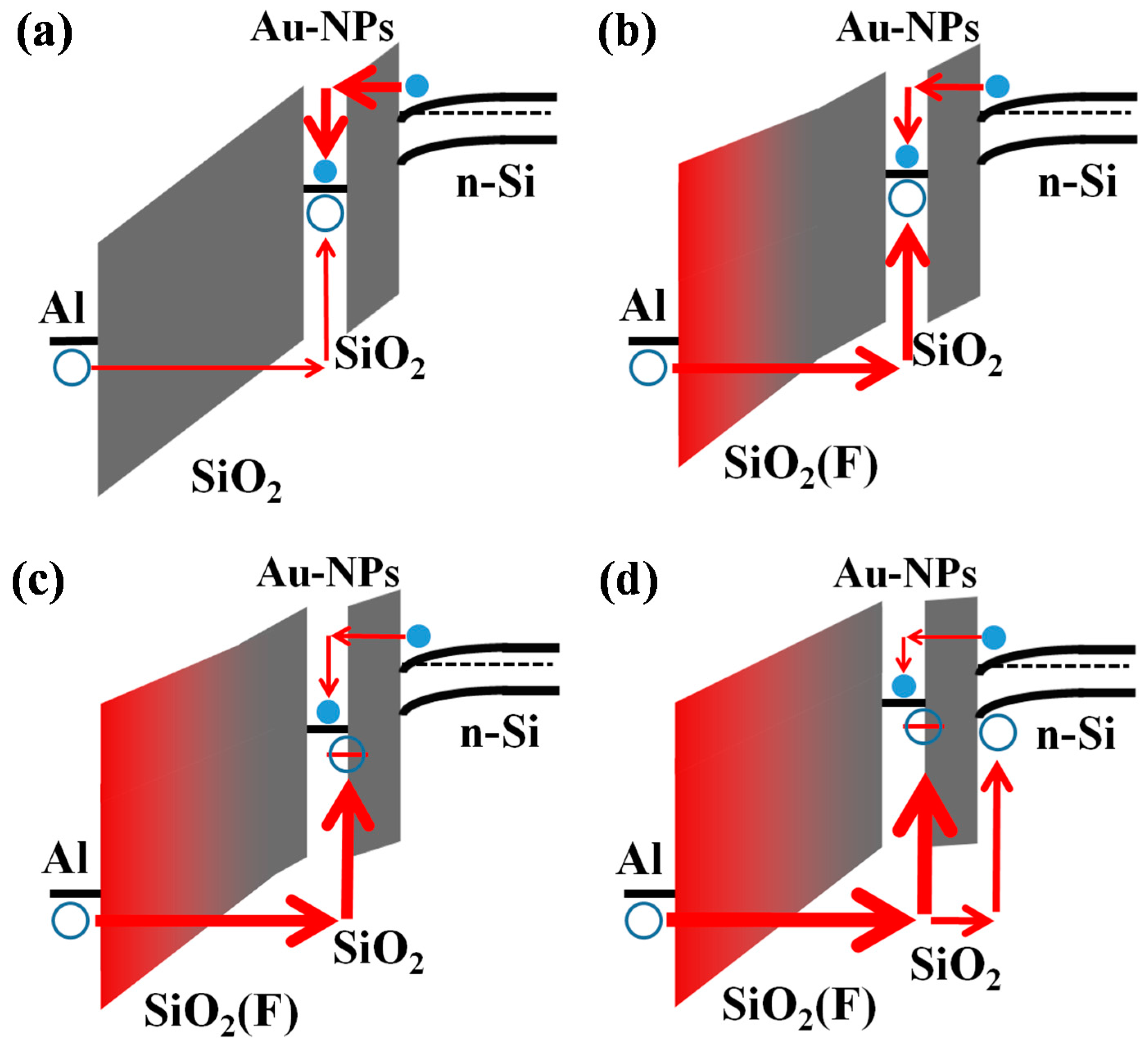

3.3. Carrier Injection Mechanisms

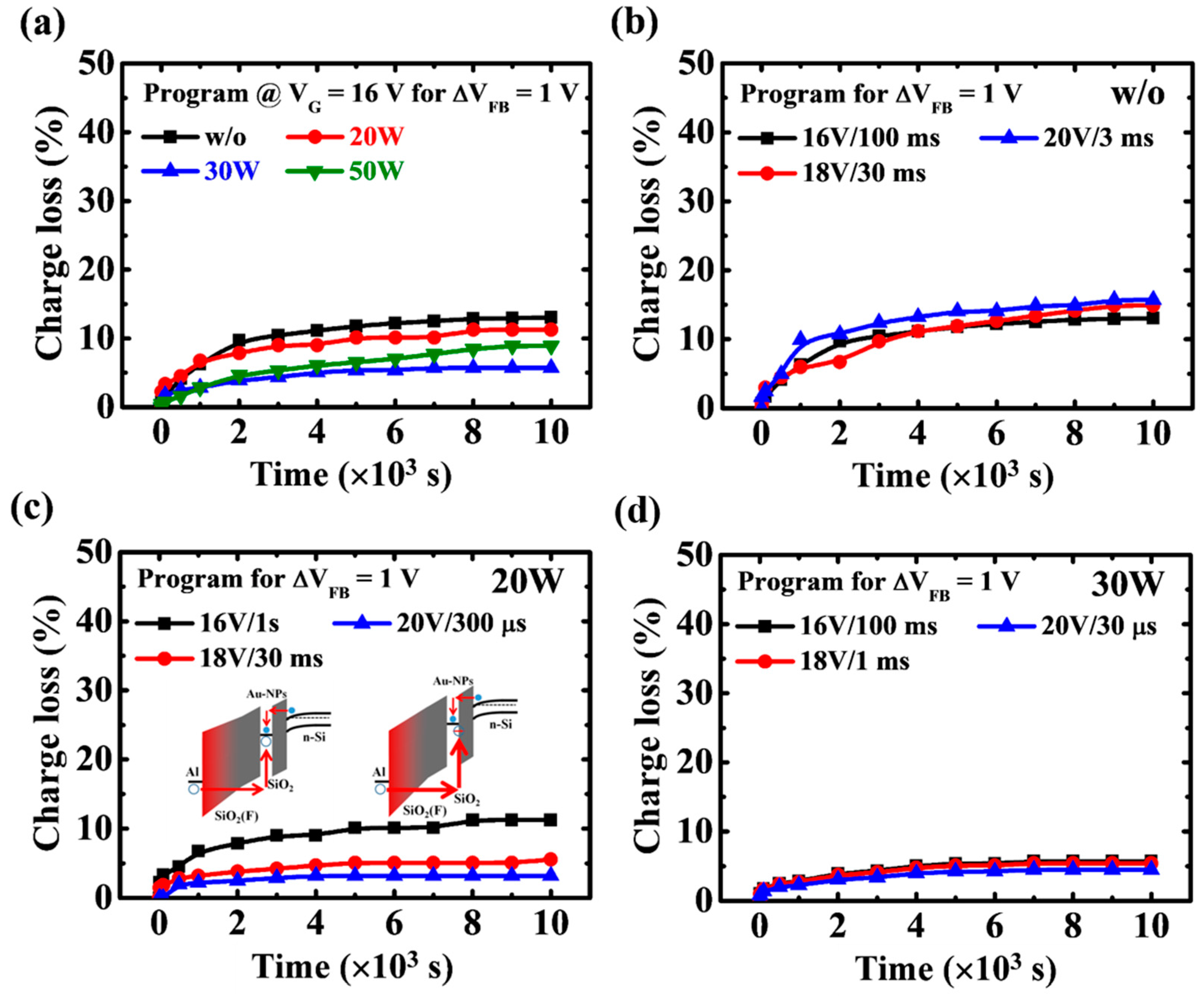

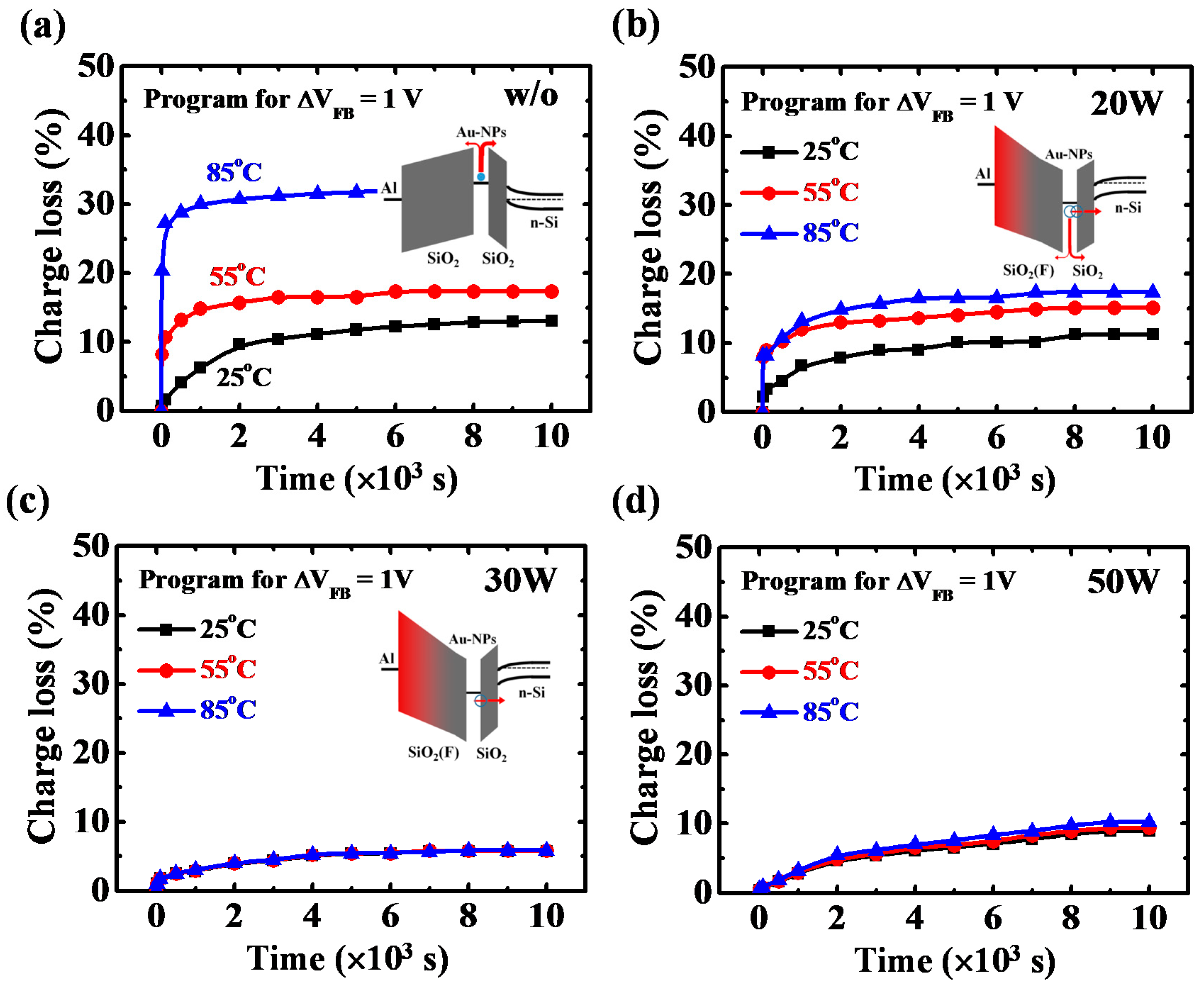

3.4. Data Retention Behaviors

4. Conclusions

Supplementary Materials

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Kimura, S. Advanced non-volatile embedded memory for a wide range of applications. In Proceedings of the IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016. [Google Scholar]

- Micheloni, R.; Picca, M.; Amato, S.; Schwalm, H.; Scheppler, M.; Commodaro, S. Non-volatile memories for removable media. Proc. IEEE 2009, 97, 148–160. [Google Scholar] [CrossRef]

- Chang, T.C.; Jian, F.Y.; Chen, S.C.; Tsai, Y.T. Developments in nanocrystal memory. Mater. Today 2011, 14, 608–615. [Google Scholar] [CrossRef]

- Tiwari, S.; Rana, F.; Hanafi, H.; Hartstein, A.; Crabbe, E.F.; Chan, K. A silicon nanocrystals based memory. Appl. Phys. Lett. 1996, 68, 1377–1379. [Google Scholar] [CrossRef]

- You, H.C.; Hsu, T.H.; Ko, F.H.; Huang, J.W.; Yang, W.L.; Lei, T.F. SONOS-type flash memory using an HfO2 as a charge trapping layer deposited by the sol–gel spin-coating method. IEEE Electron Device Lett. 2006, 27, 653–655. [Google Scholar]

- Compagnoni, C.M.; Ielmini, D.; Spinelli, A.S.; Lacaita, A.L.; Previtali, C.; Gerardi, C. Study of data retention for nanocrystal Flash memories. In Proceedings of the IEEE International Reliability Physics Symposium, Dallas, TX, USA, 30 March–4 April 2003. [Google Scholar]

- Jiang, D.; Huo, Z.; Zhang, M.; Jin, L.; Bai, J.; Yu, Z.; Liu, J.; Wang, Q.; Yang, X.; Wang, Y.; et al. A novel junction-assisted programming scheme for Si-nanocrystal memory devices with improved performance. Semicond. Sci. Technol. 2011, 26, 115008. [Google Scholar] [CrossRef]

- Chen, W.R.; Chang, T.C.; Hsieh, Y.T.; Chang, C.Y. Formation and nonvolatile memory application of Ge nanocrystals by using internal competition reaction of Si1.33Ge0.67 and Si2.67Ge1.33N2 layers. IEEE Trans. Nanotechnol. 2009, 8, 185–189. [Google Scholar]

- Wang, J.C.; Lai, C.S.; Chen, Y.K.; Lin, C.T.; Liu, C.P.; Huang, R.S.M.; Fang, Y.C. Characteristics of Gadolinium oxide nanocrystal memory with optimized rapid thermal annealing. Electrochem. Solid State Lett. 2009, 12, H202–H204. [Google Scholar] [CrossRef]

- Wang, J.C.; Lin, C.T.; Lai, C.S.; Hsu, J.L.; Ai, C.F. Improved characteristics of Gd2O3 nanocrystal memory with substrate high–low junction. Solid-State Electron. 2010, 54, 1493–1496. [Google Scholar] [CrossRef]

- Liu, Z.; Lee, C.; Narayanan, V.; Pei, G.; Kan, E.C. Metal nanocrystal memories—Part II: Electrical characteristics. IEEE Trans. Electron Devices 2002, 49, 1614–1622. [Google Scholar] [CrossRef]

- Marino, L.; Marino, S.; Wang, D.; Bruno, E.; Scaramuzza, N. Nonvolatile memory effects in an orthoconic smectic liquid crystal mixture doped with polymercapped gold nanoparticles. Soft Matter 2014, 10, 3842–3849. [Google Scholar] [CrossRef] [PubMed]

- Lue, H.T.; Lai, E.K.; Wang, S.Y.; Yang, L.W.; Yang, T.; Chen, K.C.; Hsieh, K.Y.; Liu, R.; Lu, C.Y. A novel gate-injection program/erase p-channel NAND-type flash memory with high (10M cycle) endurance. In Proceedings of the IEEE Symposium on VLSI Technology, Kyoto, Japan, 12–14 June 2007. [Google Scholar]

- Wang, J.C.; Chang, K.P.; Liao, C.H.; Chang, R.D.; Lai, C.S.; Chang, L.C. Low-damage NH3 plasma treatment on SiO2 tunneling oxide of chemically-synthesized gold nanoparticle nonvolatile memory. Curr. Appl. Phys. 2016, 16, 605–610. [Google Scholar] [CrossRef]

- Huang, C.H.; Lin, C.T.; Wang, J.C.; Chou, C.; Ye, Y.R.; Cheng, B.M.; Lai, C.S. Tunable bandgap energy of fluorinated nanocrystals for flash memory applications produced by low-damage plasma treatment. Nanotechnology 2012, 23, 475201. [Google Scholar] [CrossRef] [PubMed]

- Liu, Z.; Lee, C.; Narayanan, V.; Pei, G.; Kan, E.C. Metal nanocrystal memories—Part I: Device design and fabrication. IEEE Trans. Electron Dev. 2002, 49, 1606–1613. [Google Scholar] [CrossRef]

- Campbell, C.T. Ultrathin metal films and particles on oxide surfaces: Structural, electronic and chemisorptive properties. Surf. Sci. Rep. 1997, 27, 1–111. [Google Scholar] [CrossRef]

- Zinke-Allmang, M.; Feldman, L.C.; Grabow, M.H. Clustering on surfaces. Surf. Sci. Rep. 1992, 16, 377–463. [Google Scholar] [CrossRef]

- Venables, J.A.; Spiller, G.D.T.; Hanbucken, M. Nucleation and growth of thin films. Rep. Prog. Phys. 1984, 47, 399–459. [Google Scholar] [CrossRef]

- Zhang, L.; Cosandey, F.; Persaud, R.; Madey, T.E. Initial growth and morphology of thin Au films on TiO2(110). Surf. Sci. 1999, 439, 73–85. [Google Scholar] [CrossRef]

- Ruffino, F.; Crupi, I.; Irrera, A.; Grimaldi, M.G. Pd/Au/SiC nanostructured diodes for nanoelectronics: Room temperature electrical properties. IEEE Trans. Nanotechnol. 2010, 9, 414–421. [Google Scholar] [CrossRef]

- Ruffino, F.; Torrisi, V.; Marletta, G.; Grimaldi, M.G. Effects of the embedding kinetics on the surface nano-morphology of nano-grained Au and Ag films on PS and PMMA layers annealed above the glass transition temperature. Appl. Phys. A 2012, 107, 669–683. [Google Scholar] [CrossRef]

- Thompson, C.V. Solid-state dewetting of thin films. Annu. Rev. Mater. Res. 2012, 42, 399–434. [Google Scholar] [CrossRef]

- Ruffino, F.; Grimaldi, M.G. Self-organized patterned arrays of Au and Ag nanoparticles by thickness-dependent dewetting of template-confined films. J. Mater. Sci. 2014, 49, 5714–5729. [Google Scholar] [CrossRef]

- Gadkari, P.R.; Warren, A.P.; Todi, R.M.; Petrova, R.V.; Coffey, K.R. Comparison of the agglomeration behavior of thin metallic films on SiO2. J. Vac. Sci. Technol. A 2005, 23, 1152–1161. [Google Scholar] [CrossRef]

- Müller, C.M.; Spolenak, R. Dewetting of Au and AuPt alloy films: A dewetting zone model. J. Appl. Phys. 2013, 113, 094301. [Google Scholar] [CrossRef]

- Lin, C.T.; Wang, J.C.; Huang, P.W.; Chen, Y.Y.; Chang, L.C. Performance revelation and optimization of gold nanocrystal for future nonvolatile memory application. Jpn. J. Appl. Phys. 2013, 52, 04CJ09. [Google Scholar] [CrossRef]

- Yoo, J.H.; Yang, J.M. Cross-sectional transmission electron microscopy specimen preparation technique by backside Ar ion milling. Appl. Microsc. 2015, 45, 189–194. [Google Scholar] [CrossRef]

- Chang, C.W.; Deng, C.K.; Wu, S.C.; Huang, J.J.; Chang, H.R.; Lei, T.F. Characterizing fluorine-ion implant effects on poly-Si thin-film transistors with Pr2O3 gate dielectric. J. Disp. Technol. 2008, 4, 173–179. [Google Scholar] [CrossRef]

- Matsuo, P.J.; Standaert, T.E.F.M.; Allen, S.D.; Oehrlein, G.S. Characterization of Al, Cu, and TiN surface cleaning following a low-K dielectric etch. J. Vac. Sci. Technol. B 1999, 17, 1435–1447. [Google Scholar] [CrossRef]

- Baggetto, L.; Mohanty, D.; Meisner, R.A.; Bridges, C.A.; Daniel, C.; Wood III, D.L.; Dudneya, N.J.; Veith, G.M. Degradation mechanisms of lithium-rich nickel manganese cobalt oxide cathode thin films. RSC Adv. 2014, 4, 23364–23371. [Google Scholar] [CrossRef]

- Martinez, E.; Leroux, C.; Benedetto, N.; Gaumer, C.; Charbonnier, M.; Licitra, C.; Guedj, C.; Fillot, F.; Lhostis, S. Electrical and chemical properties of the HfO2/SiO2/Si stack: Impact of HfO2 thickness and thermal budget. J. Electrochem. Soc. 2009, 156, G120–G124. [Google Scholar] [CrossRef]

- Wang, J.C.; Liao, C.H.; Lin, C.T.; Chang, R.D.; Chang, L.C.; Wu, C.I.; Chang, J.H. Charge storage characteristics of nonvolatile memories with chemically-synthesized and vacuum-deposited gold nanoparticles. Curr. Appl. Phys. 2015, 15, 535–540. [Google Scholar] [CrossRef]

- Wang, S.D.; Lo, W.H.; Lei, T.F. CF4 plasma treatment for fabricating high-performance and reliable solid-phase-crystallized poly-Si TFTs. J. Electrochem. Soc. 2005, 152, G703–G706. [Google Scholar] [CrossRef]

- Usami, T.; Shimokawa, K.; Yoshimaru, M. Low dielectric constant interlayer using fluorine-doped silicon oxide. Jpn. J. Appl. Phys. 1994, 33, 408–412. [Google Scholar] [CrossRef]

- Teramoto, A.; Saito, M.; Suwa, T.; Narita, T.; Kuroda, R.; Sugawa, S. Hole-trapping process at Al2O3/GaN interface formed by atomic layer deposition. IEEE Electron Device Lett. 2017, 38, 1309–1312. [Google Scholar] [CrossRef]

- Schroder, D.K. Semiconductor Material and Device Characterization, 2nd ed.; John Wiley & Sons, Inc.: New York, NY, USA, 1998. [Google Scholar]

- Achuthan, M.K.; Bhat, K.N. Fundamentals of Semiconductor Devices, 1st ed.; Tata McGraw-Hill Education Pvt. Ltd.: New Delhi, India, 2006. [Google Scholar]

- Robertson, J.; Wallace, R.M. High-k materials and metal gates for CMOS applications. Mater. Sci. Eng. R-Rep. 2015, 88, 1–41. [Google Scholar] [CrossRef] [Green Version]

- Mishra, U.; Singh, J. Semiconductor Device Physics and Design, 1st ed.; Springer: Dordrecht, The Netherlands, 2008. [Google Scholar]

- Wang, J.C.; Lin, C.T.; Huang, P.W.; Lai, C.S.; Chang, L.C.; Wu, C.I.; Chang, J.H. Hybrid polarity and carrier injection of gold and gadolinium oxide binanocrystals structure. Appl. Phys. Lett. 2013, 102, 083507. [Google Scholar] [CrossRef]

- Yeo, Y.C.; Ranade, P.; King, T.J.; Hu, C. Effects of high-k gate dielectric materials on metal and silicon gate workfunctions. IEEE Electron Device Lett. 2002, 23, 342–344. [Google Scholar]

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, Y.-H.; Kao, C.-H.; Cheng, T.-C.; Wu, C.-I.; Wang, J.-C. Data Retention Characterization of Gate-Injected Gold-Nanoparticle Non-Volatile Memory with Low-Damage CF4-Plasma-Treated Blocking Oxide Layer. Nanomaterials 2017, 7, 385. https://doi.org/10.3390/nano7110385

Liu Y-H, Kao C-H, Cheng T-C, Wu C-I, Wang J-C. Data Retention Characterization of Gate-Injected Gold-Nanoparticle Non-Volatile Memory with Low-Damage CF4-Plasma-Treated Blocking Oxide Layer. Nanomaterials. 2017; 7(11):385. https://doi.org/10.3390/nano7110385

Chicago/Turabian StyleLiu, Yu-Hua, Chyuan-Haur Kao, Tsung-Chin Cheng, Chih-I Wu, and Jer-Chyi Wang. 2017. "Data Retention Characterization of Gate-Injected Gold-Nanoparticle Non-Volatile Memory with Low-Damage CF4-Plasma-Treated Blocking Oxide Layer" Nanomaterials 7, no. 11: 385. https://doi.org/10.3390/nano7110385