A Standard-Cell-Based CMFB for Fully Synthesizable OTAs

Abstract

:1. Introduction

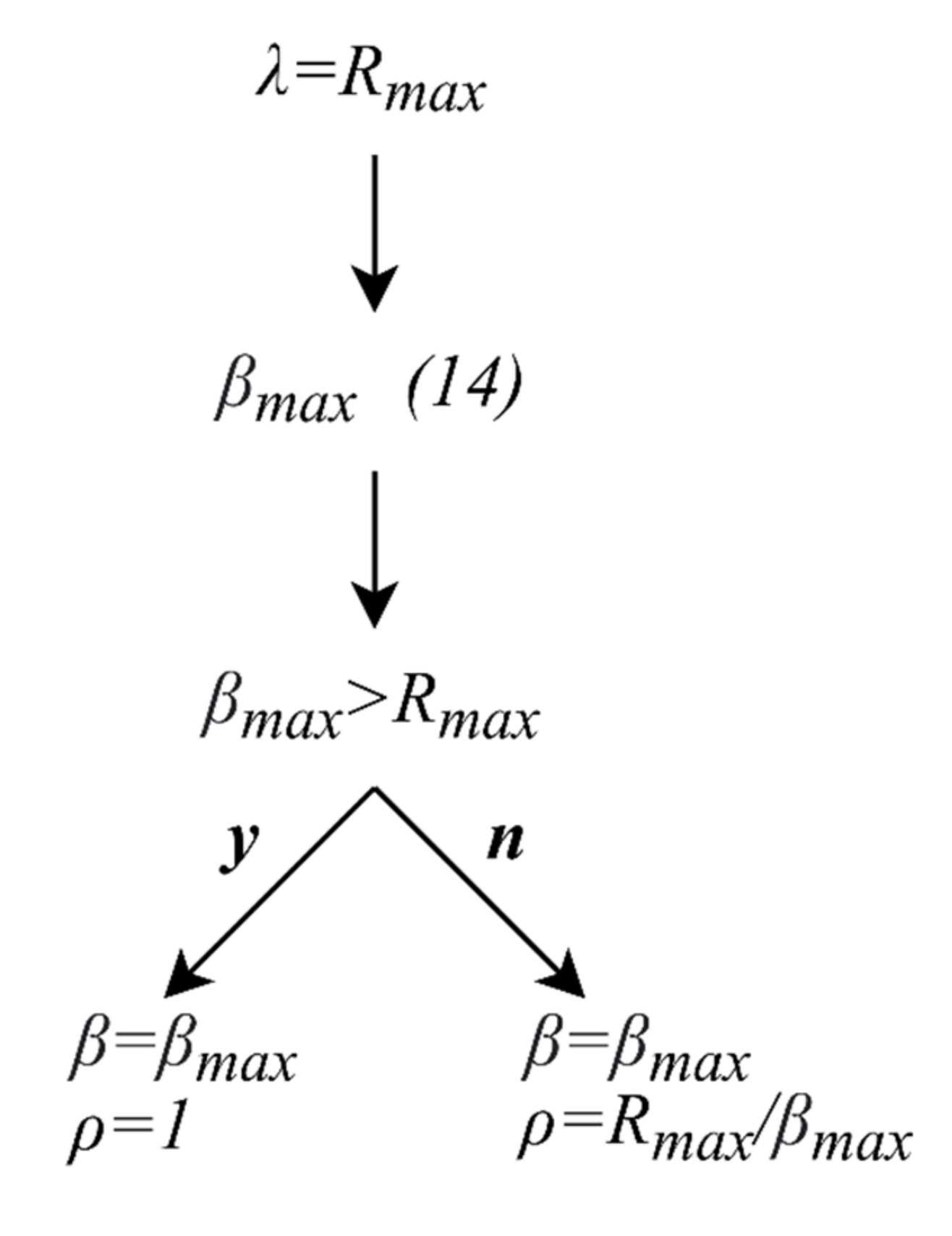

2. The Proposed CMFB

3. Standard-Cell-Based OTA

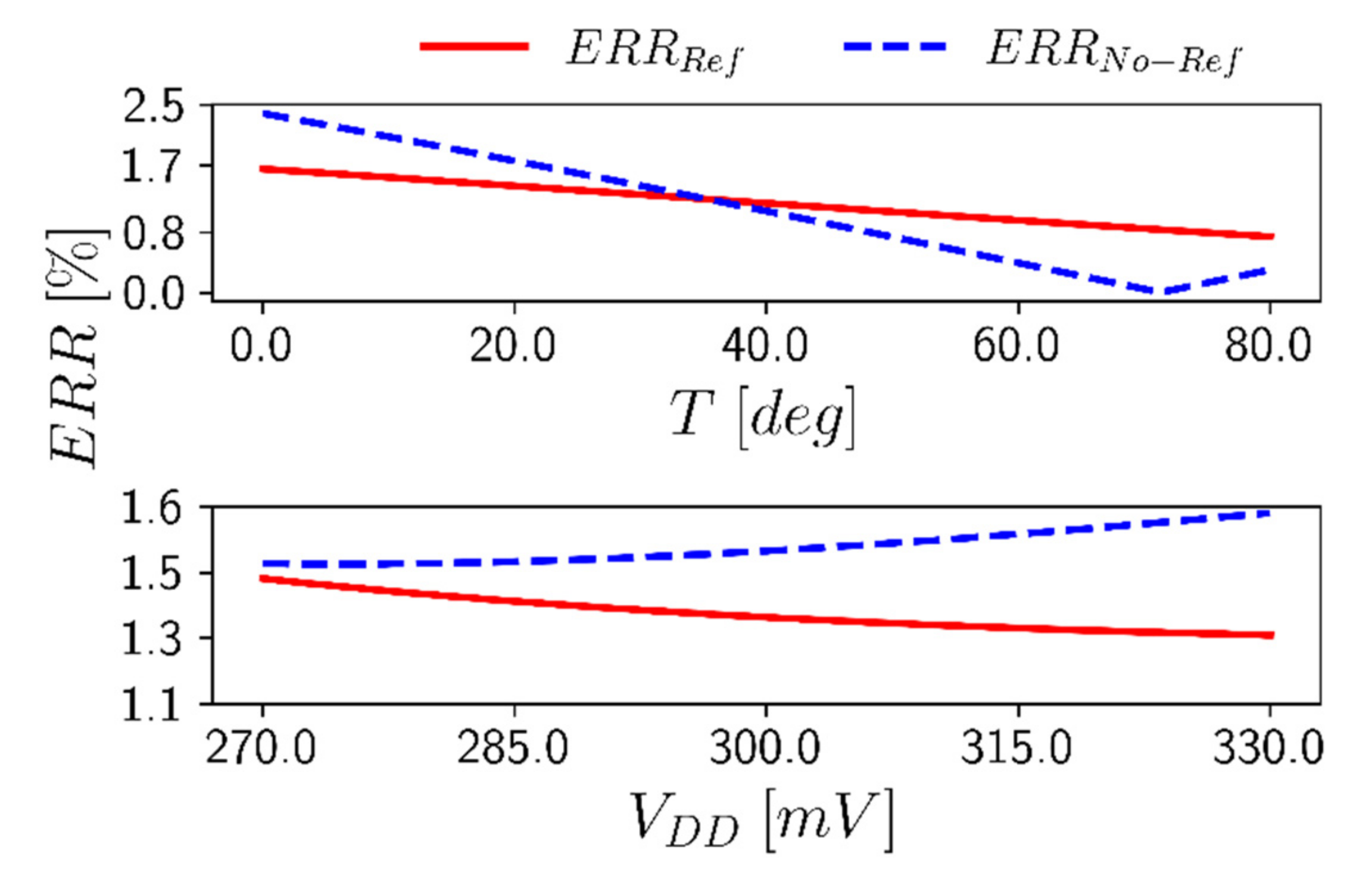

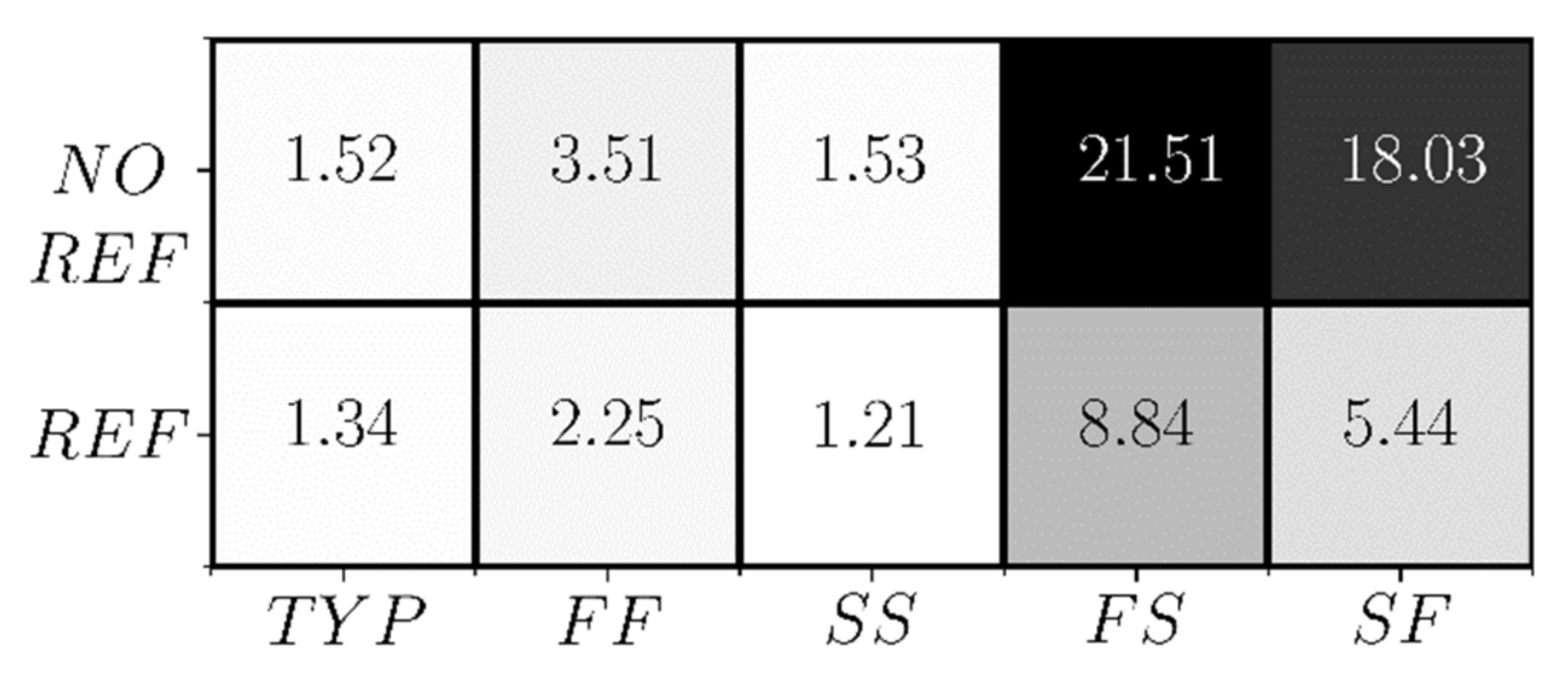

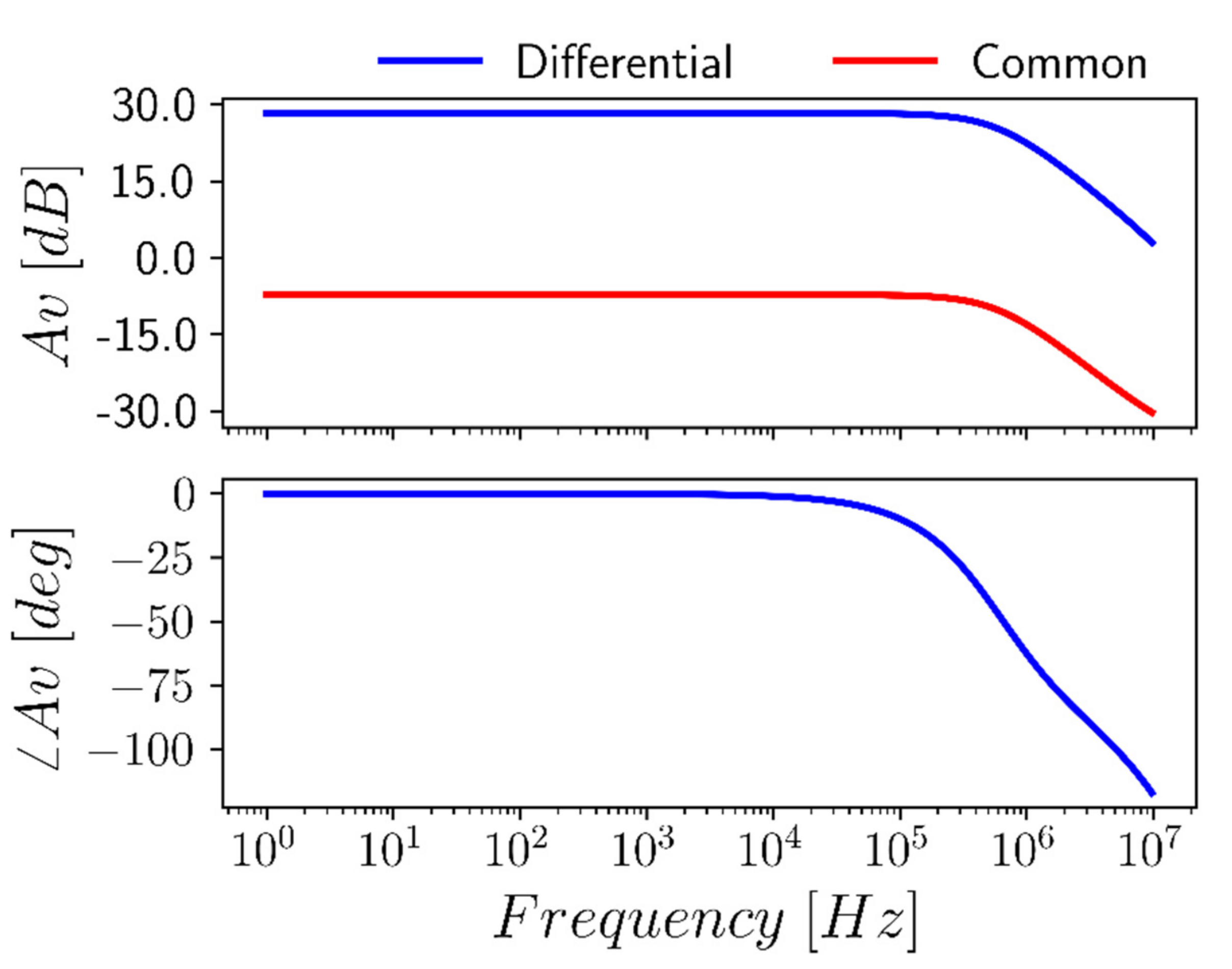

4. Simulation Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

Appendix A

References

- Chatterjee, S.; Tsividis, Y.; Kinget, P. 0.5-V analog circuit techniques and their application in OTA and filter design. IEEE J. Solid State Circuits 2005, 40, 2373–2387. [Google Scholar] [CrossRef]

- Ferreira, L.; Sonkusale, S.R. A 60-dB Gain OTA Operating at 0.25-V Power Supply in 130-nm Digital CMOS Process. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 1609–1617. [Google Scholar] [CrossRef]

- Abdelfattah, O.; Roberts, G.W.; Shih, I.; Shih, Y.-C. An Ultra-Low-Voltage CMOS Process-Insensitive Self-Biased OTA with Rail-to-Rail Input Range. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 2380–2390. [Google Scholar] [CrossRef]

- Akbari, M.; Hashemipour, O. A 63-dB gain OTA operating in subthreshold with 20-nW power consumption. Int. J. Circuit Theory Appl. 2017, 45, 843–850. [Google Scholar] [CrossRef]

- Richelli, A.; Colalongo, L.; Kovacs-Vajna, Z.; Calvetti, G.; Ferrari, D.; Finanzini, M.; Pinetti, S.; Prevosti, E.; Savoldelli, J.; Scarlassara, S. A Survey of Low Voltage and Low Power Amplifier Topologies. J. Low Power Electron. Appl. 2018, 8, 22. [Google Scholar] [CrossRef] [Green Version]

- Veldandi, H.; Shaik, R.A. A 0.3-V Pseudo-Differential Bulk-Input OTA for Low-Frequency Applications. Circuits Syst. Signal Process. 2018, 37, 5199–5221. [Google Scholar] [CrossRef]

- Grasso, A.D.; Pennisi, S. Ultra-Low Power Amplifiers for IoT Nodes. In Proceedings of the 2018 25th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Bordeaux, France, 9–12 December 2018. [Google Scholar]

- Kulej, T.; Khateb, F. A Compact 0.3-V Class AB Bulk-Driven OTA. IEEE Trans. Very Large Scale Integr. Syst. 2020, 28, 224–232. [Google Scholar] [CrossRef]

- Renteria-Pinon, M.; Ramirez-Angulo, J.; Diaz-Sanchez, A. Simple Scheme for the Implementation of Low Voltage Fully Differential Amplifiers without Output Common-Mode Feedback Network. J. Low Power Electron. Appl. 2020, 10, 34. [Google Scholar] [CrossRef]

- Woo, K.-C.; Yang, B.-D. A 0.25V Rail-to-Rail Three-Stage OTA with an Enhanced DC Gain. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 1179–1183. [Google Scholar] [CrossRef]

- Kulej, T.; Khateb, F. A 0.3-V 98-dB Rail-to-Rail OTA in 0.18 μ m CMOS. IEEE Access 2020, 8, 27459–27467. [Google Scholar] [CrossRef]

- Deo, N.; Sharan, T.; Dubey, T. Subthreshold biased enhanced bulk-driven double recycling current mirror OTA. Analog Integr. Circuits Signal Process. 2020, 105, 229–242. [Google Scholar] [CrossRef]

- Centurelli, F.; Sala, R.D.; Scotti, G.; Trifiletti, A. A 0.3 V, Rail-to-Rail, Ultralow-Power, Non-Tailed, Body-Driven, Sub-Threshold Amplifier. Appl. Sci. 2021, 11, 2528. [Google Scholar] [CrossRef]

- Centurelli, F.; Sala, R.D.; Monsurrò, P.; Scotti, G.; Trifiletti, A. A 0.3 V rail-to-rail ultra-low-power OTA with improved bandwidth and slew rate. J. Low Power Electron. Appl. 2021, 11, 19. [Google Scholar] [CrossRef]

- Dong, S.; Wang, Y.; Tong, X.; Wang, Y.; Liu, C. A 0.3-V 8.72-nW OTA with Bulk-Driven Low-Impedance Compensation for Ultra-Low Power Applications. Circuits Syst. Signal Process. 2021, 40, 2209–2227. [Google Scholar] [CrossRef]

- Ghosh, S.; Bhadauria, V. An ultra-low-power near rail-to-rail pseudo-differential subthreshold gate-driven OTA with improved small and large signal performances. Analog Integr. Circuits Signal Process. 2021, 109, 345–366. [Google Scholar] [CrossRef]

- Centurelli, F.; Sala, R.D.; Monsurrò, P.; Tommasino, P.; Trifiletti, A. An ultra-low-voltage class-AB OTA exploiting local CMFB and body-to-gate interface. AEU Int. J. Electron. Commun. 2022, 145, 154081. [Google Scholar] [CrossRef]

- Centurelli, F.; Sala, R.D.; Monsurrò, P.; Scotti, G.; Trifiletti, A. A tree-based architecture for high-performance ultra-low-voltage amplifiers. J. Low Power Electron. Appl. 2022, 12, 12. [Google Scholar] [CrossRef]

- Ng, K.A.; Xu, Y.P. A Low-Power, High CMRR Neural Amplifier System Employing CMOS Inverter-Based OTAs with CMFB Through Supply Rails. IEEE J. Solid State Circuits 2016, 51, 724–737. [Google Scholar]

- Giustolisi, G.; Palumbo, G. A gm/ID-based design strategy for IoT and ultra-low-power OTAs with fast-settling and large capacitive loads. J. Low Power Electron. Appl. 2021, 11, 21. [Google Scholar] [CrossRef]

- Silva, R.S.; Rodovalho, L.H.; Aiello, O.; Rodrigues, C.R. A 1.9 nW, Sub-1 V, 542 pA/V Linear Bulk-Driven OTA with 154 dB CMRR for Bio-Sensing Applications. J. Low Power Electron. Appl. 2021, 11, 40. [Google Scholar] [CrossRef]

- Vafaei, M.; Parhizgar, A.; Abiri, E.; Salehi, M.R. A low power and ultra-high input impedance analog front end based on fully differential difference inverter-based amplifier for biomedical applications. AEU Int. J. Electron. Commun. 2021, 142, 154005. [Google Scholar] [CrossRef]

- Newton, S.M.; Kinget, P.R. A 4th-order analog continuous-time filter designed using standard cells and automatic digital logic design tools. In Proceedings of the 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, Canada, 22–25 May 2016. [Google Scholar]

- Liu, J.; Park, B.; Guzman, M.; Fahmy, A.; Kim, T.; Maghari, N. A Fully Synthesized 77-dB SFDR Reprogrammable SRMC Filter Using Digital Standard Cells. IEEE Trans. Very Large Scale Integr. Syst. 2018, 26, 1126–1138. [Google Scholar] [CrossRef]

- Toledo, P.; Rubino, G.R.; Musolino, F.; Crovetti, P. Re-Thinking Analog Integrated Circuits in Digital Terms: A New Design Concept for the IoT Era. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 816–822. [Google Scholar] [CrossRef]

- Drost, B.; Talegaonkar, M.; Hanumolu, P.K. Analog Filter Design Using Ring Oscillator Integrators. IEEE J. Solid State Circuits 2012, 47, 3120–3129. [Google Scholar] [CrossRef]

- Hsu, C.-W.; Kinget, P.R. A 40MHz 4th-order active-UGB-RC filter using VCO-based amplifiers with zero compensation. In Proceedings of the ESSCIRC 2014—40th European Solid State Circuits Conference (ESSCIRC), Venice, Italy, 22–26 September 2014; pp. 359–362. [Google Scholar]

- Kalani, S.; Bertolini, A.; Richelli, A.; Kinget, P.R. A 0.2V 492nW VCO-based OTA with 60 kHz UGB and 207 μVrms noise. In Proceedings of the 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017. [Google Scholar]

- Crovetti, P. A Digital-Based Analog Differential Circuit. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 3107–3116. [Google Scholar] [CrossRef]

- Palumbo, G.; Scotti, G. A Novel Standard-Cell-Based Implementation of the Digital OTA Suitable for Automatic Place and Route. J. Low Power Electron. Appl. 2021, 11, 42. [Google Scholar] [CrossRef]

- Toledo, P.; Crovetti, P.; Aiello, O.; Alioto, M. Design of Digital OTAs with Operation Down to 0.3 V and nW Power for Direct Harvesting. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 3693–3706. [Google Scholar] [CrossRef]

- Nauta, B. A CMOS transconductance-C filter technique for very high frequencies. IEEE J. Solid-State Circuits 1992, 27, 142–153. [Google Scholar] [CrossRef] [Green Version]

- Barthélemy, H.; Meillère, S.; Gaubert, J.; Dehaese, N.; Bourdel, S. OTA based on CMOS inverters and application in the design of tunable bandpass filter. Analog Integr. Circuits Signal Process. 2008, 57, 169–178. [Google Scholar] [CrossRef]

- Vlassis, S. 0.5 V CMOS inverter-based tunable transconductor. Analog Integr. Circuits Signal Process. 2012, 72, 289–292. [Google Scholar] [CrossRef]

- Lv, L.; Zhou, X.; Qiao, Z.; Li, Q. Inverter-Based Subthreshold Amplifier Techniques and Their Application in 0.3-V ΔΣ-Modulators. IEEE J. Solid-State Circuits 2019, 54, 1436–1445. [Google Scholar] [CrossRef]

- Braga, R.A.S.; Ferreira, L.H.C.; Coletta, G.D.; Dutra, O.O. A 0.25-V calibration-less inverter-based OTA for low-frequency Gm-C applications. Microelectron. J. 2019, 83, 62–72. [Google Scholar] [CrossRef]

- Manfredini, G.; Catania, A.; Benvenuti, L.; Cicalini, M.; Piotto, M.; Bruschi, P. Ultra-Low-Voltage Inverter-Based Amplifier with Novel Common-Mode Stabilization Loop. Electronics 2020, 9, 1019. [Google Scholar] [CrossRef]

- Bae, W. CMOS Inverter as Analog Circuit: An Overview. J. Low Power Electron. Appl. 2019, 9, 26. [Google Scholar] [CrossRef] [Green Version]

- Michel, F.; Steyaert, M.S.J. A 250 mV 7.5 μW 61 dB SNDR SC ∆Σ modulator using near-threshold-voltage-biased inverter amplifiers in 130 nm CMOS. IEEE J. Solid State Circuits 2012, 47, 709–721. [Google Scholar] [CrossRef]

- Yang, Z.; Yao, L.; Lian, Y. A 0.5-V 35-μW 85-dB DR double-sampled ∆Σ modulator for audio applications. IEEE J. Solid State Circuits 2012, 47, 722–735. [Google Scholar] [CrossRef]

- Suadet, A.; Kasemsuwan, V. A CMOS inverter-based class-AB pseudo-differential amplifier with current-mode common-mode feedback (CMFB). Analog Integr. Circuits Signal Process. 2013, 74, 387–398. [Google Scholar] [CrossRef]

- Ismail, A.; Mostafa, I. A process-tolerant, low-voltage, inverter-based OTA for continuous-time Σ-∆ ADC. IEEE Trans. Very Large Scale Integr. Syst. 2016, 24, 2911–2917. [Google Scholar] [CrossRef]

- Yeknami, A.F. A 300-mV ∆Σ Modulator Using a Gain-Enhanced, Inverter-Based Amplifier for Medical Implant Devices. J. Low Power Electron. Appl. 2016, 6, 4. [Google Scholar] [CrossRef] [Green Version]

- De Aguirre, P.C.C.; Susin, A.A. PVT compensated inverter-based OTA for low-voltage CT sigma-delta modulators. Electron. Lett. 2018, 54, 1264–1266. [Google Scholar] [CrossRef]

- Baghtash, H.F. A 0.4 V, tail-less, fully differential trans-conductance amplifier: An all inverter-based structure. Analog Integr. Circuits Signal Process. 2020, 104, 1–15. [Google Scholar] [CrossRef]

- Rodovalho, L.; Aiello, O.; Rodrigues, C. Ultra-Low-Voltage Inverter-Based Operational Transconductance Amplifiers with Voltage Gain Enhancement by Improved Composite Transistors. Electronics 2020, 9, 1410. [Google Scholar] [CrossRef]

- Baghtash, H.F. Bias-stabilized inverter-amplifier: An inspiring solution for low-voltage and low-power applications. Analog Integr. Circuits Signal Process. 2020, 105, 243–248. [Google Scholar] [CrossRef]

- Rodovalho, L.H. Push-pull based operational transconductance amplifier topologies for ultra low voltage supplies. Analog Integr. Circuits Signal Process. 2021, 106, 111–124. [Google Scholar] [CrossRef]

- Lee, S.; Park, S.; Kim, Y.; Kim, Y.; Lee, J.; Lee, J.; Chae, Y. A 0.6-V 86.5-dB DR 40-kHz BW inverter-based continuous-time delta-sigma modulator with PVT-robust body-biasing. IEEE Solid State Circuits Lett. 2021, 4, 178–181. [Google Scholar] [CrossRef]

- Rodovalho, L.; Rodrigues, C.R.; Aiello, O. Self-Biased and Supply-Voltage Scalable Inverter-Based Operational Transconductance Amplifier with Improved Composite Transistors. Electronics 2021, 10, 935. [Google Scholar] [CrossRef]

- Baltolu, A.; Albinet, X.; Chalet, F.; Dallet, D.; Begueret, J.-B. A robust inverter-based amplifier versus PVT for discrete-time integrators. Int. J. Circuit Theory Appl. 2018, 46, 2160–2169. [Google Scholar] [CrossRef]

- Pradeep, R.; Siddharth, R.K.; Kumar, Y.B.N.; Vasantha, M.H. Process corner calibration for standard cell based flash ADC. In Proceedings of the 2019 IEEE International Symposium on Smart Electronic Systems (iSES), Rourkela, India, 16–18 December 2019. [Google Scholar]

- Vieru, R.G.; Ghinea, R. Inverter-based ultra low voltage differential amplifiers. In Proceedings of the 2011 International Semiconductor Conference, Sinaia, Romania, 17–19 October 2011. [Google Scholar]

- Tanimoto, H.; Yazawa, K.; Haraguchi, M. A fully-differential OTA based on CMOS cascode inverters operating from 1-V power supply. Analog Integr. Circuits Signal Process. 2014, 78, 23–31. [Google Scholar] [CrossRef]

- Ruscio, D.; Centurelli, F.; Monsurrò, P.; Trifiletti, A. Reconfigurable low voltage inverter-based sample-and-hold amplifier. In Proceedings of the 2017 13th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Giardini Naxos–Taormina, Italy, 12–15 June 2017. [Google Scholar]

| Corner | FF | SS | FS | SF |

|---|---|---|---|---|

| AVD [dB] | 25.22 | 31.43 | 28.04 | 27.37 |

| GBW [MHz] | 26.4 | 10.24 | 15.28 | 14.57 |

| mφ [°] | 63.38 | 49.18 | 60.59 | 60.28 |

| Pd [μW] | 7.832 | 1.89 | 3.97 | 3.74 |

| VOS [mV] | 0.45 | 0.18 | 0.93 | 0.45 |

| SR [V/μs] | 15.15 | 5.85 | 12.47 | 6.33 |

| Voltage Variations | Temperature Variations | |||

|---|---|---|---|---|

| T [°C] | 27 | 27 | 0 | 80 |

| VDD [mV] | 270 | 330 | 300 | 300 |

| AVD [dB] | 27.28 | 29.03 | 29.25 | 26.32 |

| GBW [MHz] | 10.03 | 23.03 | 9.80 | 29.41 |

| mφ [°] | 59.94 | 52.04 | 52.10 | 58.50 |

| Pd [μW] | 2.65 | 7.15 | 2.38 | 11.21 |

| VOS [mV] | −0.29 | −0.29 | −0.29 | 0.17 |

| SR [V/μs] | 3.61 | 12.52 | 6.91 | 12.88 |

| Mean | Std | |

|---|---|---|

| AVD [dB] | 28.2 | 0.88 |

| GBW [MHz] | 15.78 | 1.91 |

| mϕ [°] | 54.47 | 3.12 |

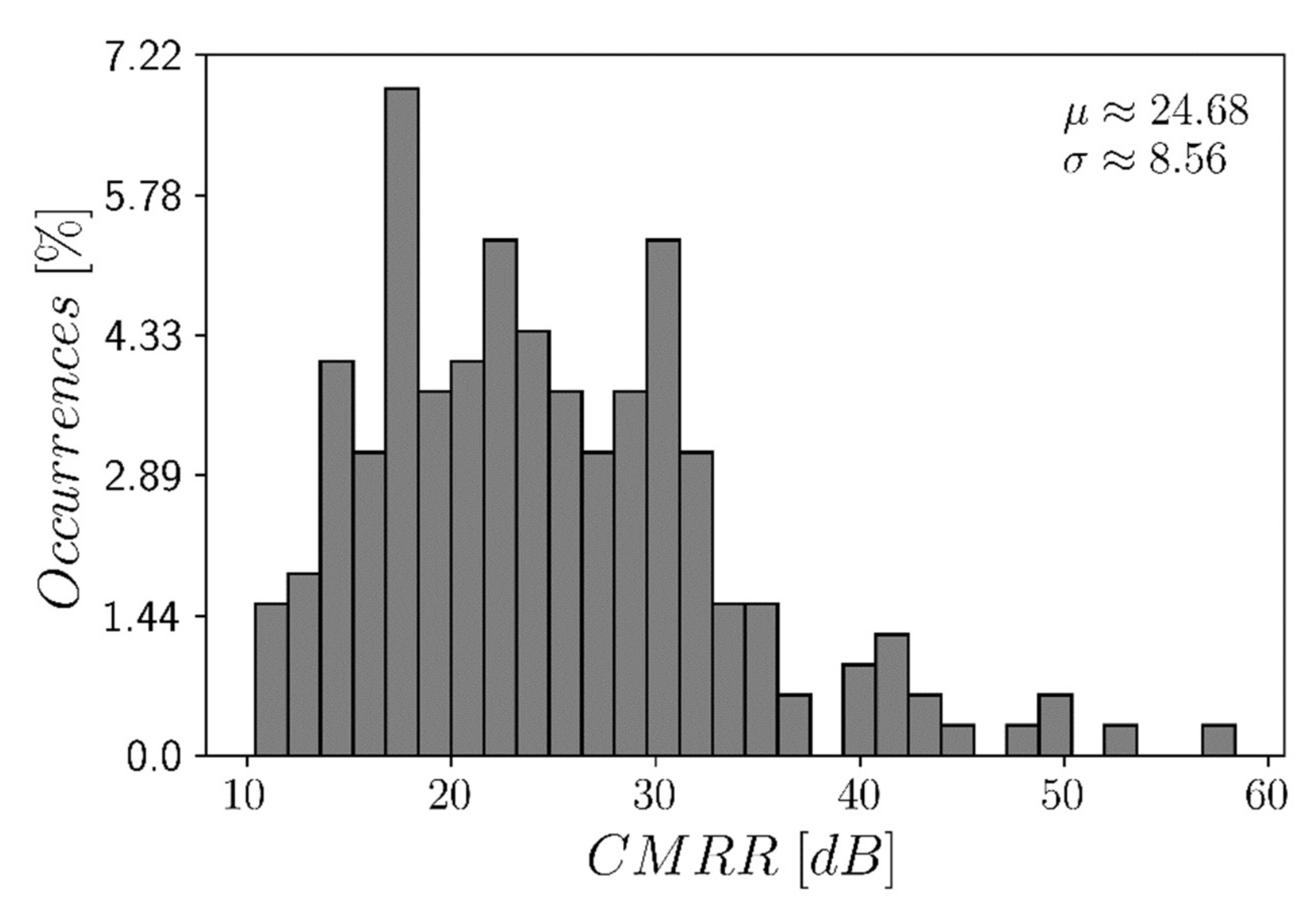

| CMRR [dB] | 24.68 | 8.56 |

| Pd [μW] | 4.49 | 0.11 |

| VOS [mV] | 0.002 | 9.2 |

| SR [V/μs] | 9.12 | 1.02 |

| Ref | This Work | [30] | [31] | [17] | [18] | [46] | [10] | [12] | [35] | [36] | [3] |

|---|---|---|---|---|---|---|---|---|---|---|---|

| Year | 2022 | 2021 | 2021 | 2022 | 2022 | 2020 | 2020 | 2020 | 2019 | 2019 | 2015 |

| Tech. [nm] | 130 | 180 | 180 | 130 | 130 | 180 | 65 | 180 | 130 | 130 | 65 |

| VDD [V] | 0.3 | 0.55 | 0.3 | 0.3 | 0.3 | 0.3 | 0.25 | 0.5 | 0.3 | 0.25 | 0.35 |

| AVD [dB] | 28.3 | 87 | 30 | 38.1 | 52.9 | 39 | 70 | 79.5 | 49.8 | 25 | 43 |

| GBW [kHz] | 15,420 | 3150 | 0.25 | 24.14 | 35.16 | 0.9 | 9.5 | 36 | 9100 | 7.23 | 3600 |

| mφ [°] | 54 | 65 | 90 | 60 | 52 | 90 | 89 | 65 | 76 | 90 | 56 |

| CL [pF] | 1.5 | 250 | 150 | 50 | 50 | 10 | 15 | 15 | 2 | 30 | 3 |

| SRAVG [V/ms] | 9075 | 2.7 | 0.085 | 14.23 | 15.06 | -- | 2 | 9.7 | 3800 | -- | 5600 |

| Pd [nW] | 4406 | 8200 | 2.4 | 59.9 | 21.9 | 0.6 | 26 | 60 | 1800 | 55 | 17,000 |

| Area [μm2] | 164 | 88.3 | 982 | 2700 | 5200 | 472 | 2000 | 3395 | -- | 52,000 | 5000 |

| Type | STD | STD | DIG | BD | BD | IB | BD | BD | IB | IB | BD |

| FOMS [MHz pF/μW] | 5.25 | 96.04 | 15.62 | 20.15 | 80.31 | 15 | 5.48 | 9 | 10.11 | 3.94 | 0.63 |

| FOML [V pF/μs μW] | 3.09 | 0.08 | 5.31 | 11.88 | 34.40 | -- | 1.15 | 2.42 | 4.22 | -- | 0.99 |

| FOMS,A [MHz pF/μW μm2] | 32.01 | 1088 | 15.9 | 7.46 | 15.44 | 31.78 | 2.74 | 2.65 | -- | 0.07 | 0.13 |

| FOML,A [V pF/ms μW μm2] | 18.84 | 0.93 | 5.4 | 4.4 | 6.61 | -- | 0.57 | 0.71 | -- | -- | 0.19 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Centurelli, F.; Della Sala, R.; Scotti, G. A Standard-Cell-Based CMFB for Fully Synthesizable OTAs. J. Low Power Electron. Appl. 2022, 12, 27. https://doi.org/10.3390/jlpea12020027

Centurelli F, Della Sala R, Scotti G. A Standard-Cell-Based CMFB for Fully Synthesizable OTAs. Journal of Low Power Electronics and Applications. 2022; 12(2):27. https://doi.org/10.3390/jlpea12020027

Chicago/Turabian StyleCenturelli, Francesco, Riccardo Della Sala, and Giuseppe Scotti. 2022. "A Standard-Cell-Based CMFB for Fully Synthesizable OTAs" Journal of Low Power Electronics and Applications 12, no. 2: 27. https://doi.org/10.3390/jlpea12020027