A C/X/Ku/K-Band Precision Compact 6-Bit Digital Attenuator with Logic Control Circuits

Abstract

:1. Introduction

- This paper theoretically analyzes the attenuation characteristics of various attenuation cells and their applicable attenuation levels.

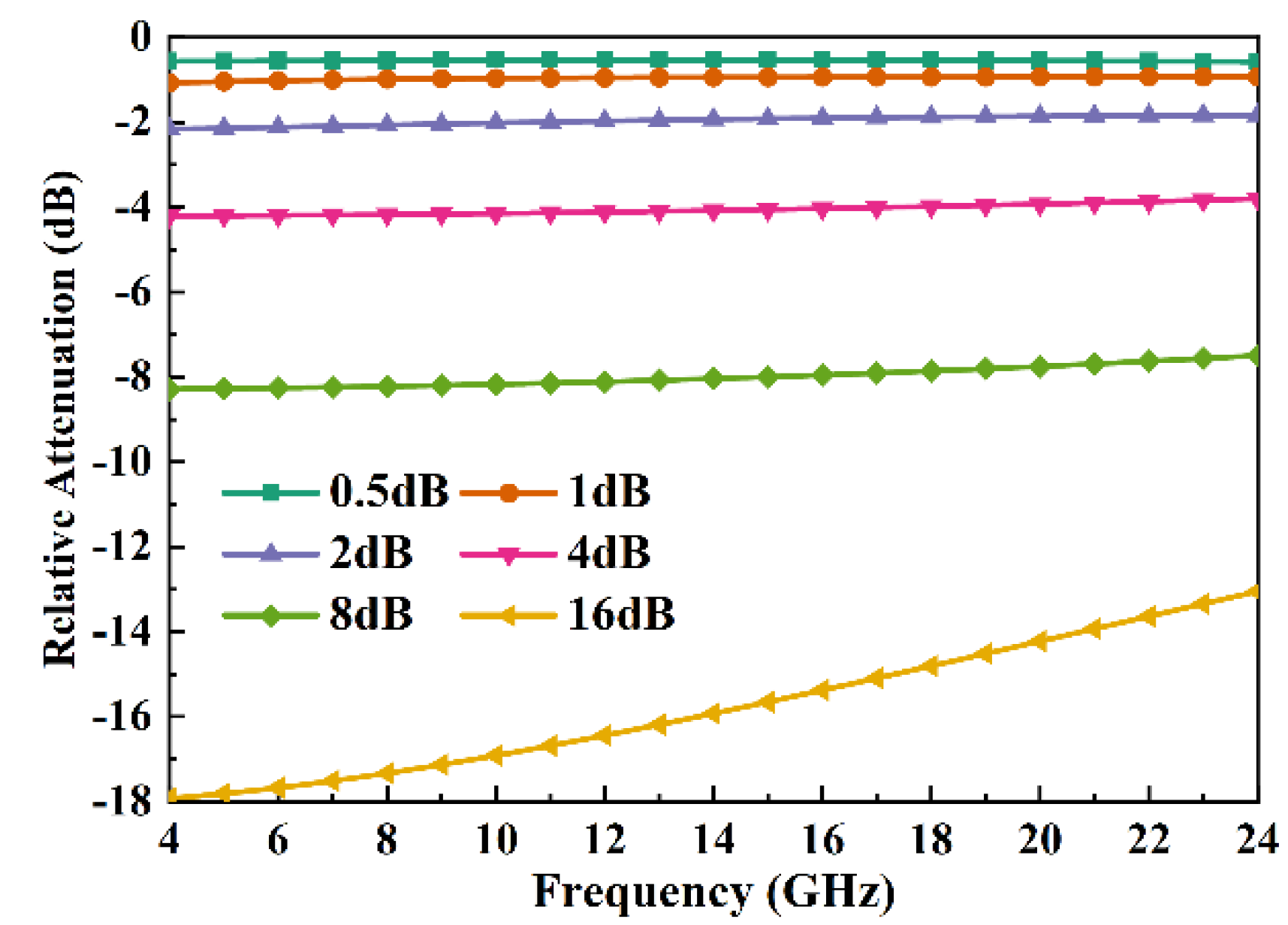

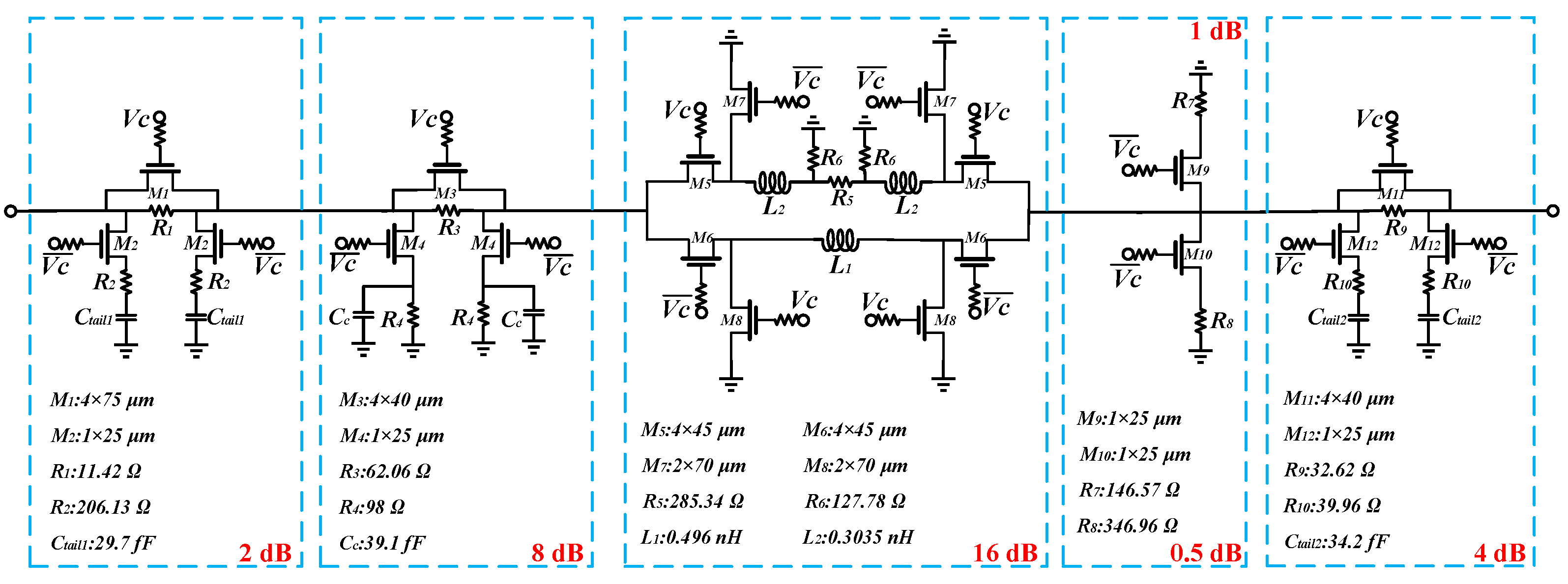

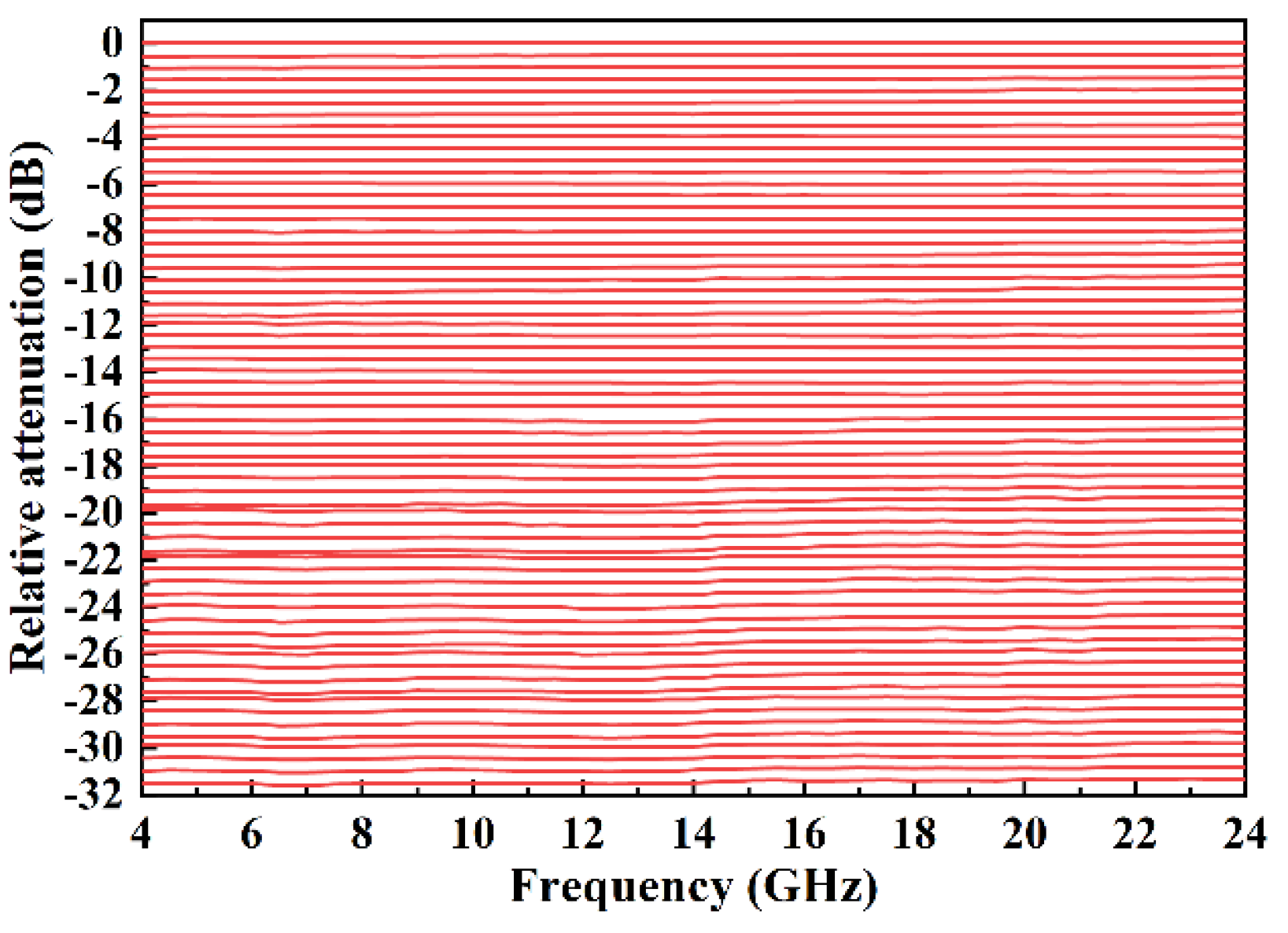

- This paper simplifies the T-type attenuation cell, improves the π-type attenuation cell in two different forms, expands the switched-path attenuation cell, and provides a more reasonable cascade for these attenuation cells. These improvements enable the attenuator to achieve a more excellent performance.

- In order to reduce the complexity of the whole radar system, an on-chip logic control circuit is designed in this paper.

- Finally, this paper designs a broadband precision compact 6-bit digital attenuator with logic control circuits.

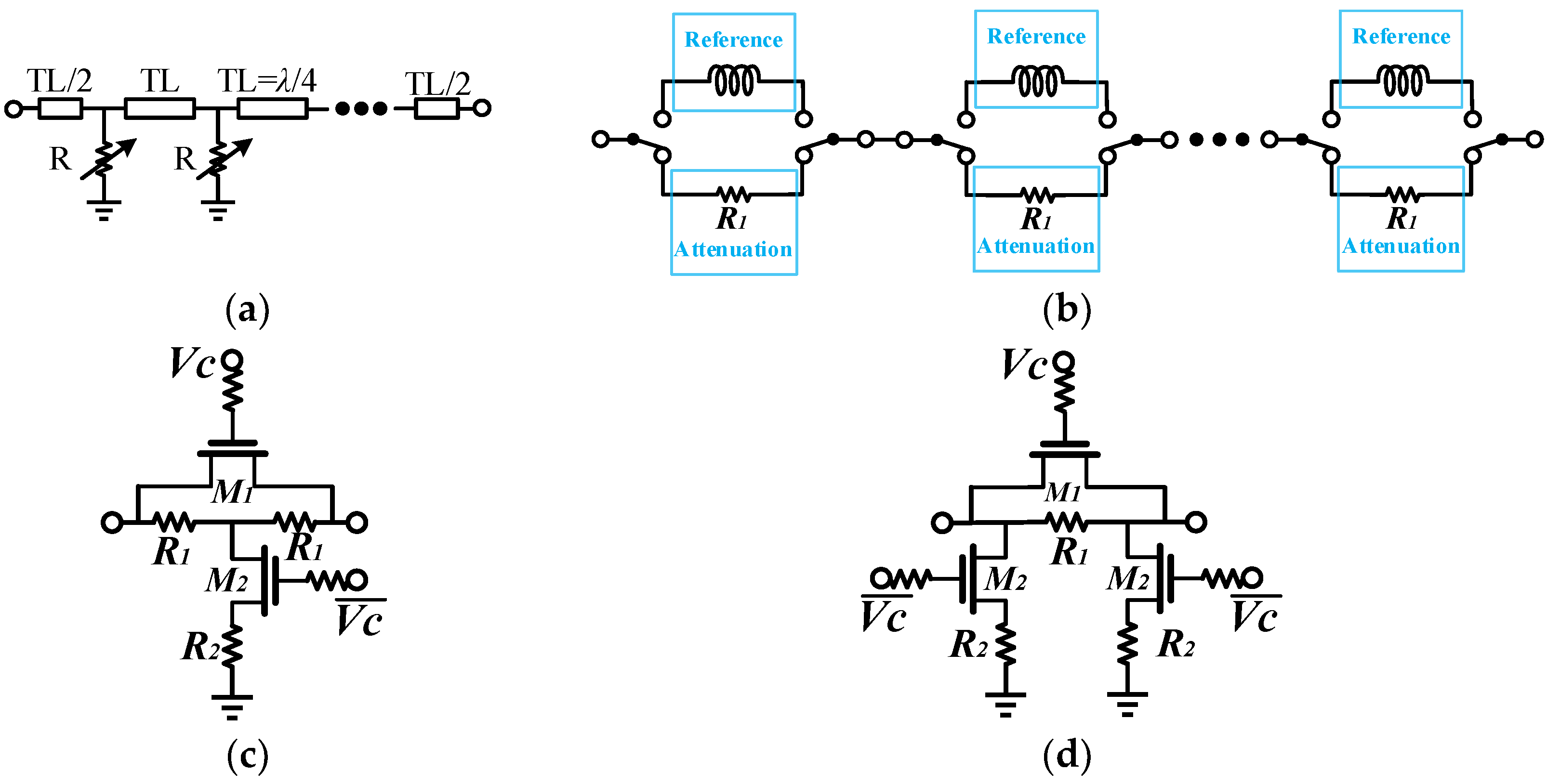

2. Attenuation Cells Analysis and Design

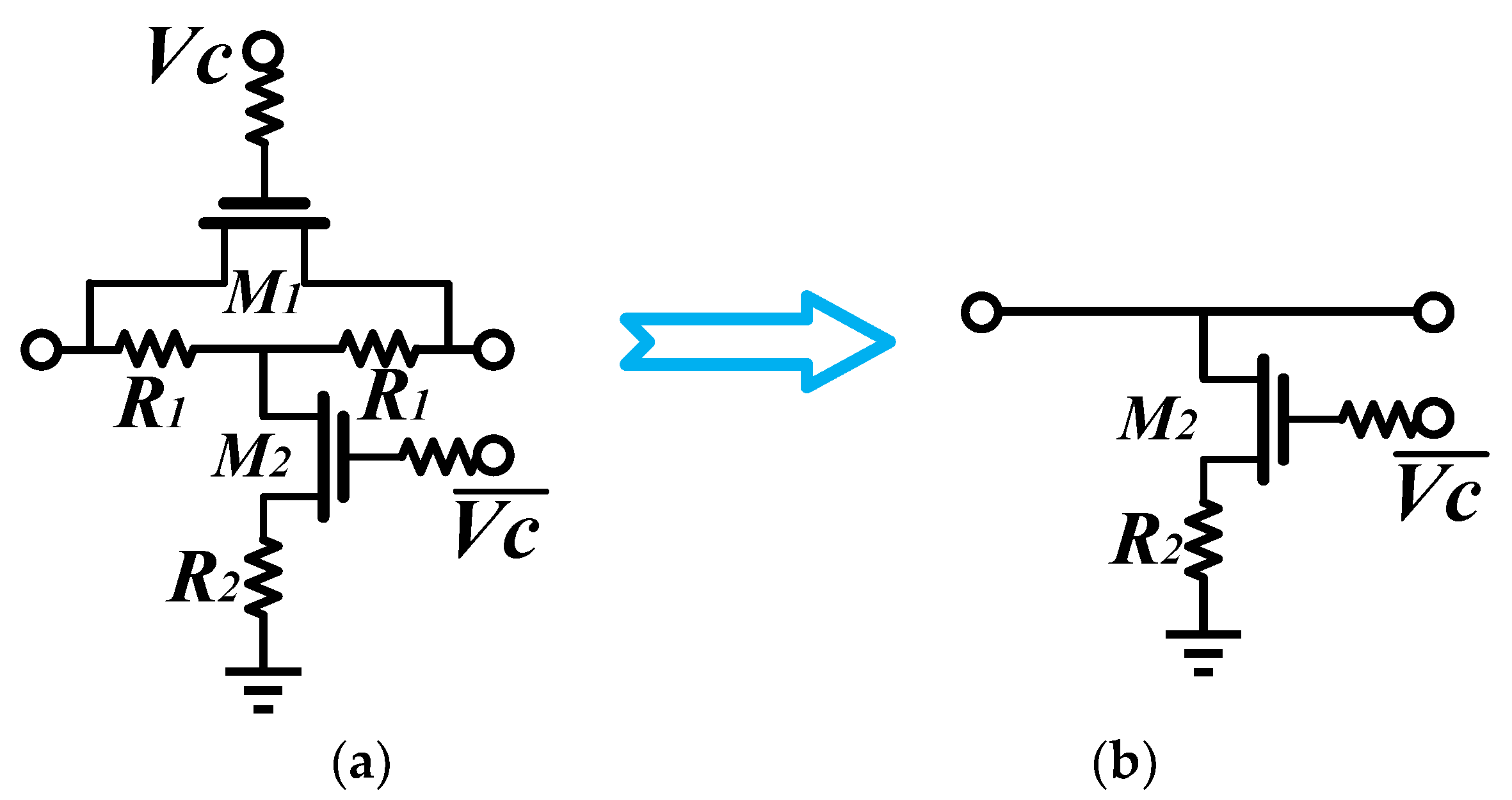

2.1. T-Type Attenuation Cell

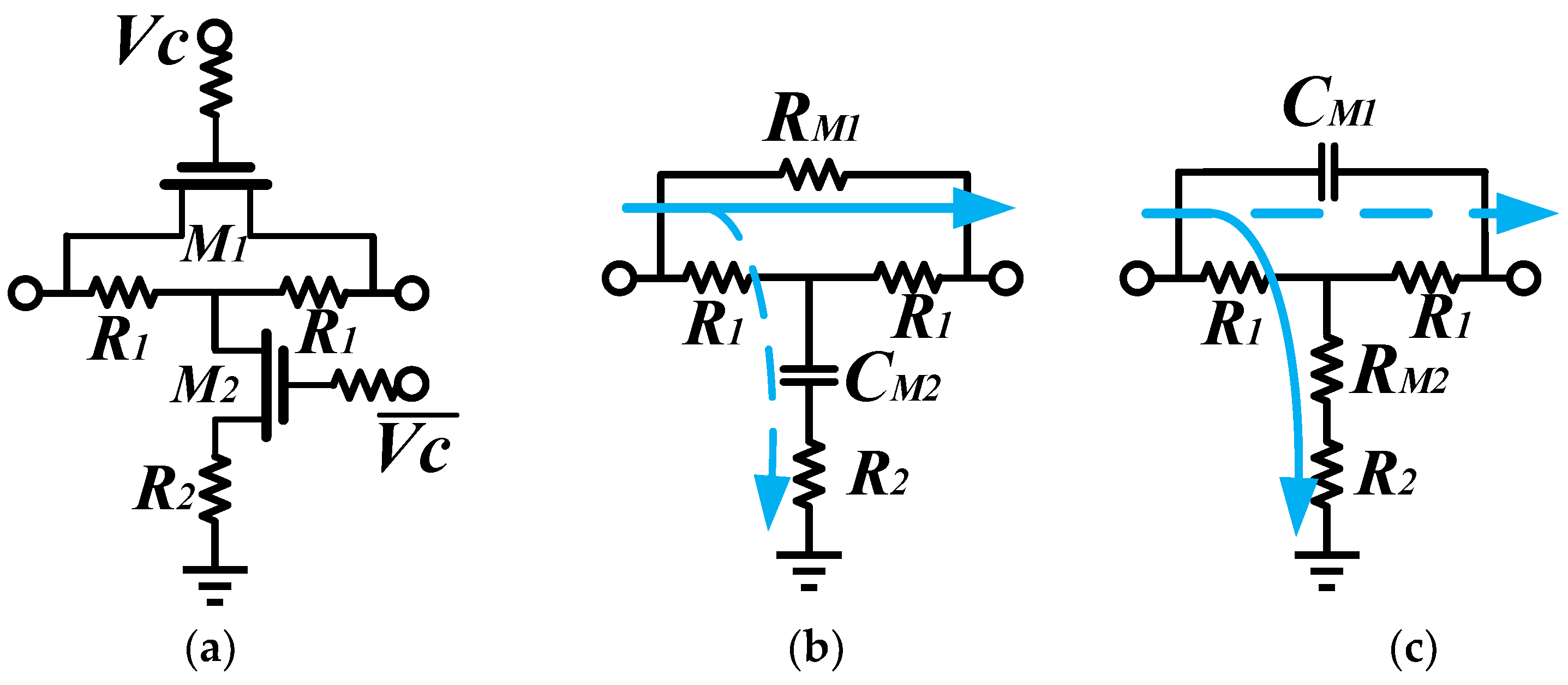

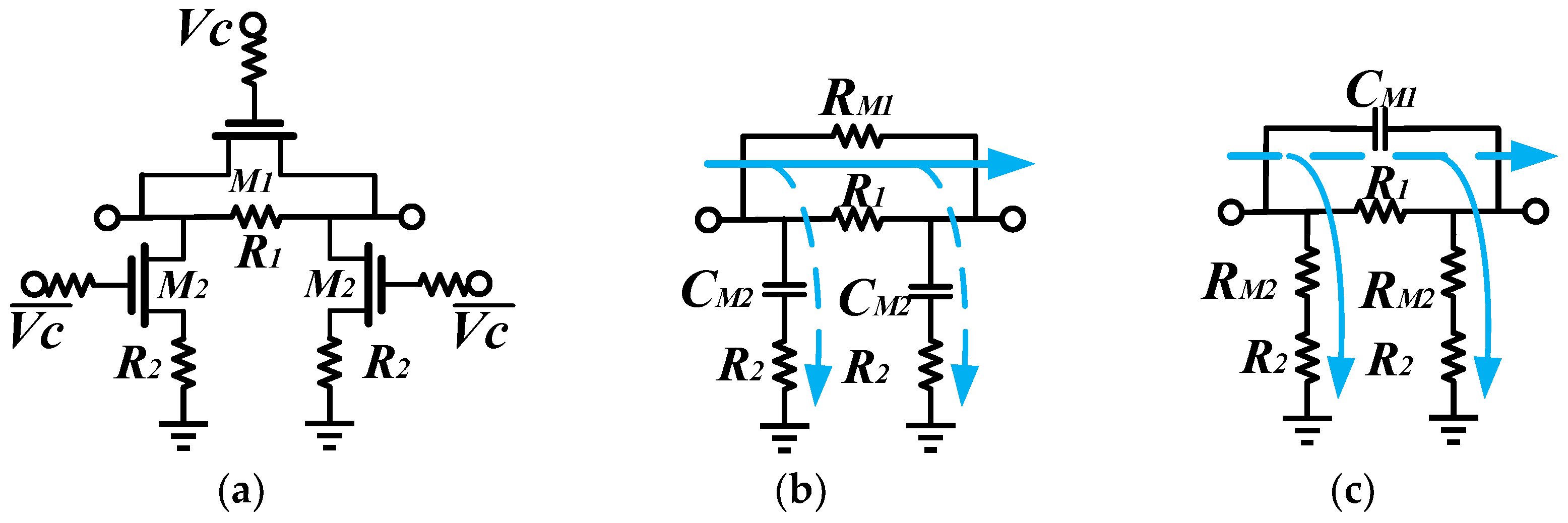

2.2. π-Type Attenuation Cell

2.2.1. Conventional π-Type Attenuation Cell

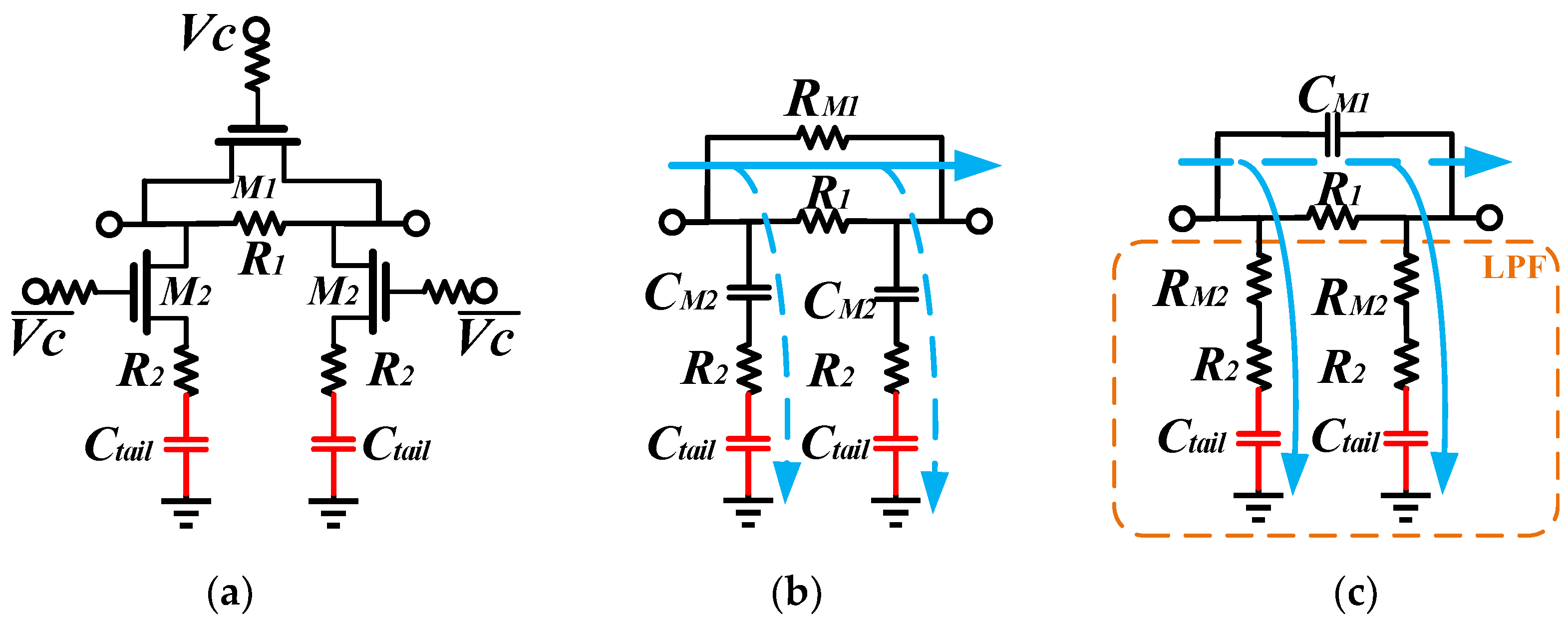

2.2.2. π-Type Attenuation Cell with Tail Capacitors

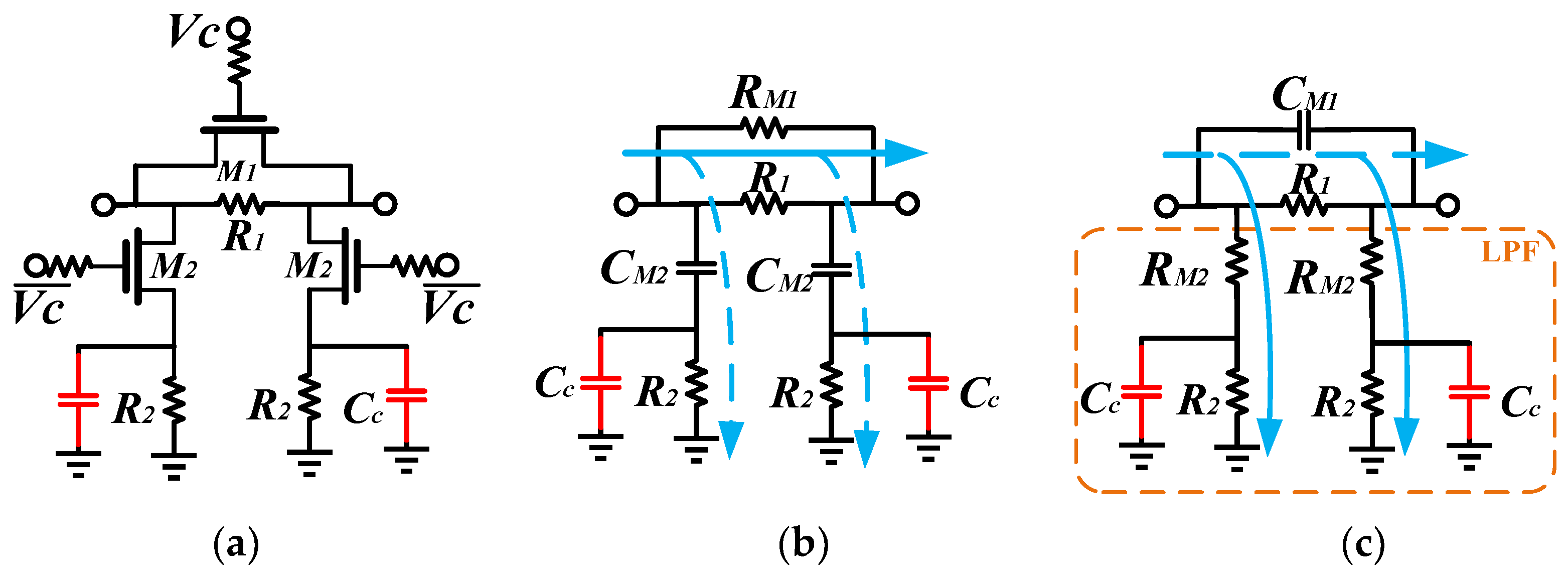

2.2.3. π-Type Attenuation Cell with Shunt Capacitors

2.2.4. Improved π-Type Attenuation Cell Selection

2.3. Switched-Path Type Attenuation Cell

2.4. Cascade of Attenuation Cells

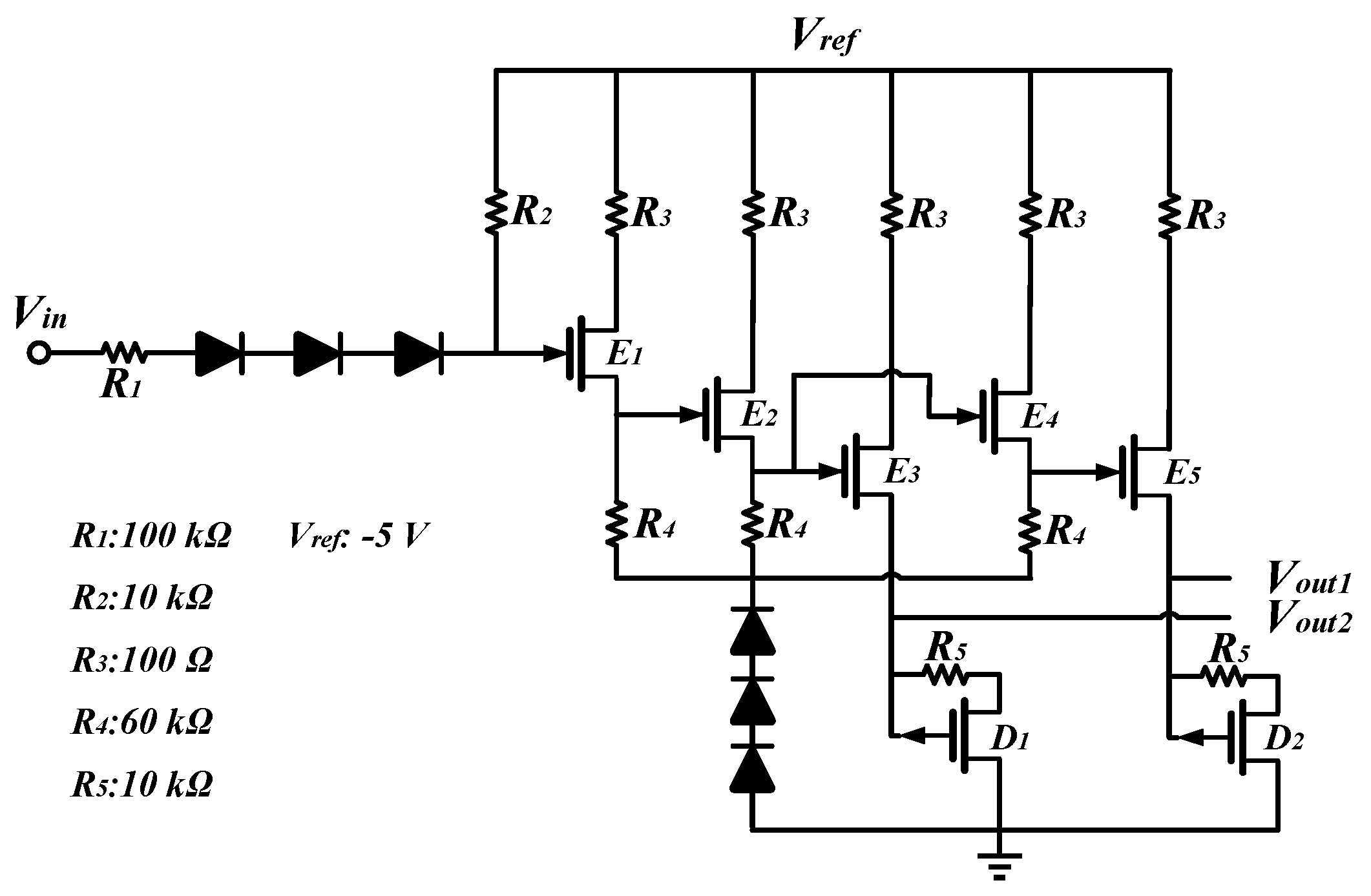

3. Logic Control Circuits

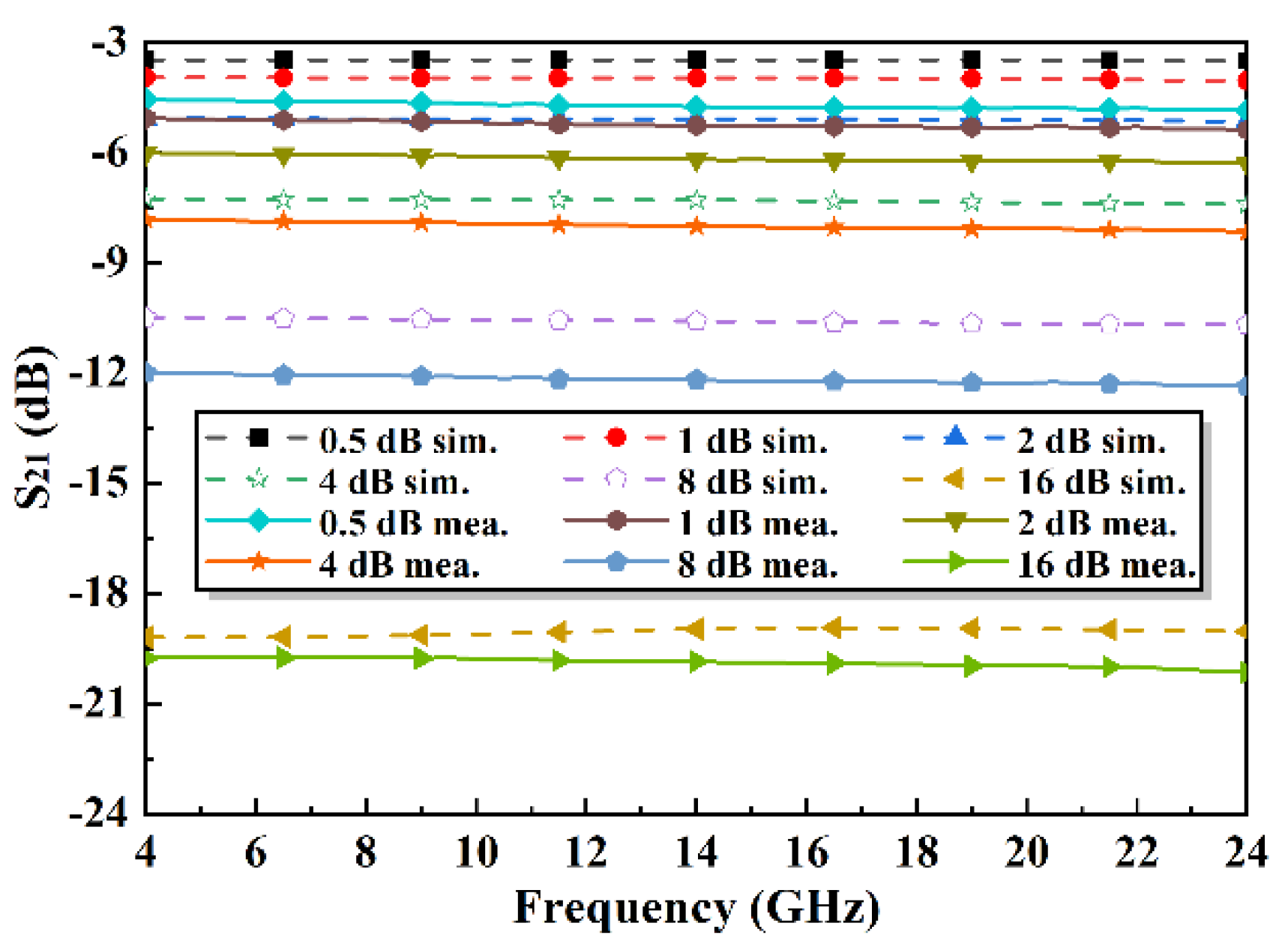

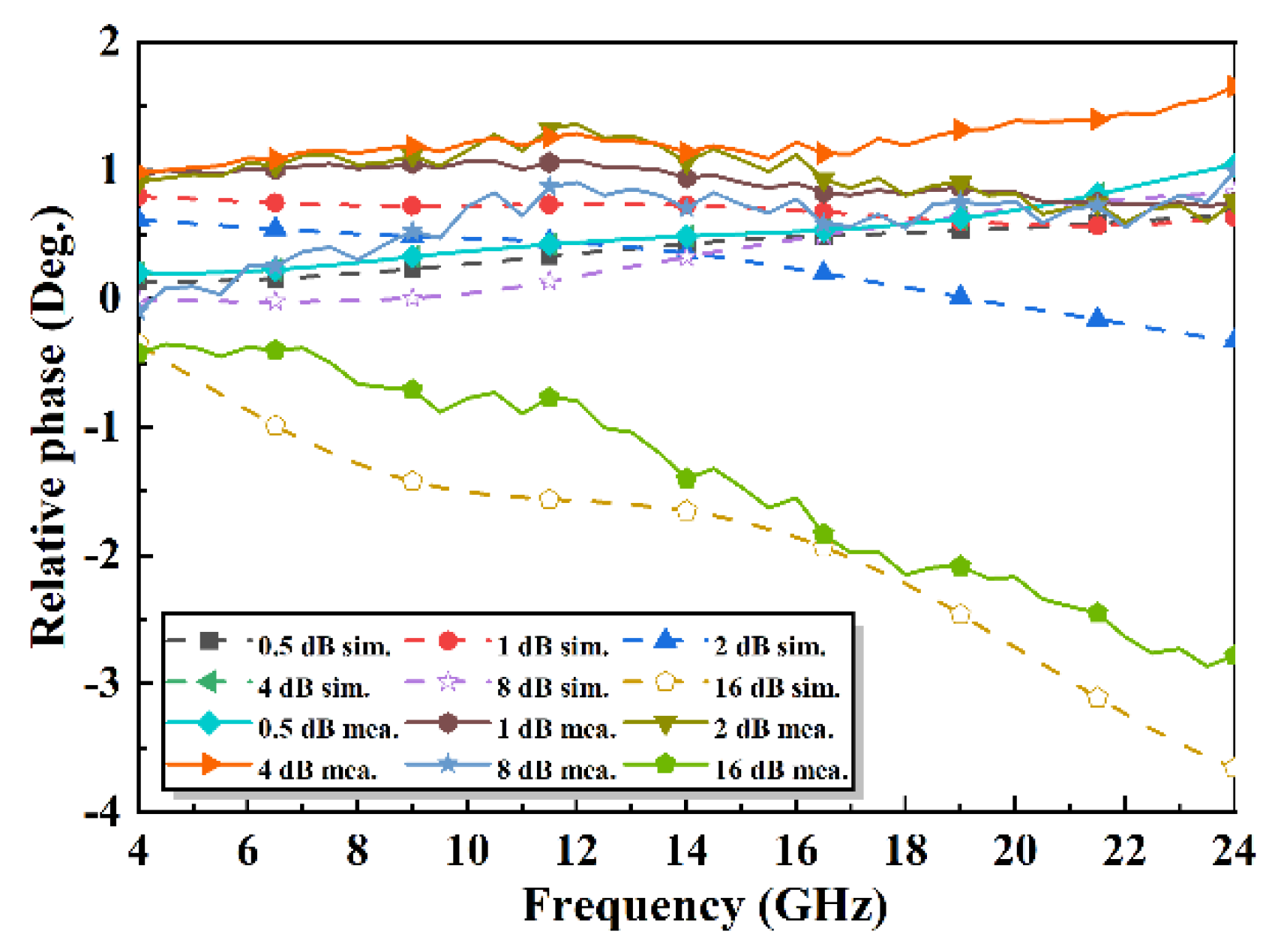

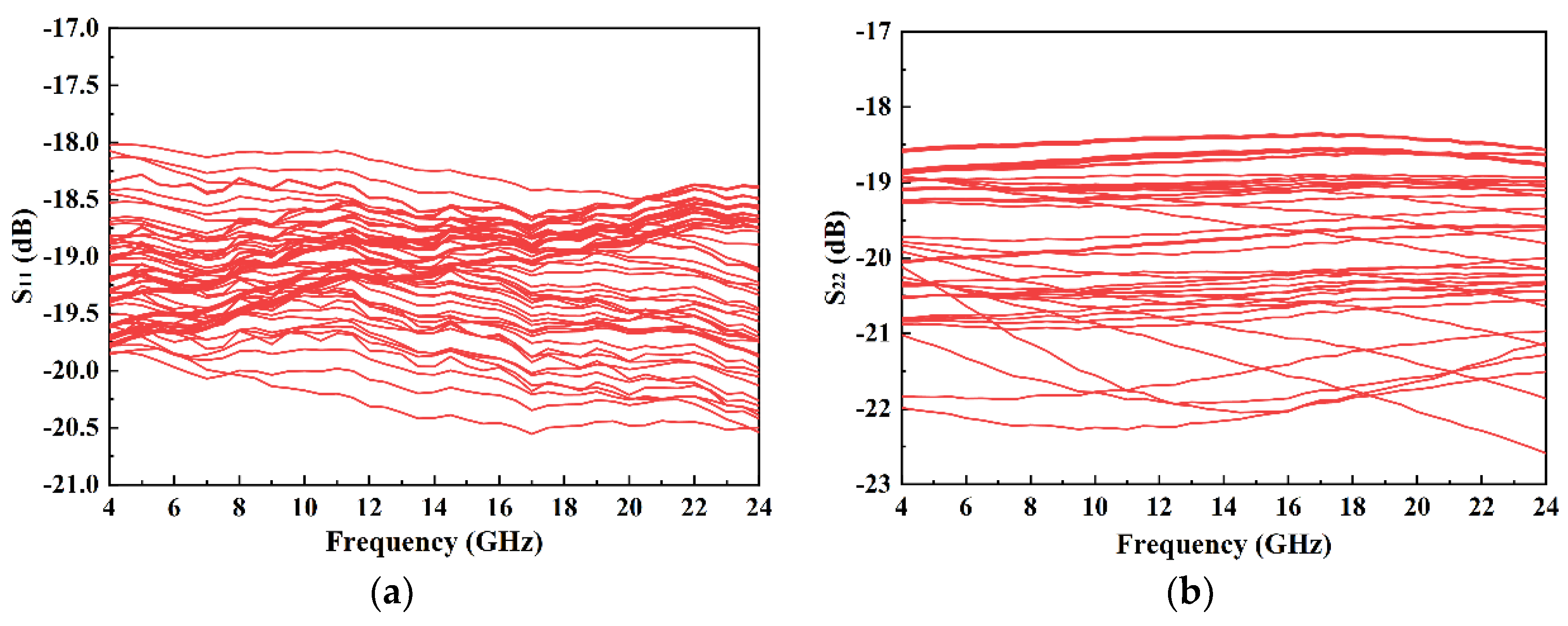

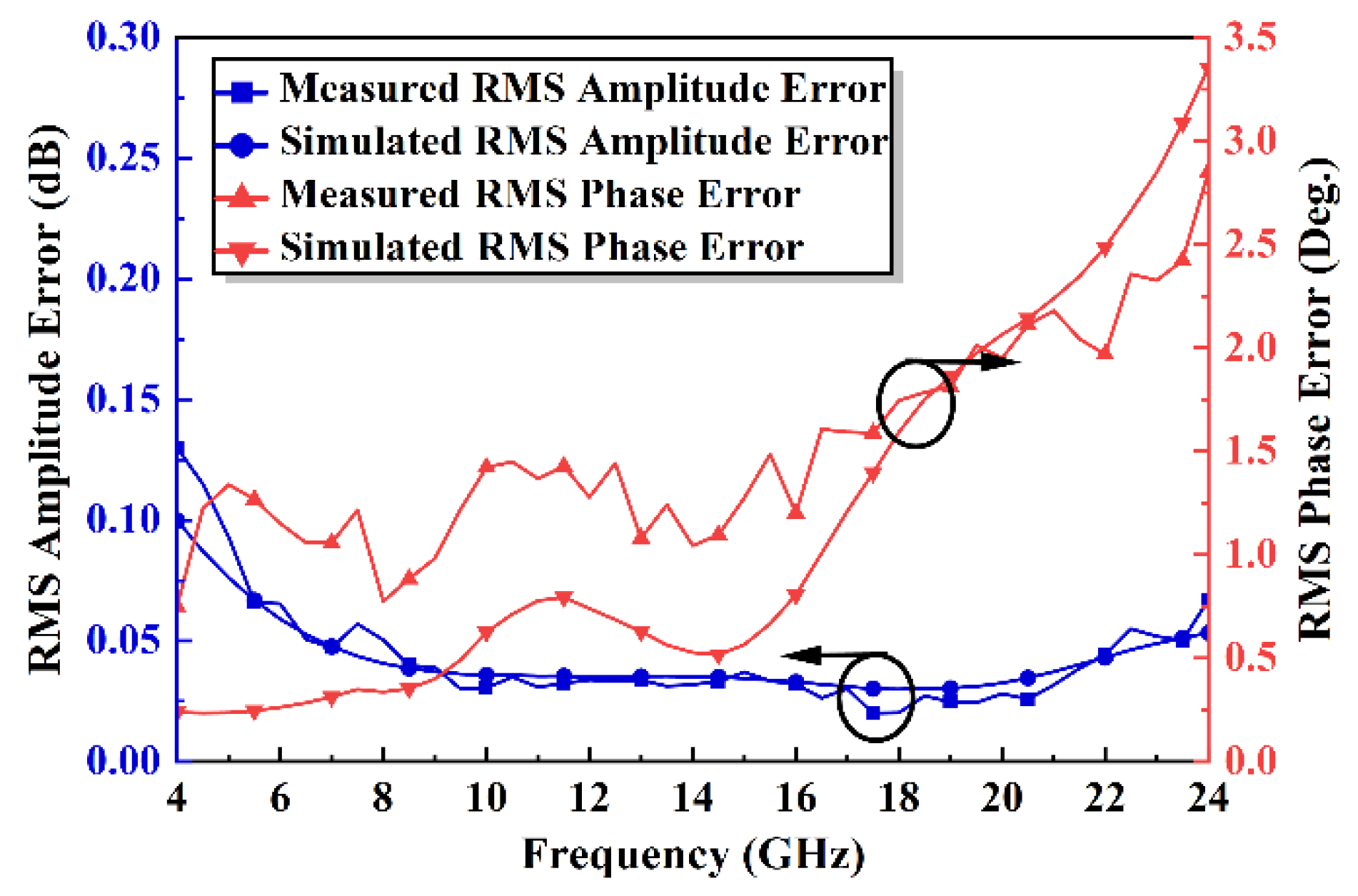

4. Simulation and Measurement Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Melde, K.L.; Taylor, M.L. Pattern characteristics of linear arrays using the constrained least squares distribution. IEEE Trans. Antennas Propag. 2003, 51, 772–775. [Google Scholar] [CrossRef]

- Zinka, S.R.; Kim, J.P. On the Generalization of Taylor and Bayliss n-bar Array Distributions. IEEE Trans. Antennas Propag. 2012, 60, 1152–1157. [Google Scholar] [CrossRef]

- Dogan, H.; Meyer, R.G. Intermodulation Distortion in CMOS Attenuators and Switches. IEEE J. Solid-State Circuits 2007, 42, 529–539. [Google Scholar] [CrossRef]

- Dogan, H.; Meyer, R.G.; Niknejad, A.M. Analysis and Design of RF CMOS Attenuators. IEEE J. Solid-State Circuits 2008, 43, 2269–2283. [Google Scholar] [CrossRef]

- Koutani, M.; Kawamura, H.; Toyoyama, S.; Iizuka, K. A Digitally Controlled Variable-gain Low-noise Amplifier with Strong Immunity to Interferers. In Proceedings of the 2006 IEEE Asian Solid-State Circuits Conference, Hangzhou, China, 13 November 2006; pp. 71–74. [Google Scholar] [CrossRef]

- Huang, Y.-Y.; Woo, W.; Yoon, Y.; Lee, C.-H. Highly Linear RF CMOS Variable Attenuators With Adaptive Body Biasing. IEEE J. Solid-State Circuits 2011, 46, 1023–1033. [Google Scholar] [CrossRef]

- Song, I.; Cho, M.-K.; Cressler, J.D. Design and Analysis of a Low Loss, Wideband Digital Step Attenuator With Minimized Amplitude and Phase Variations. IEEE J. Solid-State Circuits 2018, 53, 2202–2213. [Google Scholar] [CrossRef]

- Zhao, C.; Zeng, X.; Zhang, L.; Liu, H.; Yu, Y.; Wu, Y.; Kang, K. A 37–40-GHz Low-Phase-Imbalance CMOS Attenuator With Tail-Capacitor Compensation Technique. IEEE Trans. Circ. Syst. I Regul. Pap. 2020, 67, 3400–3409. [Google Scholar] [CrossRef]

- Doddamani, N.D.; Harishchandra; Nandi, A.V. Design of SPDT Switch, 6 Bit Digital Attenuator, 6 Bit Digital Phase Shifter for L-Band T/R Module using 0.7 μM GaAs MMIC Technology. In Proceedings of the 2007 International Conference on Signal Processing, Communications and Networking, Chennai, India, 22 February 2007; pp. 302–307. [Google Scholar] [CrossRef]

- Min, B.-W.; Rebeiz, G.M. A 10–50-GHz CMOS Distributed Step Attenuator With Low Loss and Low Phase Imbalance. IEEE J. Solid-State Circuits 2007, 42, 2547–2554. [Google Scholar] [CrossRef]

- Sjogren, L.; Ingram, D.; Biedenbender, M.; Lai, R.; Allen, B.; Hubbard, K. A low phase-error 44-GHz HEMT attenuator. IEEE Microw. Guided Wave Let. 1998, 8, 194–195. [Google Scholar] [CrossRef]

- Kim, J.-G.; Lee, K.-H. An S/C/X-Band 4-Bit Digital Step Attenuator MMIC with 0.25 μm GaN HEMT Technology. Appl. Sci. 2022, 12, 4717. [Google Scholar] [CrossRef]

- Zhao, C.; Guo, J.; Liu, H.; Yu, Y.; Wu, Y.; Kang, K. A 33–41-GHz SiGe-BiCMOS Digital Step Attenuator With Minimized Unit Impedance Variation. IEEE Trans. Very Large Scale Integ. (VLSI) Syst. 2021, 29, 568–579. [Google Scholar] [CrossRef]

- Cheon, C.D.; Rao, S.G.; Lim, W.; Cardoso, A.S.; Cho, M.-K.; Cressler, J.D. Design Methodology for a Wideband, Low Insertion Loss, Digital Step Attenuator in SiGe BiCMOS Technology. IEEE Trans. Circuits Syst. II Exp. Briefs 2022, 69, 744–748. [Google Scholar] [CrossRef]

- Li, N.; Zhang, Z.; Li, M.; Gao, H.; Wang, S.; Song, C.; Xu, Z. A DC–28-GHz 7-Bit High-Accuracy Digital-Step Attenuator in 55-nm CMOS. IEEE Microw. Wireless Compon. Lett. 2022, 32, 157–160. [Google Scholar] [CrossRef]

- Kim, K.; Lee, H.-S.; Min, B.-W. V-W Band CMOS Distributed Step Attenuator With low Phase Imbalance. IEEE Microw. Wireless Compon. Lett. 2014, 24, 548–550. [Google Scholar] [CrossRef]

- Cho, M.-K.; Kim, J.-G.; Baek, D. A Broadband Digital Step Attenuator with Low Phase Error and Low Insertion Loss in 0.18-μm SOI CMOS Technology. Electron. Telecommun. Res. Inst. J. 2013, 35, 638–643. [Google Scholar]

- Cheng, W.; Alink, M.S.O.; Annema, A.J.; Wienk, G.J.M.; Nauta, B. A Wideband IM3 Cancellation Technique for CMOS π and T-Attenuators. IEEE J. Solid-State Circuits 2013, 48, 358–368. [Google Scholar] [CrossRef]

- Luo, W.; Liu, H.; Zhang, Z.; Sun, P.; Liu, X. High-Power X-Band 5-b GaN Phase Shifter With Monolithic Integrated E/D HEMTs Control Logic. IEEE Trans. Elect. Dev. 2017, 64, 3627–3633. [Google Scholar] [CrossRef]

- Hao, D.; Zhang, W.; Liu, X.; Liu, Y. A Wideband 6-Bit Digital Attenuator in a GaAs pHEMT MMIC. Electronics 2022, 11, 2166. [Google Scholar] [CrossRef]

- Khabbaz, B.; Pospishil, A.; Singh, H.P. DC-to-20-GHz MMIC multibit digital attenuators with on-chip TTL control. IEEE J. Solid-State Circuits 1992, 27, 1457–1462. [Google Scholar] [CrossRef]

- Longhi, P.E.; Colangeli, S.; Ciccognani, W.; Limiti, E. Improved microwave attenuator topology minimizing the number of control voltages. Microw. Opt. Technol. Lett. 2019, 61, 926–929. [Google Scholar] [CrossRef]

- Wang, K.; Zhou, T.; Zhang, H.; Qiu, L. A 28–40-GHz Digital Step Attenuator With Low Amplitude and Phase Variations. IEEE Microw. Guided Wave Lett. 2021, 31, 64–67. [Google Scholar] [CrossRef]

| Reference | [21] | [22] | [4] | [8] | [7] | [13] | [23] | This Work |

|---|---|---|---|---|---|---|---|---|

| Technology | GaAs FET | GaAs | 0.13 μm CMOS | 65 nm CMOS | 0.13 μm SiGe BiCMOS | 0.13 μm SiGe BiCMOS | 0.13 μm SiGe BiCMOS | 0.15 μm GaAs PHEMT |

| Topology | Distributed T-type | T-type | T-type | T-type π-type | T-type | T-type π-type | π-type | T-type π-type Switched-path |

| Bandwidth (GHz) | DC-20 | 4–8 | 0–2.5 | 37–40 | DC-20 | 33–41 | 28–40 | 4–24 |

| Step (dB)/Bit | 1.5/4 | 0.5/5 | / | 1/5 | 0.5/6 | 0.5/5 | 1/5 | 0.5/6 |

| Attenuator Range (dB) | 22.5 | 15.5 | 42 | 31.5 | 31.5 | 15.5 | 31 | 31.5 |

| IL (dB) | 3.1–4.8 | 4.8 | 0.9–3.5 | 7 | 4 | 13 | 5.4–9.1 | 4.2–4.5 |

| Return Loss (dB) | >13 | / | >8.2 | >12 | >10 | >10 | >10 | >18 |

| RMS Attenuation (dB) | 0.5 | 0.2 | / | 0.27 | 0.37 | 0.2 | 0.43 | 0.15 |

| RMS Phase (Deg.) | / | / | / | 3.7 | 4 | 2.5 | 5.4 | 3 |

| Size (mm) | 2.6 × 1.6 | 1.8 × 1.2 | / | 0.51 × 0.42 | 1 × 0.14 | 0.5 × 0.44 | (0.21 mm2) | 1.5 × 0.4 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zeng, J.; Li, J.; Yuan, Y.; Tan, C.; Yu, Z. A C/X/Ku/K-Band Precision Compact 6-Bit Digital Attenuator with Logic Control Circuits. Electronics 2022, 11, 3620. https://doi.org/10.3390/electronics11213620

Zeng J, Li J, Yuan Y, Tan C, Yu Z. A C/X/Ku/K-Band Precision Compact 6-Bit Digital Attenuator with Logic Control Circuits. Electronics. 2022; 11(21):3620. https://doi.org/10.3390/electronics11213620

Chicago/Turabian StyleZeng, Jialong, Jiaxuan Li, Yang Yuan, Cheng Tan, and Zhongjun Yu. 2022. "A C/X/Ku/K-Band Precision Compact 6-Bit Digital Attenuator with Logic Control Circuits" Electronics 11, no. 21: 3620. https://doi.org/10.3390/electronics11213620