The ESD Characteristics of a pMOS-Triggered Bidirectional SCR in SOI BCD Technology

Abstract

:1. Introduction

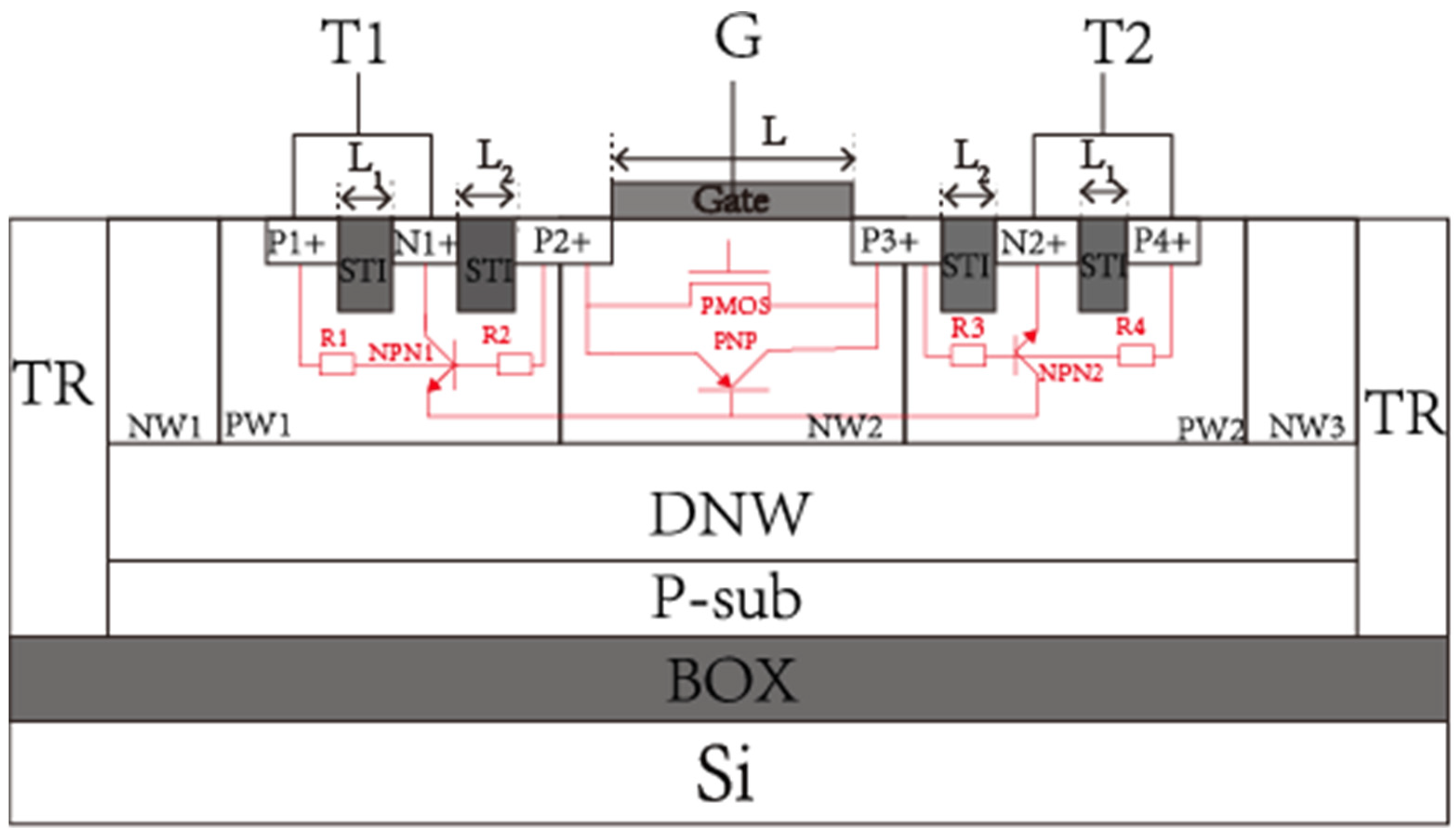

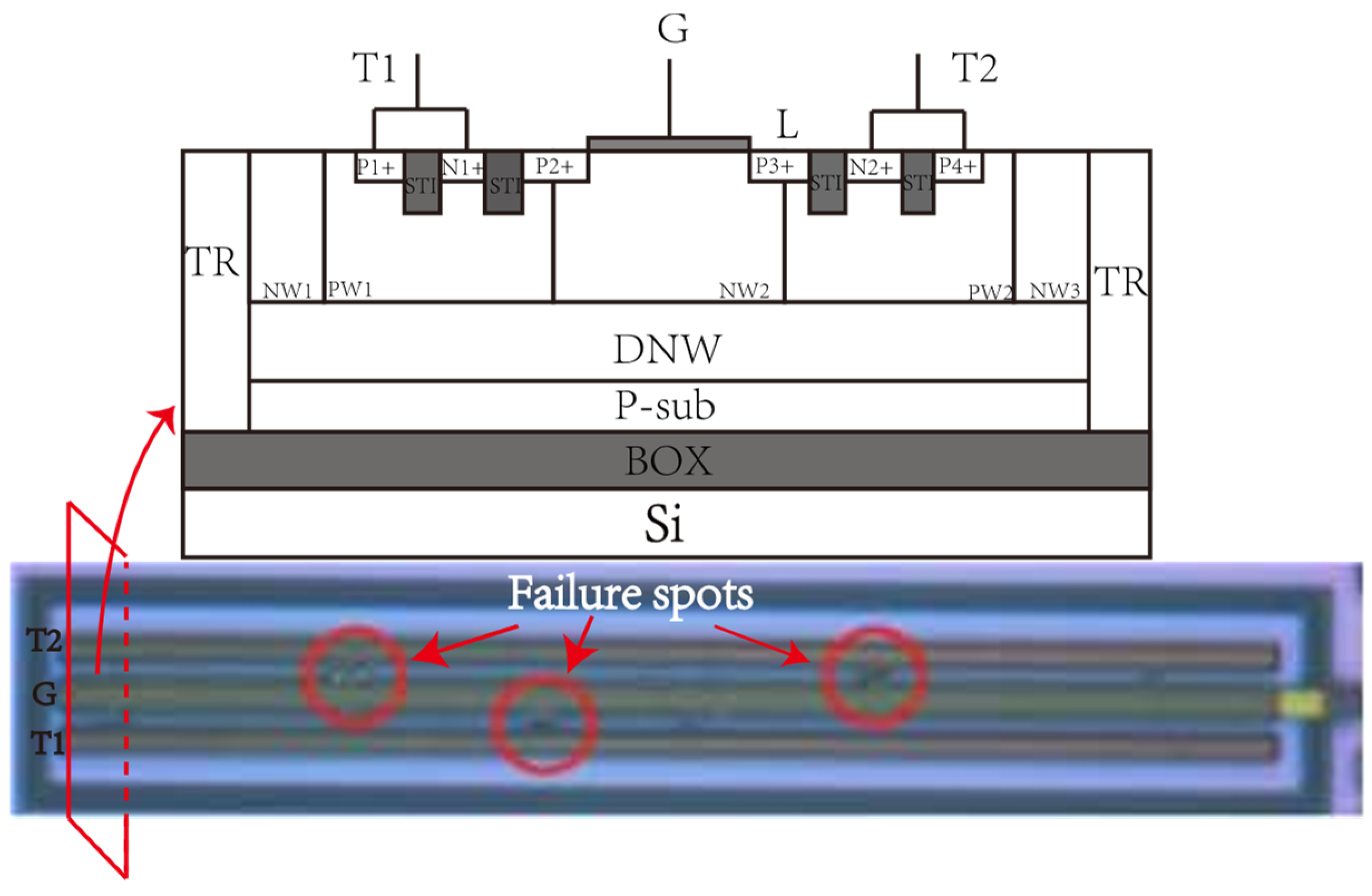

2. Test and Simulation Structure

3. Experimental Results and Analysis

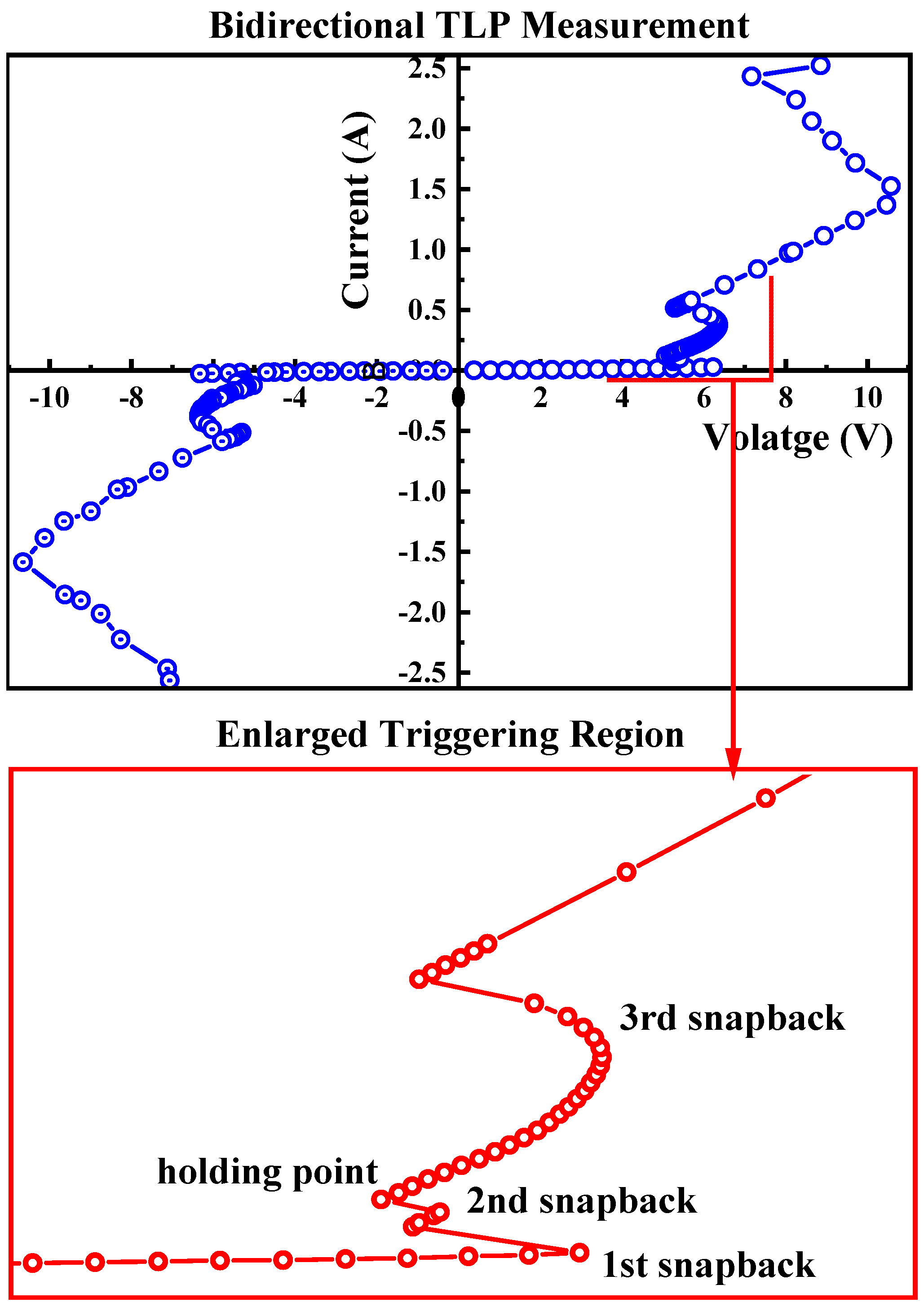

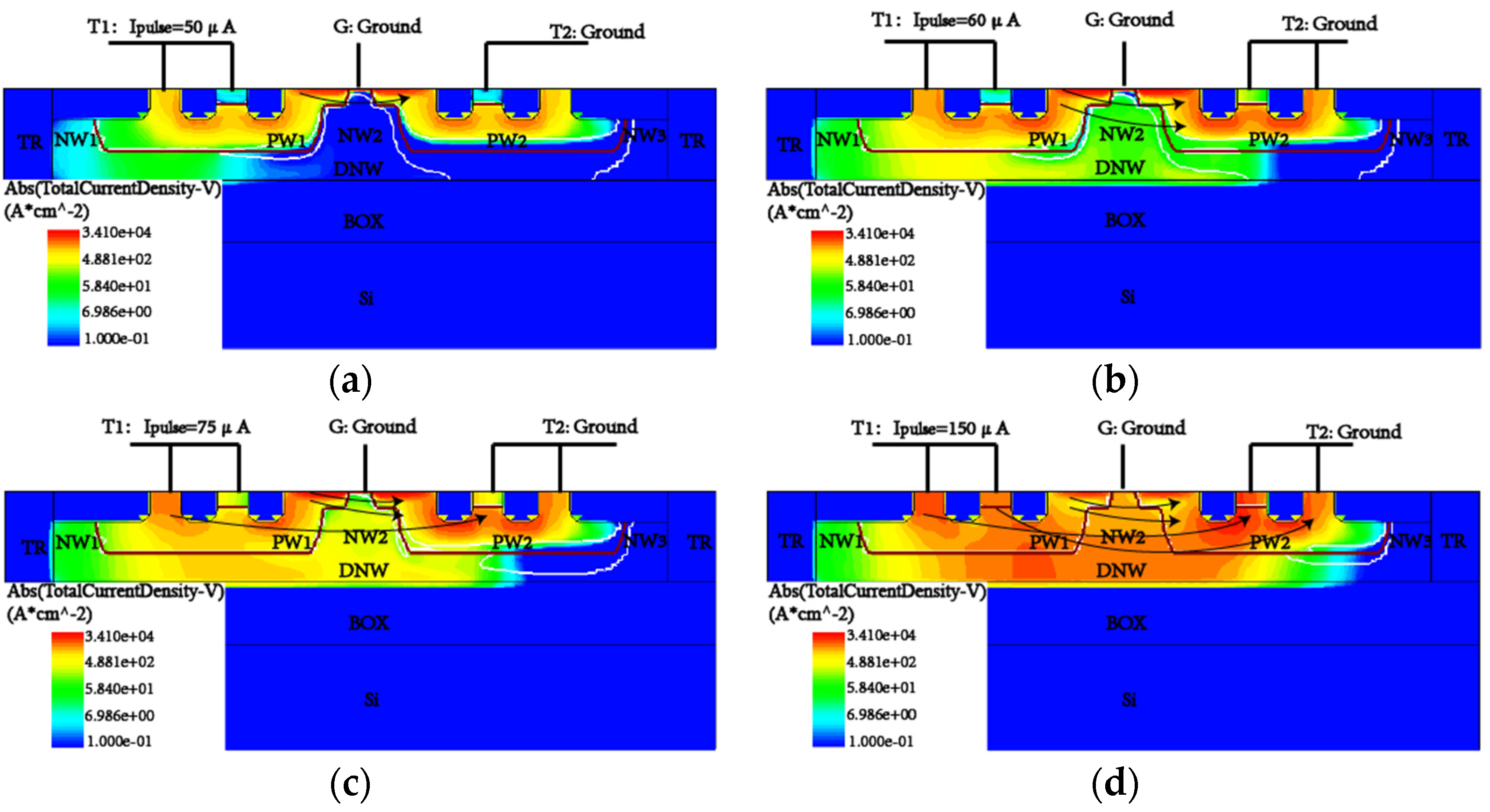

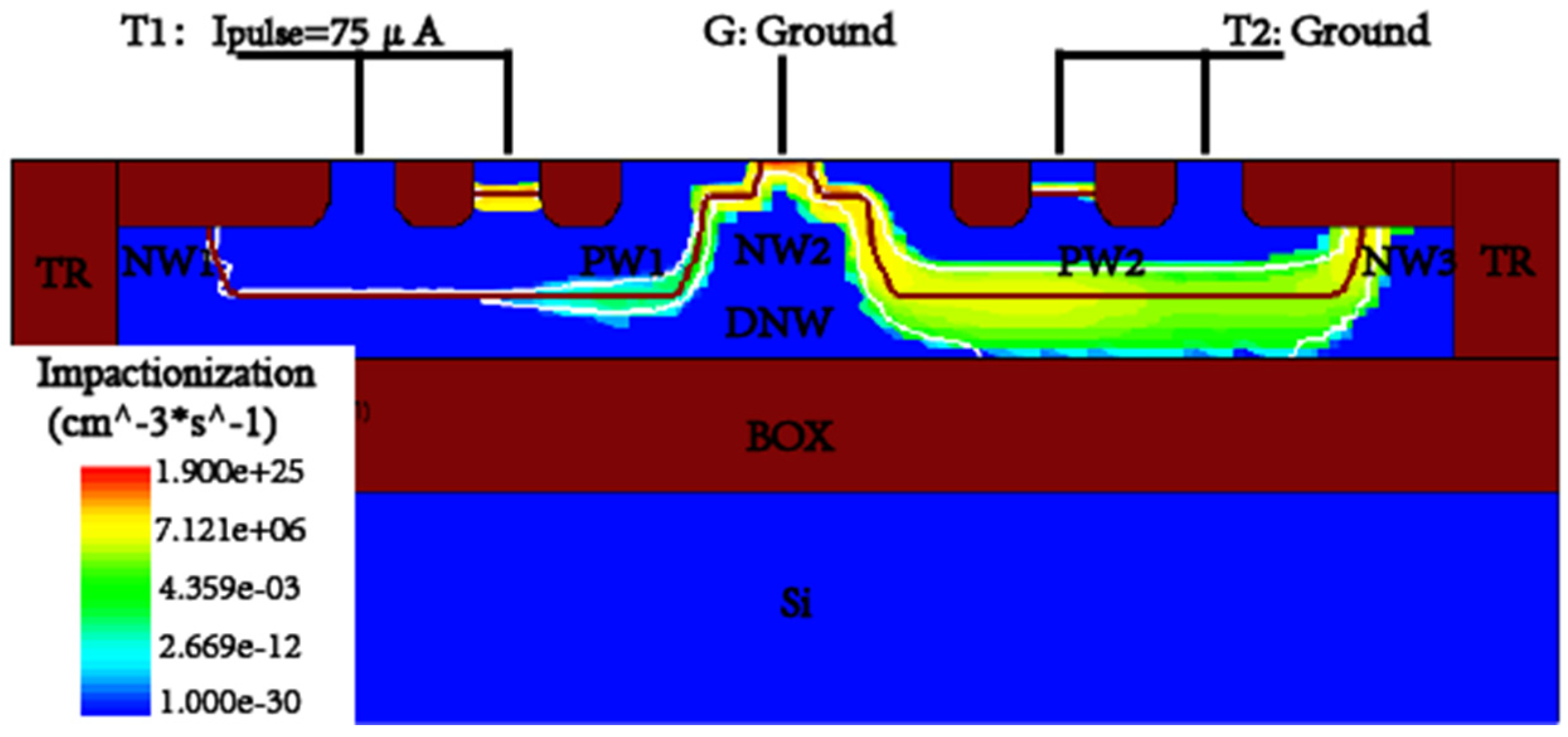

3.1. The Multiple Snapback Characteristic

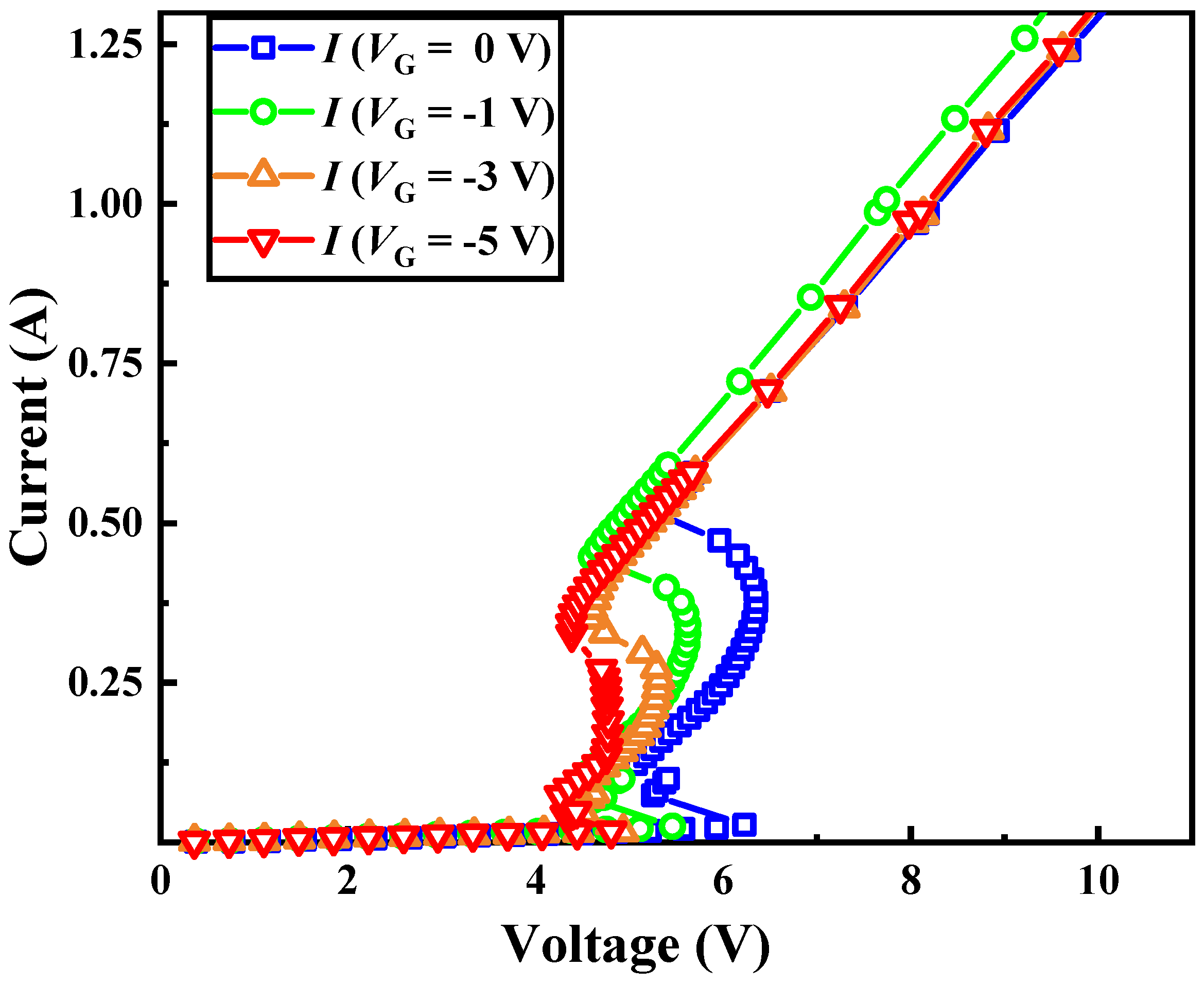

3.2. The Effect of Gate Voltage on Snapback Voltage

3.2.1. The Measured TLP Results

3.2.2. The Influence of Gate Voltage on Vt1 and Vh

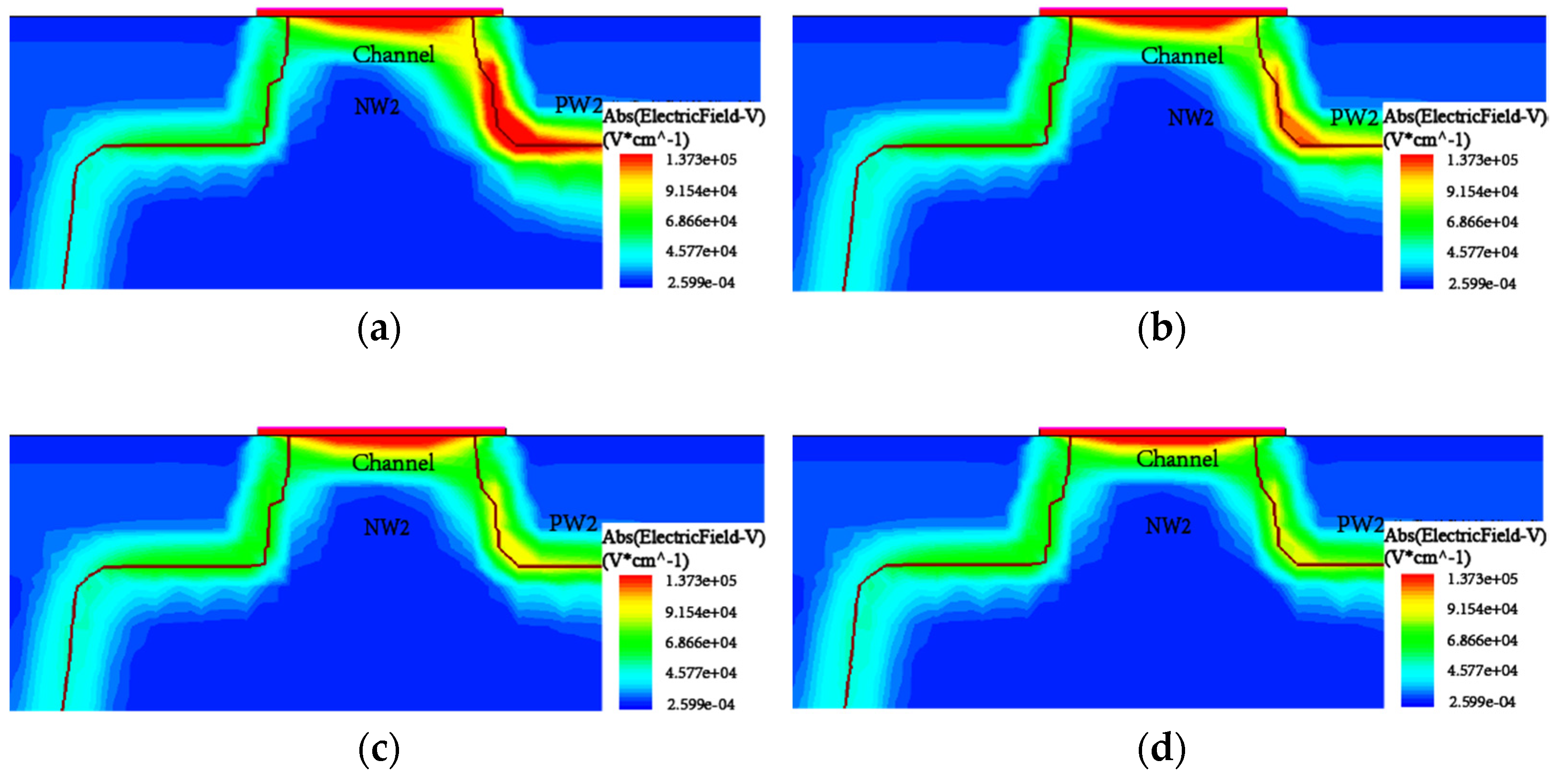

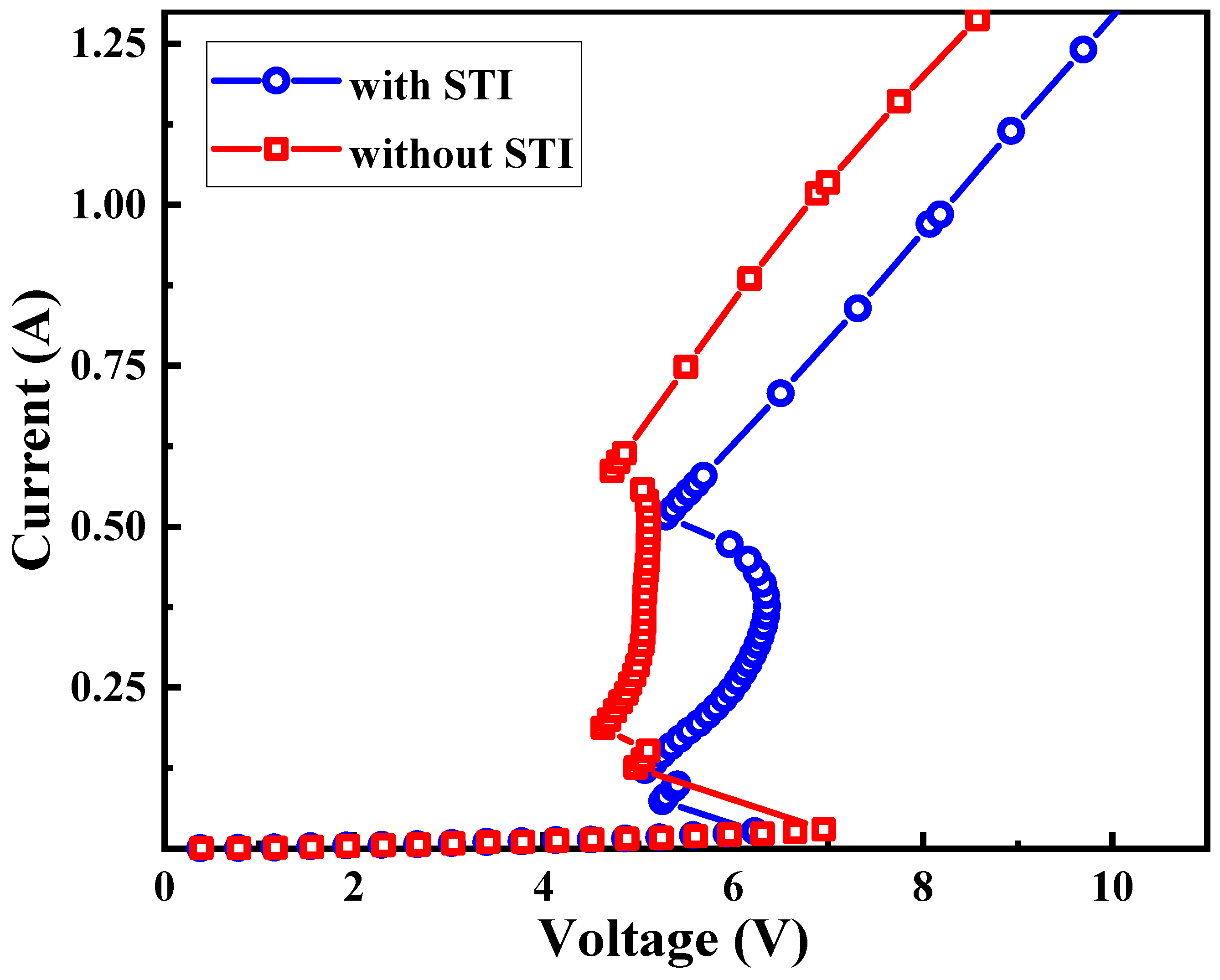

3.3. The Results Difference Caused by STI Isolation

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Bafleur, M. Introduction. In ESD Protection Methodologies; Elsevier Ltd.: Amsterdam, The Netherlands, 2017; pp. xvii–xxvi. ISBN 978-1-78548-122-2. [Google Scholar]

- Steven, L.; Voldman, H.; Wiley, J. 1.1 CMOS Latchup. In Latchup; John Wiley & Sons: Chichester, UK, 2008; pp. 1–46. [Google Scholar] [CrossRef]

- Ker, M.-D.; Hsu, S.-F. Introduction. In Transient-Induced Latchup in CMOS Integrated Circuits; IEEE: Piscataway, NJ, USA, 2009; pp. 1–21. ISBN 9780470824078. [Google Scholar]

- Chen, S.-H.; Ker, M.-D. Optimization of PMOS-triggered SCR devices for on-chip ESD protection in a 0.18-μm CMOS technology. In Proceedings of the 14th International Symposium on the Physical and Failure Analysis of Integrated Circuits, Bangalore, India, 11–13 July 2007; pp. 245–248. [Google Scholar] [CrossRef]

- Di Sarro, J.; Chatty, K.; Gauthier, R.; Rosenbaum, E. Evaluation of SCR-Based ESD Protection Devices in 90 nm and 65 nm CMOS Technologies. In Proceedings of the 2007 IEEE International Reliability Physics Symposium Proceedings. 45th Annual, Phoenix, AZ, USA, 15–19 April 2007. [Google Scholar]

- Chen, W.-Y.; Rosenbaum, E.; Ker, M.-D. Diode-Triggered Silicon-Controlled Rectifier with Reduced Voltage Overshoot for CDM ESD Protection. IEEE Trans. Device Mater. Reliab. 2011, 12, 10–14. [Google Scholar] [CrossRef]

- Mergens, M.; Russ, C.; Verhaege, K.; Armer, J.; Jozwiak, P.; Mohn, R.; Keppens, B.; Trinh, C. Diode-triggered SCR (DTSCR) for RF-ESD protection of Bi, CMOS Si, Ge HBTs and CMOS ultra-thin gate oxides. In Proceedings of the IEEE International Electron Devices Meeting 2003, Washington, DC, USA, 8–10 December 2003; pp. 515–518. [Google Scholar]

- Ker, M.D.; Chang, H.H. How to safely apply the LVTSCR for CMOS whole-chip ESD protection without being acci-dentally triggered on. J. Electrost. 1999, 47, 215–248. [Google Scholar] [CrossRef]

- Dong, S.; Wu, J.; Miao, M.; Zeng, J.; Han, Y.; Liou, J.J. High-Holding-Voltage Silicon-Controlled Rectifier for ESD Appli-cations. IEEE Electron Device Lett. 2012, 33, 1345–1347. [Google Scholar] [CrossRef]

- Vashchenko, V.; Concannon, A.; Ter Beek, M.; Hopper, P. High Holding Voltage Cascoded LVTSCR Structures for 5.5-V Tolerant ESD Protection Clamps. IEEE Trans. Device Mater. Reliab. 2004, 4, 273–280. [Google Scholar] [CrossRef]

- Wang, A.; Tsay, C.-H. On a dual-polarity on-chip electrostatic discharge protection structure. IEEE Trans. Electron Devices 2001, 48, 978–984. [Google Scholar] [CrossRef]

- Liu, Z.; Vinson, J.; Lou, L.; Liou, J. An Improved Bidirectional SCR Structure for Low-Triggering ESD Protection Applications. IEEE Electron Device Lett. 2008, 29, 360–362. [Google Scholar] [CrossRef]

- Vashchenko, V.A.; Kuznetsov, V.; Hopper, P.J. Implementation of dual-direction SCR devices in analog CMOS process. In Proceedings of the 2007 29th Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), Anaheim, CA, USA, 16–21 September 2007. [Google Scholar]

- Wang, Z.; Sun, R.-C.; Liou, J.J.; Liu, D.-G. Optimized p, MOS-Triggered Bidirectional SCR for Low-Voltage ESD Protection Applications. IEEE Trans. Electron Devices 2014, 61, 2588–2594. [Google Scholar]

- Bafleur, M.; Caignet, F.; Nolhier, N. Protection Strategies Against ESD. In ESD Protection Methodologies; Elsevier Ltd.: Amsterdam, The Netherlands, 2017; pp. 71–109. [Google Scholar] [CrossRef]

- Voldman, H.; Steven, H. Smart Power, LDMOS, and BCD Technology; John Wiley & Sons, Ltd.: Hoboken, NJ, USA, 2009; pp. 315–332. [Google Scholar] [CrossRef]

- Dong, S.; Jin, H.; Miao, M.; Wu, J.; Liou, J.J. Novel Capacitance Coupling Complementary Dual-Direction SCR for High-Voltage ESD. IEEE Electron Device Lett. 2012, 33, 640–642. [Google Scholar] [CrossRef]

- Dai, C.-T.; Ker, M.-D. Comparison Between High-Holding-Voltage SCR and Stacked Low-Voltage Devices for ESD Protection in High-Voltage Applications. IEEE Trans. Electron Devices 2018, 65, 798–802. [Google Scholar] [CrossRef]

- Hu, T.; Dong, S.; Jin, H.; Wong, H.; Xu, Z.; Li, X.; Liou, J.J. A double snapback SCR ESD protection scheme for 28 nm CMOS process. Microelectron. Reliab. 2018, 84, 20–25. [Google Scholar] [CrossRef]

- Zhang, S.; Dong, S.-R.; Wu, X.-J.; Zeng, J.; Zhong, L.; Wu, J. An improved GGNMOS triggered SCR for high holding volt-age ESD protection applications. Chin. Phys. B 2015, 24, 108502. [Google Scholar] [CrossRef]

- Mergens, M.; Wilkening, W.; Mettler, S.; Wolf, H.; Fichtner, W. Modular approach of a high current MOS compact model for circuit-level ESD simulation including transient gate coupling behavior. In Proceedings of the 37th Annual IEEE International Reliability Physics Symposium, San Diego, CA, USA, 23–25 March 1999; pp. 167–178. [Google Scholar]

- Amerasekera, A.; Ramaswamy, S.; Chang, M.-C.; Duvvury, C. Modeling MOS snapback and parasitic bipolar action for circuit-level ESD and high current simulations. In Proceedings of the 34th Annual International Reliability Physics Symposium, Dallas, TX, USA, 25–28 March 1996; pp. 318–326. [Google Scholar]

| Parameters | Volume |

|---|---|

| TSi (μm) | 1.5 |

| TBOX (μm) | 1.0 |

| Tgate (nm) | 14 |

| TSTI (μm) | 0.4 |

| DNW/DPW (μm) | 1.0 |

| L1 (μm) | 0.6 |

| L2 (μm) | 0.6 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, M.; Cai, X.; Zeng, C.; Li, X.; Ni, T.; Wang, J.; Li, D.; Zhao, F.; Han, Z. The ESD Characteristics of a pMOS-Triggered Bidirectional SCR in SOI BCD Technology. Electronics 2022, 11, 546. https://doi.org/10.3390/electronics11040546

Li M, Cai X, Zeng C, Li X, Ni T, Wang J, Li D, Zhao F, Han Z. The ESD Characteristics of a pMOS-Triggered Bidirectional SCR in SOI BCD Technology. Electronics. 2022; 11(4):546. https://doi.org/10.3390/electronics11040546

Chicago/Turabian StyleLi, Mingzhu, Xiaowu Cai, Chuanbin Zeng, Xiaojing Li, Tao Ni, Juanjuan Wang, Duoli Li, Fazhan Zhao, and Zhengsheng Han. 2022. "The ESD Characteristics of a pMOS-Triggered Bidirectional SCR in SOI BCD Technology" Electronics 11, no. 4: 546. https://doi.org/10.3390/electronics11040546