Analysis of HBM Failure in 3D NAND Flash Memory

Abstract

:1. Introduction

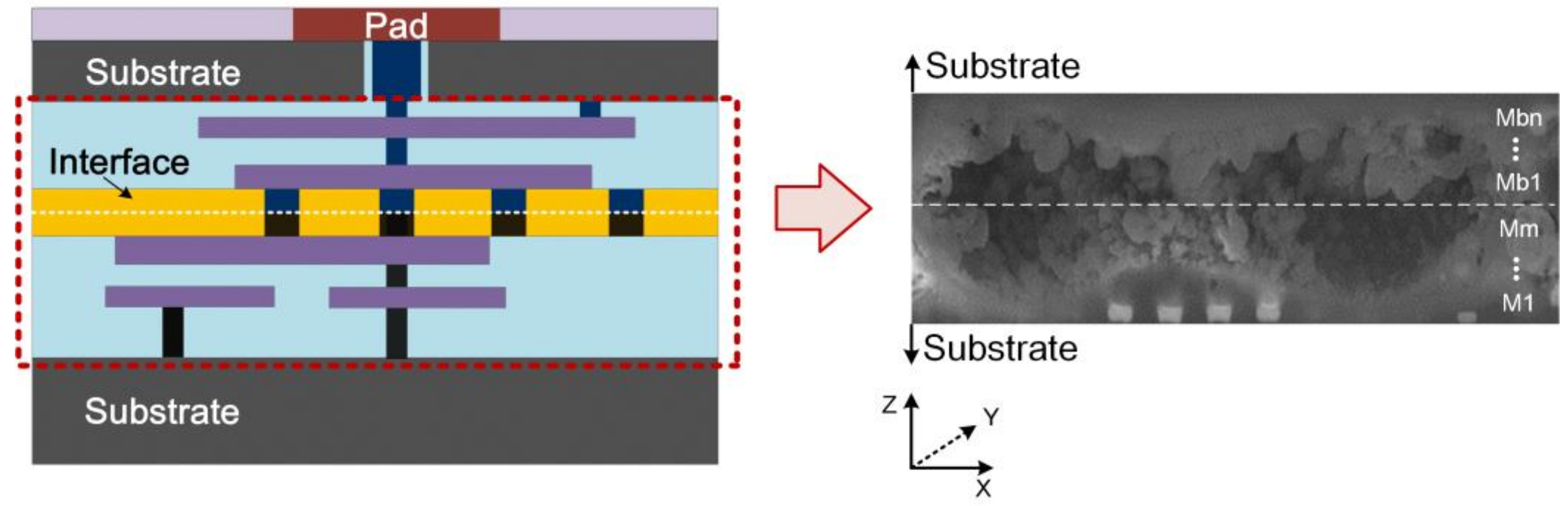

2. ESD Clamp Device Structure

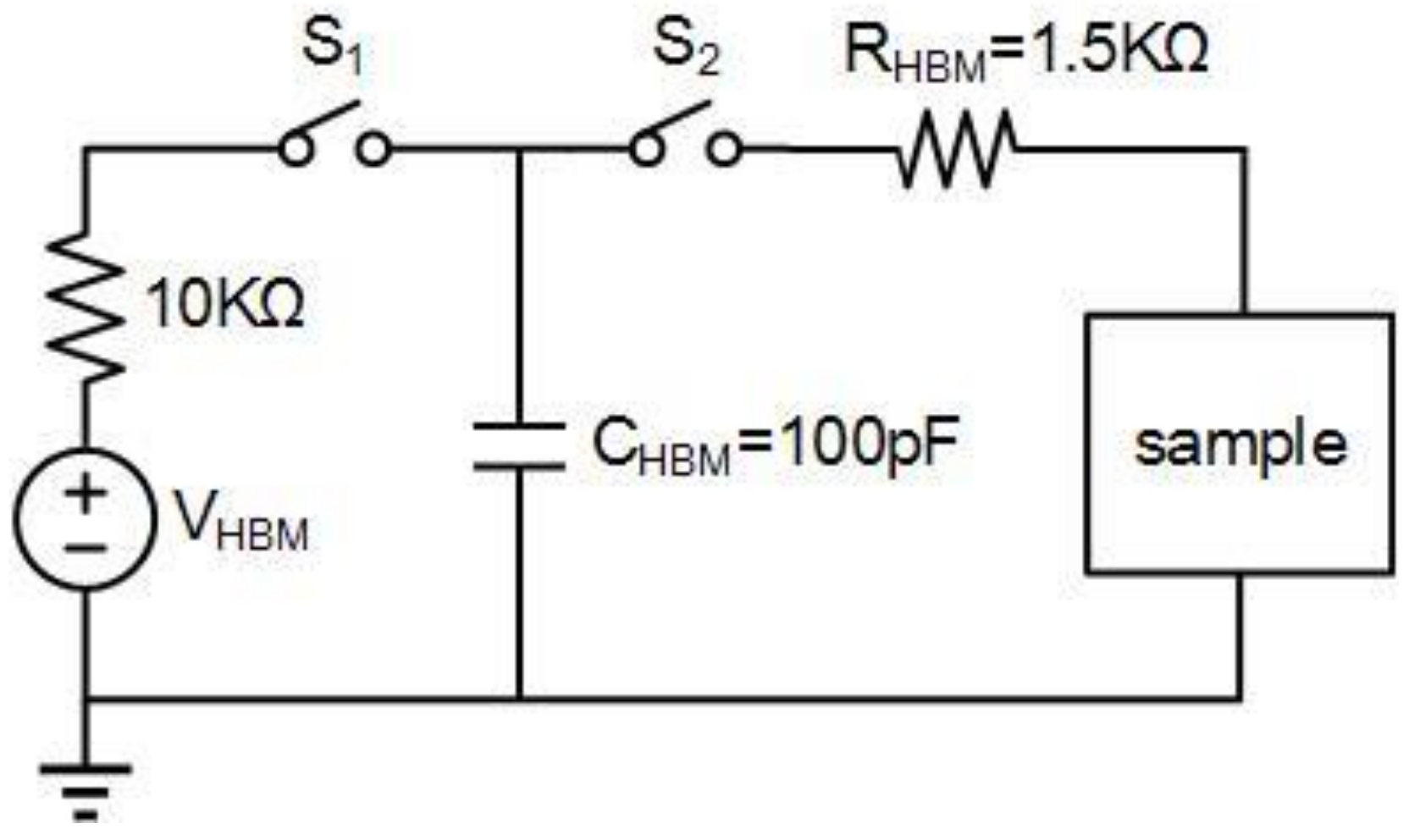

3. HBM Testing System

4. Experimental Results and Discussion

4.1. HBM Test Results

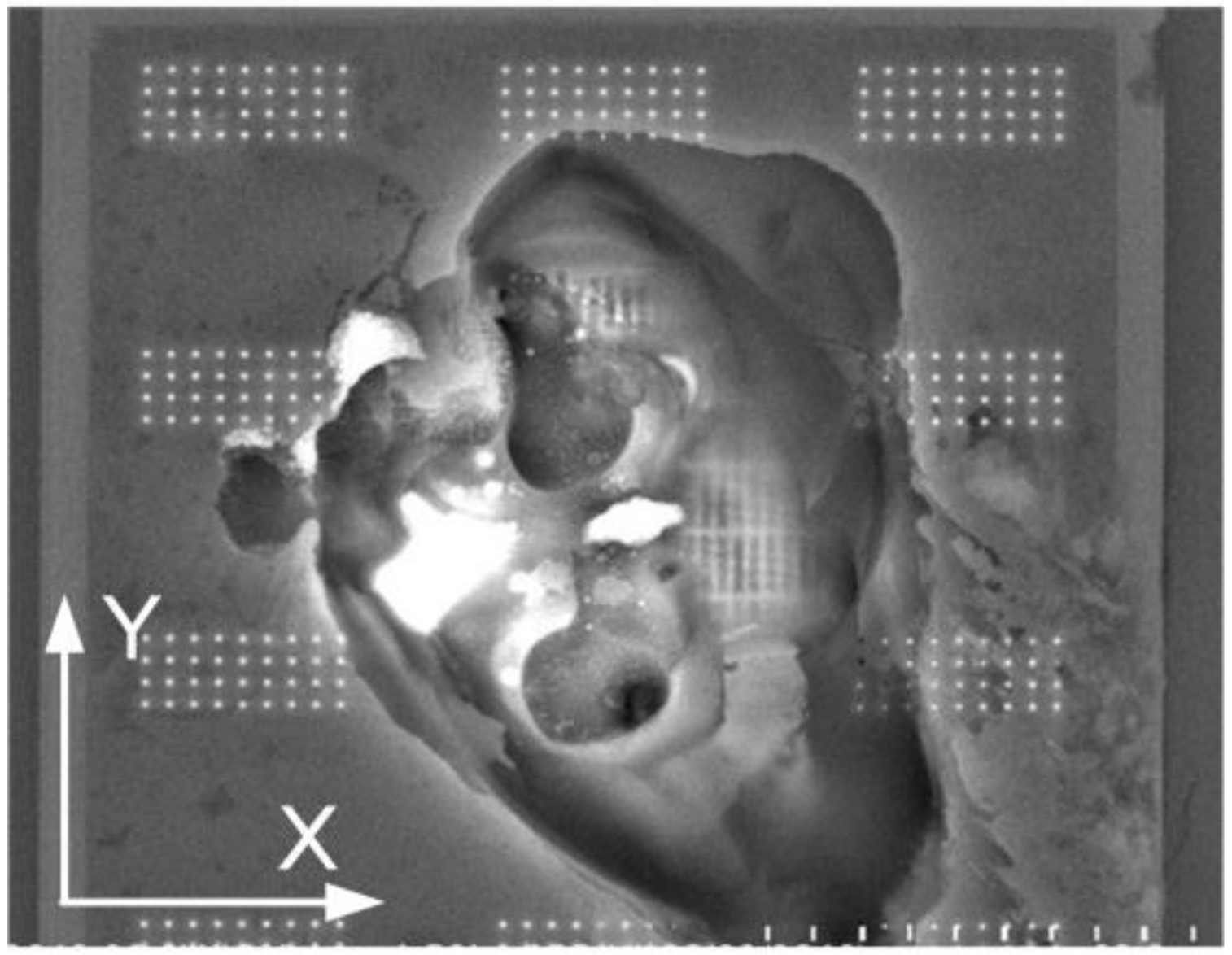

4.2. Failure Analysis: Multi-Finger NMOS

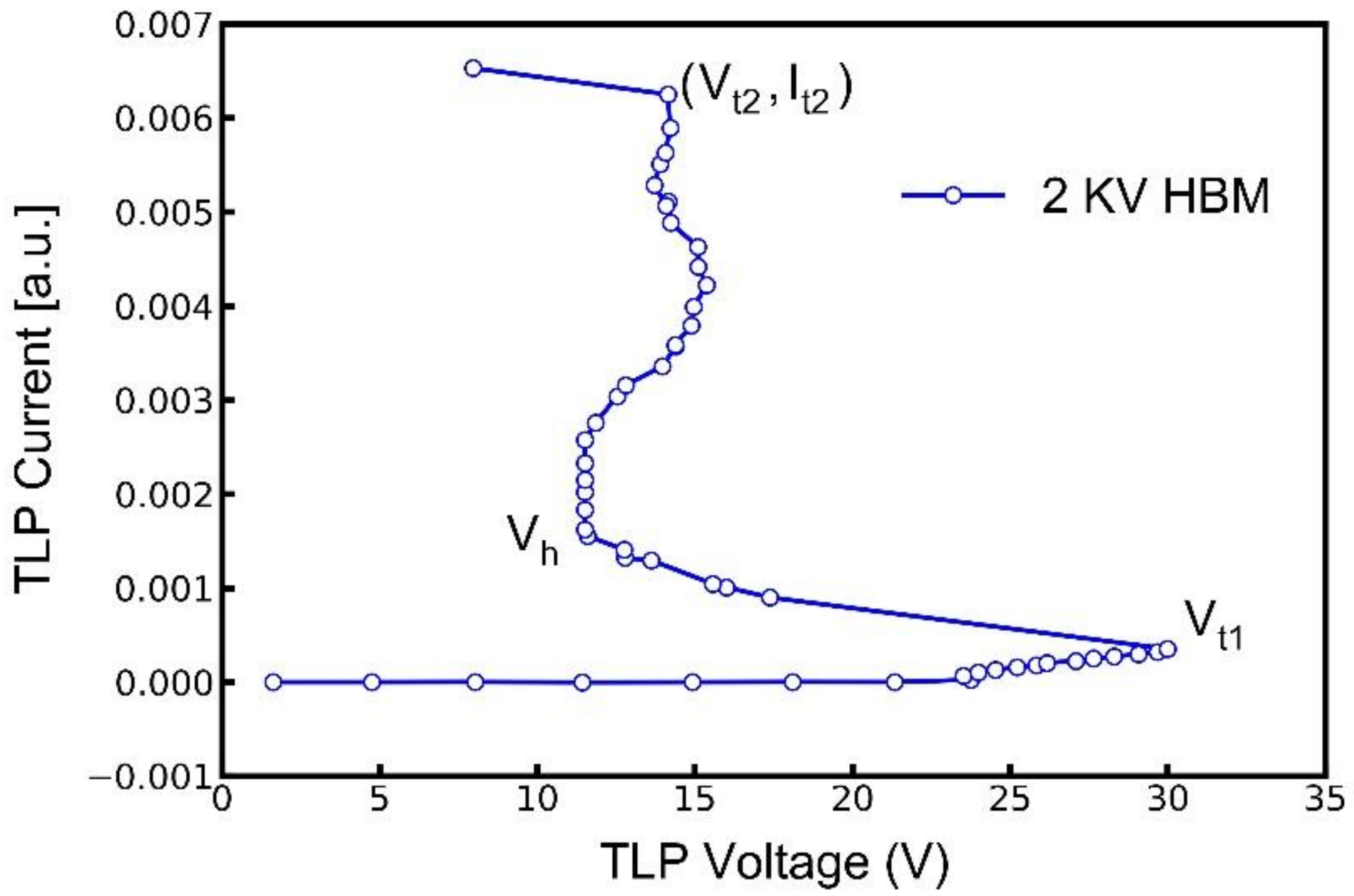

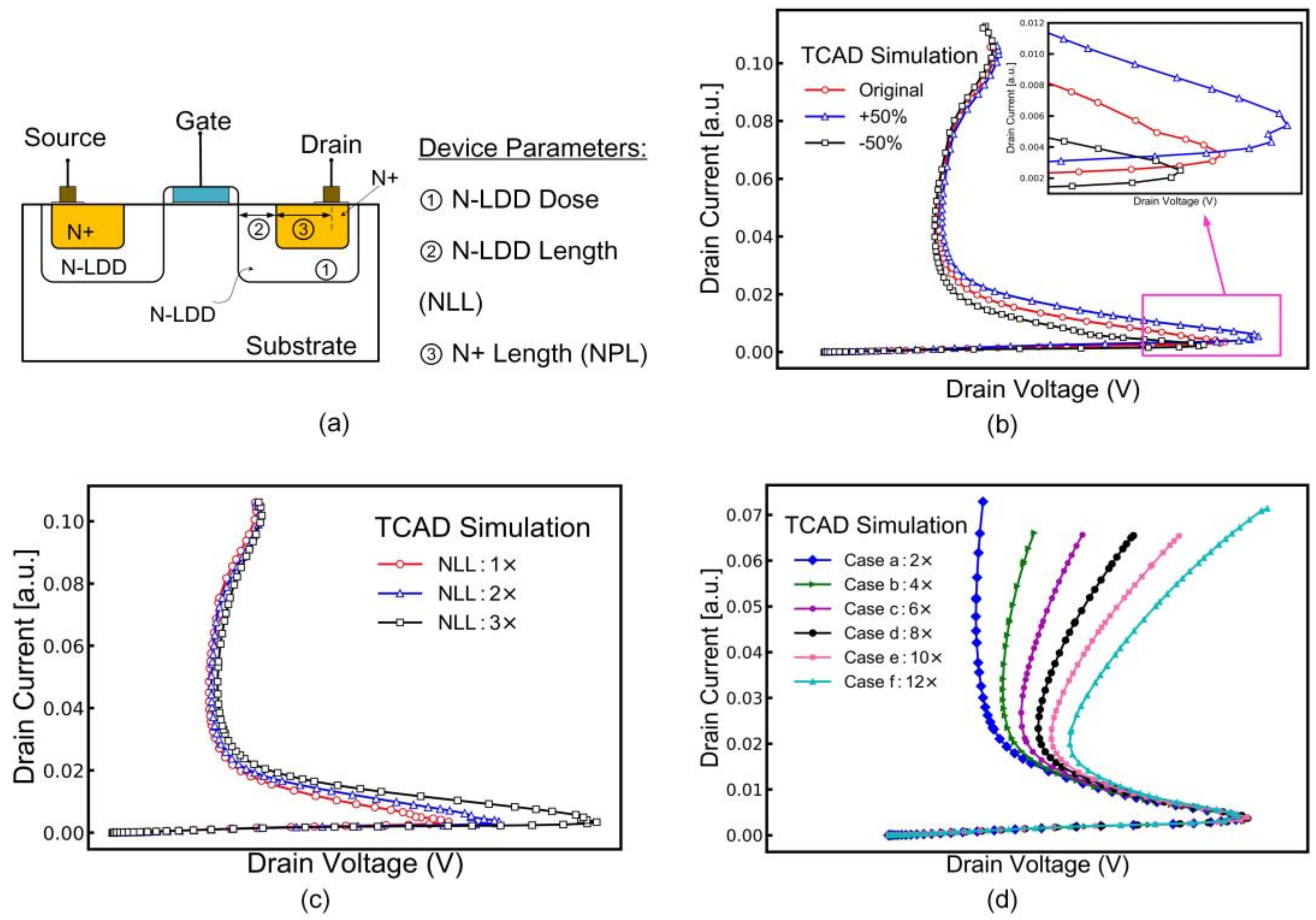

4.2.1. Analysis of NMOS Turn-On Nonuniformity

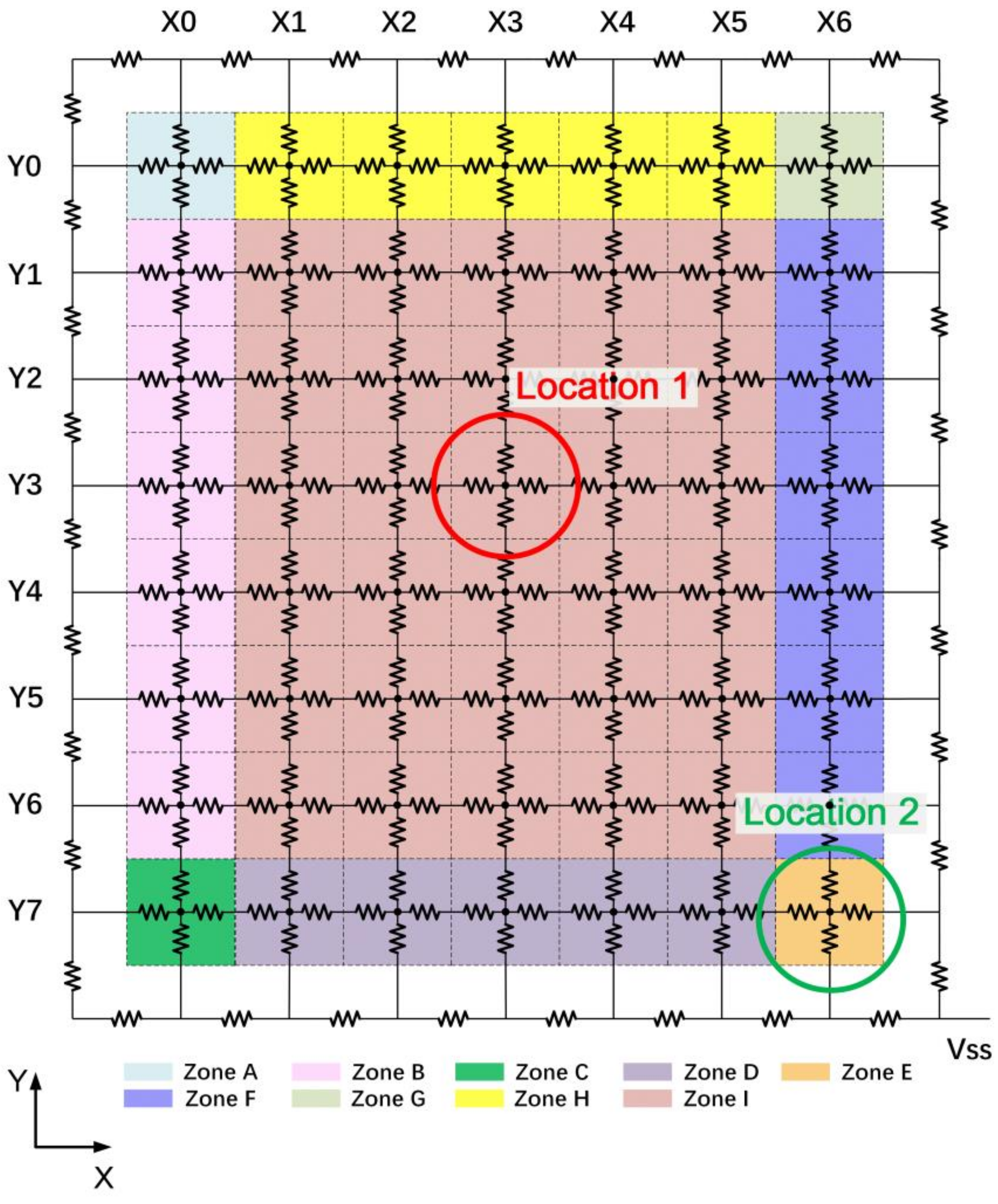

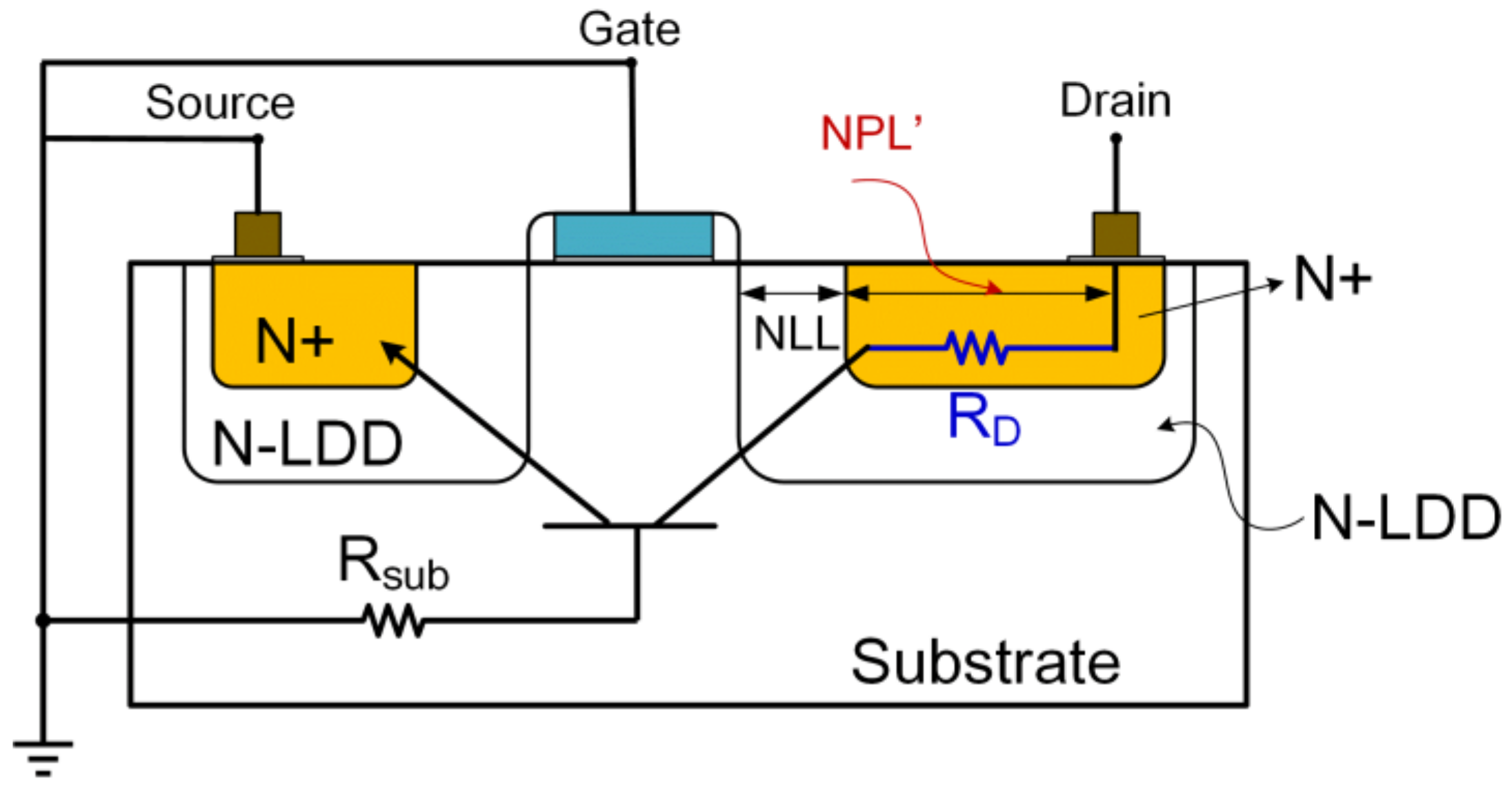

4.2.2. Analysis of Substrate Resistance

4.3. Failure Mechanism Analysis: Drain Contact and 3D Stacking

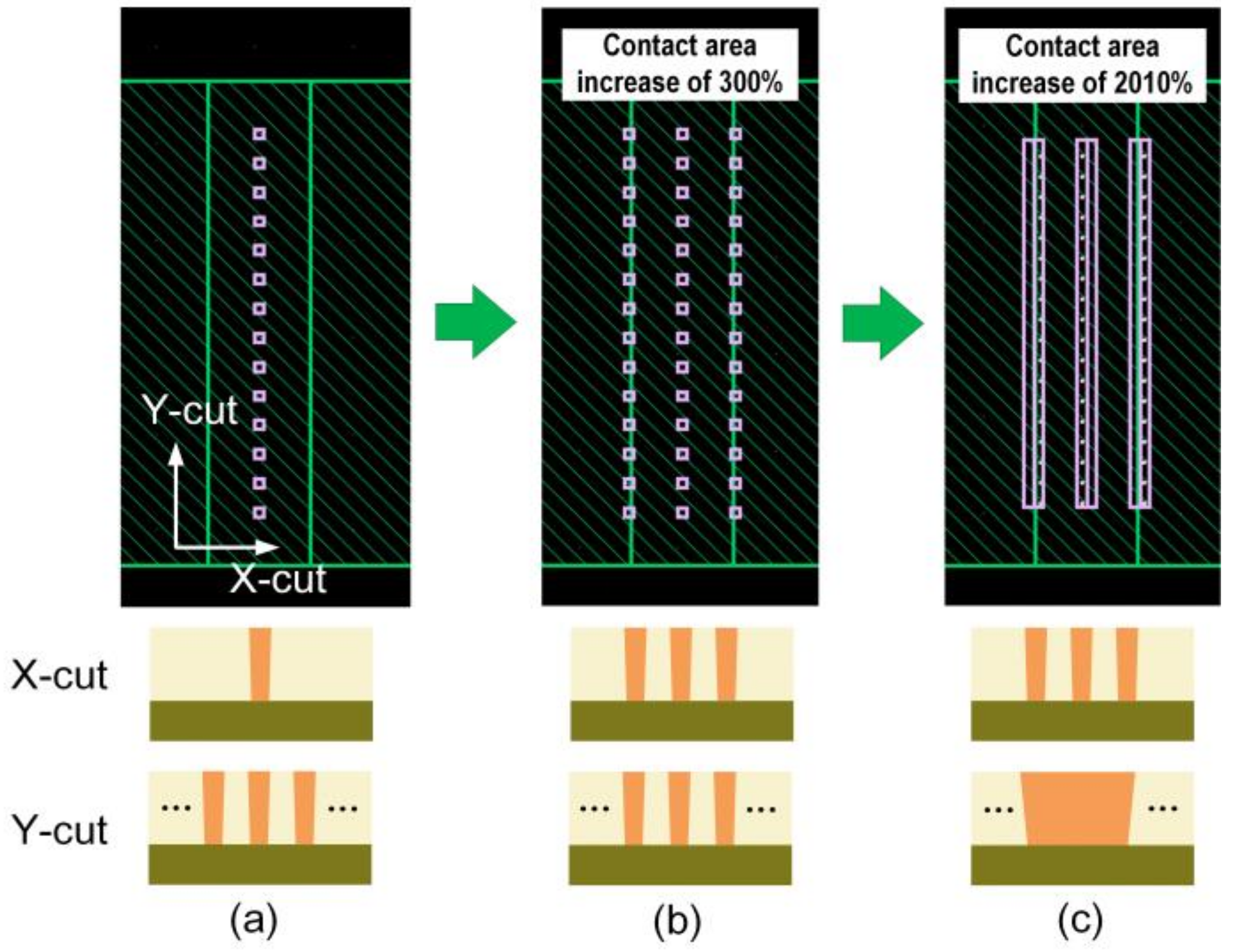

4.3.1. Effect of Drain Contact

4.3.2. Effect of 3D Stacking

5. Optimization of Heat Generation

5.1. NMOS Heat Optimization

5.2. Contact Heat Reduction

5.3. Silicon Results

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Wang, A.Z.H. On-Chip ESD Protection for Integrated Circuits; Springer: Boston, MA, USA, 2002; pp. 31–44. [Google Scholar]

- Jahanzeb, A.; Lou, L.; Duvvury, C.; Torres, C.; Morrison, S. TLP Characterization for Testing System Level ESD Performance. In Proceedings of the Electrical Overstress/Electrostatic Discharge Symposium Proceedings 2010, Reno, NV, USA, 3–8 October 2010. [Google Scholar]

- Lee, J.; Young, R.; Liou, J.; Croft, G.; Bernier, J. An improved transmission line pulsing (TLP) setup for electrostatic discharge (ESD) testing in semiconductor devices and ICs. In Proceedings of the ICMTS Proceedings of the 2001 International Conference on Microelectronic Test Structures (Cat. No.01CH37153), Kobe, Japan, 19–22 March 2001; pp. 233–238. [Google Scholar] [CrossRef]

- Barth, J.; Verhaege, K.; Henry, L.; Richner, J. TLP calibration, correlation, standards, and new techniques [ESD test]. In Proceedings of the Electrical Overstress/Electrostatic Discharge Symposium Proceedings 2000 (IEEE Cat. No.00TH8476), Anaheim, CA, USA, 26–28 September 2000; pp. 85–96. [Google Scholar] [CrossRef]

- Ma, R.; Wang, L.; Zhang, C.; Lu, F.; Dong, Z.; Wang, A.; Lu, W.; Song, Y.; Zhao, B. TLP and HBM ESD test correlation for power ICs. In Proceedings of the 2013 IEEE International Conference of Electron Devices and Solid-State Circuits, Hong Kong, China, 3–5 June 2013; pp. 84–89. [Google Scholar] [CrossRef]

- Lee, J.-H.; Iyer, N.M. Analytical Model of Correlation Factor for Human-Body Model to Transmission-Line Pulse ESD Testing. IEEE Electron Device Lett. 2017, 38, 952–954. [Google Scholar] [CrossRef]

- Ker, M.-D.; Peng, J.-J.; Jiang, H.-C. Failure analysis of ESD damage in a high-voltage driver IC and the effective ESD protection solution [CMOS]. In Proceedings of the 9th International Symposium on the Physical and Failure Analysis of Integrated Circuits (Cat. No.02TH8614), Singapore, 8–12 July 2002; pp. 84–89. [Google Scholar] [CrossRef]

- Shao, J.; Qiao, Y.; Ma, Q.; Li, J.; Chen, Y.; Yuan, Y.; Tang, X.; Zhang, H.; Zhao, D. Investigation on the ESD failure mechanism of integrated circuits in a 0.11µm CMOS process. In Proceedings of the 2017 18th International Conference on Electronic Packaging Technology (ICEPT), Harbin, China, 16–19 August 2017; pp. 69–71. [Google Scholar] [CrossRef]

- Dai, C.-T.; Chiu, P.-Y.; Ker, M.-D.; Tsai, F.-Y.; Peng, Y.-H.; Tsai, C.-K. Failure analysis on gate-driven ESD clamp circuit after TLP stresses of different voltage steps in a 16-V CMOS process. In Proceedings of the 2012 19th IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits, Singapore, 2–6 July 2012. [Google Scholar] [CrossRef]

- Lai, P.; Wang, Y.; Liang, X.; Kuang, X.; Zou, J. Location techniques of failure analysis ESD damage in electronic component. In Proceedings of the 2014 10th International Conference on Reliability, Maintainability and Safety (ICRMS), Guangzhou, China, 6–8 August 2014; pp. 127–131. [Google Scholar] [CrossRef]

- Fukasaku, K.; Yamazaki, T.; Kanno, M. Origin of It2 drop depending on process and layout with fully silicided ggMOS. In Proceedings of the EOS/ESD Symposium, Anaheim, CA, USA, 11–16 September 2011. [Google Scholar]

- Singh, A.; Shrivastava, M. 3D TCAD studies of Snapback Driven Failure in Punch-through TVS Diodes under System Level ESD Stress Conditions. In Proceedings of the 2020 42nd Annual EOS/ESD Symposium (EOS/ESD), Reno, NV, USA, 13–18 September 2020. [Google Scholar]

- Joshi, S.; Juliano, P.; Rosenbaum, E.; Kaatz, G.; Kang, S.-M. ESD protection for BiCMOS circuits. In Proceedings of the 2000 BIPOLAR/BiCMOS Circuits and Technology Meeting (Cat. No.00CH37124), Minneapolis, MN, USA, 26 September 2000; pp. 218–221. [Google Scholar] [CrossRef]

- Mergens, M.; Wilkening, W.; Mettler, S.; Wolf, H.; Stricker, A.; Fichtner, W. Analysis of lateral DMOS power devices under ESD stress conditions. IEEE Trans. Electron Devices 2000, 47, 2128–2137. [Google Scholar] [CrossRef]

- Ker, M.-D.; Hsu, H.-C.; Peng, J.-J. Novel ESD implantation for sub-quarter-micron CMOS technology with enhanced machine-model ESD robustness. In Proceedings of the 9th International Symposium on the Physical and Failure Analysis of Integrated Circuits (Cat. No.02TH8614), Singapore, 12–12 July 2002; pp. 70–74. [Google Scholar] [CrossRef]

- Li, C.; Pan, Z.; Di, M.; Zhang, F.; Li, Z.; Jiang, N.; Wang, A. ESD Device Layout Design Guidelines by 3D TCAD Simulation. In Proceedings of the 2020 4th IEEE Electron Devices Technology & Manufacturing Conference (EDTM), Penang, CA, Malaysia, 21–25 April 2020. [Google Scholar] [CrossRef]

- Ouyang, Y.; Yang, S.; Yin, D.; Huang, X.; Wang, Z.; Yang, S.; Han, K.; Xia, Z. Excellent Reliability of Xtacking™ Bonding Interface. In Proceedings of the 2021 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 21–25 March 2021. [Google Scholar] [CrossRef]

- Shen, X.; Xia, Z.; Yang, T.; Liu, L.; Dong, J.; Zhou, W.; Li, C.; Huo, Z. Hydrogen Source and Diffusion Path for Poly-Si Channel Passivation in Xtacking 3D NAND Flash Memory. IEEE J. Electron Devices Soc. 2020, 8, 1021–1024. [Google Scholar] [CrossRef]

- Park, J.-W.; Kim, D.; Ok, S.; Park, J.; Kwon, T.; Lee, H.; Lim, S.; Jung, S.-Y.; Choi, H.; Kang, T.; et al. 30.1 A 176-Stacked 512Gb 3b/Cell 3D-NAND Flash with 10.8Gb/mm2 Density with a Peripheral Circuit Under Cell Array Architecture. In Proceedings of the 2021 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; pp. 422–423. [Google Scholar] [CrossRef]

- Khakifirooz, A.; Balasubrahmanyam, S.; Fastow, R.; Gaewsky, K.H.; Ha, C.W.; Haque, R.; Jungroth, O.W.; Law, S.; Madraswala, A.S.; Ngo, B.; et al. 30.2 A 1Tb 4b/Cell 144-Tier Floating-Gate 3D-NAND Flash Memory with 40MB/s Program Throughput and 13.8Gb/mm2 Bit Density. In Proceedings of the 2021 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; pp. 424–426. [Google Scholar] [CrossRef]

- De Vos, J.; Peng, L.; Phommahaxay, A.; Van Ongeval, J.; Miller, A.; Beyne, E.; Kurz, F.; Wagenleiter, T.; Wimplinger, M.; Uhrmann, T. Importance of alignment control during permanent bonding and its impact on via-last alignment for high density 3D interconnects. In Proceedings of the 2016 IEEE International 3D Systems Integration Conference (3DIC), San Francisco, CA, USA, 8–11 November 2016. [Google Scholar] [CrossRef]

- Van der Plas, G.; Limaye, P.; Loi, I.; Mercha, A.; Oprins, H.; Torregiani, C.; Thijs, S.; Linten, D.; Stucchi, M.; Katti, G.; et al. Design Issues and Considerations for Low-Cost 3-D TSV IC Technology. IEEE J. Solid-State Circuits 2010, 46, 293–307. [Google Scholar] [CrossRef] [Green Version]

- Chen, S.H.; Thijs, S.; Linten, D.; Scholz, M.; Hellings, G.; Groeseneken, G. ESD protection devices placed inside keep-out zone (KOZ) of through Silicon Via (TSV) in 3D stacked integrated circuits. In Proceedings of the EOS/ESD Symposium, Tucson, AZ, USA, 11–16 September 2012. [Google Scholar]

- Bogaerts, L.; De Vos, J.; Gerets, C.; Jamieson, G.; Vandersmissen, K.; La Manna, A. Process related challenges for 3D face to face stacking test vehicles using a 40/50μm pitch CuSn microbump configuration. In Proceedings of the 2012 IEEE 14th Electronics Packaging Technology Conference (EPTC), Singapore, 5–7 December 2012. [Google Scholar] [CrossRef]

- Micheloni, R.; Crippa, L.; Marelli, A. Inside NAND Flash Memories; Springer Science and Business Media LLC: Berlin/Heidelberg, Germany, 2010; pp. 189–196. [Google Scholar]

- C62.38-1994—IEEE Guide on Electrostatic Discharge (ESD): ESD Withstand Capability Evaluation Methods (for Electronic Equipment Subassemblies). Available online: https://ieeexplore.ieee.org/document/696974 (accessed on 24 April 1995).

- Tien, D.K.C.; Sool, K.S. A simple but effective ESD robustness improvement for NMOS transistors used in I/O pads. In Proceedings of the 2011 IEEE Regional Symposium on Micro and Nano Electronics, Kota Kinabalu, Malaysia, 28–30 September 2011. [Google Scholar] [CrossRef]

- Huo, M.; Guo, Q.; Han, Y.; Shen, L.; Liu, Q.; Song, B.; Ma, Q.; Zhu, K.; Shen, Y.; Du, X.; et al. A Case Study of Problems in JEDEC HBM ESD Test Standard. IEEE Trans. Device Mater. Reliab. 2009, 9, 361–366. [Google Scholar] [CrossRef]

- Ding, Z.; Duan, C.; Wang, X.; Wu, Z.; Tian, Y.; Meng, M. Failure Analysis of Microwave Module by ESD Effect. In Proceedings of the 2019 IEEE 26th International Symposium on Physical and Failure Analysis of Integrated Circuits (IPFA), Hangzhou, China, 2–5 July 2019. [Google Scholar] [CrossRef]

- Ting-Nguon, T.; Prancis, C.; Swee-Thian, T. ESD failure finger-print-an effective and accurate method for root cause determination. In Proceedings of the 1997 6th International Symposium on the Physical and Failure Analysis of Integrated Circuits, Singapore, 25–25 July 1997. [Google Scholar] [CrossRef]

- Liu, F.; Huang, W.; Huang, X.; Ma, C.; Lin, X.; Liu, Z. Failure analysis of a PLL ESD structure design defect. In Proceedings of the 2017 IEEE 24th International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA), Chengdu, China, 4–7 July 2017. [Google Scholar] [CrossRef]

- Parke, S.; Moon, J.; Wann, H.; Ko, P.; Hu, C. Design for suppression of gate-induced drain leakage in LDD MOSFETs using a quasi-two-dimensional analytical model. IEEE Trans. Electron Devices 1992, 39, 1694–1703. [Google Scholar] [CrossRef]

- Ogura, S.; Tsang, P.; Walker, W.; Critchlow, D.; Shepard, J. Design and Characteristics of the Lightly Doped Drain-Source (LDD) Insulated Gate Field-Effect Transistor. IEEE J. Solid-State Circuits 1980, 15, 424–432. [Google Scholar] [CrossRef]

- Viale, B.; Allard, B. Scalable and Versatile Design Guidance Tool for the ESD Robustness of Integrated Circuits—Part II. IEEE Trans. Comput. Des. Integr. Circuits Syst. 2020, 39, 3107–3117. [Google Scholar] [CrossRef]

- Chen, K.-L. The effects of interconnect process and snapback voltage on the ESD failure threshold of NMOS transistors. IEEE Trans. Electron Devices 1988, 35, 2140–2145. [Google Scholar] [CrossRef]

| Sample | Failure Voltage (KV) |

|---|---|

| Sample 1 | 1 |

| Sample 2 | 1.25 |

| Sample 3 | 1.5 |

| X | X0 | X1 | X2 | X3 | X4 | X5 | X6 | |

|---|---|---|---|---|---|---|---|---|

| Y | ||||||||

| Y0 | 6.11 | 6.03 | 5.94 | 5.84 | 5.72 | 5.59 | 5.47 | |

| Y1 | 8.57 | 8.97 | 9.05 | 9.02 | 8.90 | 8.66 | 8.13 | |

| Y2 | 9.19 | 9.82 | 10.06 | 10.08 | 9.95 | 9.61 | 8.87 | |

| Y3 | 9.37 | 10.10 | 10.39 | 10.45 | 10.32 | 9.94 | 9.15 | |

| Y4 | 9.30 | 10.04 | 10.35 | 10.42 | 10.30 | 9.93 | 9.15 | |

| Y5 | 8.97 | 9.65 | 9.91 | 9.97 | 9.88 | 9.57 | 8.86 | |

| Y6 | 8.19 | 8.65 | 8.80 | 8.83 | 8.77 | 8.58 | 8.10 | |

| Y7 | 5.52 | 5.52 | 5.52 | 5.51 | 5.49 | 5.45 | 5.41 | |

| Sample | Failure Voltage (KV) |

|---|---|

| Sample 1 | 2 |

| Sample 2 | 2 |

| Sample 3 | 2.5 |

| Device Parameter | Vt1 | Vt2 |

|---|---|---|

| N-LDD Dose | √ | × |

| NNL | √ | × |

| NPL | × | √ |

| Sample | Failure Voltage (KV) |

|---|---|

| Sample 1# | 3.5 |

| Sample 2# | 3.5 |

| Sample 3# | 3.5 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Song, B.; Li, Z.; Wang, X.; Fu, X.; Liu, F.; Jin, L.; Huo, Z. Analysis of HBM Failure in 3D NAND Flash Memory. Electronics 2022, 11, 944. https://doi.org/10.3390/electronics11060944

Song B, Li Z, Wang X, Fu X, Liu F, Jin L, Huo Z. Analysis of HBM Failure in 3D NAND Flash Memory. Electronics. 2022; 11(6):944. https://doi.org/10.3390/electronics11060944

Chicago/Turabian StyleSong, Biruo, Zhiguo Li, Xin Wang, Xiang Fu, Fei Liu, Lei Jin, and Zongliang Huo. 2022. "Analysis of HBM Failure in 3D NAND Flash Memory" Electronics 11, no. 6: 944. https://doi.org/10.3390/electronics11060944