Pre-Layout Parasitic-Aware Design Optimizing for RF Circuits Using Graph Neural Network

Abstract

:1. Introduction

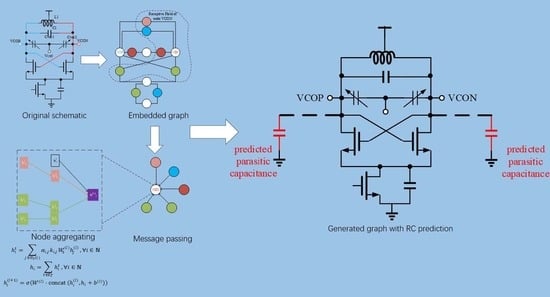

2. GNN-Based Model for Interconnect RC Prediction

2.1. Inputs and Outputs of the Model

2.2. Graph Neural Network

2.3. Training and Network Optimization

3. Experiments

3.1. Low-Voltage Charge Pump

3.2. Low-Voltage VCO

4. Results and Analysis

4.1. Accuracy of the Model

4.2. VCO Optimization Results

4.3. CP Optimization Results

4.4. PLL Optimization Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Yoshida, H.; De, K.; Boppana, V. Accurate pre-layout estimation of standard cell characteristics. In Proceedings of the 41st annual Design Automation Conference, San Diego, CA, USA, 7–11 June 2004; pp. 208–211. [Google Scholar]

- Shook, B.; Bhansali, P.; Kashyap, C.; Amin, C.; Joshi, S. MLParest: Machine learning based parasitic estimation for custom circuit design. In Proceedings of the 57th ACM/IEEE Design Automation Conference (DAC), San Diego, CA, USA, 20–24 June 2020; IEEE: Manhattan, NY, USA, 2020; pp. 1–6. [Google Scholar]

- Ren, H.; Kokai, G.F.; Turner, W.J.; Ku, T.S. ParaGraph: Layout Parasitics and Device Parameter Prediction using Graph Neural Networks. In Proceedings of the 57th ACM/IEEE Design Automation Conference (DAC), San Diego, CA, USA, 20–24 June 2020. [Google Scholar]

- Zhou, J.; Cui, G.; Zhang, Z.; Yang, C.; Liu, Z.; Sun, M. Graph neural networks: A review of methods and applications. arXiv 2018, arXiv:1812.08434. [Google Scholar] [CrossRef]

- Kipf, T.N.; Welling, M. Semi-supervised classification with graph convolutional networks. arXiv 2016, arXiv:1609.02907. [Google Scholar]

- Hamilton, W.L.; Ying, R.; Leskovec, J. Inductive representation learning on large graphs. Adv. Neural Inf. Process. Syst. 2017, 30, 1025–1035. [Google Scholar]

- Schlichtkrull, M.; Kipf, T.N.; Bloem, P.; van den Berg, R.; Titov, I.; Welling, M. Modeling relational data with graph convolutional networks. In European Semantic Web Conference; Springer: Cham, Switzerland, 2018; pp. 593–607. [Google Scholar]

- Velickovic, P.; Cucurull, G.; Casanova, A.; Romero, A.; Lio, P.; Bengio, Y. Graph attention networks. arXiv 2017, arXiv:1710.10903. [Google Scholar]

- Hsieh, Z.H.; Huang, N.X.; Shiau, M.S.; Wu, H.C.; Yang, S.Y.; Liu, D.G. A novel mixed-structure design for high-efficiency charge pump. In Proceedings of the 2009 MIXDES-16th International Conference Mixed Design of Integrated Circuits & Systems, Lodz, Poland, 25–27 June 2009; pp. 210–214. [Google Scholar]

- Biswas, D.; Bhattacharyya, T.K. Charge pump with reduced current mismatch for reference spur minimization in PLLs. Analog Integr. Circuits Signal Process. 2018, 95, 209. [Google Scholar] [CrossRef]

- Ji, X.; Xia, X.; Wang, Z.; Jin, L. A 2.4 GHz fractional-N PLL with a low-power true single-phase clock prescaler. IEICE Electron. Express 2017, 14, 20170065. [Google Scholar] [CrossRef] [Green Version]

- Zou, W.; Ren, D.; Zou, X. A wideband low-jitter PLL with an optimized Ring-VCO. IEICE Electron. Express 2020, 17, 20190703. [Google Scholar] [CrossRef] [Green Version]

- Kim, J.; Bae, B.-H. A 2–4 GHz fast-locking frequency multiplying delay-locked loop. IEICE Electron. Express 2017, 14, 20161056. [Google Scholar] [CrossRef] [Green Version]

- Murakami, R.; Hara, S.; Okada, K.; Matsuzawa, A. Design optimization of voltage controlled oscillators in consideration of parasitic capacitance. In Proceedings of the 52nd IEEE International Midwest Symposium on Circuits and Systems, Cancun, Mexico, 2–5 August 2009; pp. 1010–1013. [Google Scholar] [CrossRef]

- Ghai, D.; Mohanty, S.P.; Kougianos, E. Design of Parasitic and Process-Variation Aware Nano-CMOS RF Circuits: A VCO Case Study. In IEEE Transactions on Very Large Scale Integration (VLSI) Systems; IEEE: Manhattan, NY, USA, 2009; Volume 17, pp. 1339–1342. [Google Scholar] [CrossRef]

- Chen, J.; Hou, H.; Gao, J.; Ji, Y.; Bai, T. RGCN: Recurrent Graph Convolutional Networks for Target-Dependent Sentiment Analysis. In International Conference on Knowledge Science, Engineering and Management; Springer: Cham, Switzerland, 2019; pp. 667–675. [Google Scholar]

- Lin, Z.; Li, C.; Miao, Y.; Liu, Y.; Xu, Y. Pagraph: Scaling gnn training on large graphs via computation-aware caching. In Proceedings of the 11th ACM Symposium on Cloud Computing, Virtual Event, USA, 19–21 October 2020; pp. 401–415. [Google Scholar]

- Xu, K.; Wu, L.; Wang, Z.; Feng, Y.; Witbrock, M.; Sheinin, V. Graph2seq: Graph to sequence learning with attention-based neural networks. arXiv 2018, arXiv:1804.00823. [Google Scholar]

- Dai, H.; Kozareva, Z.; Dai, B.; Smola, A.; Song, L. Learning steady-states of iterative algorithms over graphs. In International Conference on Machine Learning; PMLR: New York, NY, USA, 2018; pp. 1106–1114. [Google Scholar]

- Zhang, Z.; Leng, J.; Ma, L.; Miao, Y.; Li, C.; Guo, M. Architectural implications of graph neural networks. IEEE Comput. Archit. Lett. 2020, 19, 59–62. [Google Scholar]

- Zhou, X.; Zeng, Y.; Wang, H. RoGAT: A robust GNN combined revised GAT with adjusted graphs. arXiv 2020, arXiv:2009.13038. [Google Scholar]

- Grover, A.; Leskovec, J. Node2vec: Scalable feature learning for networks. In Proceedings of the 22nd ACM SIGKDD International Conference on Knowledge Discovery and Data Mining, San Francisco, CA, USA, 13–17 August 2016; pp. 855–864. [Google Scholar]

| Node Type | Features | Definition |

|---|---|---|

| PMOS/NMOS * | W | width |

| L | length | |

| M | multiplier | |

| N | Number of fingers | |

| Capacitor * | W | width |

| L | length | |

| Resistor * | W | width |

| L | length | |

| M | multiplier | |

| Nets ** | PC | Predicted capacitor |

| PR | Predicted resistance |

| GNN Models | Aggregation Method |

|---|---|

| GCN [5] | |

| GraphSage [6] | |

| RGCN [7] | |

| GAT [8] | |

| ParaGraph [3] | |

| Proposed method |

| Settings | Values |

|---|---|

| Learning rate | 0.003 |

| Hidden feats | 7 |

| Hidden num | 5 |

| Aggregator type | mean |

| Activation function | Relu |

| Feature drop num | 0 |

| Epochs | 300 |

| (sub)Circuit | Specification | After manual Optimization | After GNN-Aided Optimization |

|---|---|---|---|

| VCO | Adjacent band overlap rate | 17.1% | 19.4% |

| CP | Mismatch time | 82 ps | 70 ps |

| PLL | Phase noise@10 MHz | −96.17 dBc/Hz | −107.86 dBc/Hz |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, C.; Hu, D.; Zhang, X. Pre-Layout Parasitic-Aware Design Optimizing for RF Circuits Using Graph Neural Network. Electronics 2023, 12, 465. https://doi.org/10.3390/electronics12020465

Li C, Hu D, Zhang X. Pre-Layout Parasitic-Aware Design Optimizing for RF Circuits Using Graph Neural Network. Electronics. 2023; 12(2):465. https://doi.org/10.3390/electronics12020465

Chicago/Turabian StyleLi, Chenfeng, Dezhong Hu, and Xiaoyan Zhang. 2023. "Pre-Layout Parasitic-Aware Design Optimizing for RF Circuits Using Graph Neural Network" Electronics 12, no. 2: 465. https://doi.org/10.3390/electronics12020465