Full-Custom 90 nm CNTFET Process Design Kit: Characterization, Modeling, and Implementation

Abstract

:1. Introduction

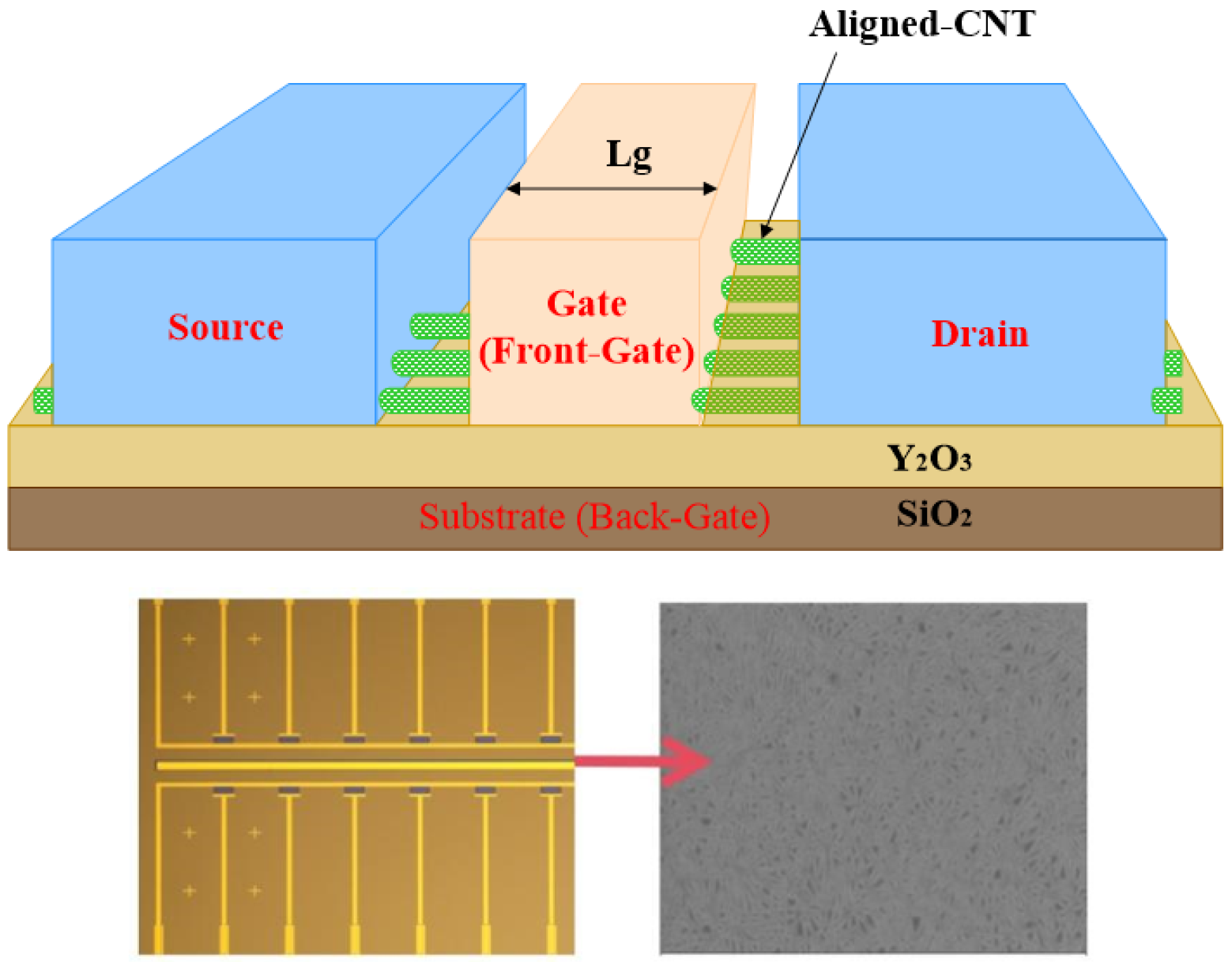

2. Review of the CNTFET Process

3. Compact Model, PDK, and Standard Cell Library

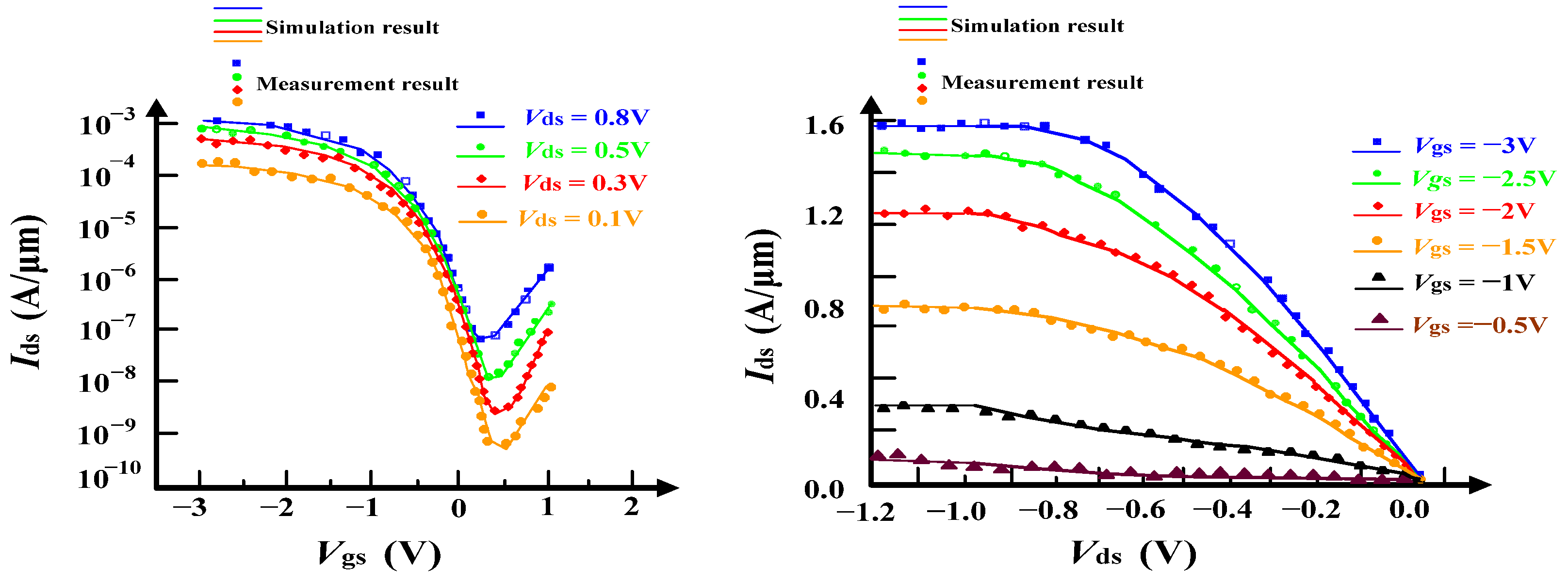

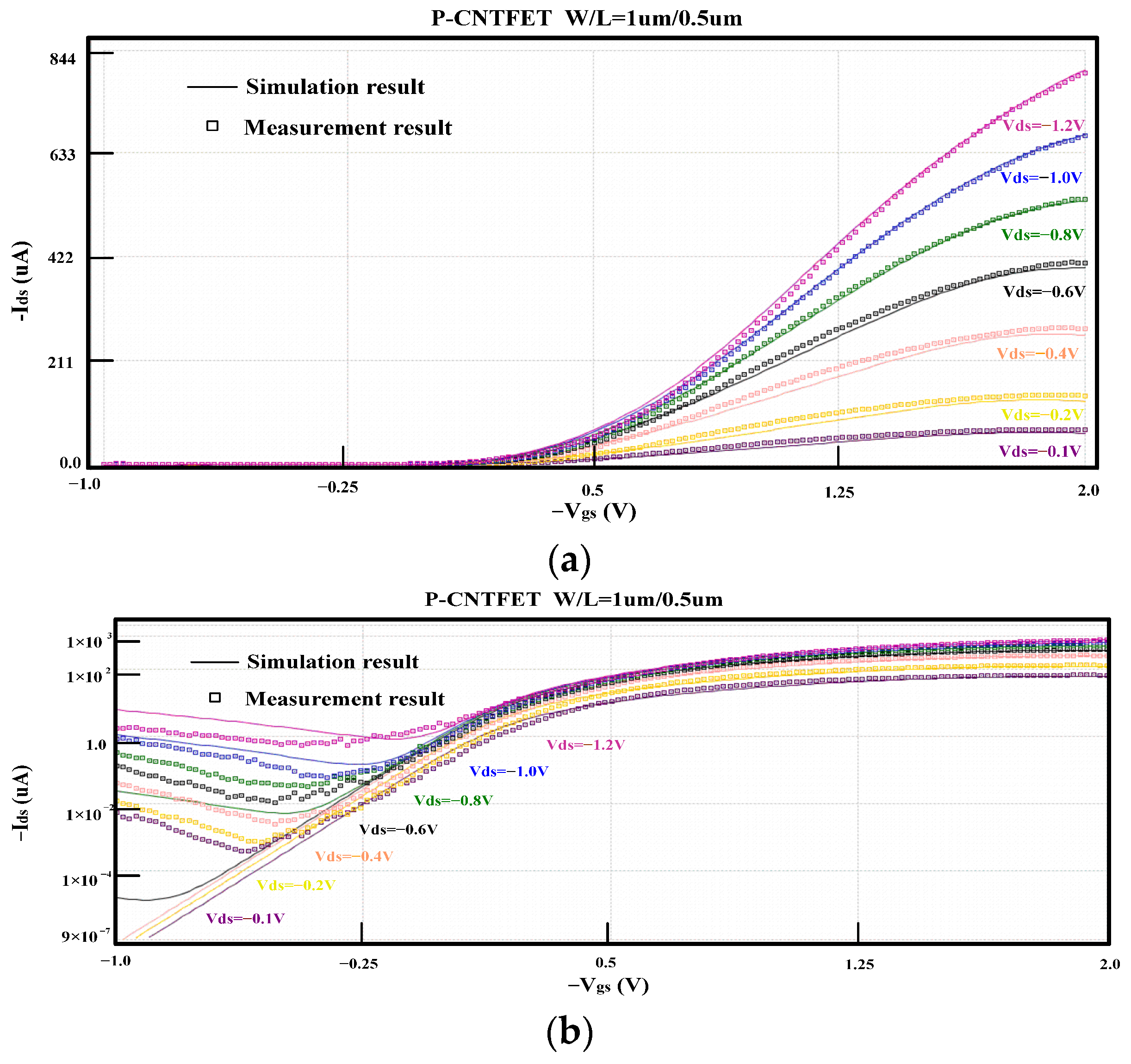

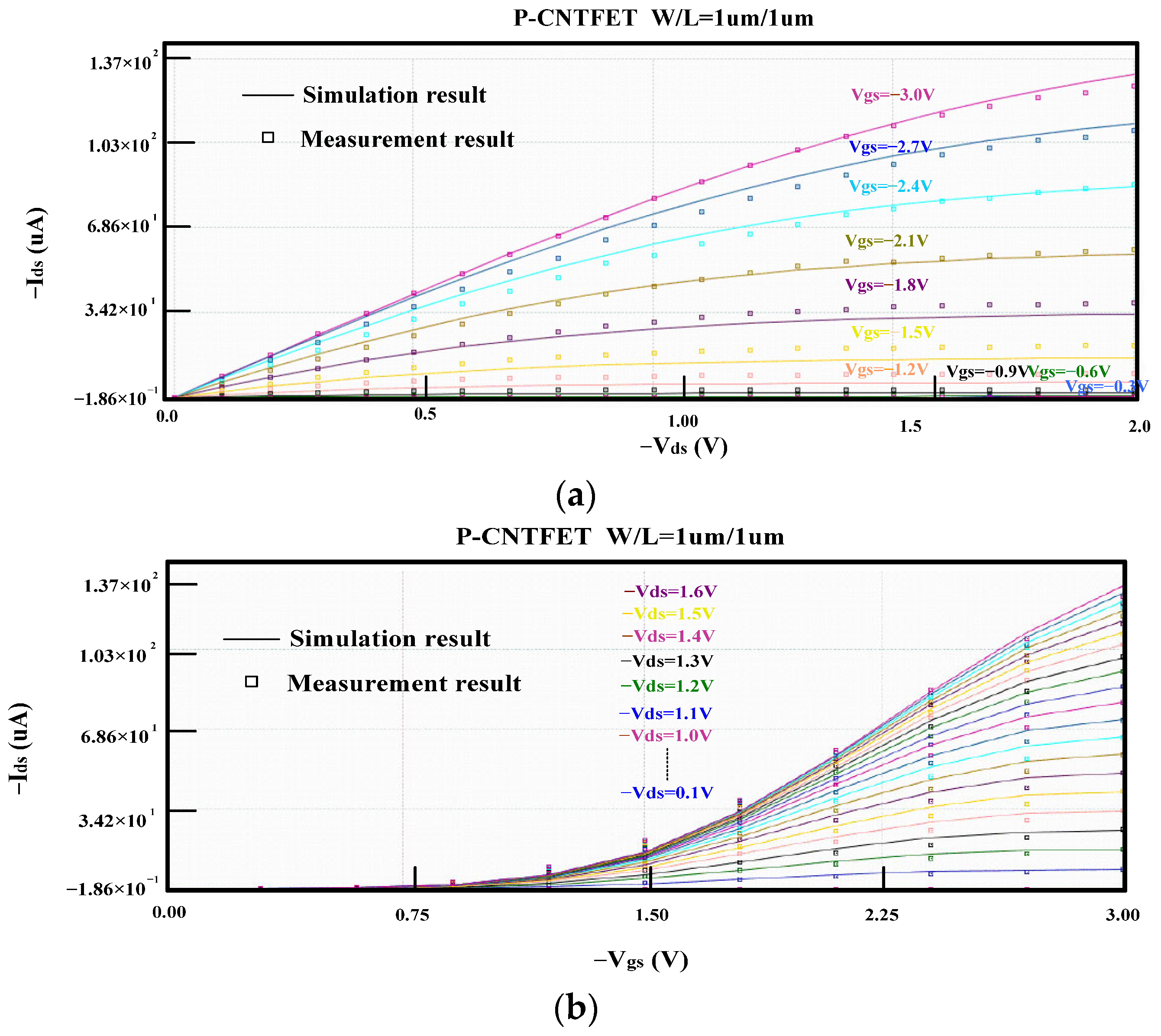

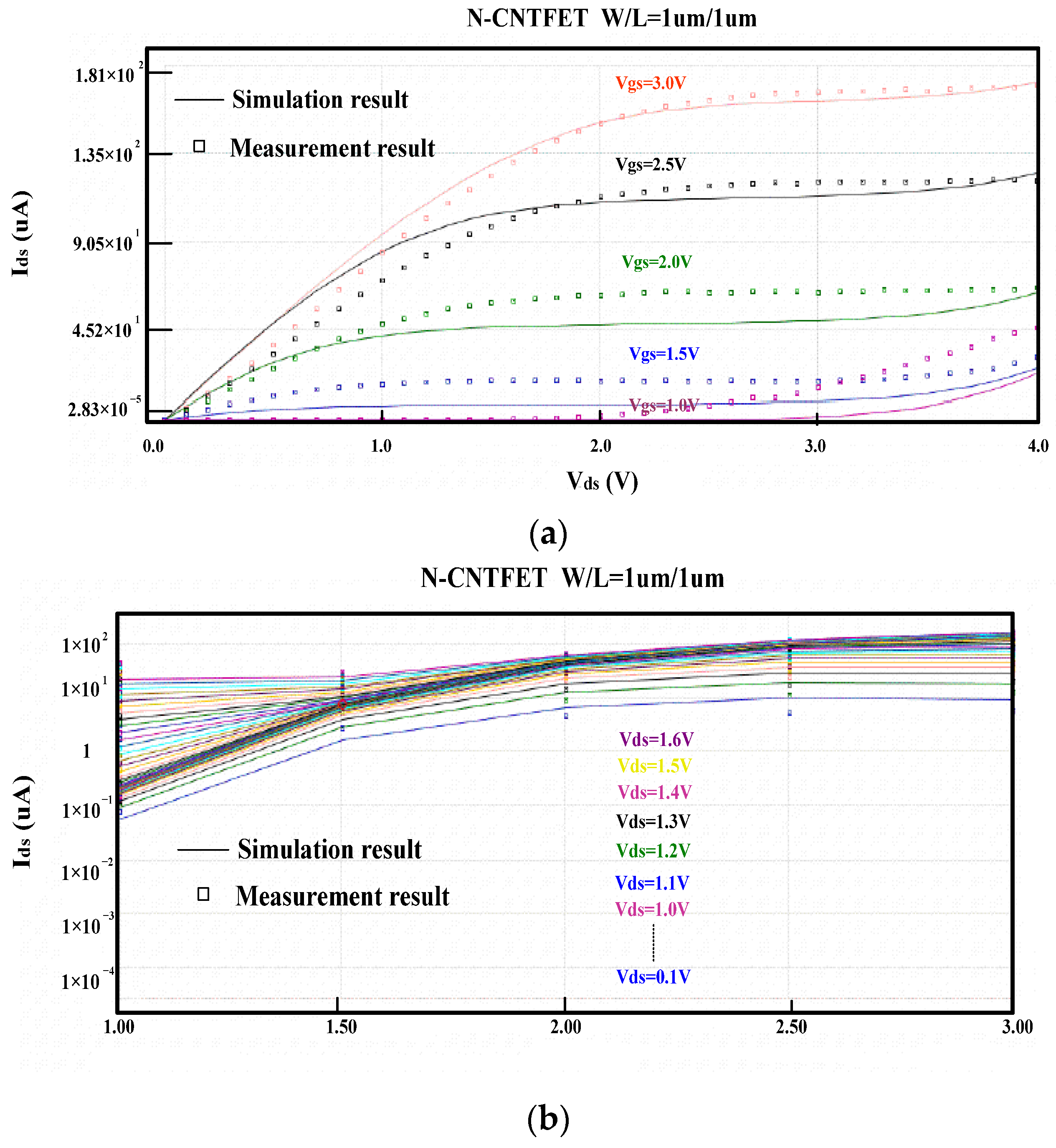

3.1. Compact Model

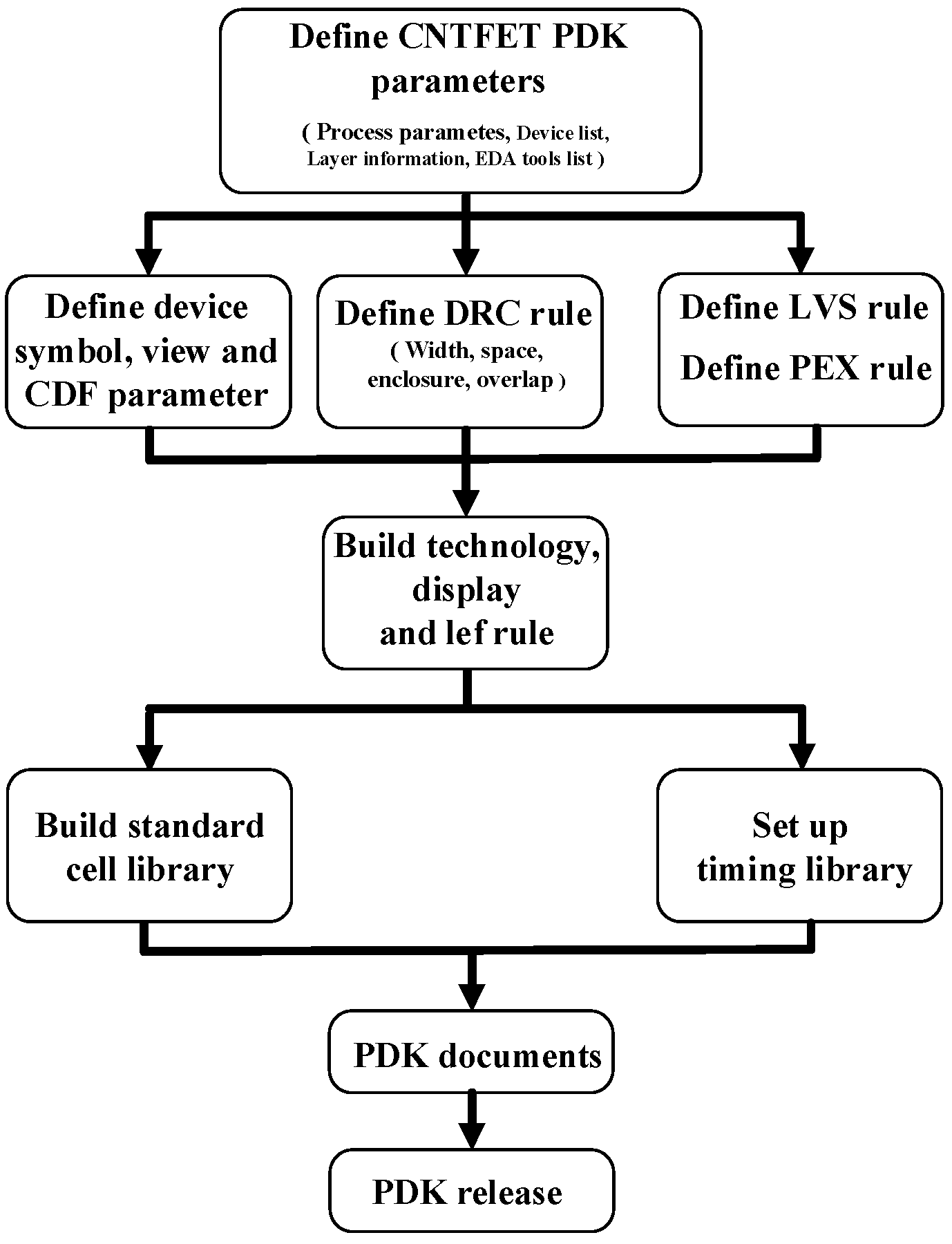

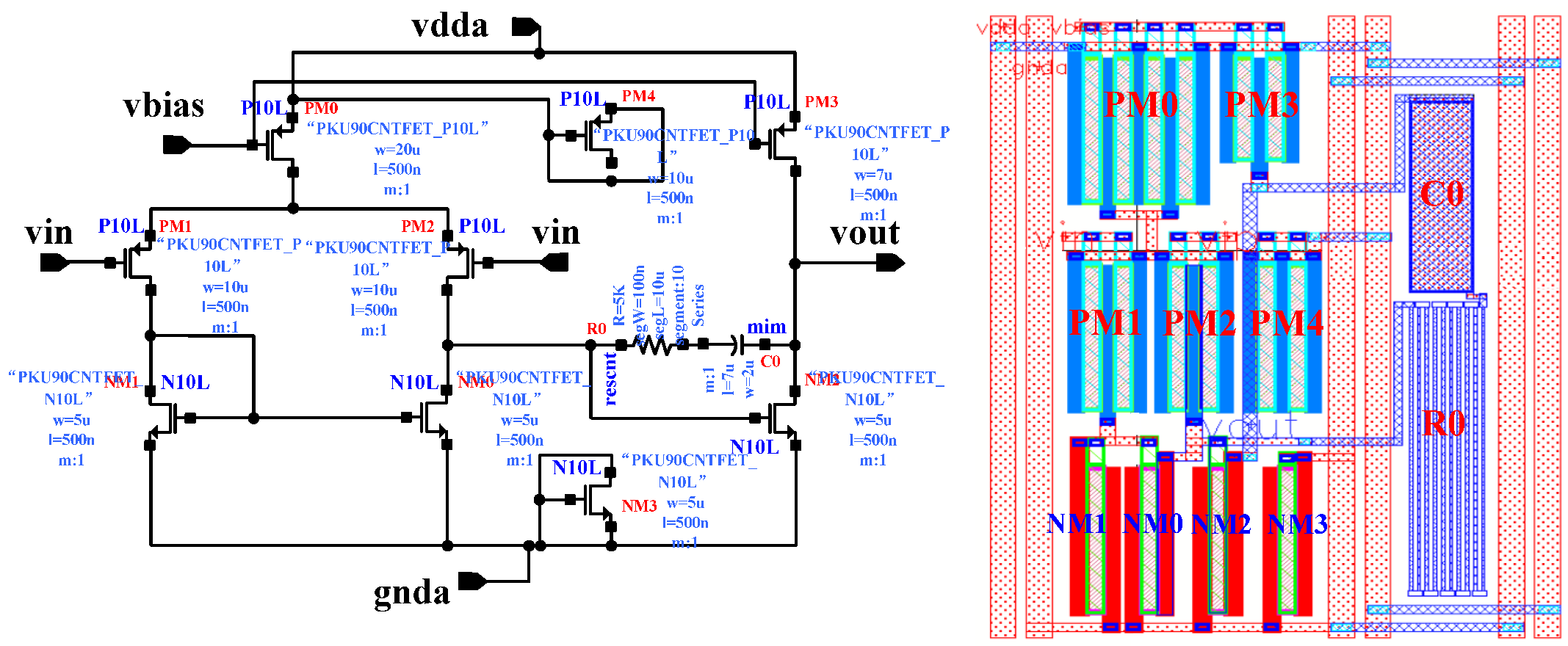

3.2. Full-Custom PDK

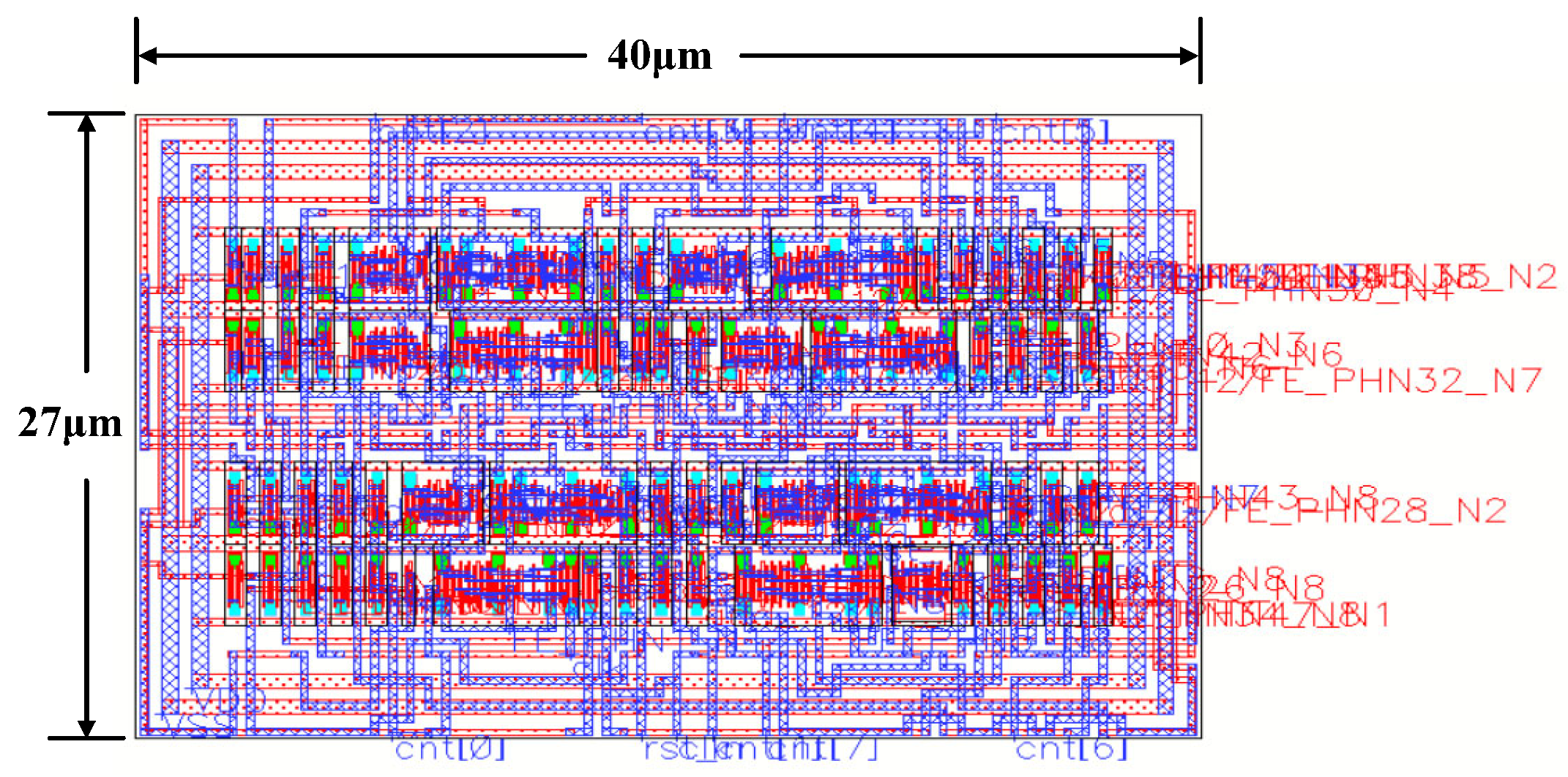

3.3. Standard Cell Library

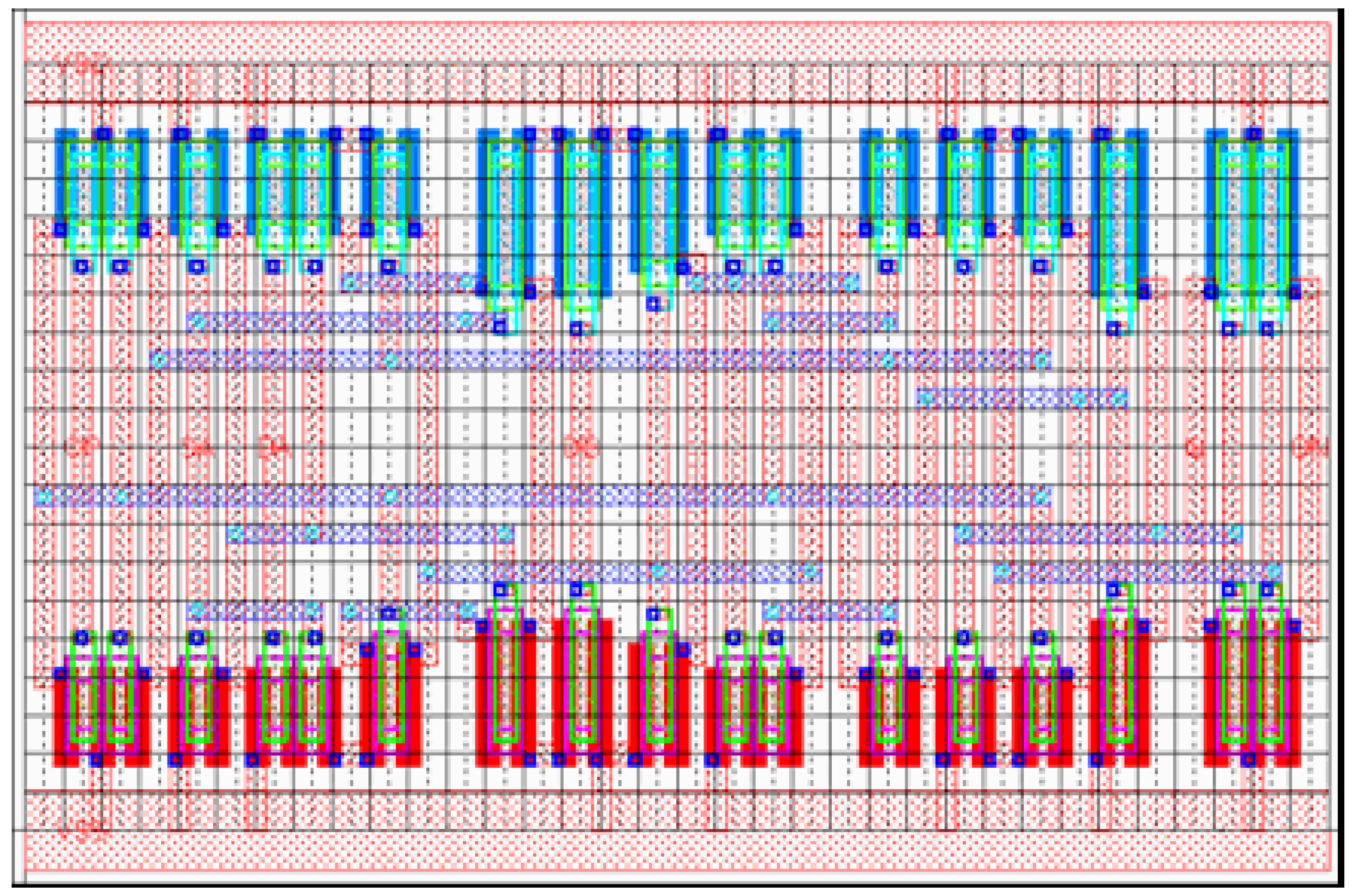

- The P/N-CNTFET transistor has been established and exists in the PDK, so the standard cell layout is implemented using Pcell.

- The resolution of the layout grid is 0.005 um.

- The layout grid is H_pitch = 160 nm, V_pitch = 160 nm. H_pitch, V_pitch is the minimum grid size for the vertical and horizontal directions, respectively. Finally, the standard cell has both horizontal and vertical dimensions that are integer multiples of 160 nm. The main reason is that the spacing between M1 and M2 is 80 um, so the horizontal and vertical dimensions are both integer multiples of the minimum spacing (160 nm).

- In the selection of the device size, because the driving capability ratio of PMOS to NMOS is approximately 1:1.2, the size ratio of PMOS to NMOS is 1.2:1.

- Metal1 routes vertically, and Metal2 routes horizontally.

- A layer of prBoundary is added as an identifier for grid. Each sub-grid is 160 nm. The upper boundary of the prBoundary falls on the upper metal boundaries of the power supply VDD; the lower boundary of it falls on the lower metal boundaries of the ground VSS.

- All ports need to be labeled on horizontal half-grid points and vertical full-grid points.

- For each label, it must be calibrated on Metal1 and at the center of the VIA. Therefore, sufficient Metal1 area should be reserved for the VIA. The boundary around Metal1 must ensure that the distance to the center of the label is greater than the metal coverage requirement (that is, the label must be located in the middle of Metal1, ensuring that at least one VIA can be placed there and that the VIA is covered by metal).

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Zhang, J.; Lin, A.; Patil, N.; Wei, H.; Wei, L.; Wong, H.S.; Mitra, S. Robust digital VLSI using carbon nanotubes. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2012, 31, 453–471. [Google Scholar] [CrossRef]

- Brady, G.J.; Way, A.J.; Safron, N.S.; Evensen, H.T.; Gopalan, P.; Arnold, M.S. Quasi-ballistic carbon nanotube array transistors with current density exceeding Si and GaAs. Sci. Adv. 2016, 2, e1601240. [Google Scholar] [CrossRef]

- Qiu, C.; Zhang, Z.; Xiao, M.; Yang, Y.; Zhong, D.; Peng, L.-M. Scaling carbon nanotube complementary transistors to 5-nm gate lengths. Science 2017, 355, 271–276. [Google Scholar] [CrossRef] [PubMed]

- Franklin, A.D.; Luisier, M.; Han, S.-J.; Tulevski, G.; Breslin, C.M.; Gignac, L.; Lundstrom, M.S.; Haensch, W. Sub-10 nm carbon nanotube transistor. Nano Lett. 2012, 12, 758–762. [Google Scholar] [CrossRef]

- Yao, Z.; Kane, C.L.; Dekker, C. High-field electrical transport in single-wall carbon nanotubes. Phys. Rev. Lett. 2000, 84, 2941–2944. [Google Scholar] [CrossRef]

- Guo, J.; Datta, S.; Lundstrom, M. A numerical study of scaling issues for Schottky-Barrier carbon nanotube transistors. IEEE Trans. Electron Devices 2004, 51, 172–177. [Google Scholar] [CrossRef]

- Guo, J.; Lundstrom, M. Role of phonon scattering in carbon nanotube field-effect transistors. Appl. Phys. Lett. 2005, 86, 193103. [Google Scholar] [CrossRef]

- Hazeghi, A.; Krishnamohan, T.; Wong, H.-S.P. Schottky-barrier carbon nanotube field-effect transistor modeling. IEEE Trans. Electron Devices 2007, 54, 439–445. [Google Scholar] [CrossRef]

- Zhang, Z.; Wang, S.; Ding, L.; Liang, X.; Pei, T.; Shen, J.; Xu, H.; Chen, Q.; Cui, R.; Li, Y.; et al. Self-aligned ballistic n-type single walled carbon nanotube field-effect transistors with adjustable threshold voltage. Nano Lett. 2008, 8, 3696–3701. [Google Scholar] [CrossRef] [PubMed]

- Raychowdhury, A.; Mukhopadhyay, S.; Roy, K. A circuit-compatible model of ballistic carbon nanotube field-effect transistors. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2004, 23, 1411–1420. [Google Scholar] [CrossRef]

- Robert-Peillard, A.; Rotkin, S.V. Modeling hysteresis phenomena in nanotube field-effect transistors. IEEE Trans. Nanotechnol. 2005, 4, 284–288. [Google Scholar] [CrossRef]

- Baumgardner, J.E.; Pesetski, A.A.; Murduck, J.M.; Przybysz, J.X.; Adam, J.D.; Zhang, H. Inherent linearity in carbon nanotube fieldeffect transistors. Appl. Phys. Lett. 2007, 91, 052107. [Google Scholar] [CrossRef]

- Estrada, D.; Dutta, S.; Liao, A.; Pop, E. Reduction of hysteresis for carbon nanotube mobility measurements using pulsed characterization. Nanotechnology 2010, 21, 085702. [Google Scholar] [CrossRef]

- Koswatta, S.O.; Valdes-Garcia, A.; Steiner, M.B.; Lin, Y.-M.; Avouris, P. Ultimate RF performance potential of carbon electronics. IEEE Trans. Microw. Theory Technol. 2011, 59, 2739–2750. [Google Scholar] [CrossRef]

- Claus, M.; Haferlach, M.; Gross, D.; Schröter, M. Critical review of CNTFET compact models. Proc. WCM/NanoTech 2012, 2, 770–775. [Google Scholar]

- Alam, A.U.; Rogers, C.M.S.; Paydavosi, N.; Holland, K.D.; Ahmed, S.; Vaidyanathan, M. RF linearity potential of carbon-nanotube transistors versus MOSFETs. IEEE Trans. Nanotechnol. 2013, 12, 340–351. [Google Scholar] [CrossRef]

- Shi, C.; Miwa, S.; Yang, T. CNFET7: An Open Source Cell Library for 7-nm CNFET Technology. In Proceedings of the 2023 28th Asia and South Pacific Design Automation Conference (ASP-DAC), Tokyo, Japan, 16–19 January 2023. [Google Scholar]

- Deng, J.; Wong, H.-S.P. A Compact SPICE Model for Carbon-Nanotube Field-Effect Transistors Including Nonidealities and Its Application—Part I: Model of the Intrinsic Channel Region. IEEE Trans. Electron Devices 2007, 57, 3186–3194. [Google Scholar] [CrossRef]

- Deng, J.; Wong, H.-S.P. A Compact SPICE Model for Carbon-Nanotube Field-Effect Transistors Including Nonidealities and Its Application—Part II: Full Device Model and Circuit Performance Benchmarking. IEEE Trans. Electron Devices 2007, 54, 3195–3205. [Google Scholar] [CrossRef]

- Najari, M.; Fregonese, S.; Maneux, C.; Mnif, H.; Masmoudi, N.; Zimmer, T. Schottky barrier carbon nanotube transistor: Compact modeling, scaling study, and circuit design applications. IEEE Trans. Electron Devices 2011, 58, 195–205. [Google Scholar] [CrossRef]

- Gelao, G.; Marani, R.; Diana, R.; Perri, A.G. Perri. A semiempirical SPICE model for n-type conventional CNTFETs. IEEE Trans. Nanotechnol. 2011, 10, 506–512. [Google Scholar] [CrossRef]

- Luo, J.; Wei, L.; Lee, C.-S.; Franklin, A.D.; Guan, X.; Pop, E.; Antoniadis, D.A.; Wong, H.-S.P. Compact Model for Carbon Nanotube Field-Effect Transistors Including Nonidealities and Calibrated with Experimental Data down to 9-nm Gate Length. IEEE Trans. Electron Devices 2013, 60, 1834–1843. [Google Scholar] [CrossRef]

- Lee, C.; Pop, E.; Franklin, A.; Haensch, W.; Wong, H.S.P. A Compact Virtual-Source Model for Carbon Nanotube FETs in the Sub-10-nm Regime—Part I: Intrinsic Elements. Trans. Electron Devices 2015, 62, 3061–3069. [Google Scholar] [CrossRef]

- Lee, C.; Pop, E.; Franklin, A.; Haensch, W.; Wong, H.S.P. A Compact Virtual-Source Model for Carbon Nanotube FETs in the Sub-10-nm Regime—Part II: Extrinsic Elements, Performance Assessment, and Design Optimization. Trans. Electron Devices 2015, 62, 3070–3078. [Google Scholar] [CrossRef]

- Avouris, P.; Chen, Z.; Perebeinos, V. Carbon-based electronics. Nat. Nanotechnol. 2007, 2, 605–615. [Google Scholar] [CrossRef] [PubMed]

- Franklin, A.D. Nanomaterials in transistors: From high-performance to thin-film applications. Science 2015, 349, Aab2750. [Google Scholar] [CrossRef]

- Geier, M.L.; McMorrow, J.J.; Xu, W.C.; Zhu, J.; Kim, C.H.; Marks, T.J.; Hersam, M.C. Solution-processed carbon nanotube thin-film complementary static random access memory. Nat. Nanotechnol. 2015, 10, 944–948. [Google Scholar] [CrossRef]

- Cao, Q.; Han, S.J.; Tersoff, J.; Franklin, A.D.; Zhu, Y.; Zhang, Z.; Tulevski, G.S.; Tang, J.S.; Haesch, W. End-bonded contacts for carbon nanotube transistors with low, size-independent resistance. Science 2015, 350, 68–72. [Google Scholar] [CrossRef] [PubMed]

- Lin, Y.; Cao, Y.; Ding, S.; Zhang, P.; Xu, L.; Liu, C.; Hu, Q.; Jin, C.; Peng, L.-M.; Zhang, Z. Scaling aligned carbon nanotube transistors to a sub-10 nm node. Science 2023, 6, 506–515. [Google Scholar] [CrossRef]

- Liu, Y. Research on the Mechanism and Model of CNTFET Device Based on Nano Model. Master’s Dissertation, University of Chinese Academy of Sciences, Beijing, China, 2022. [Google Scholar]

- Zhang, Y.; Yang, Y.; Yang, T.; Zhang, Y. A Compact Physical Drain Current Model of Multi Tube Carbon Nanotube Field Effect Transistor Including Diameter Dispersion Effects. IEEE Trans. Electron Devices 2021, 68, 6571–6579. [Google Scholar] [CrossRef]

- BSIM Group. BSIMSOIv4.4 MOSFET MODEL Users’ Manual; University of California: Berkeley, CA, USA, 2010. [Google Scholar]

- Chen, K.; Ma, C.; Zhang, Q.; Li, Y.; Zhao, J.; Chen, M. FreePDK15TFET: An Open-source Process Design Kit for 15 nm CMOS and TFET devices. In Proceedings of the 2021 IEEE International Symposium on Circuits and Systems (ISCAS), Daegu, Republic of Korea, 22–28 May 2021. [Google Scholar]

- Frégonèse, S.; Maneux, C.; Zimmer, T. A Compact Model for Dual-Gate One-Dimensional FET: Application to Carbon-Nanotube FETs. Trans. Electron Devices 2011, 58, 206–215. [Google Scholar] [CrossRef]

| Parameter | Description |

|---|---|

| Lch | Channel length |

| Lgeff | Mean free path in the channel region of intrinsic CNTFET with imperfect elastic scattering |

| Lss | Source-extended region length of CNTFET |

| Ldd | Drain-extended region length of CNTFET |

| Efi | Fermi energy |

| Kgate | Dielectric constant of high-K top-gate dielectric material |

| Tox | Thickness of high-K top-gate dielectric material |

| Csub | Coupling capacitor between channel and back-gate (back-gate effect) |

| Ccsd | Coupling capacitor between channel and source/drain region |

| CoupleRatio | Percentage of Ccsd corresponding to the coupling capacitor between channel and drain |

| Vfbn, Vfbp | Flat band voltage of N-CNTFET and P-CNTFET |

| Pitch | Distance between centers of two adjacent CNTs in the device |

| CNTPos | Position of carbon nanotubes under gate |

| n1, n2 | Chirality of CNTFET |

| tubes | Number of carbon nanotubes in device |

| coeffvg0, coeffvg1, coeffvg2 | Fitting parameters |

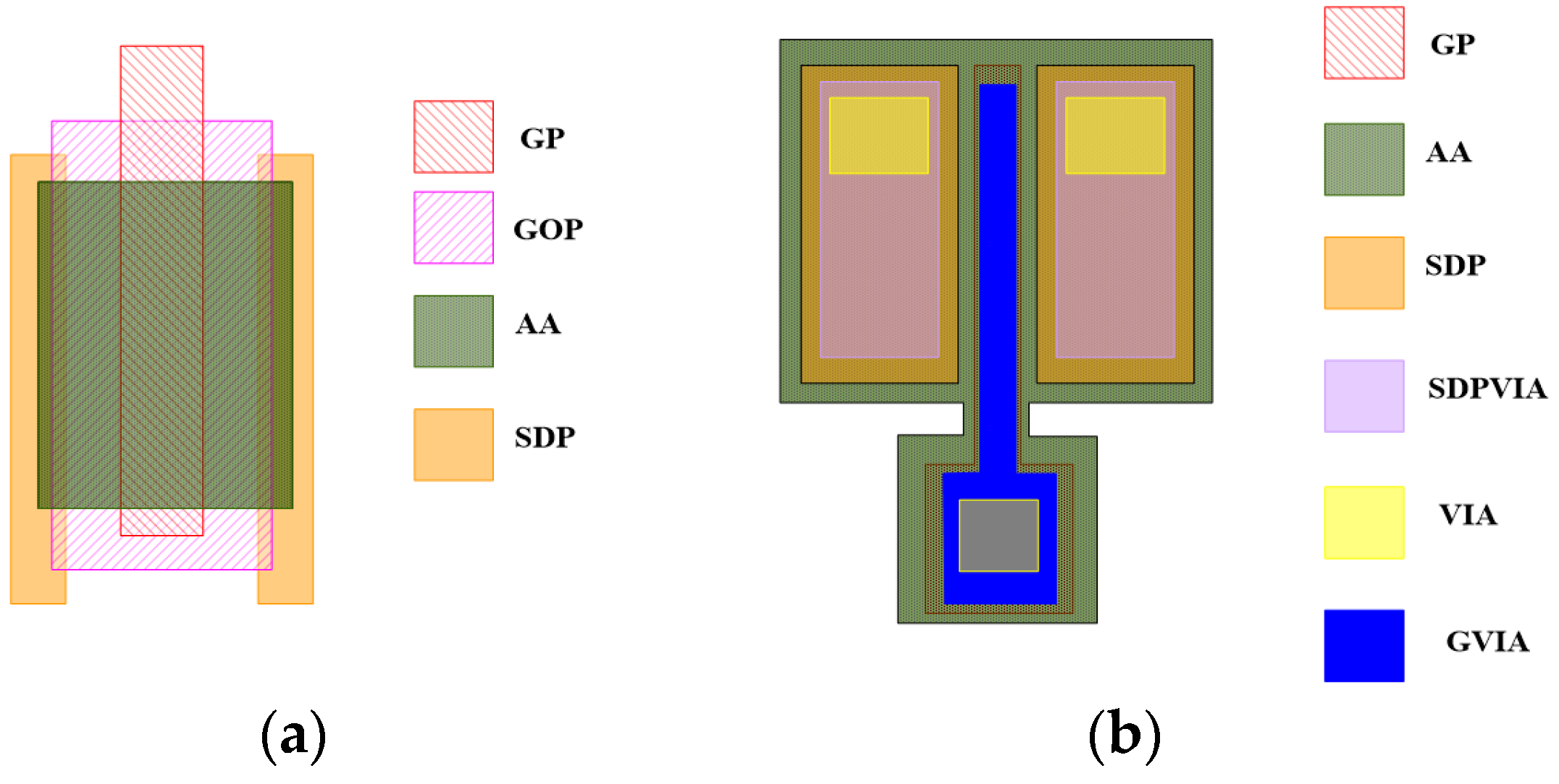

| Layer | Definition |

|---|---|

| GP | P gate |

| GOP | P gate oxygen |

| AA | Active area |

| SDP | P source–drain contact |

| SDPVIA | VIA of drain and source |

| VIA | Standard VIA |

| GVIA | VIA of gate |

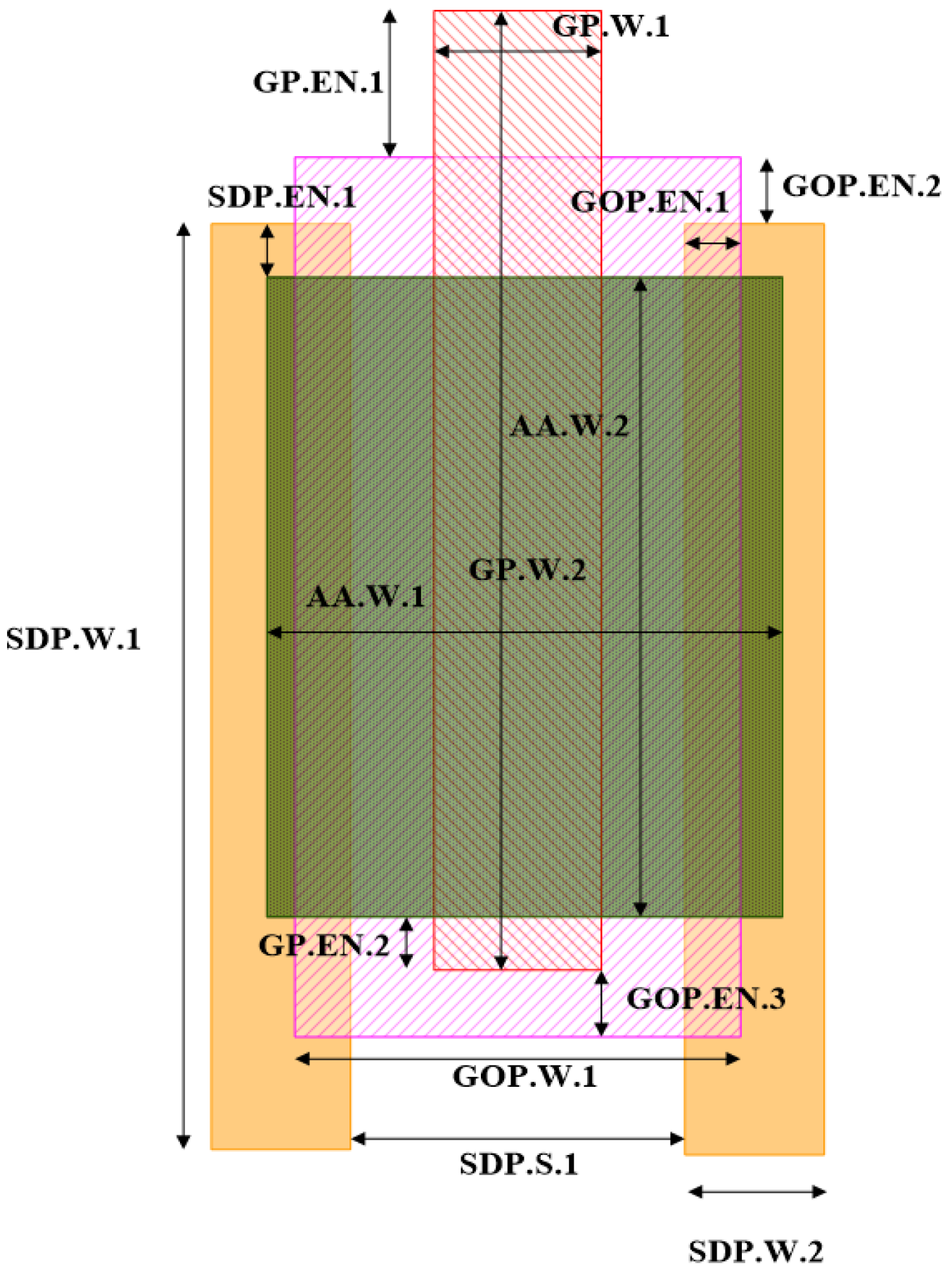

| DRC Rule | Description | Dimension (nm) |

|---|---|---|

| GP.W.1 | P gate length | ≥90 |

| GP.W.2 | P gate width | ≥110 |

| GOP.W.1 | P gate oxide width | ≥175 |

| GOP.EN.1 | Horizontal extension of P gate oxide to SDP | 15 |

| GOP.EN.2 | Vertical extension of P gate oxide to SDP | 50 |

| GOP.EN.3 | Extension of P gate oxide to GP | 50 |

| AA.W.1 | Horizontal width of AA | ≥500 |

| AA.W.2 | Vertical width of AA | ≥200 |

| SDP.W.1 | Horizontal width of SDP | ≥700 |

| SDP.W.2 | Vertical width of SDP | ≥80 |

| SDP.S.1 | Space between SDP | ≥95 |

| SDP.EN.1 | Extension of SDP to AA | 50 |

| Category | Description | #Cells |

|---|---|---|

| Combinational | INVDx, BUFFDx, BUFTDx, ND2Dx, NR2Dx, AN2Dx, OR2Dx, XNR2Dx, XOR2Dx | 18 |

| Complex Logic | AO211Dx, OA211Dx, AOI211Dx, IAO21Dx, IOA21Dx, OAI211Dx, MUX2Dx, MUX2NDx | 16 |

| Latch | LHCNDx, LNCNDx | 4 |

| Flip-Flop | DFXDx | 2 |

| Scan Cell | SDFDx, SDFKCNDx | 2 |

| Delay Cell | DELx | 2 |

| Clock Buffer | CKBDx, CKNDx | 2 |

| Adder | FA1Dx, HA1Dx | 2 |

| Tie-High/Tie-Low Cell | TIEH, TIEL | 2 |

| Filler Cell for Core | FILL | 2 |

| Decoupling Cell | DCAPx | 2 |

| Parameter | [18] | [22] | [23] | [34] | This Work |

|---|---|---|---|---|---|

| Technology (nm) | 32 | 9 | 15 | 200 | 90 |

| Gate structure | dual gate | single gate | single gate | dual gate | dual gate |

| Simulation tool | HSPICE | HSPICE | HSPICE | HSPICE | HSPICE |

| Method | numerical analysis | semi-analytical | virtual source (VS) | numerical analysis | numerical analysis |

| Convergence | good | good | good | good | good |

| Characteristics | quantum confinement, scattering, screening effect | contact resistance modeling, tunneling | effective mobility, inverse subthreshold slope degradation, quantum capacitance | Schottky barrier, electrostatic modeling, tunneling | back-gate effect, transmission probability, tunneling |

| Standard Cell | Description | #Cells |

|---|---|---|

| HA1D0 | Full adder | 6 |

| INVD0 | Inverter | 1 |

| XOR2D1 | XOR gate | 1 |

| DFXD1 | Flip-flop | 8 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, L.; Zhang, Y.; Chen, Z.; Chen, J.; Chen, H.; Jiang, J.; Chen, C. Full-Custom 90 nm CNTFET Process Design Kit: Characterization, Modeling, and Implementation. Electronics 2024, 13, 605. https://doi.org/10.3390/electronics13030605

Chen L, Zhang Y, Chen Z, Chen J, Chen H, Jiang J, Chen C. Full-Custom 90 nm CNTFET Process Design Kit: Characterization, Modeling, and Implementation. Electronics. 2024; 13(3):605. https://doi.org/10.3390/electronics13030605

Chicago/Turabian StyleChen, Liming, Yuyan Zhang, Zhifeng Chen, Jiming Chen, Huangwei Chen, Jianhua Jiang, and Chengying Chen. 2024. "Full-Custom 90 nm CNTFET Process Design Kit: Characterization, Modeling, and Implementation" Electronics 13, no. 3: 605. https://doi.org/10.3390/electronics13030605