A Power-Efficient High-Drive Current Mirror Combining a Regulated Cascode Topology with a Non-Linear CCII-Based Feedback

Abstract

:1. Introduction

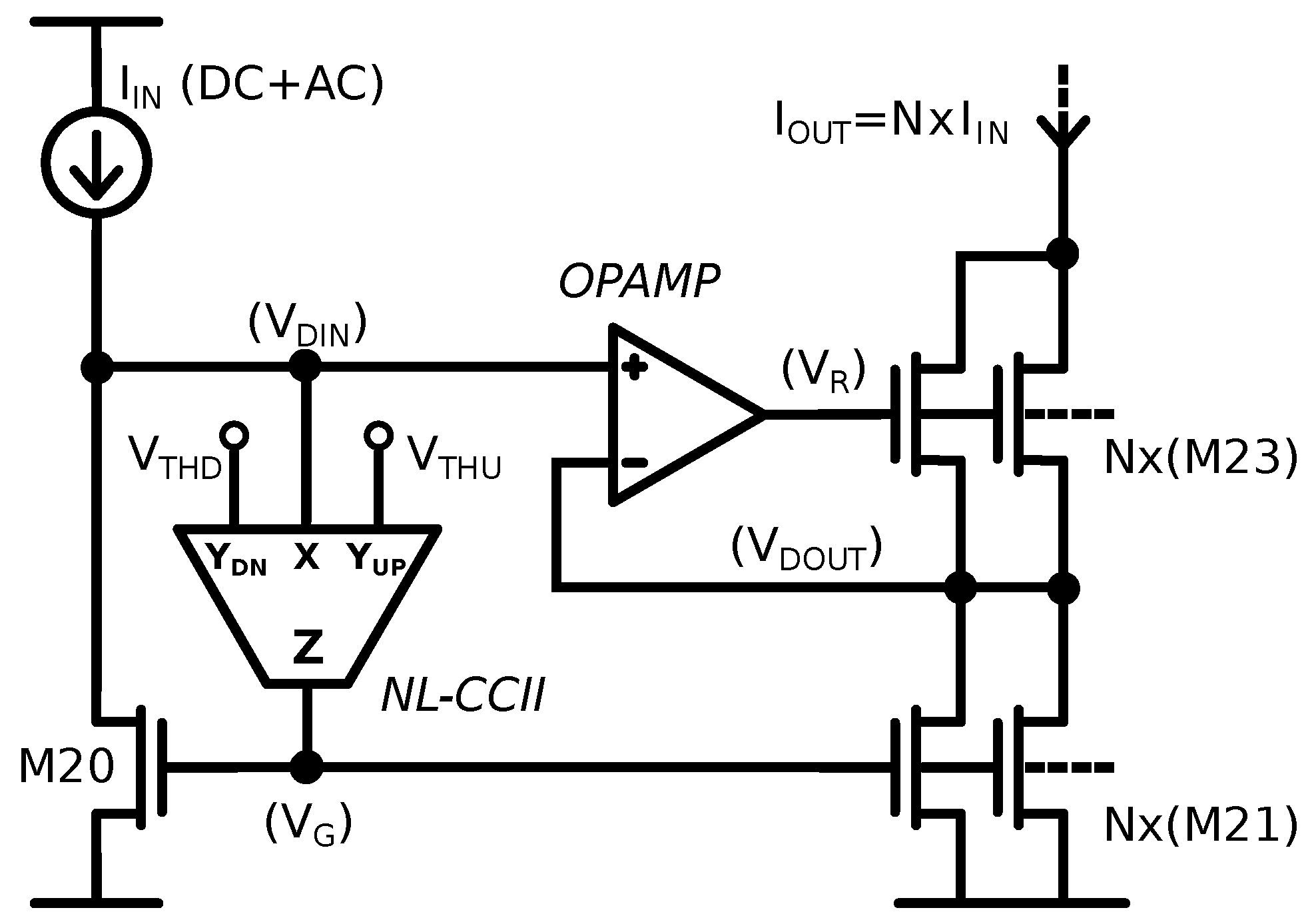

2. Improved Current Mirror with Non-Linear CCII-Based Feedback

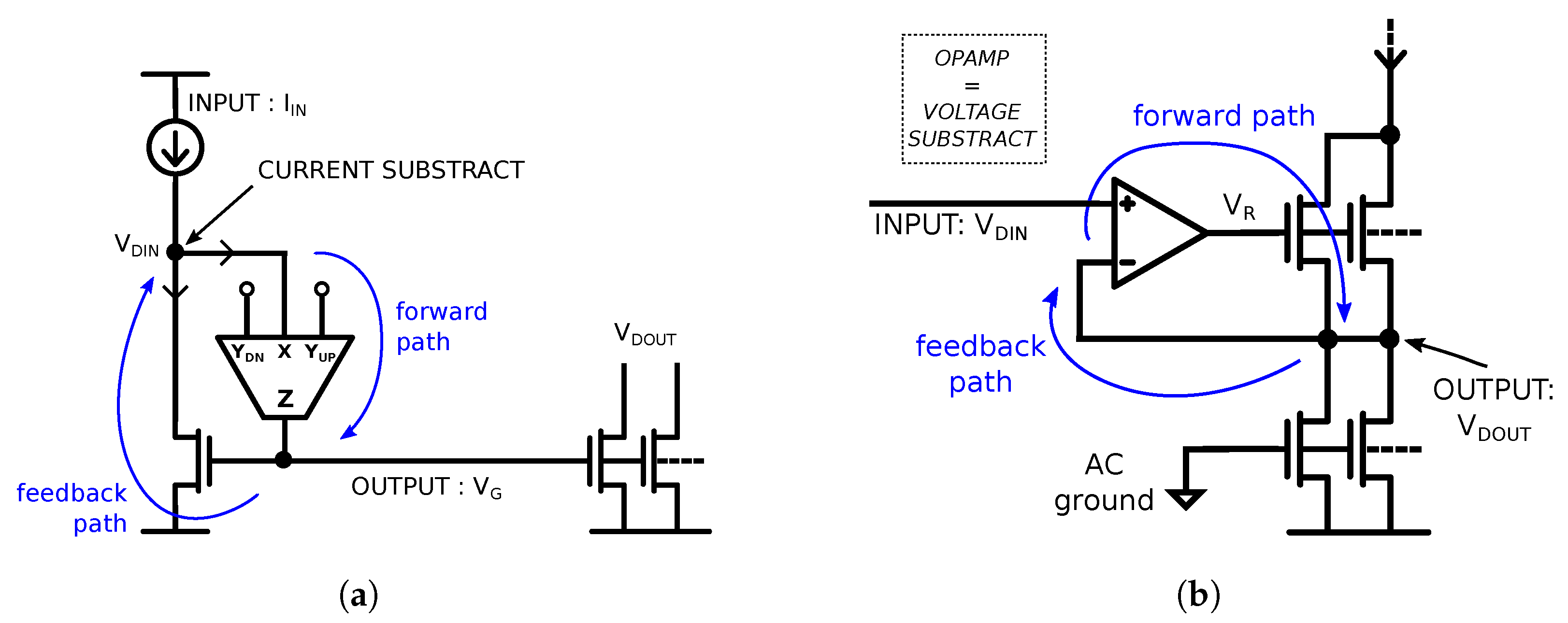

2.1. Principles of Operation

2.2. System Model

2.3. Design Considerations for the NL-CCII and the OPAMP

3. Simulation Results and Comparison with Reference Structures

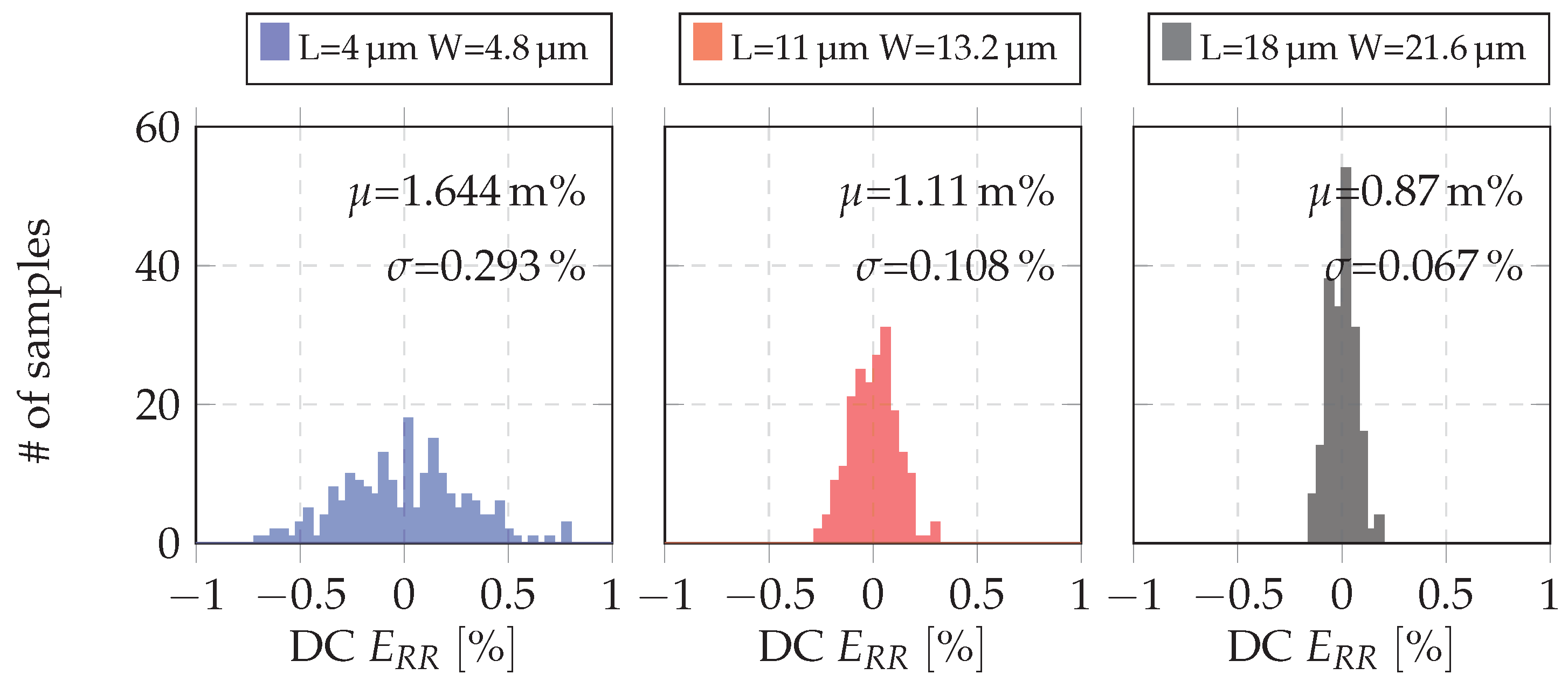

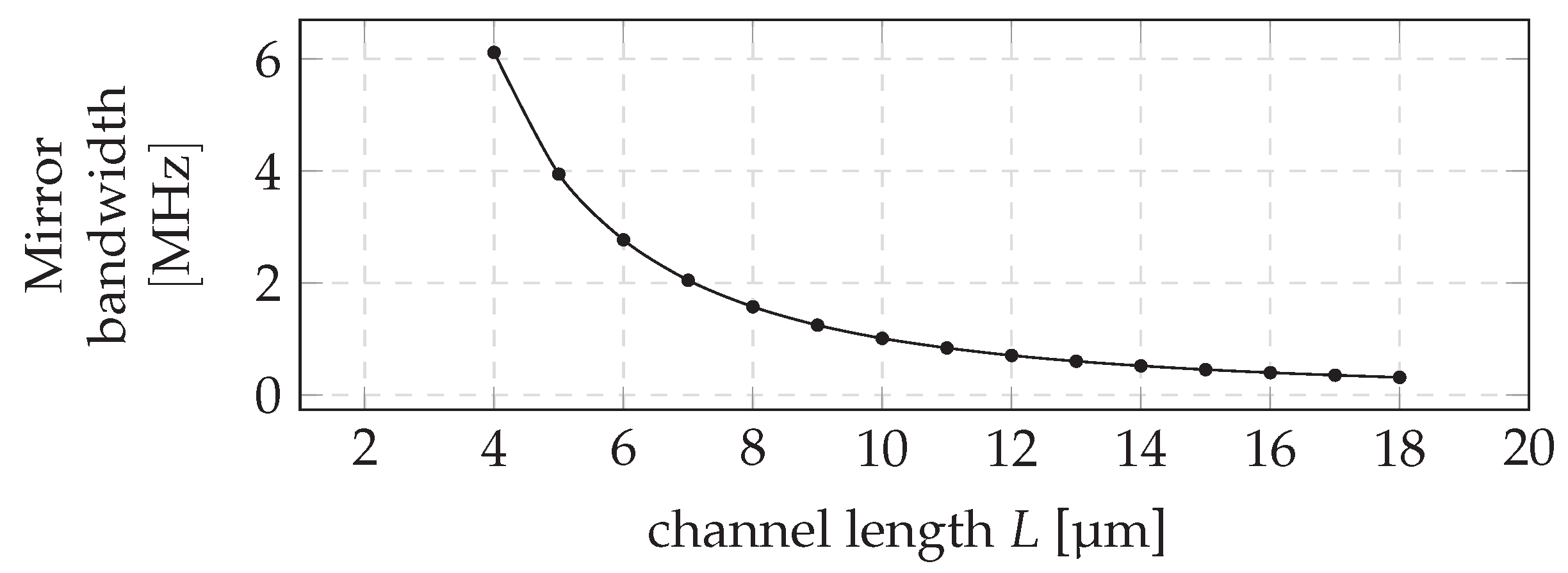

3.1. CM Sizing and Speed–Accuracy Trade-Off

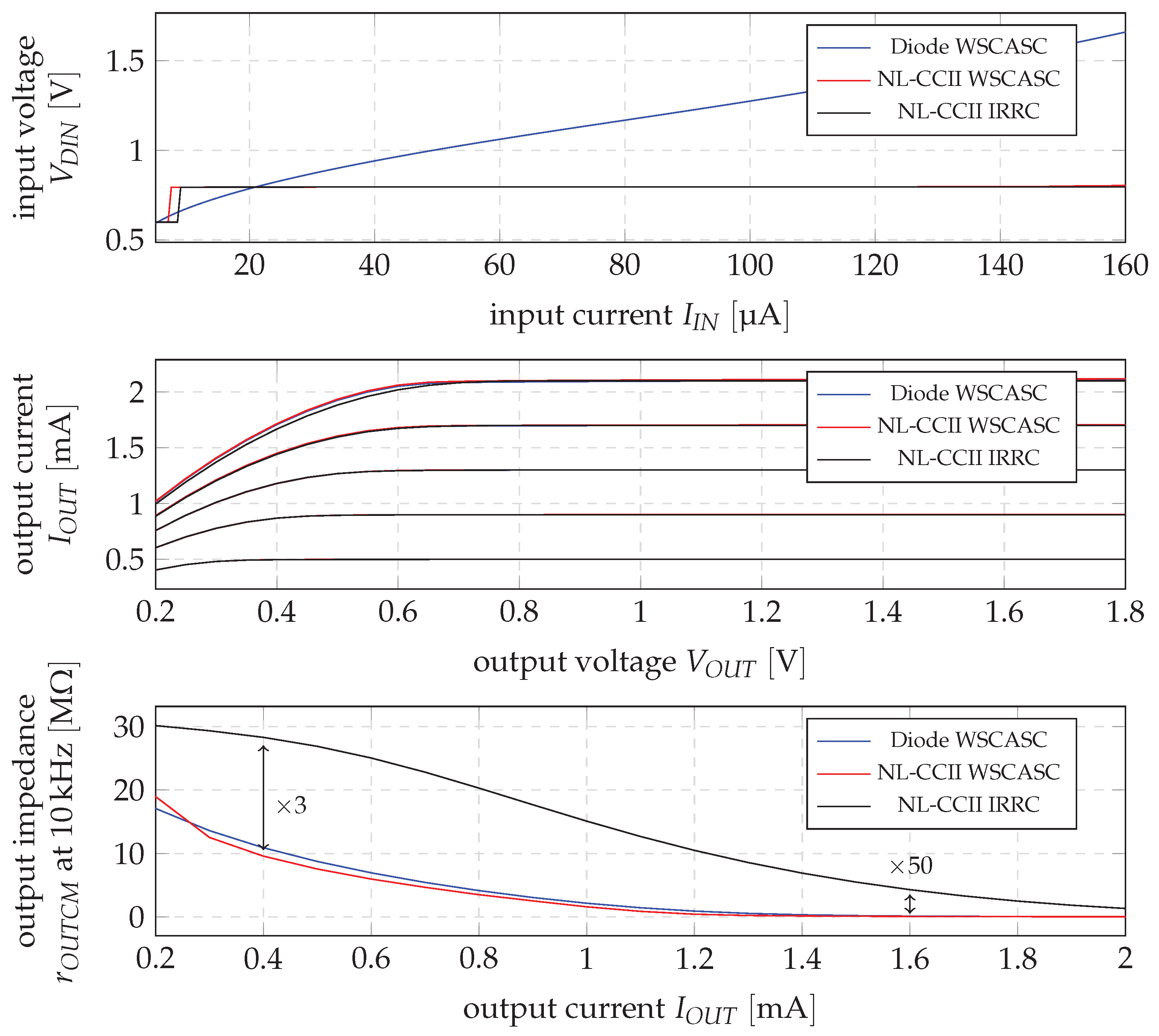

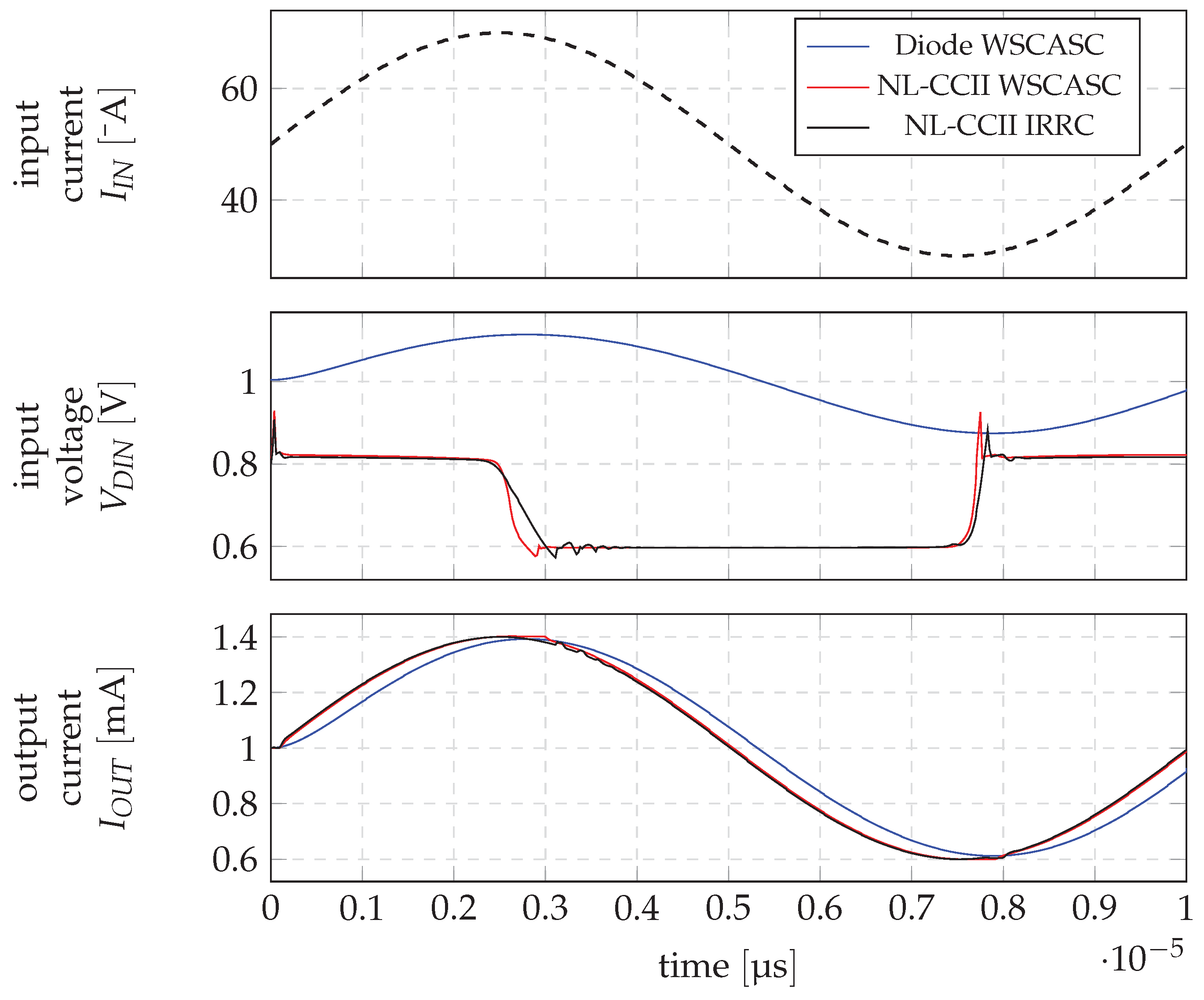

3.2. Typical Static and Dynamic Behaviour

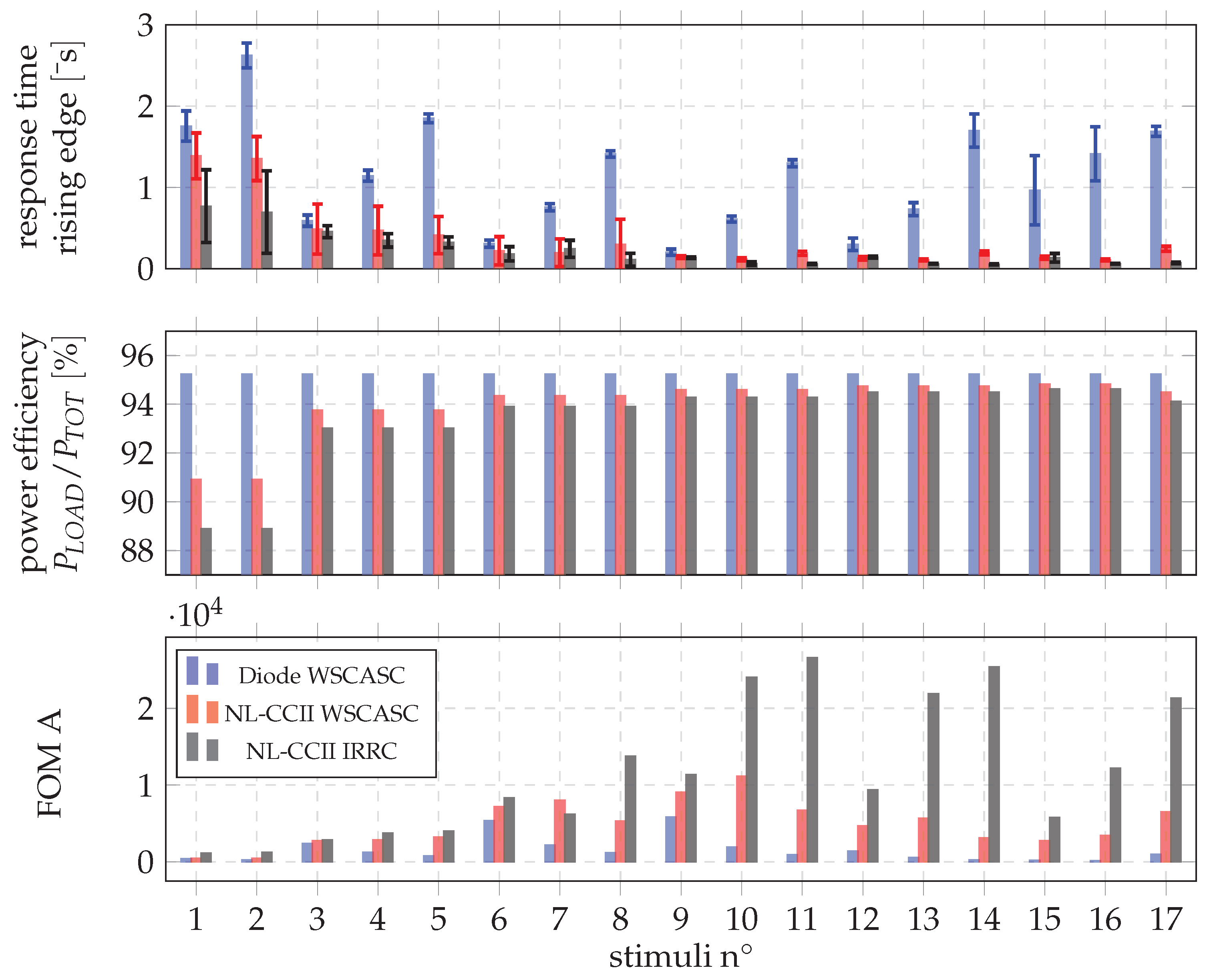

3.3. Statistical Results and Speed-Power-Accuracy Metrics

4. Discussion and Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Kinget, P.R.; Steyaert, M. Impact of transistor mismatch on the speed-accuracy-power trade-off of analog CMOS circuits. In Proceedings of the Custom Integrated Circuits Conference, San Diego, CA, USA, 5–8 May 1996. [Google Scholar] [CrossRef]

- Bastos, J.; Steyaert, M.; Pergoot, A.; Sansen, W. Mismatch Characterization of Submicron MOS Transistors. Analog. Integr. Circuits Signal Process. 1997, 12, 95–106. [Google Scholar] [CrossRef]

- Kinget, P.R. Device mismatch and tradeoffs in the design of analog circuits. IEEE J. Solid-State Circuits 2005, 40, 1212–1224. [Google Scholar] [CrossRef]

- Aggarwal, B.; Gupta, M.; Gupta, A.K. A low voltage wide swing level shifted FVF based current mirror. In Proceedings of the 2013 International Conference on Advances in Computing, Communications and Informatics (ICACCI), Mysore, India, 22–25 August 2013. [Google Scholar] [CrossRef]

- Serrano, T.; Linares-Barranco, B. The active-input regulated-cascode current mirror. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 1994, 41, 464–467. [Google Scholar] [CrossRef]

- Moazzeni, S.; Cowan, G.E.R. Application of active current mirrors to improve the speed of analog decoder circuits. In Proceedings of the 2009 52nd IEEE International Midwest Symposium on Circuits and Systems, Cancun, Mexico, 2–5 August 2009. [Google Scholar] [CrossRef]

- Julien, M.; Bernard, S.; Soulier, F.; Kerzerho, V.; Cathebras, G. Formal analysis of high-performance stabilized active-input current mirror. In Proceedings of the 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017. [Google Scholar] [CrossRef]

- Julien, M.; Bernard, S.; Soulier, F.; Kerzèrho, V.; Cathèbras, G. Breaking the speed-power-accuracy trade-off in current mirror with non-linear CCII feedback. Microelectron. J. 2019, 83, 77–85. [Google Scholar] [CrossRef]

- Aggarwal, B.; Gupta, M.; Gupta, A.K. A comparative study of various current mirror configurations: Topologies and characteristics. Microelectron. J. 2016, 53, 134–155. [Google Scholar] [CrossRef]

- Li, Y.; Wang, H.; Trik, M. Design and simulation of a new current mirror circuit with low power consumption and high performance and output impedance. Analog. Integr. Circuits Signal Process. 2024, 119, 29–41. [Google Scholar] [CrossRef]

- Xie, H.; Wang, Z.; Liu, G.; Lu, J.; Yi, X. A novel active-input cascode current mirror with high precision and low power dissipation. Eng. Rep. 2022, 4, e12451. [Google Scholar] [CrossRef]

- Pennisi, S. A low-voltage design approach for class AB current-mode circuits. IEEE Trans. Circuits Syst. II Analog. Digit. Signal Process. 2002, 49, 273–279. [Google Scholar] [CrossRef]

- Safari, L.; Minaei, S. A simple low voltage, high output impedance resistor based current mirror with extremely low input and output voltage requirements. In Proceedings of the 2016 39th International Conference on Telecommunications and Signal Processing (TSP), Vienna, Austria, 27–29 June 2016. [Google Scholar] [CrossRef]

- Vajpayee, P.; Srivastava, A.; Rajput, S.; Sharma, G. Low voltage regulated cascode current mirrors suitable for sub-1V operation. In Proceedings of the 2010 IEEE Asia Pacific Conference on Circuits and Systems, Kuala Lumpur, Malaysia, 6–9 December 2010. [Google Scholar] [CrossRef]

- Koliopoulos, C.; Psychalinos, C. A Comparative Study of the Performance of the Flipped Voltage Follower Based Low-Voltage Current Mirrors. In Proceedings of the 2007 International Symposium on Signals, Circuits and Systems, Iasi, Romania, 13–14 July 2007. [Google Scholar] [CrossRef]

| W/L | W/L | W/L | W/L | ||||

|---|---|---|---|---|---|---|---|

| M1 | M2 | M5 | M6 | ||||

| M3 | M4 | M7 | M8 | ||||

| M3B | M4B | M71 | M81 | ||||

| MA | MB | M72 | M82 | ||||

| MC | MG | M73 | M83 | ||||

| MD | MH | M9 | M12 | ||||

| ME | MI | M10 | M13 | ||||

| MF | MJ | M11 | M14 |

| at | at | ||

|---|---|---|---|

| DCO WSCASC CM | |||

| NL-CCII WSCASC CM | 244 | ||

| NL-CCII IRRC CM |

| THD (dB) | SFDR (dB) | |

|---|---|---|

| DCO WSCASC CM | −27.8 | 30.2 |

| NL-CCII WSCASC CM | −35.4 | 37.24 |

| NL-CCII IRRC CM | −43.7 | 46.32 |

| # | Bias | Step | # | Bias | Step |

|---|---|---|---|---|---|

| 1 | 10 | ± | 9 | 70 | ± |

| 2 | 10 | ±2 | 10 | 70 | ±2 |

| 3 | 30 | ± | 11 | 70 | ±20 |

| 4 | 30 | ±2 | 12 | 90 | ± |

| 5 | 30 | ±20 | 13 | 90 | ±2 |

| 6 | 50 | ± | 14 | 90 | ±20 |

| 7 | 50 | ±2 | 15 | 110 | ± |

| 8 | 50 | ±20 | 16 | 110 | ±2 |

| 17 | 60 | ±55 |

| Perf | This Work | [10] | [11] | [12] | [13] | [9] | [14] | [15] |

|---|---|---|---|---|---|---|---|---|

| Technology () | 0.18 | 0.18 | 0.18 | 0.5 | 0.18 | 0.18 | 0.25 | 0.18 |

| Supply voltage () | 1.8 | 1 | 1 | 1 | 0.9 | 1.8 | 1 | 1.5 |

| Min output current () | 100 | 50 | 0.1 | 10 | 0 | 0 | 0 | |

| Max output current () | 2000 | 1000 | 1000 | 100 | 60 | 280 | 300 | |

| Output error (%) | 0.06 | 2 | 0.16 | 0.4 | 0.3 | 0.8 | 5 | 2.4 |

| Resp. time at 1% () | 0.07 | 0.04 | 0.07 | 0.02 | ||||

| THD (%) FR = Full Range | 0.65 @ 36% FR | 0.8 @ 50% FR | 0.8 @ 50% FR | 1 | ||||

| Bandwidth (MHz) | 11.15 | 168 | 82 | 140 | 80 | 132 | 398 | |

| Power efficiency (%) | 94.12 | 50 | 50 | 30 | 50 | 33 | 40 | |

| FOM A | 22.7 | 0.63 | 1.07 | 0.33 | ||||

| FOM B | 17.5 | 4.2 | 25.6 | 10.5 | 8.25 | 2.63 | 3.08 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Julien, M.; Bernard, S.; Soulier, F.; Kerzérho, V.; Cathébras, G. A Power-Efficient High-Drive Current Mirror Combining a Regulated Cascode Topology with a Non-Linear CCII-Based Feedback. Electronics 2024, 13, 1556. https://doi.org/10.3390/electronics13081556

Julien M, Bernard S, Soulier F, Kerzérho V, Cathébras G. A Power-Efficient High-Drive Current Mirror Combining a Regulated Cascode Topology with a Non-Linear CCII-Based Feedback. Electronics. 2024; 13(8):1556. https://doi.org/10.3390/electronics13081556

Chicago/Turabian StyleJulien, Mohan, Serge Bernard, Fabien Soulier, Vincent Kerzérho, and Guy Cathébras. 2024. "A Power-Efficient High-Drive Current Mirror Combining a Regulated Cascode Topology with a Non-Linear CCII-Based Feedback" Electronics 13, no. 8: 1556. https://doi.org/10.3390/electronics13081556