Simulation Analysis in Sub-0.1 μm for Partial Isolation Field-Effect Transistors

Abstract

:1. Introduction

2. Experimental Methods

3. Results and Discussion

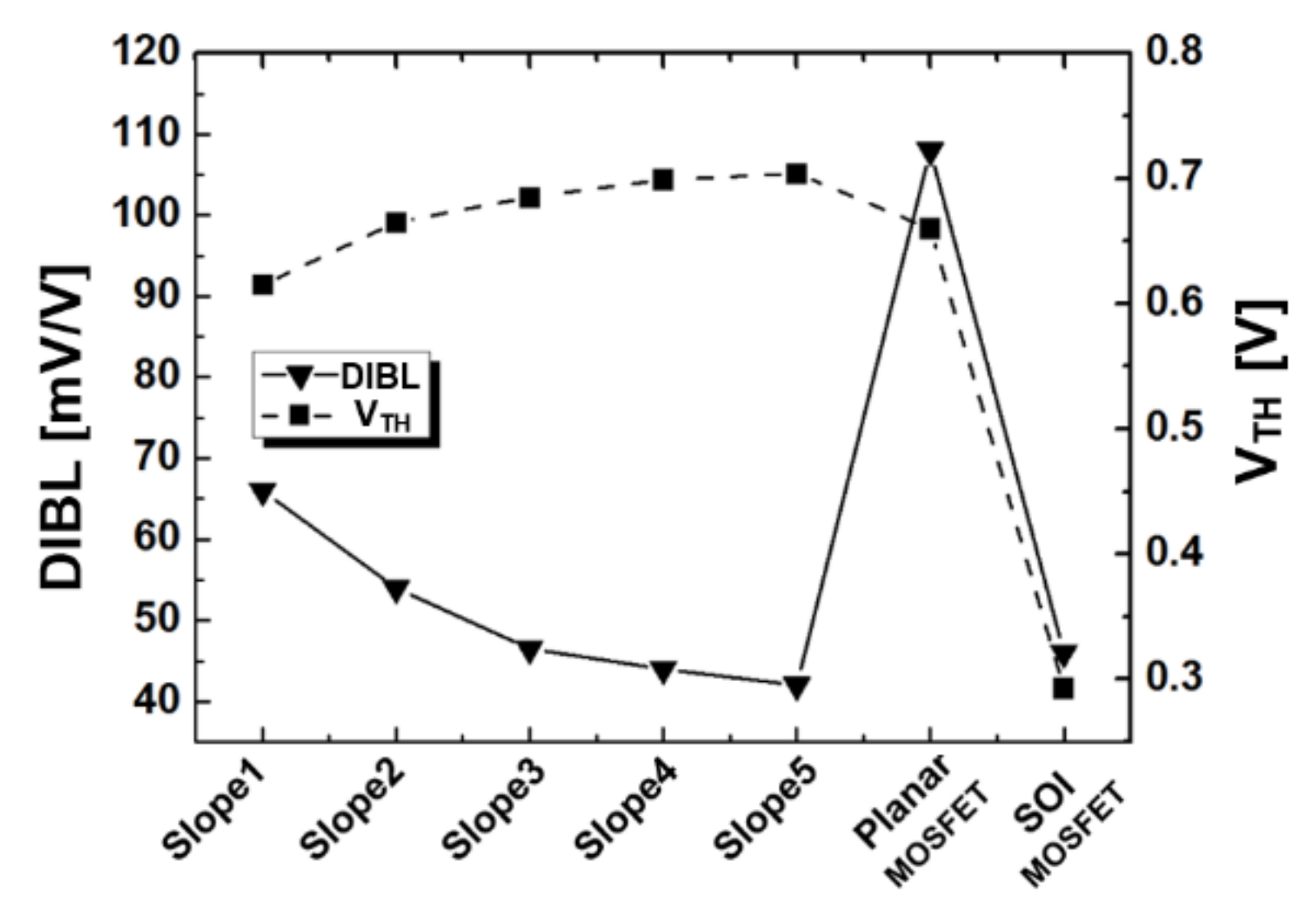

3.1. Five Slope

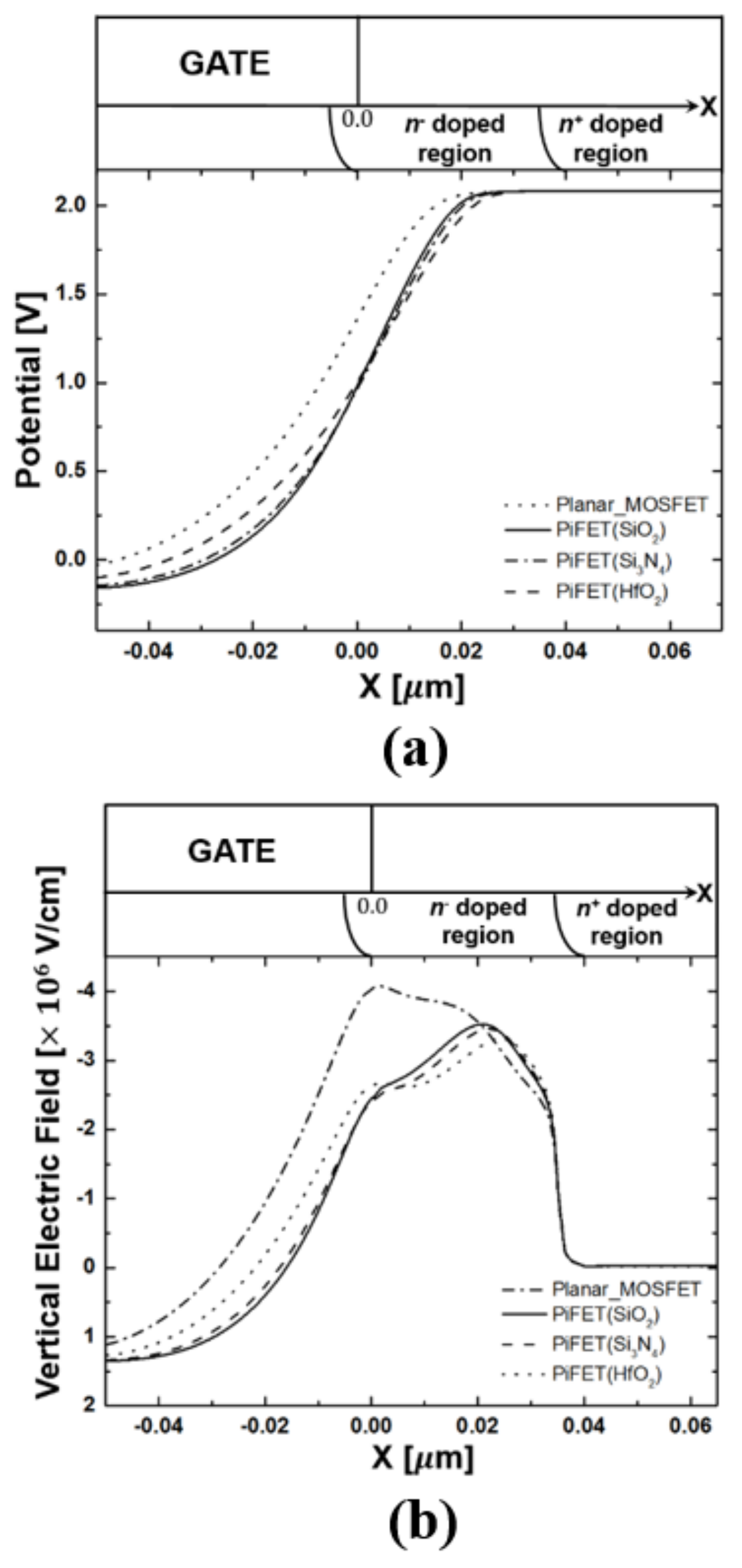

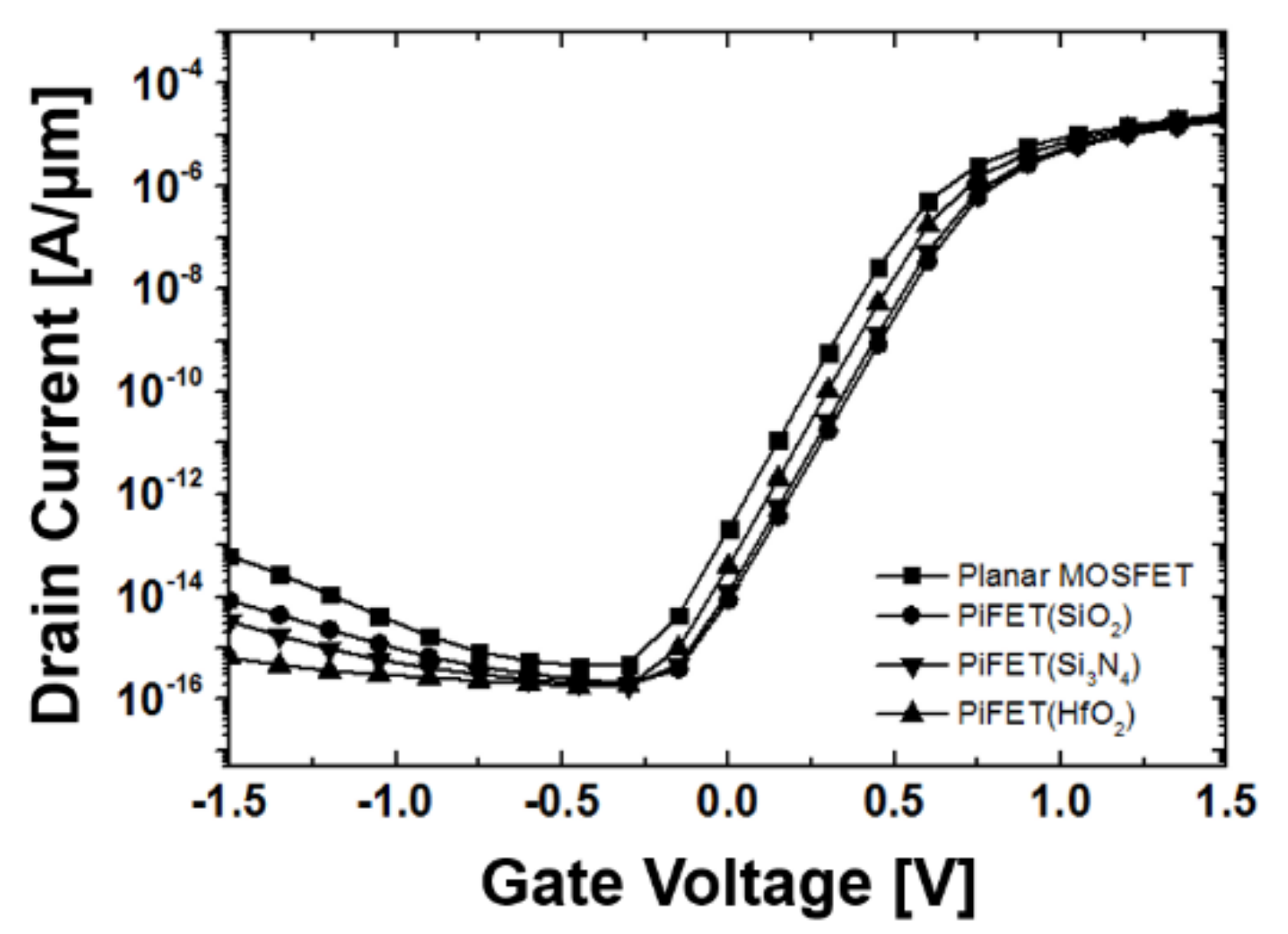

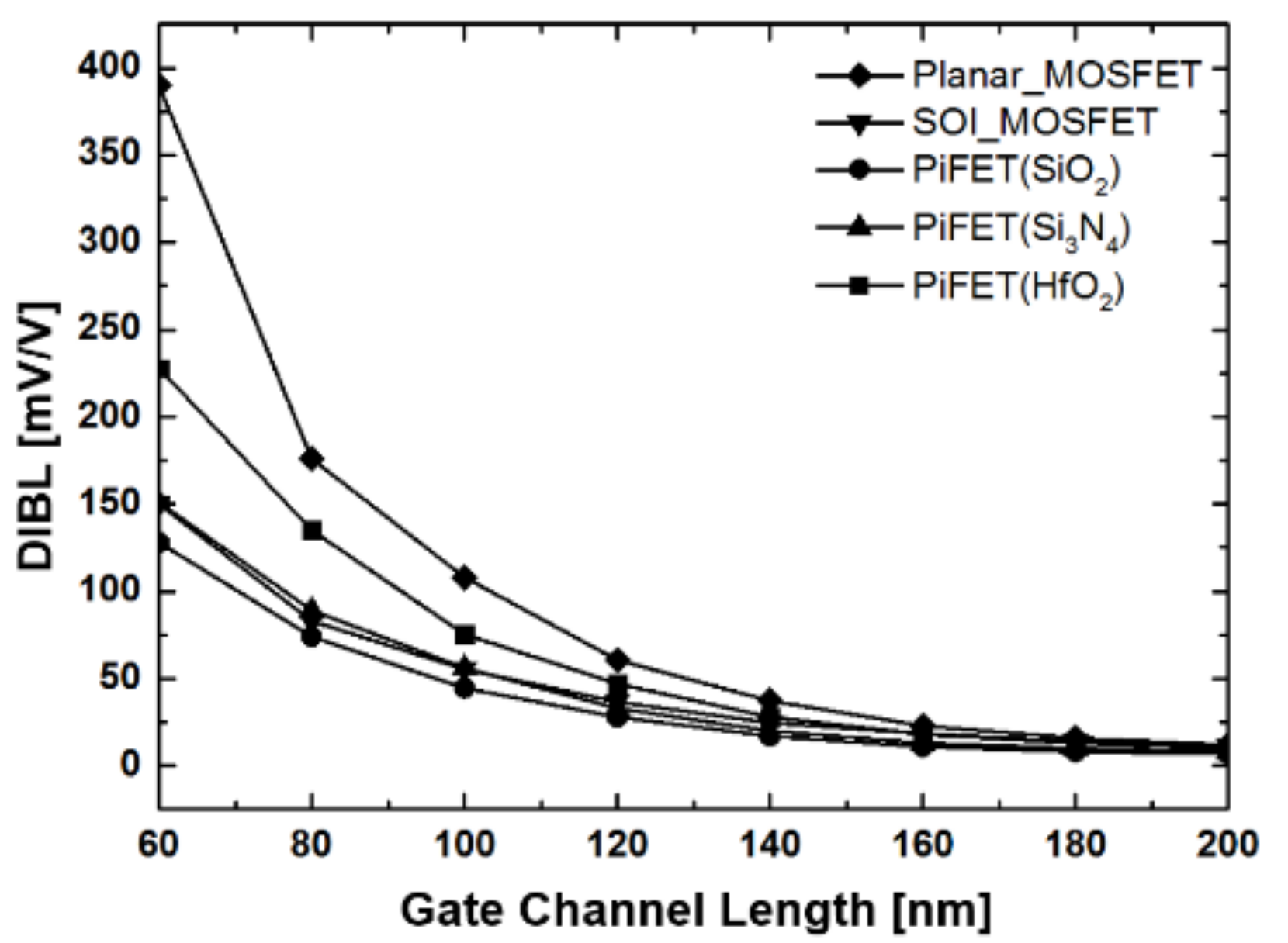

3.2. Various Dielectric Constants

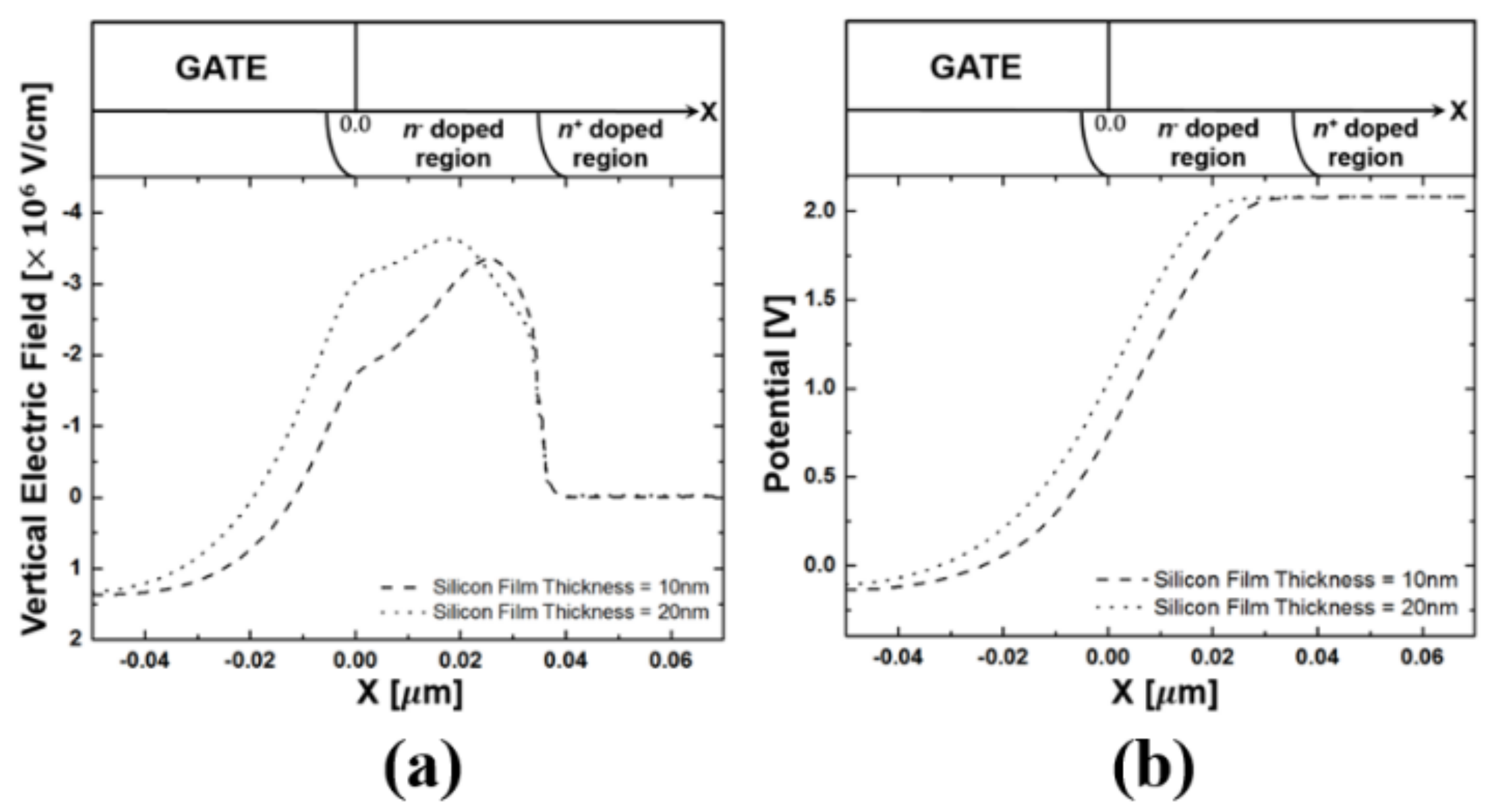

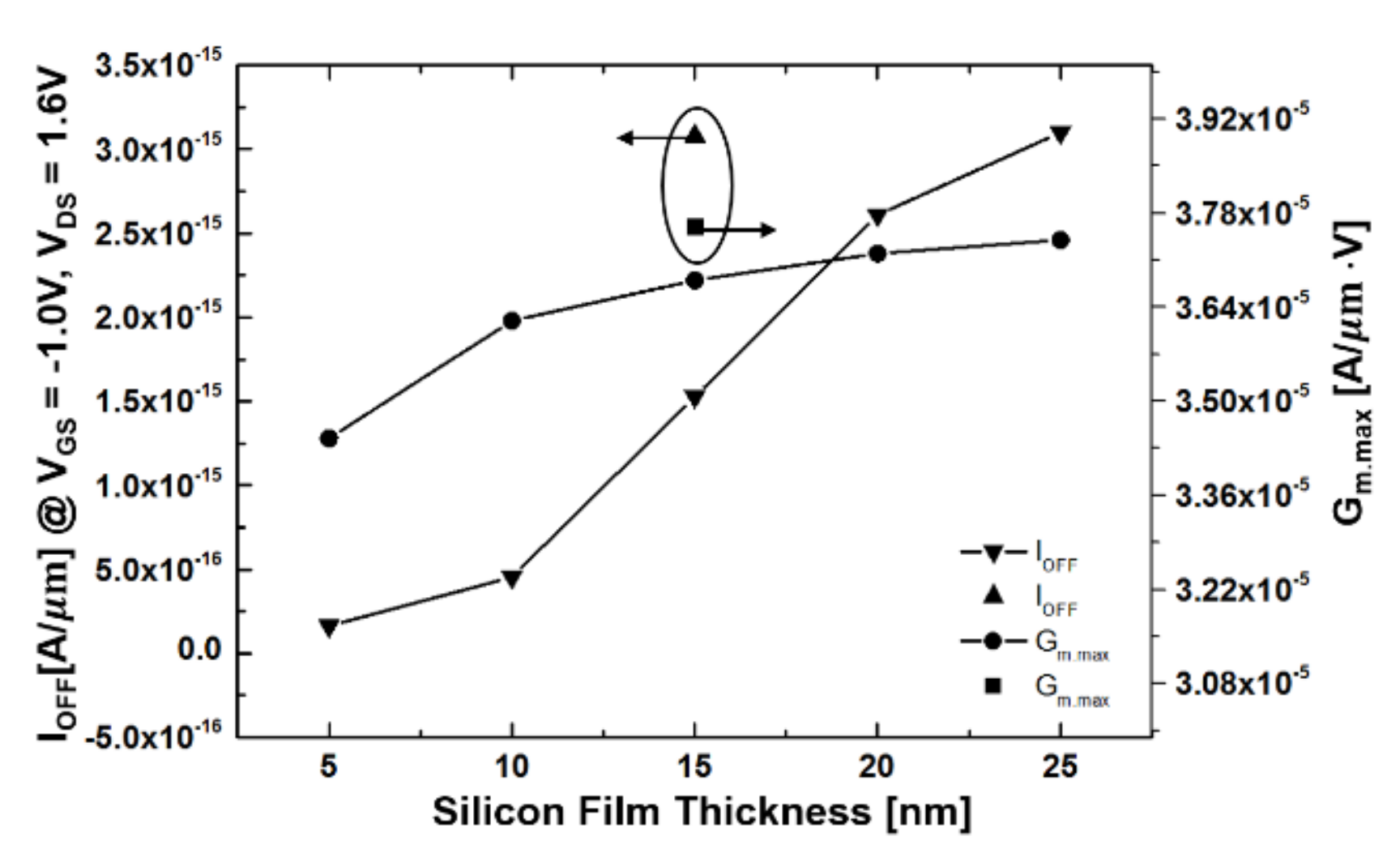

3.3. Silicon Film Thickness

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Chang, L.; Choi, Y.-K.; Ha, D.; Ranade, P.; Xiong, S.; Bokor, J.; Hu, C.; King, T.-J. Extremely scaled silicon nano-CMOS device. Proc. IEEE 2003, 91, 1860–1873. [Google Scholar] [CrossRef]

- Veeraraghavan, S.; Fossum, J.G. Short-Channel Effects in SO1 MOSFET’s. IEEE Trans. Electron Devices 1989, 36, 522–528. [Google Scholar] [CrossRef]

- Risho, K. Buried Layer Engineering to Reduce the Drain-Induced Barrier Lowering of Sub-0.05 µm SOI-MOSFET. Jpn. J. Appl. Phys. 1999, 38, 2294–2299. [Google Scholar]

- Wang, J.; Kistler, N.; Woo, J.; Viswanathan, C.R. Mobility-Field Behavior of Fully Depleted SO1 MOSFET’s. IEEE Electron Device Lett. 1994, 15, 117–119. [Google Scholar] [CrossRef]

- Veeraraghavan, S.; Fossum, J.G. A Physical Short-channel Model for the Thin-Film SOI MOSFET Applicable to Device and Circuit CAD. IEEE Trans. Electron Devices 1988, 35, 1866–1874. [Google Scholar] [CrossRef]

- Koh, R.; Kato, H.; Matsumoto, H. Capacitance Network Model of the Short Channel Effect for 0.1 µm Fully Depleted SOI MOSFET. Jpn. J. Appl. Phys. 1996, 35, 996–1000. [Google Scholar] [CrossRef]

- Kumar, M.J.; Chaudhry, A. Two-Dimensional Analytical Modeling of Fully Depleted DMG SOI MOSFET and Evidence for Diminished SCEs. IEEE Trans. Electron Devices 2004, 51, 569–574. [Google Scholar] [CrossRef] [Green Version]

- Chaudhry, A.; Kumar, M.J. Investigation of the Novel Attributes of a Fully Depleted Dual-Material Gate SOI MOSFET. IEEE Trans. Electron Devices 2004, 51, 1463–1467. [Google Scholar] [CrossRef]

- Joachim, H.O.; Yamaguchi, Y.; Ishikawa, K.; Inoue, Y.; Nishimura, T. Simulation and Two-Dimensional Analytical Modeling of Subthreshold Slope in Ultrathin-Film SOI MOSFET’s Down to 0.1 um Gate Length. IEEE Trans. Electron Devices 1993, 40, 1812–1817. [Google Scholar] [CrossRef]

- Lee, M.J.; Cho, J.H.; Lee, S.D.; Ahn, J.H.; Kim, J.W.; Park, S.W.; Park, Y.J.; Min, H.S. Partial SOI Type Isolation for Improvement of DRAM Cell Transistor Characteristics. IEEE Trans. Electron Devices 2005, 26, 332–334. [Google Scholar]

- Kim, Y.K.; Lee, J.S.; Kim, G.; Park, T.; Kim, H.J.; Cho, Y.P.; Park, Y.J.; Lee, M.J. The optimized Partial Insulator Isolation MOSFET (PiFET). J. Semicond. Technol. Sci. 2017, 17, 729–732. [Google Scholar] [CrossRef]

- Jin, S.; Lee, M.J.; Yi, J.H.; Choi, J.H.; Kang, D.G.; Chung, I.Y.; Park, Y.J.; Min, H.S. New Direct Evaluation Method to Obtain the Data Retention Time Distribution of DRAM. IEEE Trans. Electron Devices 1992, 39, 2244–2350. [Google Scholar] [CrossRef]

- Hurkx, G.A.M.; Klaassen, D.B.M.; Knuvers, M.P.G. A New Recombination Model for Device Simulation Including Tunneling. IEEE Trans. Electron Devices 2006, 53, 331–338. [Google Scholar] [CrossRef]

- Jang, E.; Shin, S.; Jung, J.W.; Kim, K.R. Gate induced drain leakage reduction with analysis of gate fringing field effect on high-κ/metal gate CMOS technology. Jpn. J. Appl. Phys. 2015, 54, 06FG10. [Google Scholar] [CrossRef]

- Cheng, B.; Cao, M.; Rao, R.; Inani, A.; Voorde, P.V.; Greene, W.M.; Stork, J.M.; Yu, Z.; Zeitzoff, P.M.; Woo, J.C. The Impact of High-k Gate Dielectrics and Metal Gate Electrodes on Sub-100 nm MOSFET’s. IEEE Trans. Electron Devices 1999, 46, 1537–1544. [Google Scholar] [CrossRef]

- Ernst, T.; Tinella, C.; Raynaud, C.; Cristoloveanu, S. Fringing fields in sub-0.1 μm fully depleted SOI MOSFETs: Optimization of the device architecture. Solid-State Electron. 2002, 46, 373–378. [Google Scholar] [CrossRef]

- Mizuno, T.; Kobori, T.; Saitoh, Y.; Sawada, S.; Tanaka, T. Gate-Fringing Field Effects on High Performance in High Dielectric LDD Spacer MOSFET’s. IEEE Trans. Electron Devices 1992, 39, 982–989. [Google Scholar] [CrossRef]

- Feng, W.S.; Chan, T.Y.; Hu, C. MOSFET Drain Breakdown Voltage. IEEE Trans. Electron Devices 1986, 7, 572–574. [Google Scholar]

- Chen, J.; Chan, T.Y.; Chen, I.C.; Ko, P.K.; Hu, C. Subbreakdown Drain Leakage Current in MOSFET. IEEE Trans. Electron Devices 1987, 8, 449–450. [Google Scholar] [CrossRef]

- Chen, J.; Assaderaghi, F.; Ko, P.K.; Hu, C. The Enhancement of Gate-Induced-Drain-Leakage (GIDL) Current in Short-Channel SO1 MOSFET and its Application in Measuring Lateral Bipolar Current Gain β. IEEE Trans. Electron Devices 1992, 13, 515–517. [Google Scholar]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, Y.K.; Lee, J.S.; Kim, G.; Park, T.; Kim, H.; Cho, Y.P.; Park, Y.J.; Lee, M.J. Simulation Analysis in Sub-0.1 μm for Partial Isolation Field-Effect Transistors. Electronics 2018, 7, 227. https://doi.org/10.3390/electronics7100227

Kim YK, Lee JS, Kim G, Park T, Kim H, Cho YP, Park YJ, Lee MJ. Simulation Analysis in Sub-0.1 μm for Partial Isolation Field-Effect Transistors. Electronics. 2018; 7(10):227. https://doi.org/10.3390/electronics7100227

Chicago/Turabian StyleKim, Young Kwon, Jin Sung Lee, Geon Kim, Taesik Park, HuiJung Kim, Young Pyo Cho, Young June Park, and Myoung Jin Lee. 2018. "Simulation Analysis in Sub-0.1 μm for Partial Isolation Field-Effect Transistors" Electronics 7, no. 10: 227. https://doi.org/10.3390/electronics7100227

APA StyleKim, Y. K., Lee, J. S., Kim, G., Park, T., Kim, H., Cho, Y. P., Park, Y. J., & Lee, M. J. (2018). Simulation Analysis in Sub-0.1 μm for Partial Isolation Field-Effect Transistors. Electronics, 7(10), 227. https://doi.org/10.3390/electronics7100227