Electrostatic-Discharge-Immunity Impacts in 300 V nLDMOS by Comprehensive Drift-Region Engineering

Abstract

:1. Introduction

2. Layout of UHV Circular nLDMOS Devices under Test (DUTs)

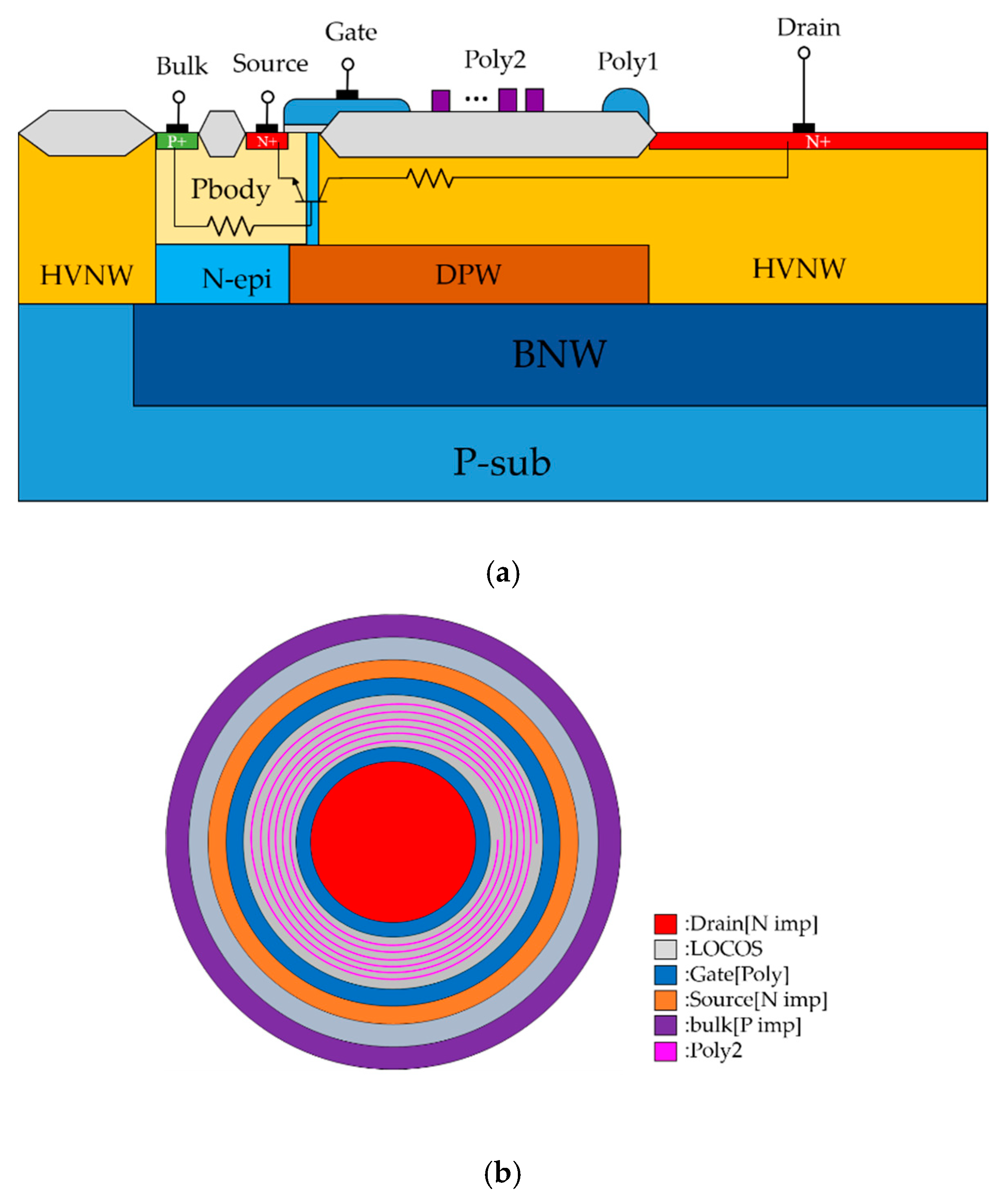

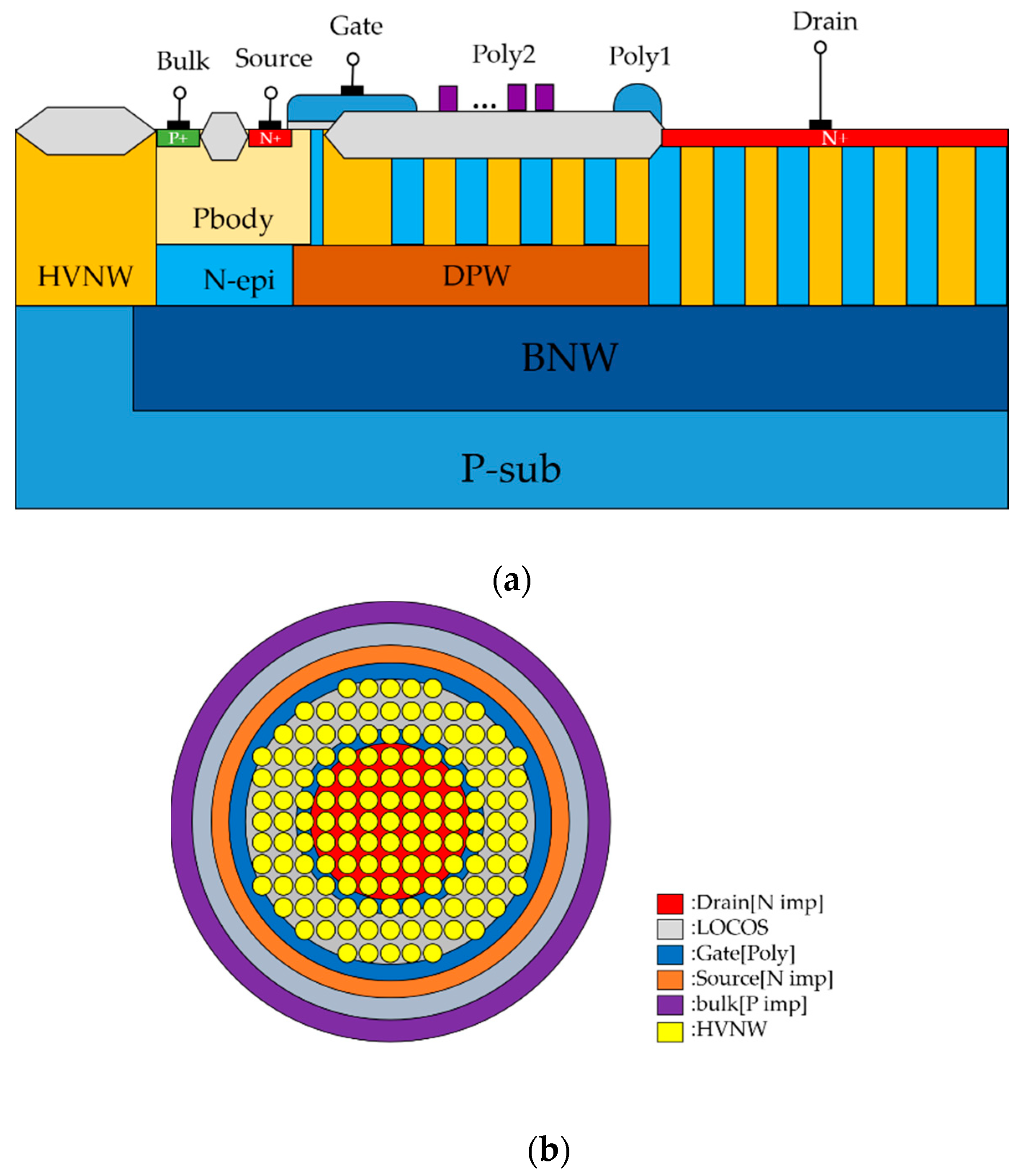

2.1. UHV Circular nLDMOS Reference Group

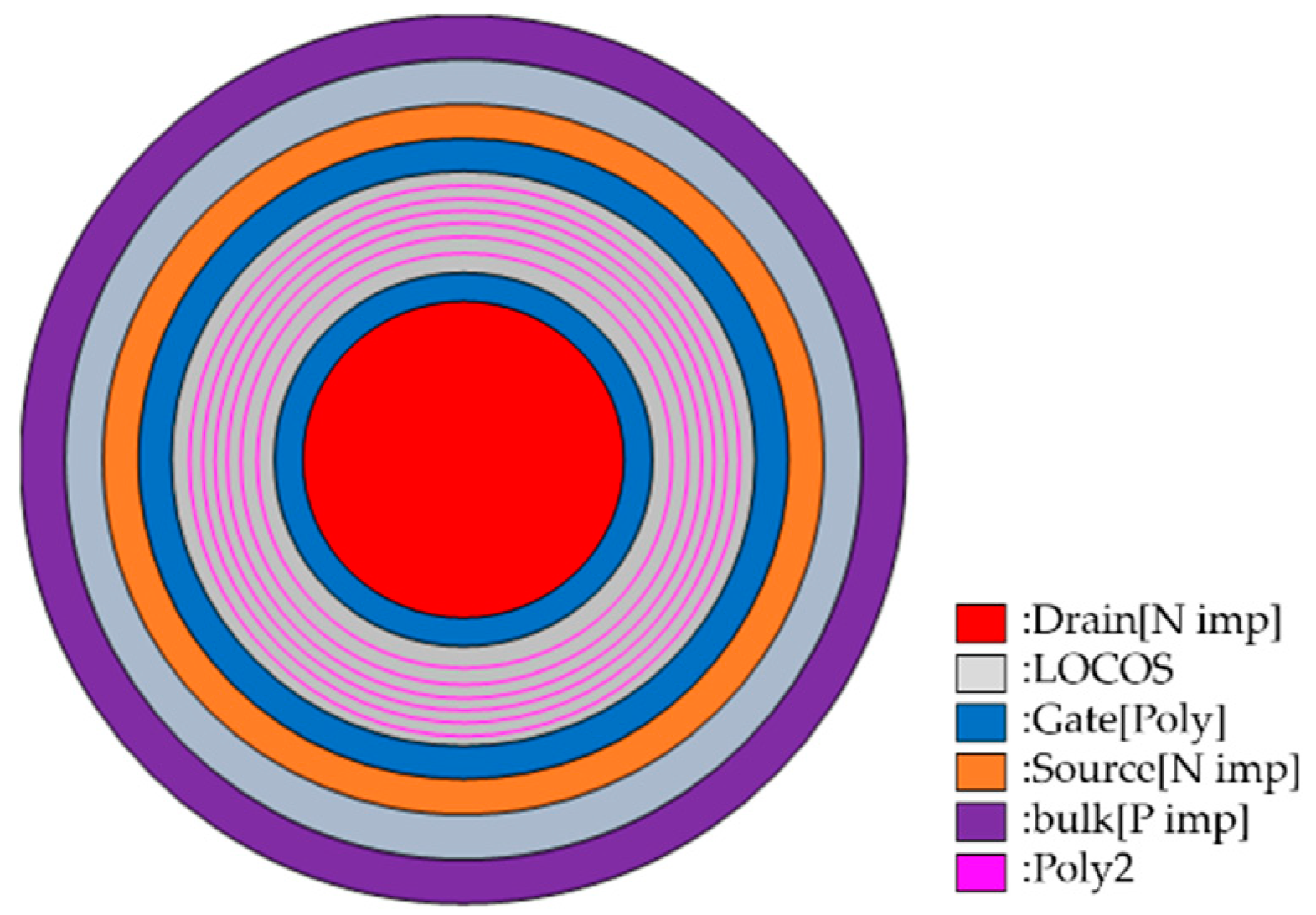

2.2. UHV Circular nLDMOS—Polysilicon-Stripe Modulation above the Drift Region

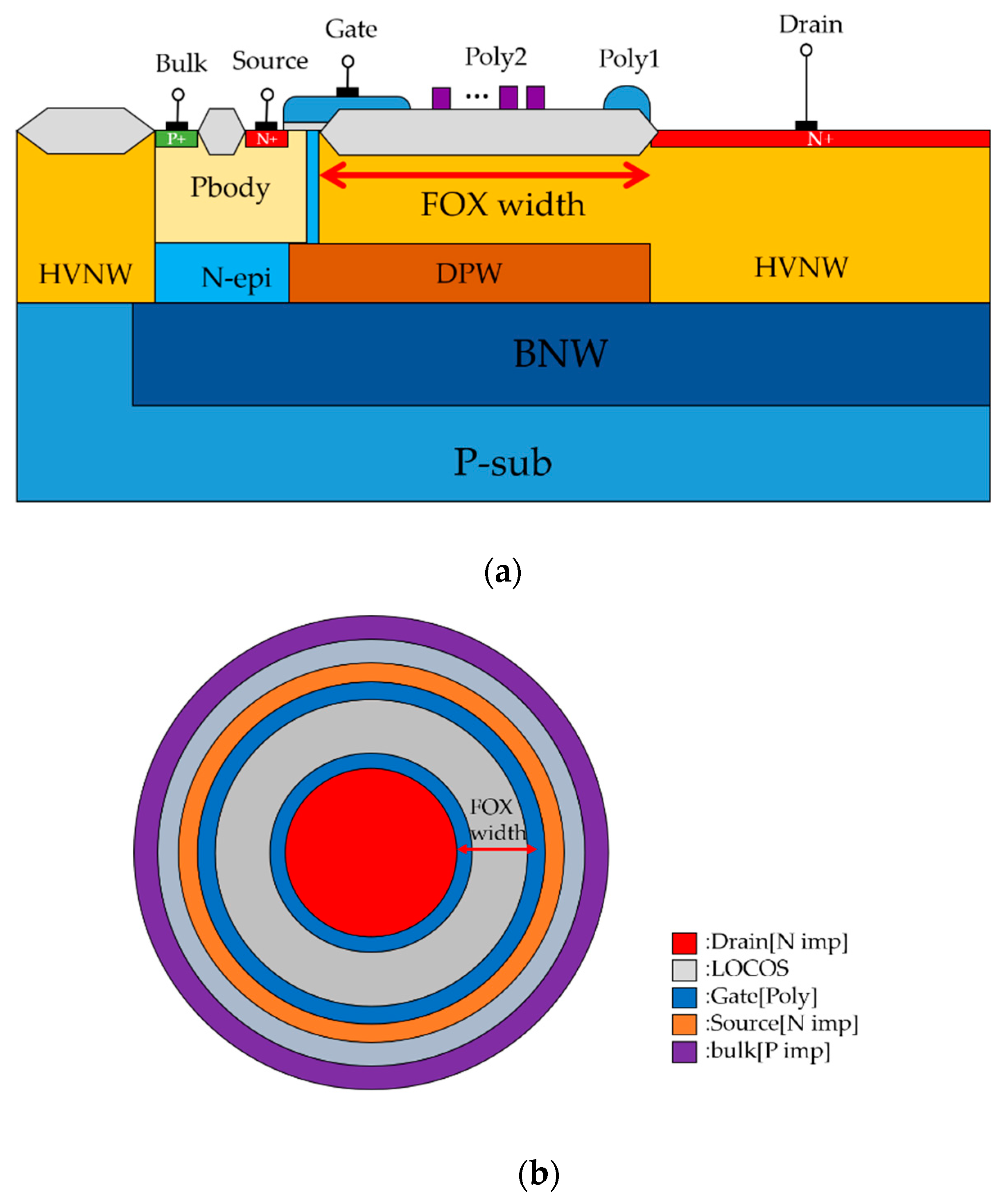

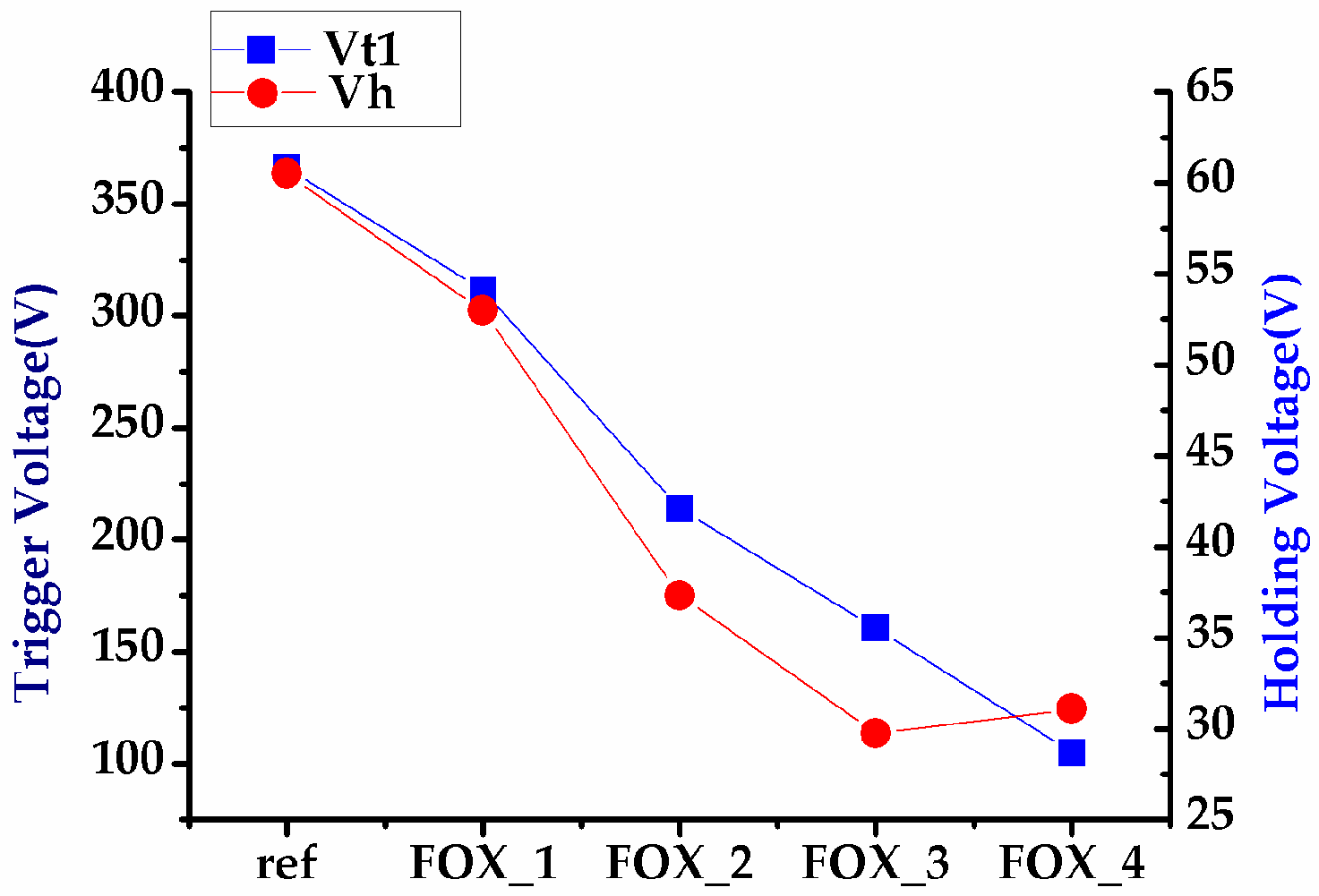

2.3. UHV Circular nLDMOS—Field-Oxide Width Modulation in the Drift Region

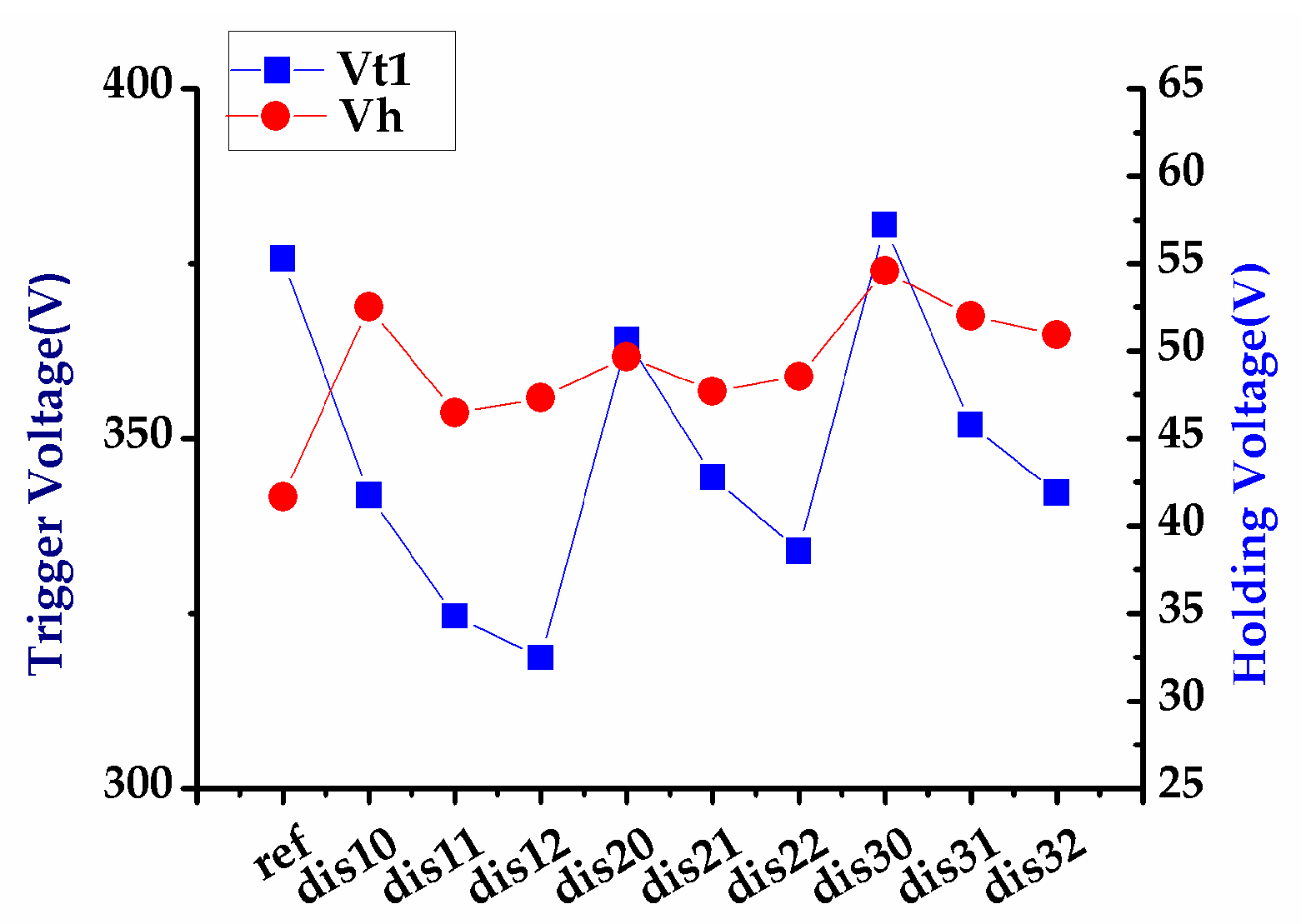

2.4. UHV Circular nLDMOS—Discrete HV N-Well (HVNW) Layer Modulation in the Drift Region

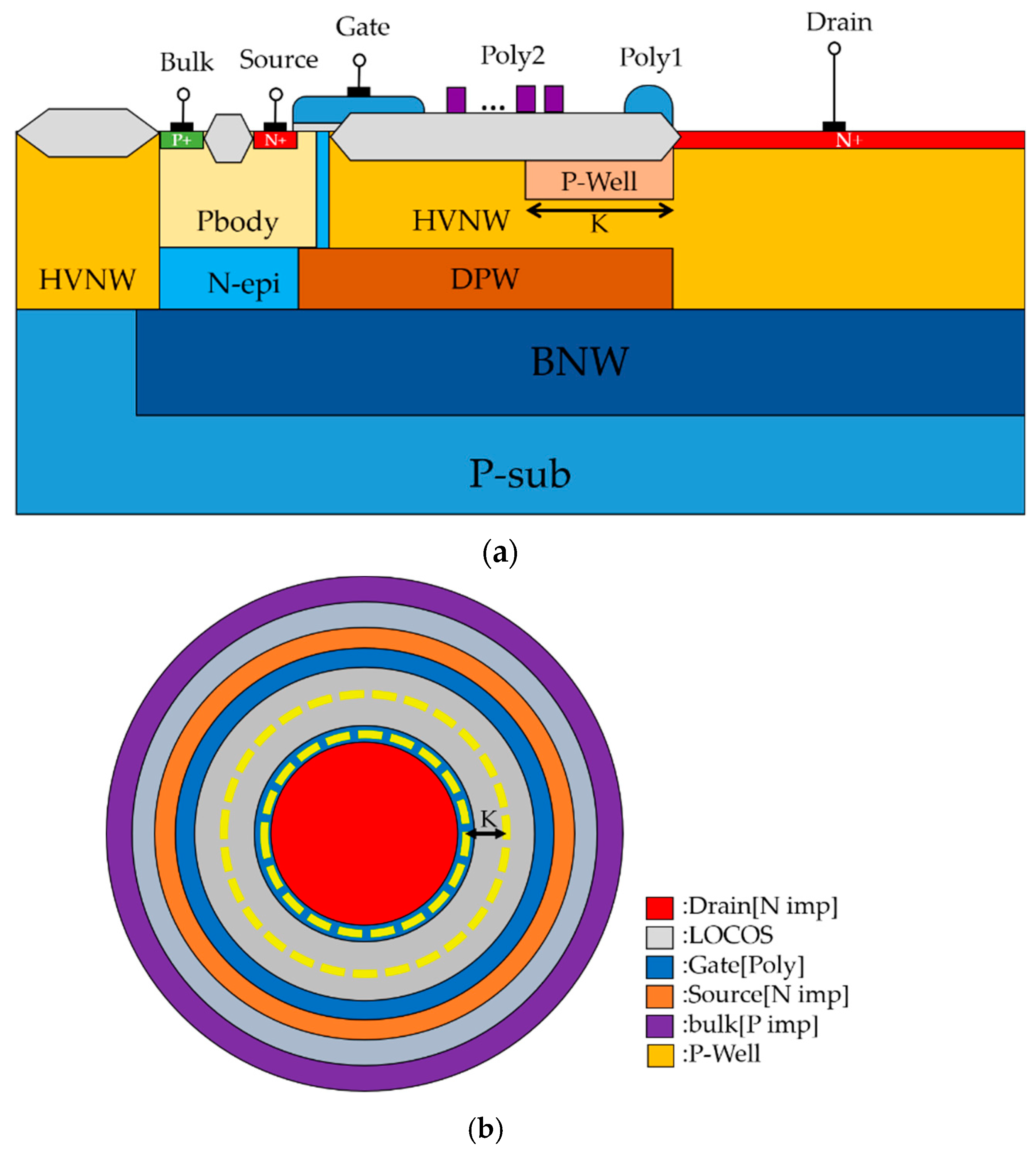

2.5. UHV Circular nLDMOS—Embedded P-Well Length Modulation in the Drift Region

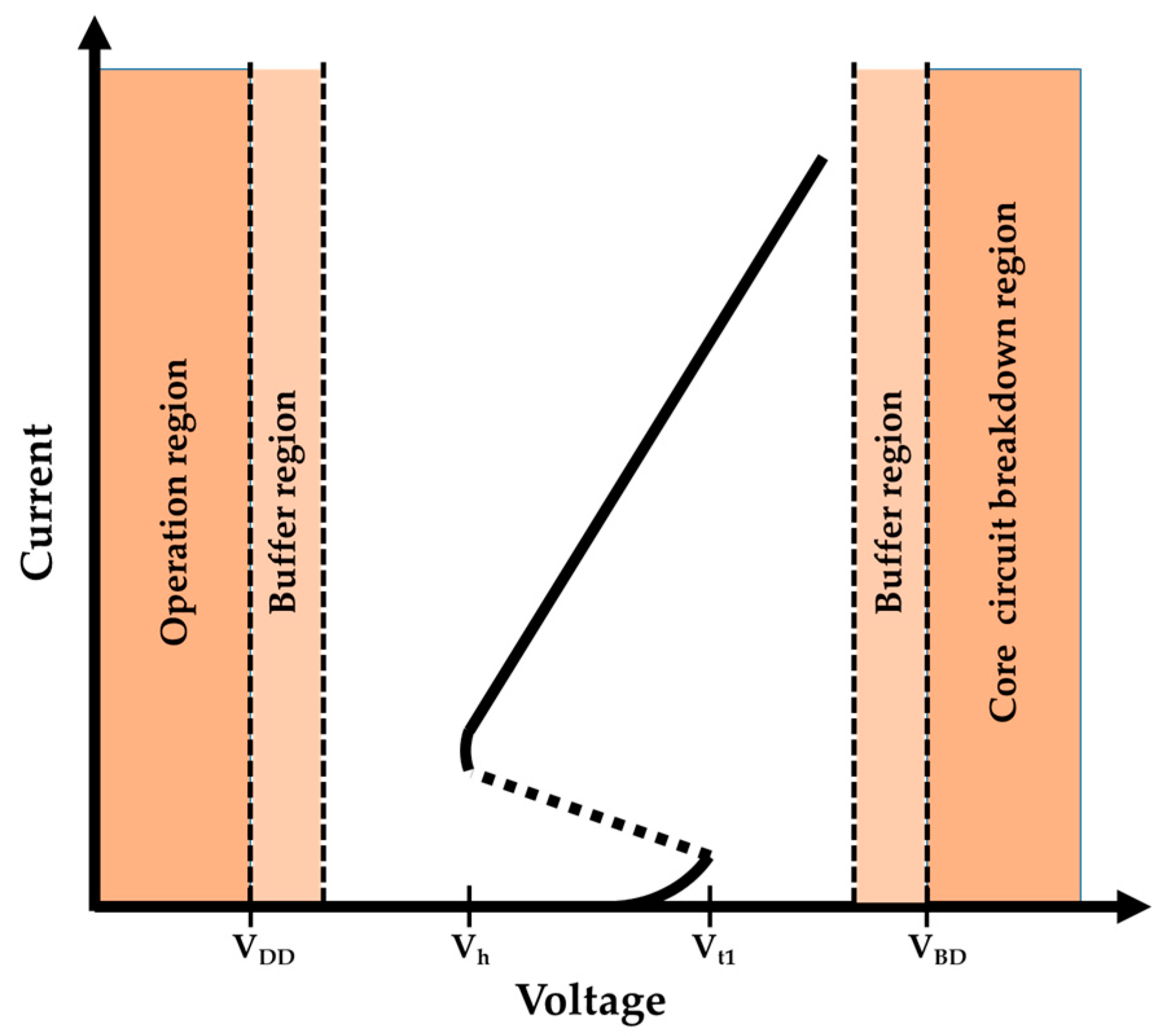

3. Testing Machine

4. Test Results and Discussion

4.1. UHV Circular nLDMOS—Polysilicon-Stripe Modulation above the Drift Region

4.2. UHV Circular nLDMOS—Field-Oxide Width Modulation in the Drift Region

4.3. UHV Circular nLDMOS—Discrete HVNW Layer Modulation in the Drift Region

4.4. UHV Circular nLDMOS—Embedded P-Well Length Modulation in the Drift Region

5. TCAD Simulation

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Qiao, M.; Zhang, K.; Zhou, X.; Zou, J.; Zhang, B.; Li, Z. 250 V Thin-Layer SOI Technology with Field pLDMOS for High-Voltage Switching IC. IEEE Trans. Electron Devices 2015, 62, 1970–1976. [Google Scholar] [CrossRef]

- Chen, Y.; Chang, C.; Yang, P. A Novel Primary-Side Controlled Universal-Input AC–DC LED Driver Based on a Source-Driving Control Scheme. IEEE Trans. Power Electron. 2015, 30, 4327–4335. [Google Scholar] [CrossRef]

- Chen, Z.; Salman, A.; Mathur, G.; Boselli, G. Design and Optimization on ESD Self-Protection Schemes for 700V LDMOS in High Voltage Power IC. In Proceedings of the in 37th Electrical Overstress/Electrostatic Discharge Symposium, Reno, NV, USA, 27 September–2 October 2015. [Google Scholar]

- Cong, L.; Lee, H. A 110-250V 2MHz Isolated DC-DC Converter with Integrated High-Speed Synchronous Three-Level Gate Drive. In Proceedings of the IEEE Energy Conversion Congress and Exposition, Montreal, QC, Canada, 20–24 September 2015; pp. 1479–1484. [Google Scholar]

- Dai, S.; Knepper, R.; Horenstein, M. A 300 LDMOS analog-multiplexed drive for MEMS devices. IEEE Trans. Circuits Syst. I. Reg. Pap. 2015, 62, 2806–2815. [Google Scholar] [CrossRef]

- Yi, B.; Chen, X. A 300-V Ultra-Low-Specific On-Resistance High-Side p-LDMOS With Auto-Biased n-LDMOS for SPIC. IEEE Trans. Power Electron. 2017, 32, 551–560. [Google Scholar] [CrossRef]

- Chang, C.; Jiang, T.; Yang, P.; Xu, Y.; Xu, C.; Chen, Y. Adaptive line voltage compensation scheme for a source-driving controlled AC–DC LED driver. IET Circuits Devices Syst. 2017, 11, 21–28. [Google Scholar] [CrossRef]

- Kim, S.; LaFonteese, D.; Zhu, D.; Sridhar, D.S.; Pendharkar, S.; Endoh, H.; Boku, K. A new ESD self-protection structure for 700V high side gate drive IC. In Proceedings of the 29th International Symposium on Power Semiconductor Devices and IC’s, Sapporo, Japan, 28 May–1 June 2017; pp. 467–470. [Google Scholar]

- Ker, M.; Lin, C.; Wu, Y.; Wang, W. ESD Protection Design with Low-Leakage Consideration for Silicon Chips of loT Applications. In Proceedings of the 7th Annual IEEE International Conference on Cyber Technology in Automation, Control and Intelligent Systems, Honolulu, HI, USA, 31 July–4 August 2017; pp. 1496–1499. [Google Scholar]

- Wu, J.; Lyu, X.; Kong, M.; Yi, B.; Chen, X. A novel level-shifter integrated on the edge termination region of the high voltage device. In Proceedings of the TENCON 2017 IEEE Region 10 Conference, Penang, Malaysia, 5–8 November 2017; pp. 2683–2686. [Google Scholar]

- Li, W.; Makuuchi, M.; Chujo, N. Design of High-Voltage and High-Speed Driver. In Proceedings of the IEEE 12th International Conference on Power Electronics and Drive Systems, Honolulu, HI, USA, 12–15 December 2017; pp. 448–452. [Google Scholar]

- Sun, W.; Ye, R.; Liu, S.; Wei, J.; Su, W.; Lin, F.; Sun, G.; Lin, Z. Layout Arrangement Concern for Lateral DMOS With Large Geometric Array Used as Output Device. IEEE Trans. Device Mater. Reliab. 2017, 17, 450–457. [Google Scholar] [CrossRef]

- Yi, B.; Cheng, J.; Chen, X. A High-Voltage Quasi-p-LDMOS Using Electrons as Carriers in Drift Region Applied for SPIC. IEEE Trans. Power Electron. 2018, 33, 3363–3374. [Google Scholar] [CrossRef]

- Adila, A.; Husam, A.; Husi, G. Towards the Self-Powered Internet of Things (IoT) by Energy Harvesting: Trends and Technologies for Green IoT. In Proceedings of the 2nd International Symposium on Small-scale Intelligent Manufacturing Systems, Cavan, Ireland, 16–18 April 2018. [Google Scholar]

- Wang, H.; Qiao, M.; Jin, F.; Yu, Y.; Yuan, Z.Y.; Miao, B.; Yang, W.; Wu, J.; Qian, W.; Deng, T.; et al. A 0.35 μm 600 V Ultra-Thin Epitaxial BCD Technology for High Voltage Gate Driver IC. In Proceedings of the 30th International Symposium on Power Semiconductor Devices and ICs, Chicago, IL, USA, 13–17 May 2018; pp. 311–314. [Google Scholar]

- Guo, S.; Chen, X. A Novel p-LDMOS Additionally Conducting Electrons by Control ICs. IEEE J. Electron Devices Soc. 2019, 7, 710–716. [Google Scholar] [CrossRef]

- Mohammadi, F. Operation and Analysis of Float Cum Boost Charger in High-Voltage Switchgear Backup System. In Proceedings of the 1st International Conference on Modern Approaches in Engineering Science (ICMAES), Tbilisi, Georgia, 21 November 2018. [Google Scholar]

- Ker, M. Whole-Chip ESD Protection Design with Efficient VDD-to-VSS ESD Clamp Circuits for Submicron CMOS VLSI. IEEE Trans. Electron Devices 1999, 46, 173–183. [Google Scholar]

- Ker, M.; Chang, H.; Wu, C. A gate-coupled PTLSCR/NTLSCR ESD protection circuit for deep-submicron low-voltage CMOS ICs. IEEE J. Solid-State Circuits 1997, 32, 38–51. [Google Scholar]

- Chen, T.; Ker, M. Investigation of the Gate-Driven Effect and Substrate-Triggered Effect on ESD Robustness of CMOS Devices. IEEE Trans. Device Mater. Reliab. 2001, 1, 190–203. [Google Scholar] [CrossRef]

- Wang, C.; Ker, M. ESD Protection Design with Lateral DMOS Transistor in 40-V BCD Technology. IEEE Trans. Electron Devices 2010, 57, 3395–3404. [Google Scholar] [CrossRef]

- Ker, M.; Hsu, K. Latchup-Free ESD Protection Design with Complementary Substrate-Triggered SCR Devices. IEEE J. Solid-State Circuits 2003, 38, 1380–1392. [Google Scholar]

- Ker, M.; Hsu, K. Overview of On-Chip Electrostatic Discharge Protection Design With SCR-Based Devices in CMOS Integrated Circuits. IEEE Trans. Device Mater. Reliab. 2005, 5, 235–249. [Google Scholar]

- Keppens, B.; Mergens, M.P.J.; Trinh, C.S.; Russ, C.C.; Camp, B.V.; Verhaege, K.G. ESD protection solutions for high voltage technologies. In Proceedings of the Electrical Overstress/Electrostatic Discharge Symposium, Grapevine, TX, USA, 19–23 September 2004; pp. 289–298. [Google Scholar]

- Ker, M.; Lin, K. The Impact of Low-Holding-Voltage Issue in High-Voltage CMOS Technology and the Design of Latchup-Free Power-Rail ESD Clamp Circuit for LCD Driver ICs. IEEE J. Solid-State Circuits 2005, 40, 1751–1759. [Google Scholar]

- Lin, C.; Wu, P.; Ker, M. Area-Efficient and Low-Leakage Diode String for On-Chip ESD Protection. IEEE Trans. Electron Devices 2016, 63, 531–536. [Google Scholar] [CrossRef]

- Jiang, L.; Fan, H.; He, C.; Zhang, B. A reduced surface current LDMOS with stronger ESD robustness. In Proceedings of the 11th IEEE International Conference on Solid-State and Integrated Circuit Technology, Xi’an, China, 29 October–1 November 2012. [Google Scholar]

- Wu, C.; Lee, J.; Lien, C. A Novel Drain Design for ESD Improvement of UHV-LDMOS. IEEE Trans. Electron Devices 2015, 62, 4135–4138. [Google Scholar] [CrossRef]

- Yang, F.; Chen, H.; Tian, X.; Bai, Y.; Zhu, Y. Investigation on Current Crowding Effect in IGBTs. IEEE Trans. Electron Devices 2018, 65, 636–640. [Google Scholar] [CrossRef]

- Parpia, Z.; Salama, C.A.T. Optimization of RESURF LDMOS Transistors: An Analytical Approach. IEEE Trans. Electron Devices 1990, 37, 789–796. [Google Scholar] [CrossRef]

- Yang, K.; Guo, Y.; Pan, D.; Zhang, J.; Li, M.; Tong, Y.; He, L.; Yao, J. A Novel Variation of Lateral Doping Technique in SOI LDMOS With Circular Layout. IEEE Trans. Electron Devices 2018, 65, 1447–1452. [Google Scholar] [CrossRef]

- Pjenčák, J.; Agam, M.; Šeliga, L.; Yao, T.; Suwhanov, A. Novel Approach for NLDMOS Performance Enhancement by Critical Electric Field Engineering. In Proceedings of the 30th International Symposium on Power Semiconductor Devices & ICs, Chicago, IL, USA, 13–17 May 2018; pp. 307–310. [Google Scholar]

- Atlas User’s Manual; Silvaco Group Inc.: Santa Clara, CA, USA, 2018.

| Samples Name | Field-Oxide Width (μm) |

|---|---|

| Ref. | 29 |

| FOX_1 | 23.2 |

| FOX_2 | 17.4 |

| FOX_3 | 11.6 |

| FOX_4 | 5.8 |

| Size | 1 μm | 2 μm | 3 μm | |

|---|---|---|---|---|

| Space | ||||

| 1.34 μm | dis10 | dis20 | dis30 | |

| 2.68 μm | dis11 | dis21 | dis31 | |

| 4.02 μm | dis12 | dis22 | dis32 | |

| Samples Name | P-Well Length (μm) |

|---|---|

| Ref. | 0 |

| PW_5 | 5 |

| PW_7 | 7 |

| PW_9 | 9 |

| PW_11 | 11 |

| Samples | Vt1(V) | Vh(V) | It2(A) | VBK(V) |

|---|---|---|---|---|

| Spiral type | 375.13 | 58.69 | 3.20 | 395.12 |

| Concentric circle type | 375.71 | 41.66 | 5.09 | 411.20 |

| Samples | Vt1(V) | Vh(V) | It2(A) | VBK(V) | |

|---|---|---|---|---|---|

| Ref. nLDMOS | 364.44 | 60.49 | 2.46 | 389.59 | |

| FOX width | FOX_1 | 311.40 | 52.97 | 3.65 | 269.85 |

| FOX_2 | 213.88 | 37.34 | 2.99 | 142.25 | |

| FOX_3 | 160.61 | 29.74 | 2.43 | 130.34 | |

| FOX_4 | 104.89 | 31.09 | 6.84 | 105.43 | |

| Samples | Vt1(V) | Vh(V) | It2(A) | VBK(V) | |

|---|---|---|---|---|---|

| Ref. nLDMOS | 375.71 | 41.66 | 5.09 | 411.20 | |

| HVNW discrete | dis 10 | 341.94 | 52.52 | 3.43 | 212.32 |

| dis 11 | 324.67 | 46.48 | 3.72 | 193.79 | |

| dis 12 | 318.69 | 47.31 | 4.15 | 190.29 | |

| dis 20 | 364.15 | 49.65 | 3.20 | 255.48 | |

| dis 21 | 344.48 | 47.72 | 4.17 | 215.27 | |

| dis 22 | 333.98 | 48.52 | 3.57 | 196.76 | |

| dis 30 | 380.50 | 54.60 | 2.22 | 289.29 | |

| dis 31 | 351.92 | 51.99 | 3.20 | 222.75 | |

| dis 32 | 342.27 | 50.95 | 4.12 | 197.62 | |

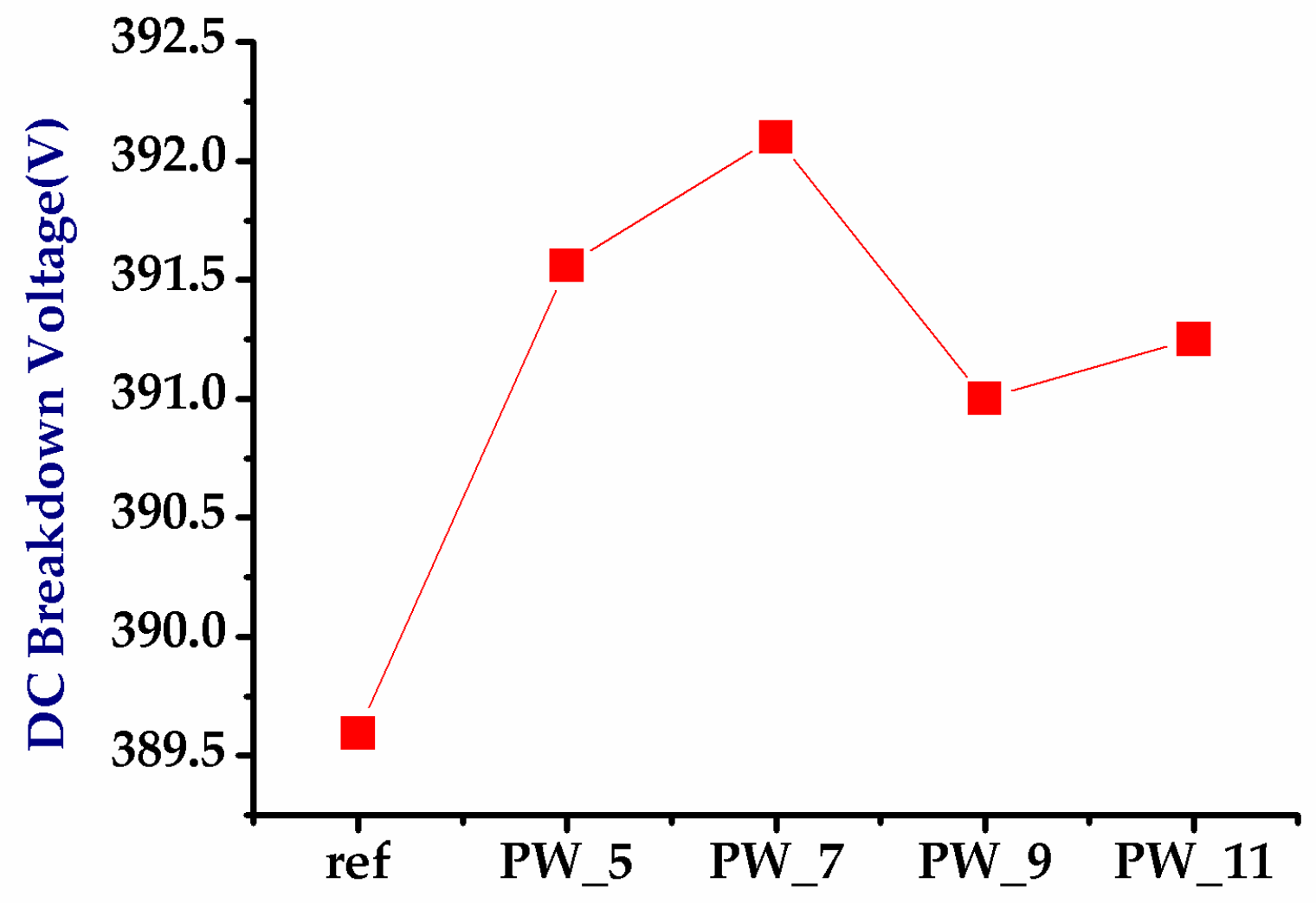

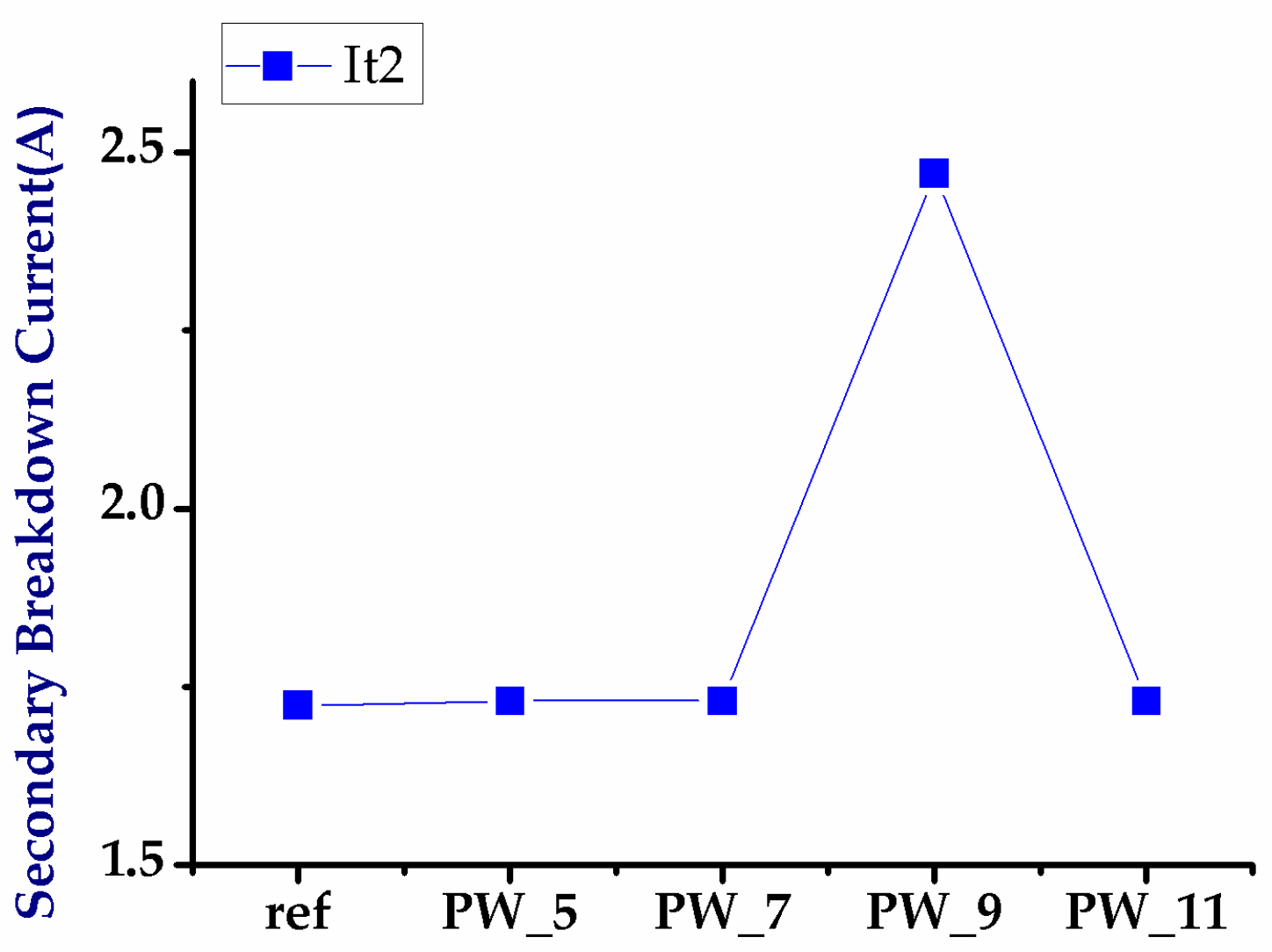

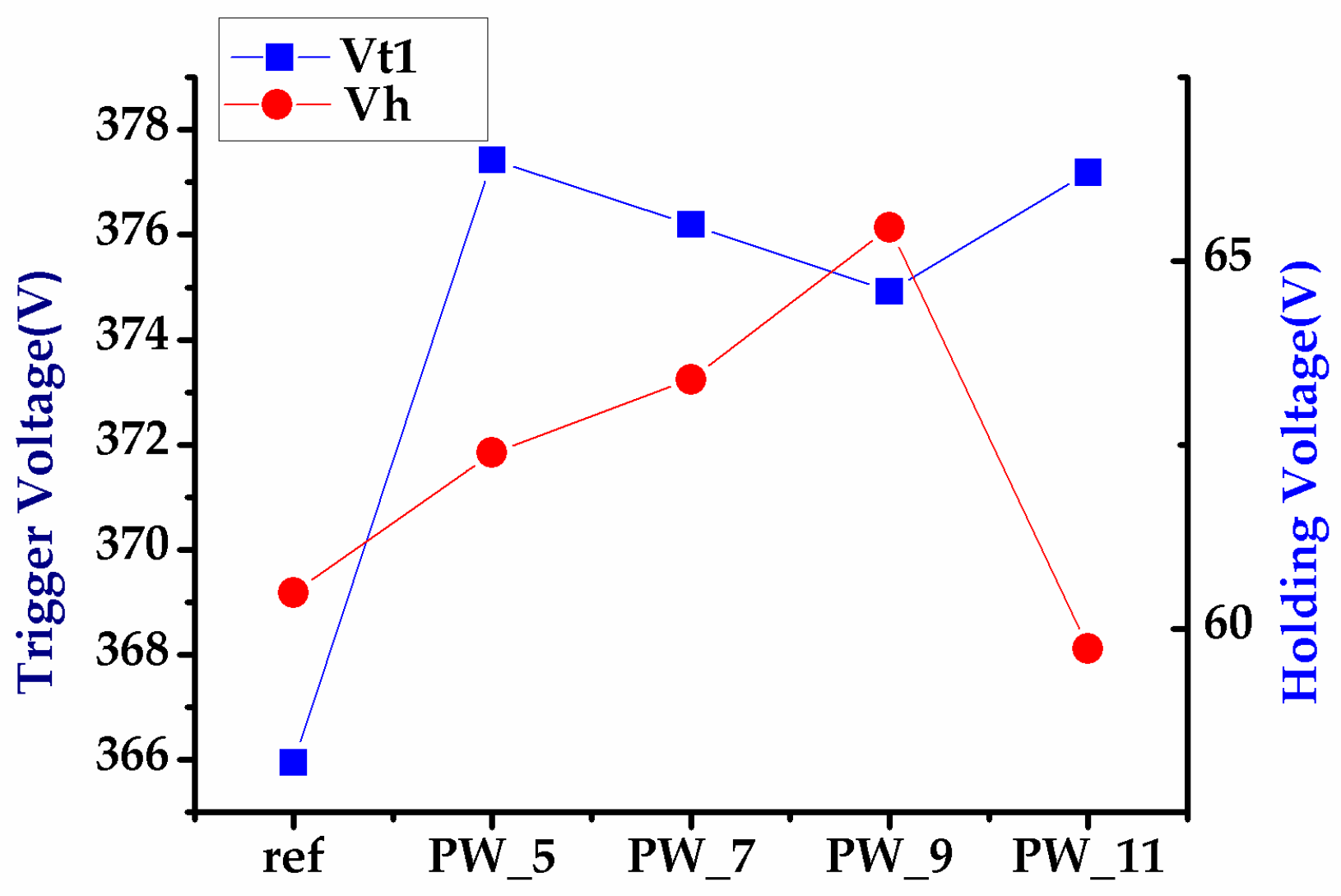

| Samples | Vt1(V) | Vh(V) | It2(A) | VBK(V) | |

|---|---|---|---|---|---|

| Ref. nLDMOS | 364.44 | 60.49 | 1.72 | 389.59 | |

| P-Well | PW_5 | 377.42 | 62.39 | 1.73 | 391.56 |

| PW_7 | 376.195 | 63.39 | 1.73 | 392.10 | |

| PW_9 | 374.92 | 65.46 | 2.47 | 391.00 | |

| PW_11 | 377.19 | 59.72 | 1.73 | 391.25 | |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lin, P.-L.; Chen, S.-L.; Fan, S.-K. Electrostatic-Discharge-Immunity Impacts in 300 V nLDMOS by Comprehensive Drift-Region Engineering. Electronics 2019, 8, 1469. https://doi.org/10.3390/electronics8121469

Lin P-L, Chen S-L, Fan S-K. Electrostatic-Discharge-Immunity Impacts in 300 V nLDMOS by Comprehensive Drift-Region Engineering. Electronics. 2019; 8(12):1469. https://doi.org/10.3390/electronics8121469

Chicago/Turabian StyleLin, Po-Lin, Shen-Li Chen, and Sheng-Kai Fan. 2019. "Electrostatic-Discharge-Immunity Impacts in 300 V nLDMOS by Comprehensive Drift-Region Engineering" Electronics 8, no. 12: 1469. https://doi.org/10.3390/electronics8121469