Single Event Transients in CMOS Ring Oscillators

Abstract

:1. Introduction

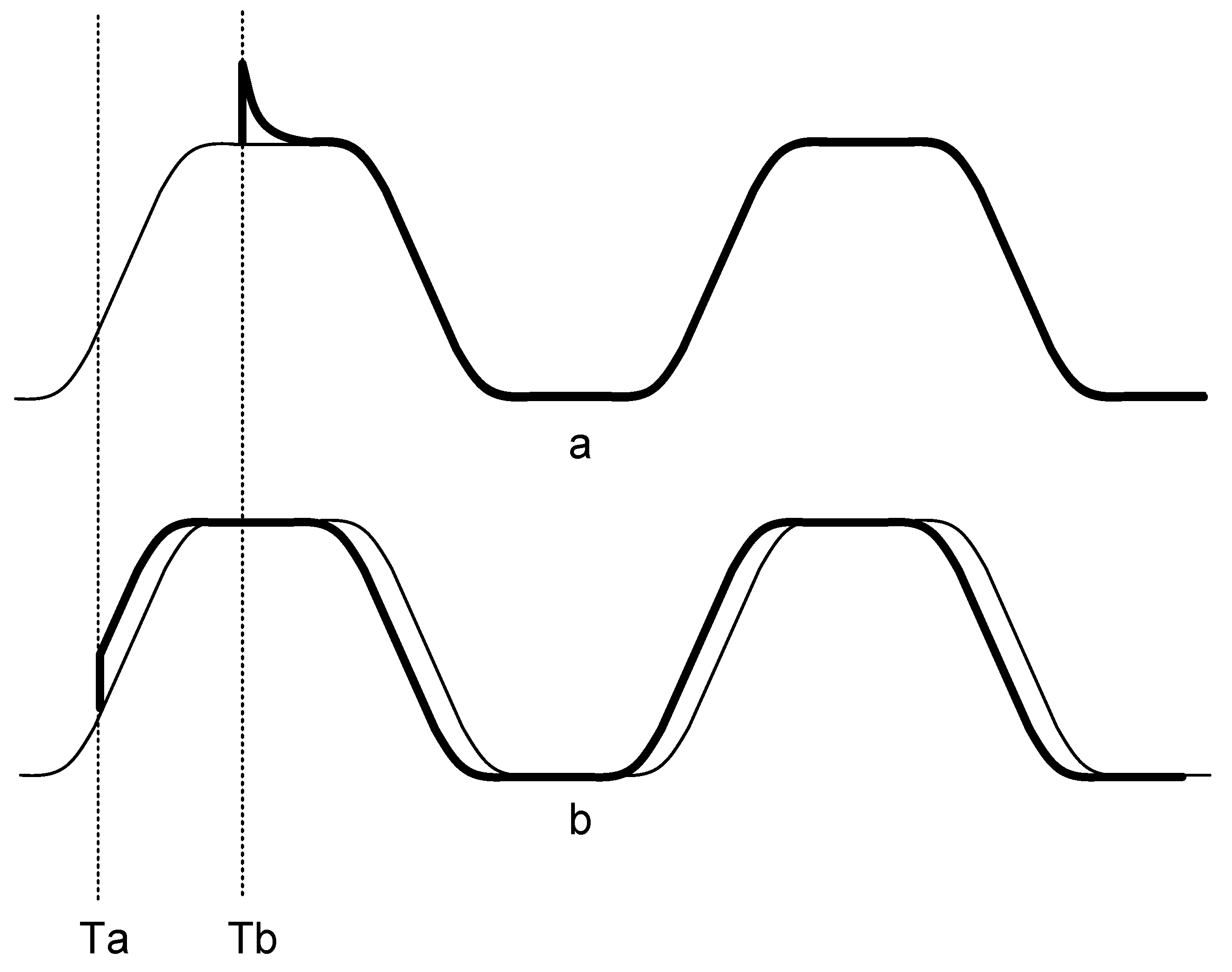

2. Time Dependent Effects in Oscillators

2.1. Calculation of the ISF

2.2. Particle Strikes as a Noise Source

3. Experiments

3.1. Experimental Circuit Description

3.2. Simulation Results

3.3. Experimental Measurement Setup

3.4. Experimental Results

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Young, I.A.; Greason, J.K.; Wong, K.L. A PLL clock generator with 5 to 110 MHz of lock range for microprocessors. IEEE J. Solid-State Circuits 1992, 27, 1599–1607. [Google Scholar] [CrossRef] [Green Version]

- Jung, D.; An, Y.; Ryu, K.; Park, J.; Jung, S. All-Digital Fast-Locking Delay-Locked Loop Using a Cyclic-Locking Loop for DRAM. IEEE Trans. Circuits Syst. II 2015, 62, 1023–1027. [Google Scholar] [CrossRef]

- Yang, S.; Yin, J.; Mak, P.; Martins, R.P. A 0.0056 mm2 -249-dB-FoM All-Digital MDLL Using a Block-Sharing Offset-Free Frequency-Tracking Loop and Dual Multiplexed-Ring VCOs. IEEE J. Solid-State Circuits 2019, 54, 88–98. [Google Scholar] [CrossRef]

- McNeill, J.A. Jitter in ring oscillators. IEEE J. Solid-State Circuits 1997, 32, 870–879. [Google Scholar] [CrossRef]

- Prinzie, J.; Christiansen, J.; Moreira, P.; Steyaert, M.; Leroux, P. Comparison of a 65 nm CMOS Ring- and LC-Oscillator Based PLL in Terms of TID and SEU Sensitivity. IEEE Trans. Nucl. Sci. 2017, 64, 245–252. [Google Scholar] [CrossRef]

- Yang, Z.; Chen, R.Y. High-Performance Low-Cost Dual 15 GHz/30 GHz CMOS LC Voltage-Controlled Oscillator. IEEE Microwave Wirel. Compon. Lett. 2016, 26, 714–716. [Google Scholar] [CrossRef]

- Lu, J.; Wang, N.; Chang, M.F. A single-LC-tank 5–10 GHz quadrature local oscillator for cognitive radio applications. In Proceedings of the 2011 IEEE Radio Frequency Integrated Circuits Symposium, Baltimore, MD, USA, 5–7 June 2011; pp. 1–4. [Google Scholar] [CrossRef]

- Buhr, S.; Kreißig, M.; Ellinger, F. Low Power 16 Phase Ring Oscillator and PLL for Use in sub-ns Time Synchronization over Ethernet. In Proceedings of the 2018 25th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Bordeaux, France, 9–12 December 2018; pp. 53–56. [Google Scholar] [CrossRef]

- Bravhar, K.; Martins, V.; Santos, L.; Codinachs, D.M. BRAVE NG-MEDIUM FPGA reconfiguration through SpaceWire: example use case and performance analysis. In Proceedings of the 2018 IEEE NASA/ESA Conference on Adaptive Hardware and Systems (AHS), Edinburgh, UK, 6–9 August 2018; pp. 135–141. [Google Scholar]

- Kuppambatti, J.; Ban, J.; Andeen, T.; Brown, R.; Carbone, R.; Kinget, P.; Brooijmans, G.; Sippach, W. A radiation-hard dual-channel 12-bit 40 MS/s ADC prototype for the ATLAS liquid argon calorimeter readout electronics upgrade at the CERN LHC. Nucl. Instrum. Methods Phys. Res. Sect. A 2017, 855, 38–46. [Google Scholar] [CrossRef] [Green Version]

- Hansen, M. CMS ECAL electronics developments for HL-LHC. J. Instrum. 2015, 10, C03028. [Google Scholar] [CrossRef]

- Prinzie, J.; Christiansen, J.; Moreira, P.; Steyaert, M.; Leroux, P. A 2.56-GHz SEU Radiation Hard LC-Tank VCO for High-Speed Communication Links in 65-nm CMOS Technology. IEEE Trans. Nucl. Sci. 2018, 65, 407–412. [Google Scholar] [CrossRef]

- Hajimiri, A.; Lee, T.H. A general theory of phase noise in electrical oscillators. IEEE J. Solid-State Circuits 1998, 33, 179–194. [Google Scholar] [CrossRef]

- Lee, T.H.; Hajimiri, A. Oscillator phase noise: A tutorial. IEEE J. Solid-State Circuits 2000, 35, 326–336. [Google Scholar] [CrossRef]

- De Smedt, V.; Gielen, G.; Dehaene, W. Temperature-And Supply Voltage-Independent Time References for Wireless Sensor Networks; Springer: Cham, Switzerland, 2015. [Google Scholar]

- Hajimiri, A.; Limotyrakis, S.; Lee, T.H. Jitter and phase noise in ring oscillators. IEEE J. Solid-State Circuits 1999, 34, 790–804. [Google Scholar] [CrossRef] [Green Version]

- Black, D.A.; Robinson, W.H.; Wilcox, I.Z.; Limbrick, D.B.; Black, J.D. Modeling of Single Event Transients With Dual Double-Exponential Current Sources: Implications for Logic Cell Characterization. IEEE Trans. Nucl. Sci. 2015, 62, 1540–1549. [Google Scholar] [CrossRef]

- Maneatis, J.G. Low-jitter process-independent DLL and PLL based on self-biased techniques. IEEE J. Solid-State Circuits 1996, 31, 1723–1732. [Google Scholar] [CrossRef]

- Prinzie, J.; Steyaert, M.; Leroux, P. Radiation Hardened CMOS Integrated Circuits for Time-Based Signal Processing; Springer: Cham, Switzerland, 2018. [Google Scholar]

- Kundert, K. Predicting the phase noise and jitter of PLL-based frequency synthesizers. In Phase-Locking in High-Performance Systems: From Devices to Architectures; John Wiley & Sons, Inc.: New York, NY, USA, 2003; pp. 46–69. [Google Scholar]

- Vanassche, P.; Gielen, G.; Gielen, G.; Gielen, G.; Sansen, W. On the difference between two widely publicized methods for analyzing oscillator phase behavior. In Proceedings of the 2002 IEEE/ACM International Conference on Computer-Aided Design, San Jose, CA, USA, 10–14 November 2002; pp. 229–233. [Google Scholar]

- Levantino, S.; Maffezzoni, P.; Pepe, F.; Bonfanti, A.; Samori, C.; Lacaita, A.L. Efficient Calculation of the Impulse Sensitivity Function in Oscillators. IEEE Trans. Circuits Syst. II 2012, 59, 628–632. [Google Scholar] [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Prinzie, J.; De Smedt, V. Single Event Transients in CMOS Ring Oscillators. Electronics 2019, 8, 618. https://doi.org/10.3390/electronics8060618

Prinzie J, De Smedt V. Single Event Transients in CMOS Ring Oscillators. Electronics. 2019; 8(6):618. https://doi.org/10.3390/electronics8060618

Chicago/Turabian StylePrinzie, Jeffrey, and Valentijn De Smedt. 2019. "Single Event Transients in CMOS Ring Oscillators" Electronics 8, no. 6: 618. https://doi.org/10.3390/electronics8060618