Optimization of the Cell Structure for Radiation-Hardened Power MOSFETs

Abstract

:1. Introduction

2. Design Considerations

2.1. Cell Structure

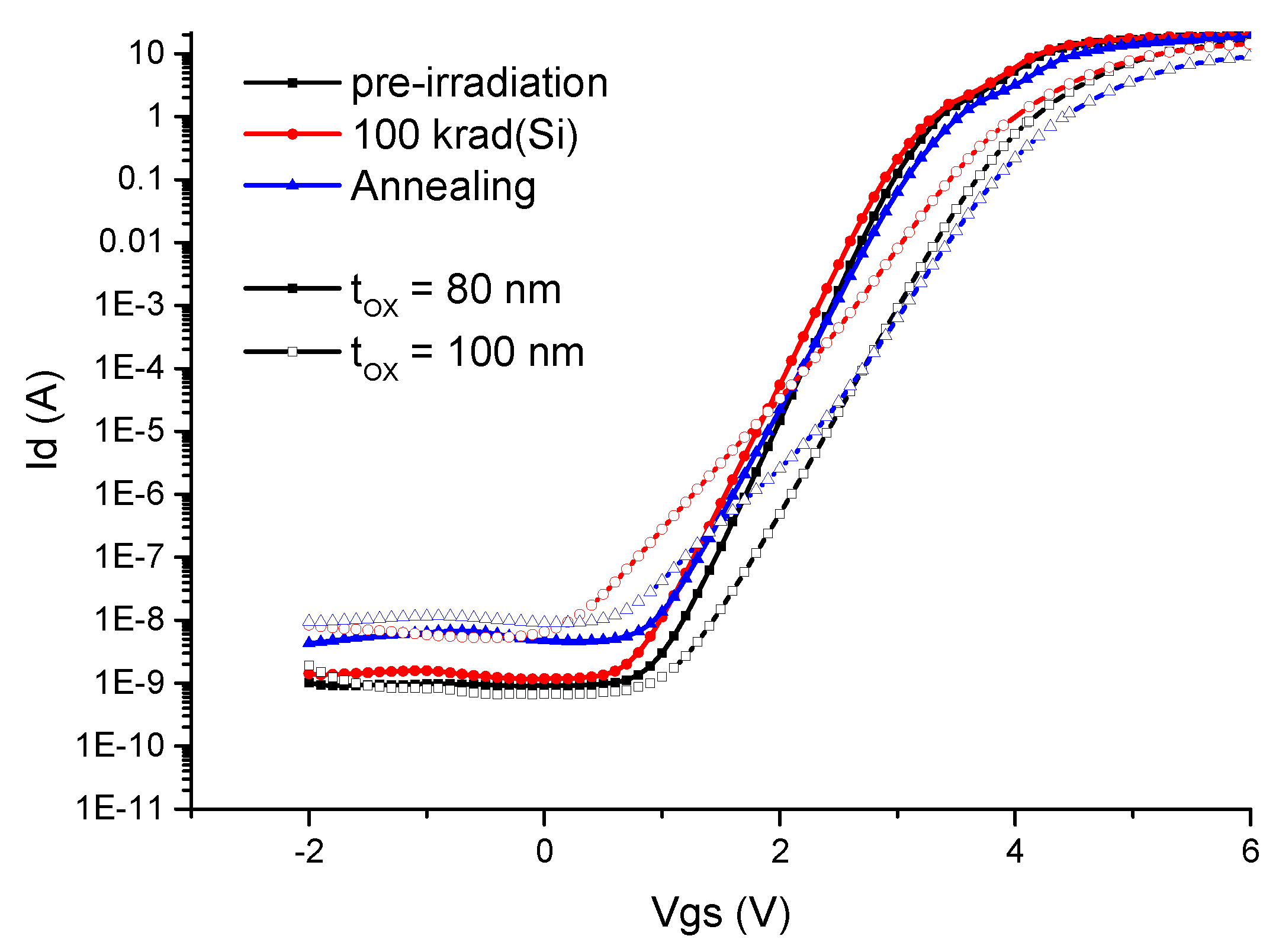

2.2. Oxide Thickness

2.3. JFET Region Width

2.4. P Body and P+ Well Doping

3. Results

4. Discussion

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Nomenclature

| Symbol | Description | Equation |

| ECRIT | Critical electric field of gate oxide that must withstand heavy-ion injection | (1) |

| VGS | Applied gate voltage | (1) |

| tOX | Gate oxide thickness | (1) |

| EBD | Intrinsic dielectric breakdown strength | (1) |

| Z | The atomic number of the injected heavy ions | (1) |

| tOX,min | The minimum gate oxide bounded by single event gate rupture (SEGR) effects | (2) |

| α | The coupled ratio of drain voltage | (2) |

| VDS | Applied drain voltage | (2) |

| ΔVot,it | Threshold shifts induced by oxide-charge or interface traps | (3) |

| COX | Gate capacitance | (3) |

| ρot,it | The charge distribution of radiation-induced oxide-trapped or interface-trapped charge | (3) |

| ΔQot | Radiation-induced charges in oxide | (4) |

| q | Electric charge | (4) |

| g0 | Electron–hole pair generation rate in SiO2 | (4) |

| D | The total dose level | (4) |

| Yh | Charge yield of holes | (4) |

| σh | Trapping cross section for holes captured by hole traps in oxide | (4) |

| εOX | The dielectric constant of SiO2 | (4) |

| ΔQit | Radiation-induced interface trap charges | (5) |

| Yp | Product of concentration of hydrogen-containing defects and cross section for proton release from these defects | (5) |

| σp | The cross section of protons captured by the traps at interface | (5) |

| tOX,max | The maximum gate oxide bounded by total ionizing dose (TID) effects | (6) |

| ΔVth,max | The maximum allowed threshold shift | (6) |

| RJFET,SP | Specific resistance contributed by the JFET region | (7) |

| ρJFET | The resistivity of the JFET region | (7) |

| HJP | Body junction depth | (7) |

| LCELL | Cell pitch | (7) |

| LJFET | JFET region width | (7) |

References

- Adell, P.C.; Scheick, L.Z. Radiation Effects in Power Systems: A Review. IEEE Trans. Sci. 2013, 60, 1929–1952. [Google Scholar] [CrossRef]

- Barth, J.; Gee, G.; Adolphsen, J.W. First observation of proton induced power MOSFET burnout in space: The CRUX experiment on APEX. IEEE Trans. Sci. 1996, 43, 2921–2926. [Google Scholar]

- George, J.S.; Clymer, D.A.; Turflinger, T.L.; Mason, L.W.; Stone, S.; Koga, R.; Beach, E.; Huntington, K.; Lauenstein, J.-M.; Titus, J.; et al. Response Variability in Commercial MOSFET SEE Qualification. IEEE Trans. Sci. 2017, 64, 317–324. [Google Scholar] [CrossRef]

- Kuboyama, S.; Mizuta, E.; Nakada, Y.; Shindou, H. Physical analysis of damage sites introduced by SEGR in silicon vertical power MOSFETs and implications for post-irradiation gate-stress test. IEEE Trans. Nucl. Sci. 2019, in press. [Google Scholar] [CrossRef]

- Singh, G.; Galloway, K.F.; Russell, T.J. Radiation-Induced Interface Traps in Power Mosfets. IEEE Trans. Sci. 1986, 33, 1454–1459. [Google Scholar] [CrossRef] [Green Version]

- Picard, C.; Brisset, C.; Hoffmann, A.; Charles, J.-P.; Joffre, F.; Adams, L.; Siedle, A.H. Use of electrical stress and isochronal annealing on power MOSFETs in order to characterize the effects of 60 Co irradiation. Microelectron. Reliab. 2000, 40, 1647–1652. [Google Scholar] [CrossRef]

- Titus, J.L. An Updated Perspective of Single Event Gate Rupture and Single Event Burnout in Power MOSFETs. IEEE Trans. Sci. 2013, 60, 1912–1928. [Google Scholar] [CrossRef]

- Roper, G.B.; Lowis, R. Development of a radiation hard n-channel power MOSFET. IEEE Trans. Nucl. Sci. 1983, 30, 4110–4115. [Google Scholar] [CrossRef]

- Davis, K.; Schrimpf, R.; Cellier, F.; Galloway, K.; Burton, D.; Wheatley, C. The effects of ionizing radiation on power-MOSFET termination structures. IEEE Trans. Sci. 1989, 36, 2104–2109. [Google Scholar] [CrossRef] [Green Version]

- Savage, M.; Burton, D.; Wheatley, C.; Titus, J.; Gillberg, J. An improved stripe-cell SEGR hardened power MOSFET technology. IEEE Trans. Sci. 2001, 48, 1872–1878. [Google Scholar] [CrossRef]

- Liu, S.; Titus, J.L.; Boden, M. Effect of Buffer Layer on Single-Event Burnout of Power DMOSFETs. IEEE Trans. Sci. 2007, 54, 2554–2560. [Google Scholar] [CrossRef]

- Wan, X.; Zhou, W.S.; Ren, S.; Liu, D.G.; Xu, J.; Bo, H.L.; Zhang, E.X.; Schrimpf, R.D.; Fleetwood, D.M.; Ma, T. SEB Hardened Power MOSFETs With High-K Dielectrics. IEEE Trans. Sci. 2015, 62, 2830–2836. [Google Scholar] [CrossRef]

- Baliga, B.J. Advanced Power MOSFET Concepts; Springer: New York, NY, USA, 2010; pp. 23–61. [Google Scholar]

- Grant, D.A.; Gowar, J. Power MOSFETs: Theory and Applications, 1st ed.; Wiley-Interscience: New York, NY, USA, 1989. [Google Scholar]

- Schrimpf, R.; Wahle, P.; Andrews, R.; Cooper, D.; Galloway, K. Dose-rate effects on the total-dose threshold-voltage shift of power MOSFETs. IEEE Trans. Sci. 1988, 35, 1536–1540. [Google Scholar] [CrossRef]

- Titus, J.; Wheatley, C.; Van Tyne, K.; Krieg, J.; Burton, D.; Campbell, A. Effect of ion energy upon dielectric breakdown of the capacitor response in vertical power MOSFETs. IEEE Trans. Sci. 1998, 45, 2492–2499. [Google Scholar] [CrossRef]

- Javanainen, A.; Ferlet-Cavrois, V.; Jaatinen, J.; Kettunen, H.; Muschitiello, M.; Pintacuda, F.; Rossi, M.; Schwank, J.R.; Shaneyfelt, M.R.; Virtanen, A. Semi-Empirical Model for SEGR Prediction. IEEE Trans. Sci. 2013, 60, 2660–2665. [Google Scholar] [CrossRef]

- STMicroelectronics. STRH8N10 Datasheets. Available online: https://www.st.com/resource/en/datasheet/strh8n10.pdf (accessed on 3 May 2019).

- Iakovlev, S.A.; Anashin, V.S.; Chubunov, P.A.; Koziukov, A.E.; Bu-Khasan, K.B.; Maksimenko, T.A.; Chlenov, A.M. MOSFETs SEB & SEGR qualification results with SOA estimation. In Proceedings of the 17th European Conference on Radiation and Its Effects on Components and Systems (RADECS), Geneva, Switzerland, 2–6 October 2017. [Google Scholar]

- Wheatley, C.; Titus, J.; Burton, D. Single-event gate rupture in vertical power MOSFETs; an original empirical expression. IEEE Trans. Sci. 1994, 41, 2152–2159. [Google Scholar] [CrossRef]

- Schwank, J.R.; Shaneyfelt, M.R.; Fleetwood, D.M.; Felix, J.A.; Dodd, P.E.; Paillet, P.; Ferlet-Cavrois, V. Radiation effects in MOS oxides. IEEE Trans. Nucl. Sci. 2008, 55, 1833–1853. [Google Scholar] [CrossRef]

- Fleetwood, D.; Meisenheimer, T.; Scofield, J. 1/f noise and radiation effects in MOS devices. IEEE Trans. Electron Devices 1994, 41, 1953–1964. [Google Scholar] [CrossRef]

- Rashkeev, S.; Cirba, C.; Fleetwood, D.; Schrimpf, R.; Witczak, S.; Michez, A.; Pantelides, S. Physical model for enhanced interface-trap formation at low dose rates. IEEE Trans. Sci. 2002, 49, 2650–2655. [Google Scholar] [CrossRef]

- Hohl, J.H.; Galloway, K.F. Analytical model for single event burnout of power MOSFETs. IEEE Trans. Electron Devices 1994, 41, 1953–1964. [Google Scholar] [CrossRef]

- Wrobel, T.; Beutler, D. Solutions to heavy ion induced avalanche burnout in power devices. IEEE Trans. Sci. 1992, 39, 1636–1641. [Google Scholar] [CrossRef] [Green Version]

- Johnson, G.H.; Palau, J.M.; Dachs, C.; Galloway, K.F.; Schrimpf, R.D. A review of the techniques used for modeling single-event effects in power MOSFET’s. IEEE Trans. Nucl. Sci. 1996, 43, 546–560. [Google Scholar] [CrossRef]

- Department of Defense. MIL-STD-883E, Test Method 1019.4. Ionizing Radiation (Total Dose) Test Procedure; Defense Supply Center Columbus: Columbus, OH, USA, 1996. [Google Scholar]

- Department of Defense. MIL-STD-750E, Test Method 1019.5 Steady-State Total Dose Irradiation Procedure; Defense Supply Center Columbus: Columbus, OH, USA, 2006. [Google Scholar]

- Khosropour, P.; Galloway, K.F.; Zupac, D.; Schrimpf, R.D.; Calvel, P. Application of test method 1019.4 to non-hardened power MOSFETs. IEEE Trans. Nucl. Sci. 1994, 41, 555–560. [Google Scholar] [CrossRef]

- Winokur, P.S.; Schwank, J.R.; McWhorter, P.J.; Dressendorfer, P.V.; Turpin, D.C. Correlating the Radiation Response of MOS Capacitors and Transistors. IEEE Trans. Sci. 1984, 31, 1453–1460. [Google Scholar] [CrossRef]

- McWhorter, P.J.; Winokur, P.S. Simple technique for separating the effects of interface traps and trapped-oxide charge in metal-oxide-semiconductor transistors. Appl. Phys. Lett. 1986, 48, 133–135. [Google Scholar] [CrossRef]

- Zupac, D.; Galloway, K.; Khosropour, P.; Anderson, S.; Schrimpf, R.; Calvel, P. Separation of effects of oxide-trapped charge and interface-trapped charge on mobility in irradiated power MOSFETs. IEEE Trans. Sci. 1993, 40, 1307–1315. [Google Scholar] [CrossRef]

| Symbol in Figure 1 | Value | Unit |

|---|---|---|

| tox | 80 | nm |

| HJP | 3 | µm |

| LCELL | 10 | µm |

| LBODY | ~2 | µm |

| LJFET | ~3 | µm |

| NBODY | ~5 × 1016 | cm−3 |

| Unit | Virgin | 150 krad(Si) | Anneal | ||||

|---|---|---|---|---|---|---|---|

| Gate Bias | Drain Bias | Gate Bias | Drain Bias | Gate Bias | Drain Bias | ||

| VT | V | 3.75 | 3.82 | 3.61 | 3.68 | 3.88 | 3.66 |

| Vot | V | 0.96 | 0.99 | 0.45 | 0.30 | 0.68 | 0.69 |

| µn | cm2/V·s | 319.34 | 339.00 | 273.30 | 252.45 | 219.05 | 279.15 |

| ΔVT | V | 0.00 | 0.00 | −0.14 | −0.14 | 0.13 | −0.15 |

| ΔVot | V | 0.00 | 0.00 | −0.51 | −0.69 | −0.28 | −0.30 |

| ΔVit | V | 0.00 | 0.00 | 0.37 | 0.55 | 0.41 | 0.14 |

| ΔNot | cm−2 | 0.00 | 0.00 | 1.37 × 1011 | 1.86 × 1011 | 0.76 × 1011 | 0.80 × 1011 |

| ΔNit | cm−2 | 0.00 | 0.00 | 1.00 × 1011 | 1.48 × 1011 | 1.11 × 1011 | 0.39 × 1011 |

| Δµn | cm2/V·s | 0.00 | 0.00 | −46.05 | −86.85 | −100.29 | −59.85 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, T.; Wan, X.; Jin, H.; Li, H.; Sun, Y.; Liang, R.; Xu, J.; Zheng, L. Optimization of the Cell Structure for Radiation-Hardened Power MOSFETs. Electronics 2019, 8, 598. https://doi.org/10.3390/electronics8060598

Wang T, Wan X, Jin H, Li H, Sun Y, Liang R, Xu J, Zheng L. Optimization of the Cell Structure for Radiation-Hardened Power MOSFETs. Electronics. 2019; 8(6):598. https://doi.org/10.3390/electronics8060598

Chicago/Turabian StyleWang, Teng, Xin Wan, Hu Jin, Hao Li, Yabin Sun, Renrong Liang, Jun Xu, and Lirong Zheng. 2019. "Optimization of the Cell Structure for Radiation-Hardened Power MOSFETs" Electronics 8, no. 6: 598. https://doi.org/10.3390/electronics8060598