RHBD Techniques to Mitigate SEU and SET in CMOS Frequency Synthesizers

Abstract

:1. Introduction

2. Architecture of the Frequency Synthesizer

2.1. Phase-Frequency Detector (PFD) and Charge Pump (CP)

2.2. Low Pass Filter (LPF)

2.3. Voltage Controlled Oscillator (VCO)

2.4. Frequency Divider by Two (FD2)

2.5. Mixer Buffer (MB) and CML to CMOS Converter (CML2CMOS Converter)

2.6. Programmable Frequency Divider (Programmable-FD)

3. SET and SEU Analysis in the Frequency Synthesizer

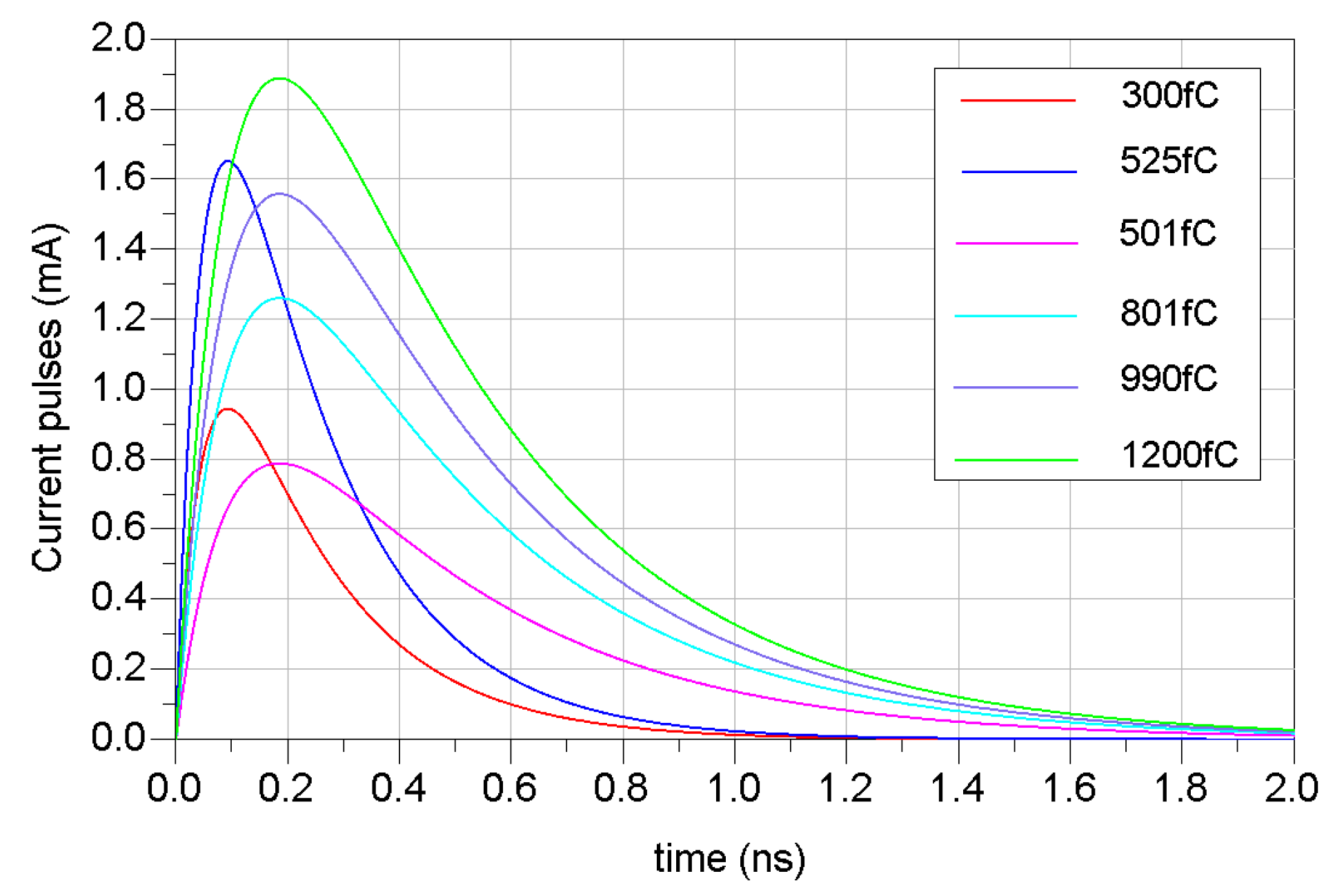

3.1. Impacts Modeling

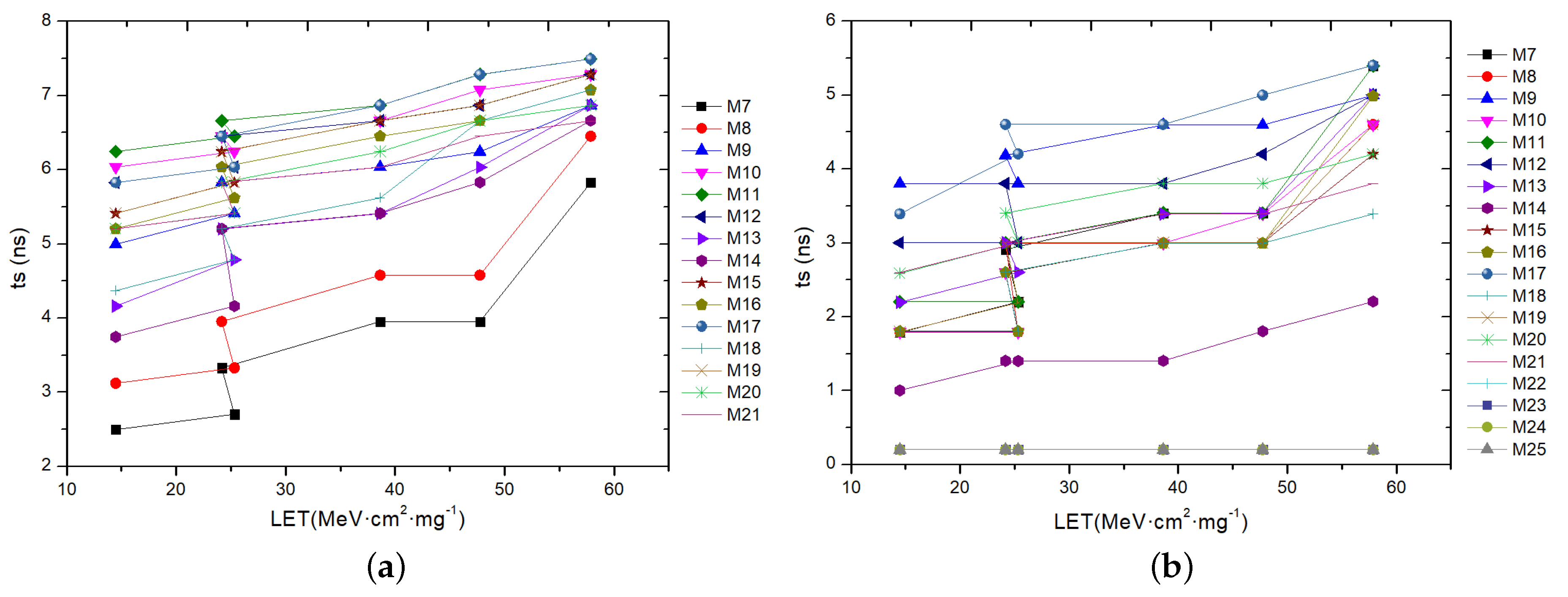

3.2. SET and SEU Analysis

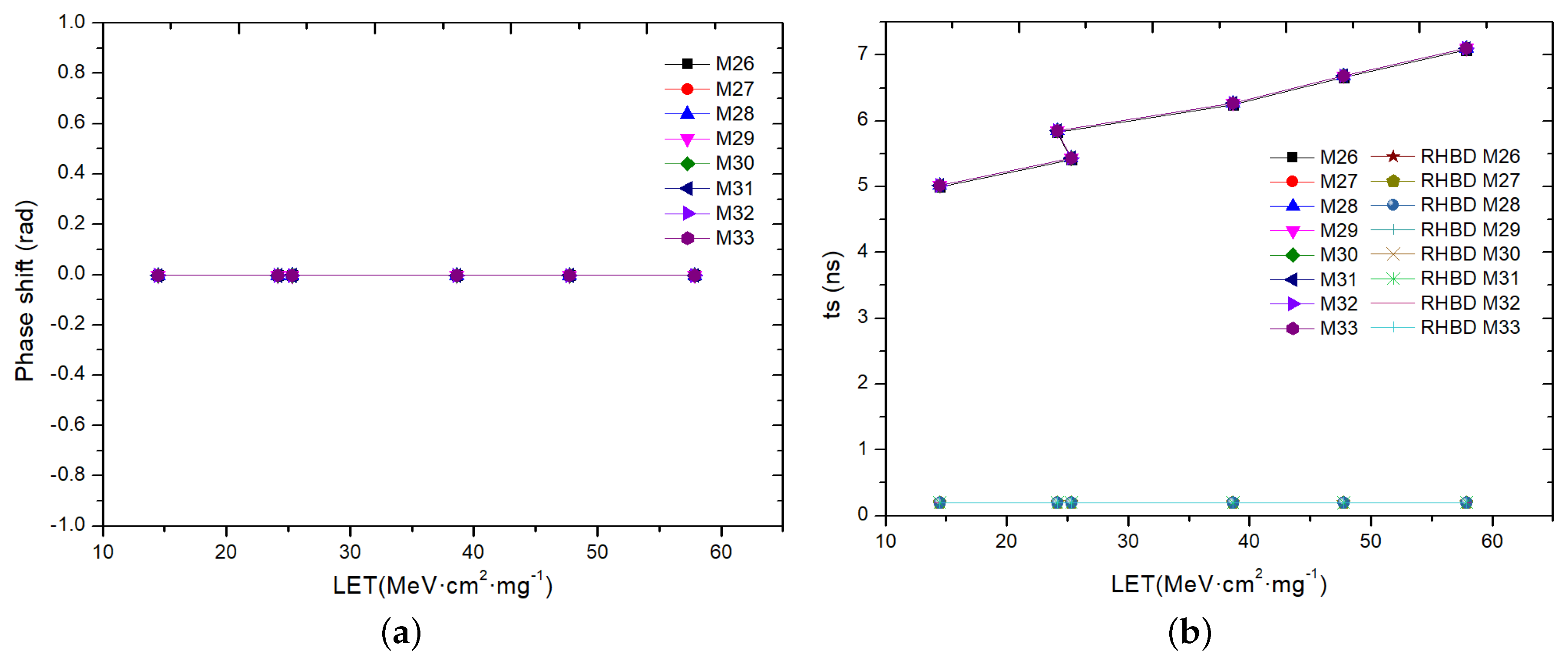

4. RHBD Design

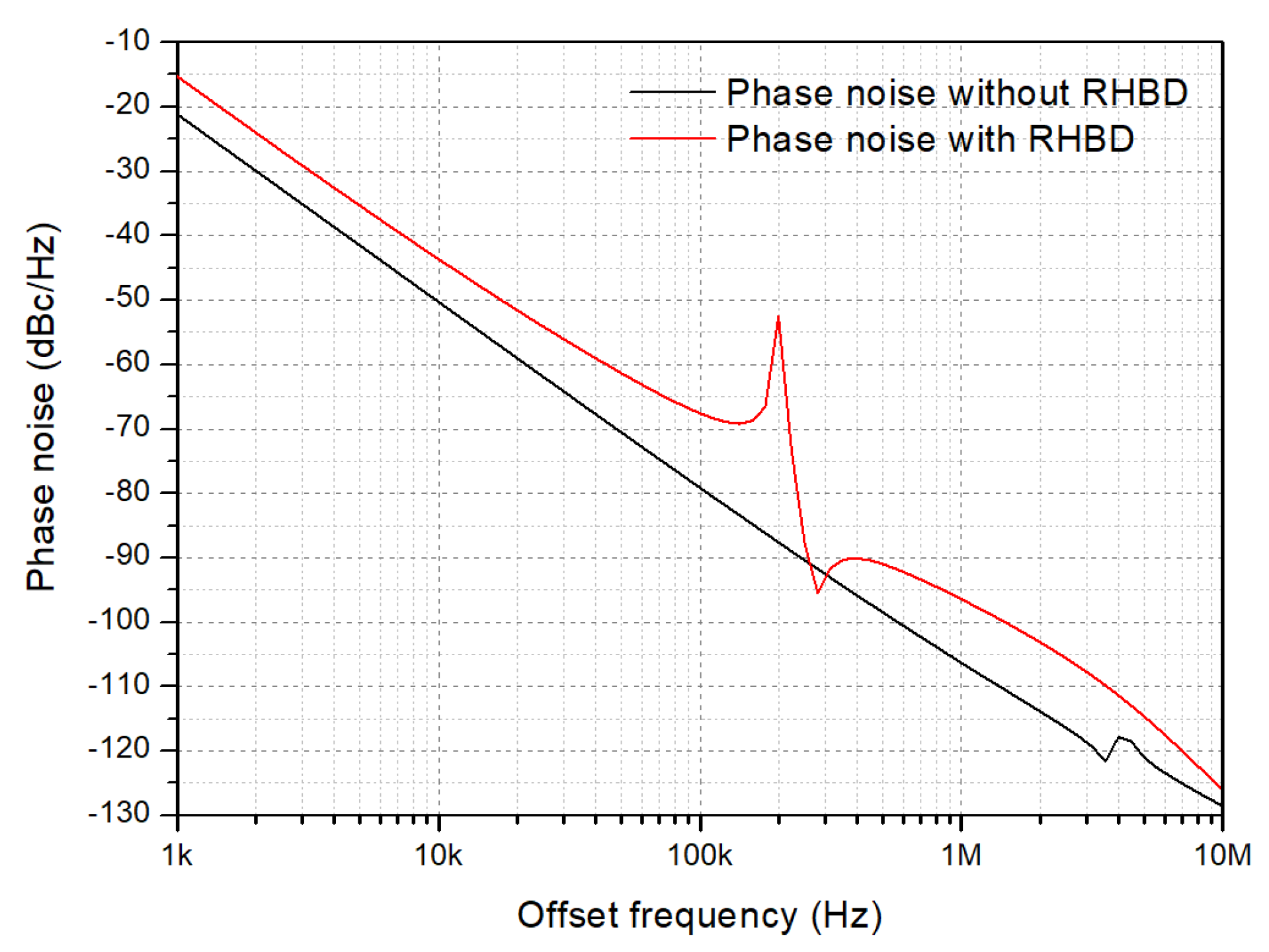

4.1. VCO

4.2. FD2

4.3. CML2CMOS Converter and MB

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Abbreviations

| CML | Current-Mode Logic |

| CML2CMOS converter | CML to CMOS converter |

| CMOS | Complementary Metal-Oxide-Semiconductor |

| CP | Charge Pump |

| DICE | Dual Interlocked Storage Cell |

| D2SE | Differential to Single-Ended |

| FD2 | Frequency Divider by 2 |

| GFC | Gated Feedback Cell |

| IEEE | The Institute of Electrical and Electronics Engineers |

| LET | Linear Energy Transfer |

| LPF | Low Pass Filter |

| MB | Mixer Buffer |

| O-QPSK | Offset Quadrature Phase Shift Keying |

| PD-SOI | Partially Depleted-Silicon-on-Insulator |

| PFD | Phase Frequency Detector |

| Programmable-FD | Programmable Frequency Divider |

| PLL | Phase-Locked Loop |

| RC | Resistor–Capacitor |

| RF | Radio Frequency |

| RHBD | Radiation Hardening-By-Design |

| SEE | Single Event Effect |

| SET | Single Event Transient |

| SET-HBD-CP | SET-Hardened-By-Design Charge Pump |

| SEU | Single Event Upset |

| TMR | Triple Modular Redundancy |

| VCO | Voltage Controlled Oscillator |

| WSN | Wireless Sensor Networks |

References

- Bagatin, M.; Gerardin, S. Ionizing Radiation Effects in Electronics: From Memories To Imagers; CRC Press: Boca Raton, FL, USA, 2015; p. 391. [Google Scholar]

- Gaillard, R. Single Event Effects: Mechanisms and Classification. In Soft Errors in Modern Electronic Systems. Frontiers in Electronic Testing; Springer: Boston, MA, USA, 2011; pp. 27–54. [Google Scholar] [CrossRef]

- Kerns, S.E.; Shafer, B.D. The Design of Radiation-Hardened ICS for Space: A Compendium of Approaches. Proc. IEEE 1988, 76, 1470–1509. [Google Scholar] [CrossRef]

- Wang, T. Study of Single-Event Transient Effects on Analog Circuits. Ph.D. Thesis, University of Saskatchewan, Saskatoon, SK, Canada, 2011. [Google Scholar]

- Dayaratna, L.; Seehra, S.; Bogorad, A.; Ramos, L. Single event upset characteristics of some digital integrated frequency synthesizers. In Proceedings of the 1999 IEEE Radiation Effects Data Workshop. Workshop Record. Held in conjunction with IEEE Nuclear and Space Radiation Effects Conference (Cat. No.99TH8463), Norfolk, VA, USA, 12–16 June 1999; pp. 46–52. [Google Scholar] [CrossRef]

- Chung, H.H.; Chen, W.; Bakkaloglu, B.; Barnaby, H.J.; Vermeire, B.; Kiaei, S. Analysis of Single Events Effects on Monolithic PLL Frequency Synthesizers. IEEE Trans. Nucl. Sci. 2006, 53, 3539–3543. [Google Scholar] [CrossRef]

- Sotskov, D.I.; Elesin, V.V.; Kuznetsov, A.G.; Nazarova, G.N.; Chukov, G.V.; Boychenko, D.V.; Telets, V.A.; Usachev, N.A. Total Ionizing Dose Effects in Phase-Locked Loop ICs and Frequency Synthesizers. In Proceedings of the 2015 15th European Conference on Radiation and Its Effects on Components and Systems (RADECS), Moscow, Russia, 14–18 September 2015; pp. 1–3. [Google Scholar] [CrossRef]

- Chen, Z.; Ding, D.; Dong, Y.; Shan, Y.; Zhou, S.; Hu, Y.; Zheng, Y.; Peng, C.; Chen, R. Study of Total-Ionizing-Dose Effects on a Single-Event-Hardened Phase-Locked Loop. IEEE Trans. Nucl. Sci. 2018, 65, 997–1004. [Google Scholar] [CrossRef]

- Prinzie, J.; Christiansen, J.; Moreira, P.; Steyaert, M.; Leroux, P. Comparison of a 65 nm CMOS ring- and lc-oscillator based PLL in terms of TID and SEU sensitivity. IEEE Trans. Nucl. Sci. 2017, 64, 245–252. [Google Scholar] [CrossRef]

- Zhang, Z.; Chen, L.; Djahanshahi, H. A Hardened-By-Design Technique for LC-Tank Voltage Controlled Oscillator. In Proceedings of the 2018 IEEE Canadian Conference on Electrical & Computer Engineering (CCECE), Quebec City, QC, Canada, 13–16 May 2018; pp. 1–4. [Google Scholar] [CrossRef]

- Zhou, Q.; Zhang, C.; Tan, J.; Zhu, L.; Wang, L.; Luo, W. A SET-hardened phase-locked loop. In Proceedings of the 2017 IEEE 3rd Information Technology and Mechatronics Engineering Conference (ITOEC), Chongqing, China, 3–5 October 2017; pp. 196–199. [Google Scholar] [CrossRef]

- Li, N.; She, X. Single event transient tolerant frequency divider. IET Comput. Digit. Tech. 2014, 8, 140–147. [Google Scholar] [CrossRef]

- Chen, Z.; Lin, M.; Ding, D.; Zheng, Y.; Sang, Z.; Zou, S. Analysis of Single-Event Effects in a Radiation-Hardened Low-Jitter PLL Under Heavy Ion and Pulsed Laser Irradiation. IEEE Trans. Nucl. Sci. 2017, 64, 106–112. [Google Scholar] [CrossRef]

- Standards Committee of the IEEE Computer Society. IEEE Standard for Local and Metropolitan Area Networks—Part 15.4: Low-Rate Wireless Personal Area Networks (WPANs); IEEE Std 802.15.4-2011; Standards Committee of the IEEE Computer Society: New York, NY, USA, 2006. [Google Scholar]

- Weste, N.H.E.; Harris, D.M. CMOS VLSI Design: A Circuits and Systems Perspective; Addison Wesley: Boston, MA, USA, 2011; p. 838. [Google Scholar]

- Razavi, B. Design of Analog CMOS Integrated Circuits; McGraw-Hill: New York, NY, USA, 2001; p. 684. [Google Scholar]

- Fujitsu Microelectronics America Inc. Super PLL Application Guide: Integer PLL Loop Filter Design; Fujitsu Microelectronics America Inc.: San Jose, CA, USA, 2002; pp. 22–24. [Google Scholar]

- Hajimiri, A.; Lee, T. Design issues in CMOS differential LC oscillators. IEEE J. Solid-State Circuits 1999, 34, 717–724. [Google Scholar] [CrossRef] [Green Version]

- Senjaliya, C.; Neelakantan, U. 180 nm CMOS process based L-band CML to CMOS converter. IJARIIE 2018, 4, 3697–3700. [Google Scholar]

- Portela-Garcia, M.; Lopez-Ongil, C.; Garcia-Valderas, M.; Entrena, L.; Thys, G.; Redant, S. Assessing SET sensitivity of a PLL. In Proceedings of the Design of Circuits and Integrated Systems, Madrid, Spain, 26–28 November 2014; pp. 1–6. [Google Scholar] [CrossRef]

- Garg, R.; Khatri, S.P. Analysis and Design of Resilient VLSI Circuits. Ph.D. Thesis, Texas A&M University, College Station, TX, USA, 2010. [Google Scholar] [CrossRef] [Green Version]

- Lochner, S.; Deppe, H. Radiation studies on the UMC 180 nm CMOS process at GSI. In Proceedings of the 2009 European Conference on Radiation and Its Effects on Components and Systems, Bruges, Belgium, 14–18 September 2009; pp. 614–616. [Google Scholar] [CrossRef]

- Eaton, P.; Benedetto, J.; Mavis, D.; Avery, K.; Sibley, M.; Gadlage, M.; Turflinger, T. Single event transient pulsewidth measurements using a variable temporal latch technique. IEEE Trans. Nucl. Sci. 2004, 51, 3365–3368. [Google Scholar] [CrossRef]

- Mateos-Angulo, S.; Rodríguez, R.; del Pino, J.; González, B.; Khemchandani, S.L. Single event effects analysis and charge collection mechanisms on AlGaN/GaN HEMTs. Semicond. Sci. Technol. 2019, 34, 035029. [Google Scholar] [CrossRef]

- González Ramírez, D.; Lalchand Khemchandani, S.; del Pino, J.; Mayor-Duarte, D.; San Miguel-Montesdeoca, M.; Mateos-Angulo, S. Single event transients mitigation techniques for CMOS integrated VCOs. Microelectron. J. 2018, 73, 37–42. [Google Scholar] [CrossRef]

- Mateos-Angulo, S.; San-Miguel-Montesdeoca, M.; Mayor-Duarte, D.; Khemchandani, S.L.; del Pino, J. SET analysis and radiation hardening techniques for CMOS LNA topologies. Semicond. Sci. Technol. 2018, 33, 085010. [Google Scholar] [CrossRef]

- Lalchand Khemchandani, S.; del Pino Suarez, J.; Diaz Ortega, R.; Hernandez, A. A fully integrated single core VCO with a wide tuning range for DVB-H. Microw. Opt. Technol. Lett. 2009, 51, 1338–1343. [Google Scholar] [CrossRef]

- Calin, T.; Nicolaidis, M.; Velazco, R. Upset hardened memory design for submicron CMOS technology. IEEE Trans. Nucl. Sci. 1996, 43, 2874–2878. [Google Scholar] [CrossRef]

- Krithivasan, R.; Marshall, P.W.; Nayeem, M.; Sutton, A.K.; Kuo, W.M.; Haugerud, B.M.; Najafizadeh, L.; Cressler, J.D.; Carts, M.A.; Marshall, C.J.; et al. Application of RHBD Techniques to SEU Hardening of Third-Generation SiGe HBT Logic Circuits. IEEE Trans. Nucl. Sci. 2006, 53, 3400–3407. [Google Scholar] [CrossRef]

| tr (ps) | tf (ps) | Q (fC) | LET, d = 2 m (MeV·cm2·mg−1) |

|---|---|---|---|

| 50 | 200 | 300 | 14.47 |

| 50 | 200 | 525 | 25.31 |

| 100 | 400 | 501 | 24.16 |

| 100 | 400 | 801 | 38.62 |

| 100 | 400 | 990 | 47.74 |

| 100 | 400 | 1200 | 57.86 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Díez-Acereda, V.; L. Khemchandani, S.; del Pino, J.; Mateos-Angulo, S. RHBD Techniques to Mitigate SEU and SET in CMOS Frequency Synthesizers. Electronics 2019, 8, 690. https://doi.org/10.3390/electronics8060690

Díez-Acereda V, L. Khemchandani S, del Pino J, Mateos-Angulo S. RHBD Techniques to Mitigate SEU and SET in CMOS Frequency Synthesizers. Electronics. 2019; 8(6):690. https://doi.org/10.3390/electronics8060690

Chicago/Turabian StyleDíez-Acereda, V., Sunil L. Khemchandani, J. del Pino, and S. Mateos-Angulo. 2019. "RHBD Techniques to Mitigate SEU and SET in CMOS Frequency Synthesizers" Electronics 8, no. 6: 690. https://doi.org/10.3390/electronics8060690