Enhanced Thermal Management of GaN Power Amplifier Electronics with Micro-Pin Fin Heat Sinks

Abstract

:1. Introduction

2. Experimental and Simulation Details

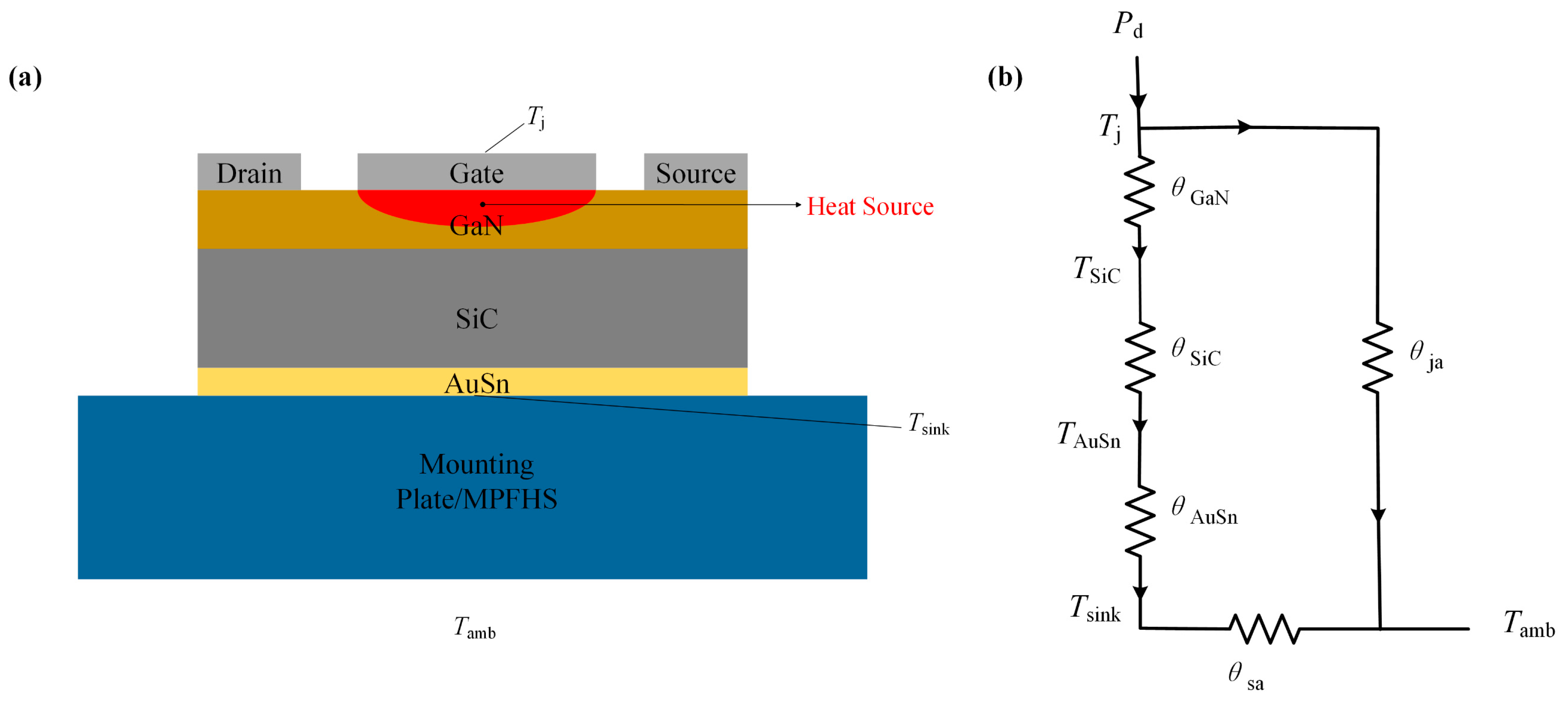

2.1. GaN-on-SiC Power Amplifier and Thermal Experiments

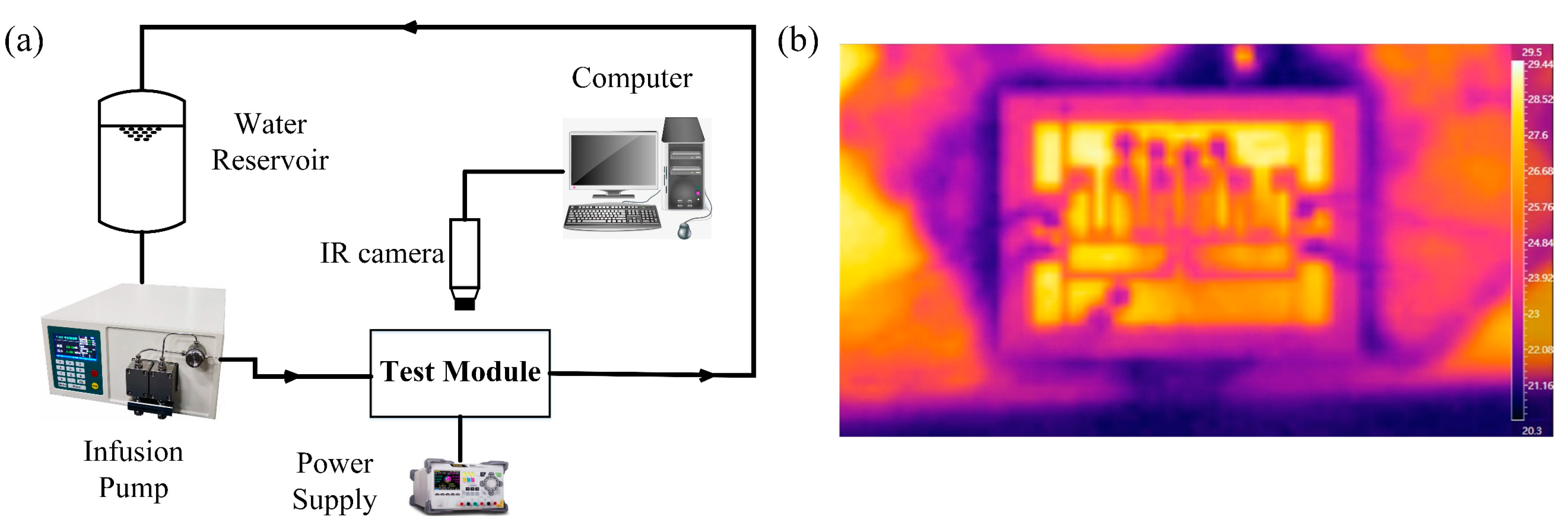

2.2. MPFHS Fabrication and Experimental Loop

2.3. Thermal Simulation

2.4. Data Reduction

3. Results and Discussion

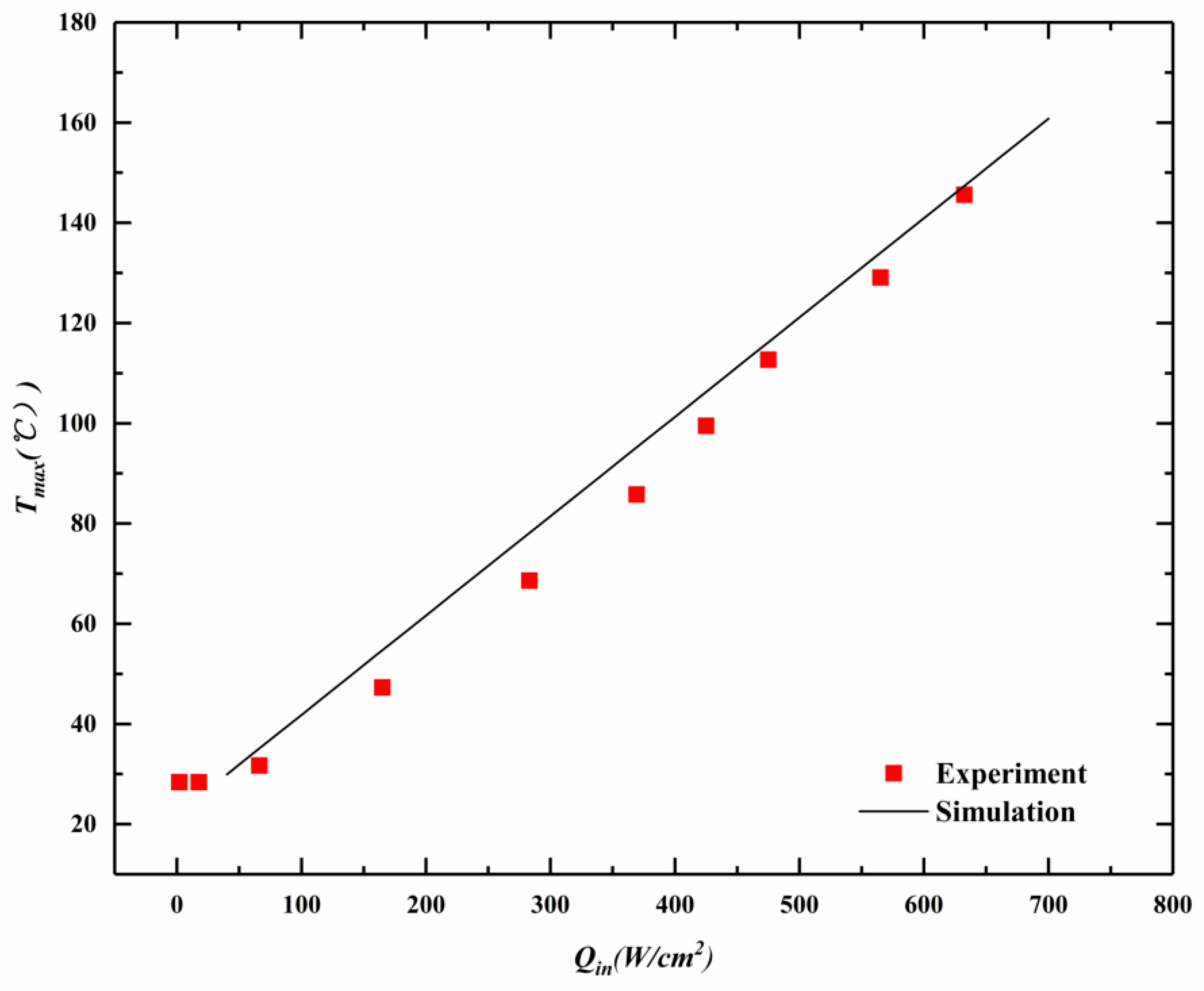

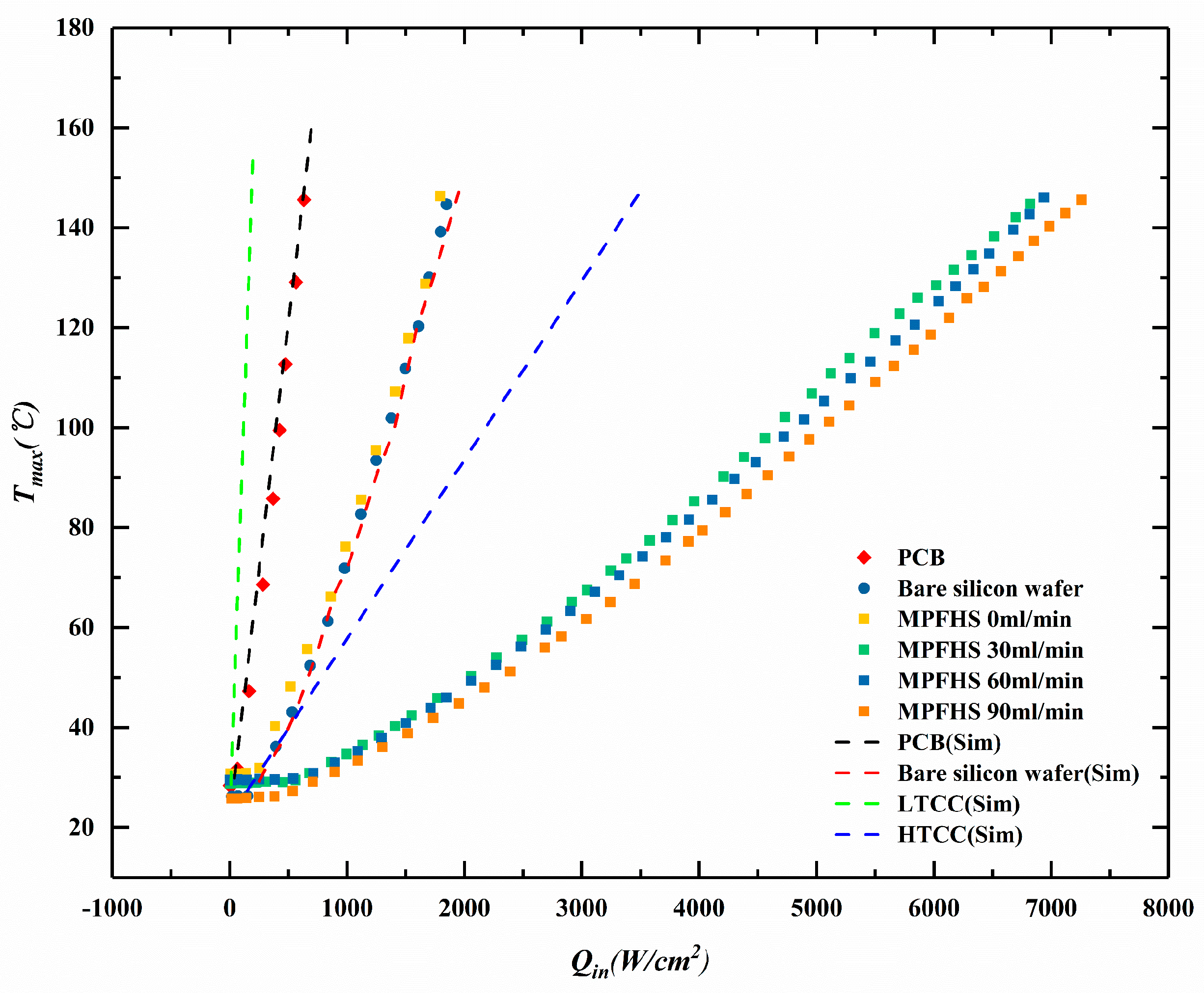

3.1. PCB, Bare Silicon Wafer and MPFHS

3.2. Thermal Resistance Analysis

4. Conclusions

- (1)

- The thermal performance of a GaN device can be improved by increasing the thermal conductivity of the mounting material. The dissipated power density of the GaN power amplifier was 200 W/cm2 when mounted on LTCC (thermal conductivity is 2 Wm−1 K−1). While mounted on HTCC (thermal conductivity increasing to 180 Wm−1 K−1), the power density increased 17.5-fold to 3500 W/cm2.

- (2)

- The thermal performance of a GaN device can be improved by applying a silicon-based micro-pin fin heat sink. When mounted on the MPFHS, the power density reached 7250 W/cm2 (at a Tj of 145 °C and a mass flow rate of 90 mL/min), which is nearly a two-fold increase compared with traditional mounting material HTCC. This means that using a silicon-based MPFHS can improve the reliability of the device and reduce the junction temperature effectively, making it a promising thermal management method.

- (3)

- The improvement of thermal management was limited for GaN mounted on the MPFHS, with a mass flow rate increase from 30 to 90 mL/min. Nonetheless, lots of heat sink optimization schemes could be further developed to achieve the optimal cooling effect, such as the cross-shape of micro-pin fins or the pin fin arrangement.

- (4)

- The θtotal was improved 18.5-fold compared with the PCB and MPFHS at a mass flow rate of 90 mL/min. These significant results can elongate the mean time to failure and ensure a more reliable operation of GaN devices.

- (5)

- Replacing the traditional base plates (PCB, silicon wafer and LTCC/HTCC) with an MPFHS plate can significantly reduce the θjs to approach the theoretical limitation value. In future studies, this is a promising and possible way of developing the die-attach method in order to improve thermal interface resistance for solving this bottleneck problem. Alternatively, removing interface layers and adopting an interchip cooling strategy are also the promising approaches.

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Nomenclature

| ΔT | Temperature Drop [°C] |

| c | Specific Heat [Jkg−1 K−1] |

| FEM | Finite Element Model |

| HTCC | High-Temperature Co-fired Ceramics |

| h | Heat Transfer Coefficient [Wm−2 K−1] |

| k | Thermal Conductivity [Wm−1 K−1] |

| LTCC | Low-Temperature Co-fired Ceramics |

| MPFHS | Micro Pin Fin Heat Sink |

| P | Power [W] |

| PA | Power Amplifier |

| PCB | Printed Circuit Board |

| Q | Power Density [W/cm2] |

| Greek symbols | |

| θ | Thermal Resistance [°C/W] |

| ρ | Density [kg/m3] |

| Subscripts | |

| amb | Ambient |

| d | Dissipated power density |

| in | Input |

| j | Junction |

| ja | Junction to Ambient Air |

| js | Junction to Sink |

| max | Maximum |

| sa | Sink to Ambient Air |

| sink | Heat Sink |

| total | Total Thermal Resistance |

References

- Pomeroy, J.; Bernardoni, M.; Sarua, A.; Manoi, A.; Dumka, D.C.; Fanning, D.M.; Kuball, M. Achieving the Best Thermal Performance for GaN-on-Diamond. In Proceedings of the 2013 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), Monterey, CA, USA, 13–16 October 2013; pp. 1–4. [Google Scholar]

- Park, J.; Shin, M.W.; Lee, C. Thermal Modeling and Measurement of GaN-Based HFET Devices. IEEE Electron Device Lett. 2003, 24, 424–426. [Google Scholar] [CrossRef]

- Sarua, A.; Ji, H.; Kuball, M.; Uren, M.; Martin, T.; Hilton, K.; Balmer, R. Integrated micro-Raman/ Infrared Thermography Probe for Monitoring of Self-Heating in AlGaN/GaN Transistor Structures. IEEE Trans. Electron Devices 2006, 53, 2438–2447. [Google Scholar] [CrossRef]

- Tian, T.; Sun, X.; Gao, H.; Lu, S. Improved Thermal Management of Power Cells with Adding Cooling Path from Collector to Ground. Electron. Lett. 2019, 55, 513–515. [Google Scholar] [CrossRef]

- Samanta, K.K. PA Thermal Management and Packaging: Wideband PA and Packaging, History, and Recent Advances: Part 2. IEEE Microw. Mag. 2016, 17, 73–81. [Google Scholar] [CrossRef]

- Sarua, A.; Ji, H.; Hilton, K.P.; Wallis, D.J.; Uren, M.J.; Martin, T.; Kuball, M. Thermal Boundary Resistance Between GaN and Substrate in AlGaN/GaN Electronic Devices. IEEE Trans. Electron Devices 2007, 54, 3152–3158. [Google Scholar] [CrossRef]

- Kuball, M.; Rajasingam, S.; Sarua, A.; Uren, M.J.; Martin, T.J.; Hughes, B.T.; Hilton, K.P.; Balmer, R.S. Measurement of Temperature Distribution in Multifinger AlGaN/GaN Heterostructure Field-Effect Transistors Using Micro-Raman Spectroscopy. Appl. Phys. Lett. 2003, 82, 124–126. [Google Scholar] [CrossRef]

- Faqir, M.; Batten, T.; Mrotzek, T.; Knippscheer, S.; Massiot, M.; Buchta, M.; Blanck, H.; Rochette, S.; Vendier, O.; Kuball, M. Improved Thermal Management for Gan Power Electronics: Silver Diamond Composite Packages. Microelectron. Reliab. 2012, 52, 3022–3025. [Google Scholar] [CrossRef]

- GaN Power Amplifier Design Solutions. 2018. Available online: https://www.microwavejournal.com/articles/31075-gan-power-amplifier-design-solutions (accessed on 20 October 2020).

- Ma, A.; Wei, J.; Yuan, M.; Fang, J. Enhanced Flow Boiling Heat Transfer of FC-72 on Micro-Pin-Finned Surfaces. Int. J. Heat Mass Transf. 2009, 52, 2925–2931. [Google Scholar] [CrossRef]

- Krishnamurthy, S.; Peles, Y. Flow Boiling of Water in a Circular Staggered Micro-Pin Fin Heat Sink. Int. J. Heat Mass Transf. 2008, 51, 1349–1364. [Google Scholar] [CrossRef]

- Colthup, N.B.; Daly, L.H.; Wiberley, S.E. Introduction to Infrared and Raman Spectroscopy, 2nd ed.; Academy Press: New York, NY, USA, 1975; pp. 69–118. [Google Scholar]

- Lorenzini, D.; Green, C.; Sarvey, T.; Zhang, X.; Hu, Y.; Fedorov, A.G.; Bakir, M.S.; Joshi, Y. Embedded Single Phase Microfluidic Thermal Management for Non-Uniform Heating and Hotspots Using Microgaps with Variable Pin Fin Clustering. Int. J. Heat Mass Transf. 2016, 103, 1359–1370. [Google Scholar] [CrossRef]

- Shafeie, H.; Abouali, O.; Jafarpur, K.; Ahmadi, G. Numerical Study of Heat Transfer Performance of Single-Phase Heat Sinks with Micro Pin-Fin Structures. Appl. Therm. Eng. 2013, 58, 68–76. [Google Scholar] [CrossRef]

- Gregorčič, P.; Zupančič, M.; Golobič, I. Scalable Surface Microstructuring by a Fiber Laser for Controlled Nucleate Boiling Performance of High-and Low-Surface-Tension Fluids. Sci. Rep. 2018, 8, 7461. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Heo, K.Y.; Kihm, K.D.; Lee, J.S. Fabrication and Experiment of Micro-Pin-Finned Microchannels to Study Surface Roughness Effects on Convective Heat Transfer. J. Micromechanics Microengineering 2014, 24, 125025. [Google Scholar] [CrossRef]

- Alam, T.; Lee, P.; Yap, C.R. Effects of Surface Roughness on Flow Boiling in Silicon Microgap Heat Sinks. Int. J. Heat Mass Transf. 2013, 64, 28–41. [Google Scholar] [CrossRef]

- Chen, B.; Zhou, Z.; Shi, J.; Schafer, S.R.; Chen, C.-L. Flooded Two-Phase Flow Dynamics and Heat Transfer with Engineered Wettability on Microstructured Surfaces. J. Heat Transf. 2015, 137, 091021. [Google Scholar] [CrossRef] [Green Version]

- Shen, C.; Zhang, C.; Bao, Y.; Wang, X.; Liu, Y.; Ren, L. Experimental Investigation on Enhancement of Nucleate Pool Boiling Heat Transfer Using Hybrid Wetting Pillar Surface at Low Heat Fluxes. Int. J. Therm. Sci. 2018, 130, 47–58. [Google Scholar] [CrossRef]

- Li, Q.; Yu, Y.; Zhou, P.; Yan, H. Enhancement of Boiling Heat Transfer Using Hydrophilic-Hydrophobic Mixed Surfaces: A Lattice Boltzmann Study. Appl. Therm. Eng. 2018, 132, 490–499. [Google Scholar] [CrossRef]

- Kim, B.S.; Shin, S.; Lee, D.; Choi, G.; Lee, H.; Kim, K.M.; Cho, H.H. Stable and Uniform Heat Dissipation by Nucleate-Catalytic Nanowires for Boiling Heat Transfer. Int. J. Heat Mass Transf. 2014, 70, 23–32. [Google Scholar] [CrossRef]

- Kim, B.S.; Shin, S.; Shin, S.J.; Kim, K.M.; Cho, H.H. Control of Superhydrophilicity/Superhydrophobicity using Silicon Nanowires via Electroless Etching Method and Fluorine Carbon Coatings. Langmuir ACS J. Surf. Colloids 2011, 27, 10148–10156. [Google Scholar] [CrossRef]

- Dixit, P.; Lin, N.; Miao, J.; Wong, W.K.; Choon, T.K. Silicon Nanopillars Based 3D Stacked Microchannel Heat Sinks Concept for Enhanced Heat Dissipation Applications in MEMS Packaging. Sens. Actuators A Phys. 2008, 141, 685–694. [Google Scholar] [CrossRef]

- Bar-Cohen, A.; Maurer, J.J.; Felbinger, J.G. Darpa’s Intra/Interchip Enhanced Cooling (Icecool) Program. In Proceedings of the International Conference on Compound Semiconductor Manufacturing Technology, CS MANTECH, New Orleans, LA, USA, 13–16 May 2013; pp. 171–174. [Google Scholar]

- Bar-Cohen, A. Gen-3 Thermal Management Technology: Role of Microchannels and Nanostructures in an Embedded Cooling Paradigm. J. Nanotechnol. Eng. Med. 2013, 4, 020907. [Google Scholar] [CrossRef]

| Parameters | GaN PA | PCB (Printed Circuit Board) | Bare Silicon Wafer | MPFHS |

|---|---|---|---|---|

| Length | 1100 μm | 2 cm | 2 cm | 2 cm |

| Width | 800 μm | 2 cm | 2 cm | 2 cm |

| Materials | Thermal Conductivity [Wm−1 K−1] | Specific Heat [Jkg−1 K−1] | ρ [kg m−3] | Thickness [μm] | Area [mm2] |

| GaN | 150 | 490 | 6070 | 2 | 1.1 × 0.8 |

| SiC | 420 | 690 | 3216 | 50 | 1.1 × 0.8 |

| AuSn | 57 | 150 | 14,700 | 25 | 1.1 × 0.8 |

| LTCC | 2 | 900 | 2500 | 500 | 20 × 20 |

| PCB | 9.5 | 1369 | 1900 | 500 | 20 × 20 |

| Si | 150 | 700 | 2329 | 500 | 20 × 20 |

| HTCC | 180 | 750 | 3280 | 500 | 20 × 20 |

| Dissipated Heat Power (W) | θja (°C W−1) | θjs (°C W−1) | θsa (°C W−1) | θtotal (°C W−1) | |

|---|---|---|---|---|---|

| PCB | 1.012 | 122.13 | 16.92 | 105.22 | 61.07 |

| Bare silicon wafer | 1.068 | 28.46 | 8.61 | 19.85 | 14.237 |

| MPFHS (0 mL/min) | 1.059 | 31.82 | 9.93 | 21.90 | 15.917 |

| MPFHS (30 mL/min) | 1.087 | 8.188 | 4.02 | 4.17 | 4.097 |

| MPFHS (60 mL/min) | 1.133 | 7.81 | 3.83 | 3.99 | 3.91 |

| MPFHS (90 mL/min) | 1.139 | 6.27 | 3.63 | 2.63 | 3.13 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kang, T.; Ye, Y.; Jia, Y.; Kong, Y.; Jiao, B. Enhanced Thermal Management of GaN Power Amplifier Electronics with Micro-Pin Fin Heat Sinks. Electronics 2020, 9, 1778. https://doi.org/10.3390/electronics9111778

Kang T, Ye Y, Jia Y, Kong Y, Jiao B. Enhanced Thermal Management of GaN Power Amplifier Electronics with Micro-Pin Fin Heat Sinks. Electronics. 2020; 9(11):1778. https://doi.org/10.3390/electronics9111778

Chicago/Turabian StyleKang, Ting, Yuxin Ye, Yuncong Jia, Yanmei Kong, and Binbin Jiao. 2020. "Enhanced Thermal Management of GaN Power Amplifier Electronics with Micro-Pin Fin Heat Sinks" Electronics 9, no. 11: 1778. https://doi.org/10.3390/electronics9111778