Hot Carrier Stress Sensing Bulk Current for 28 nm Stacked High-k nMOSFETs

Abstract

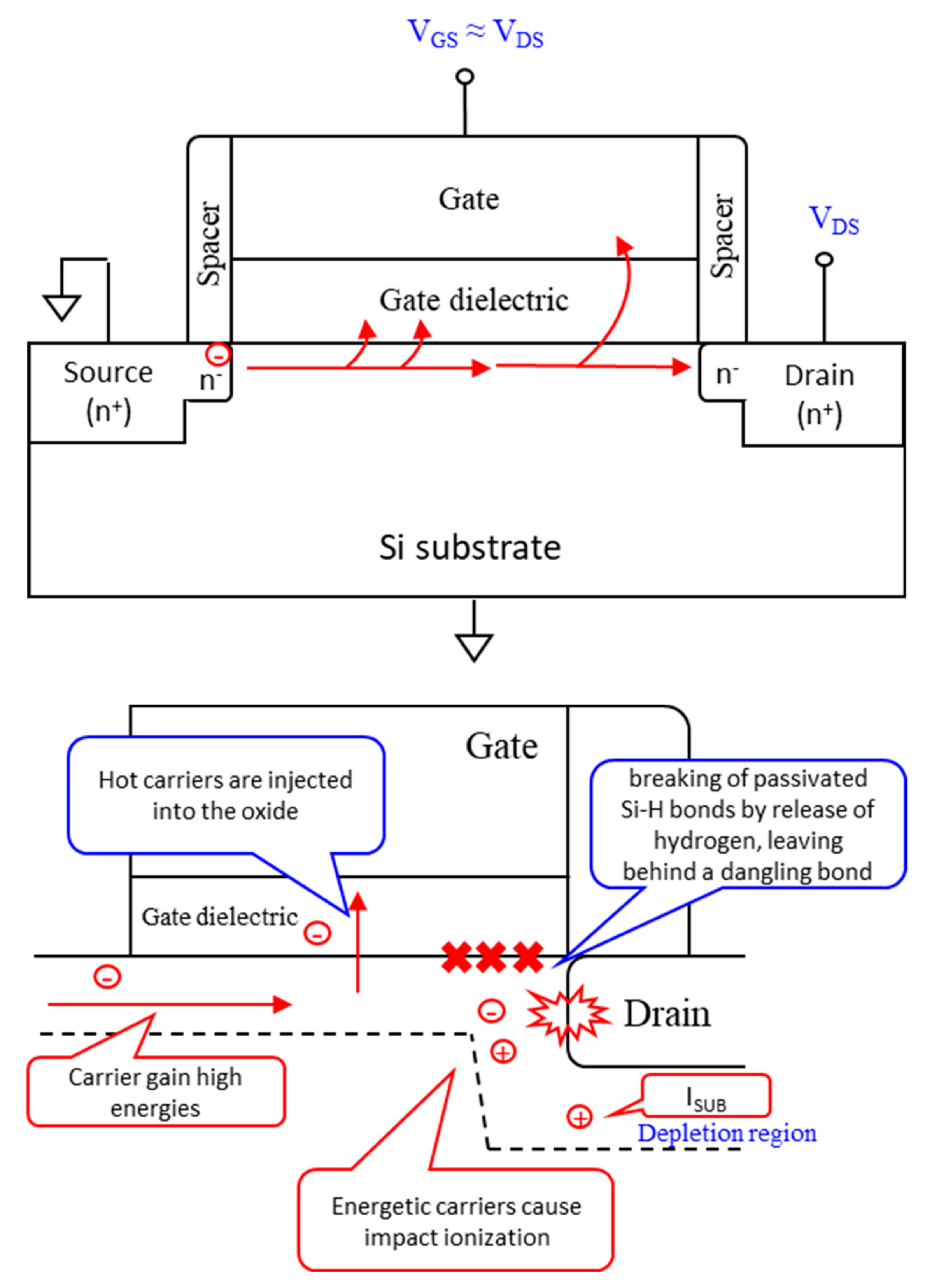

:1. Introduction

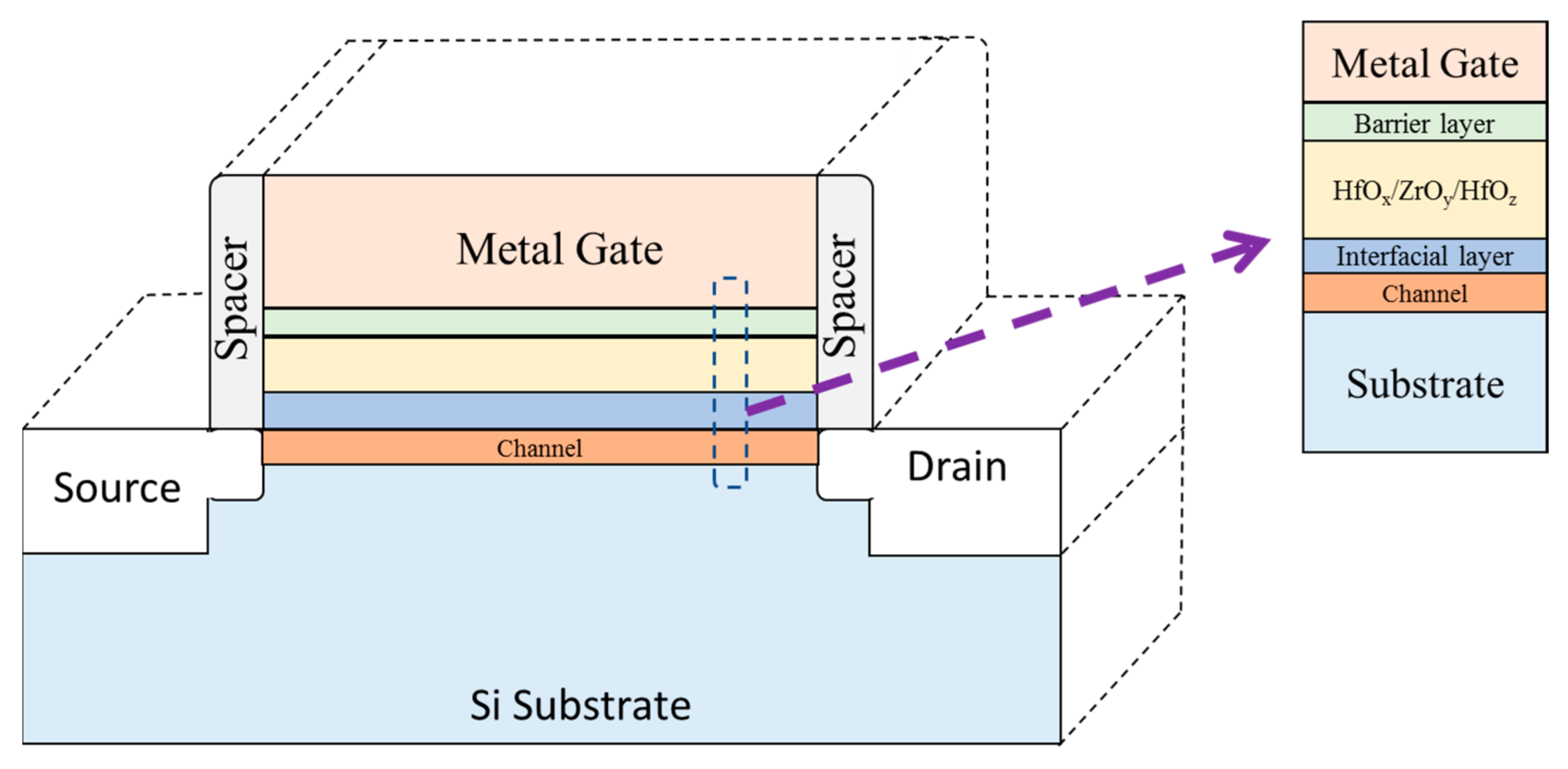

2. Concise Process Flow and Stress Conditions

3. Results and Discussion

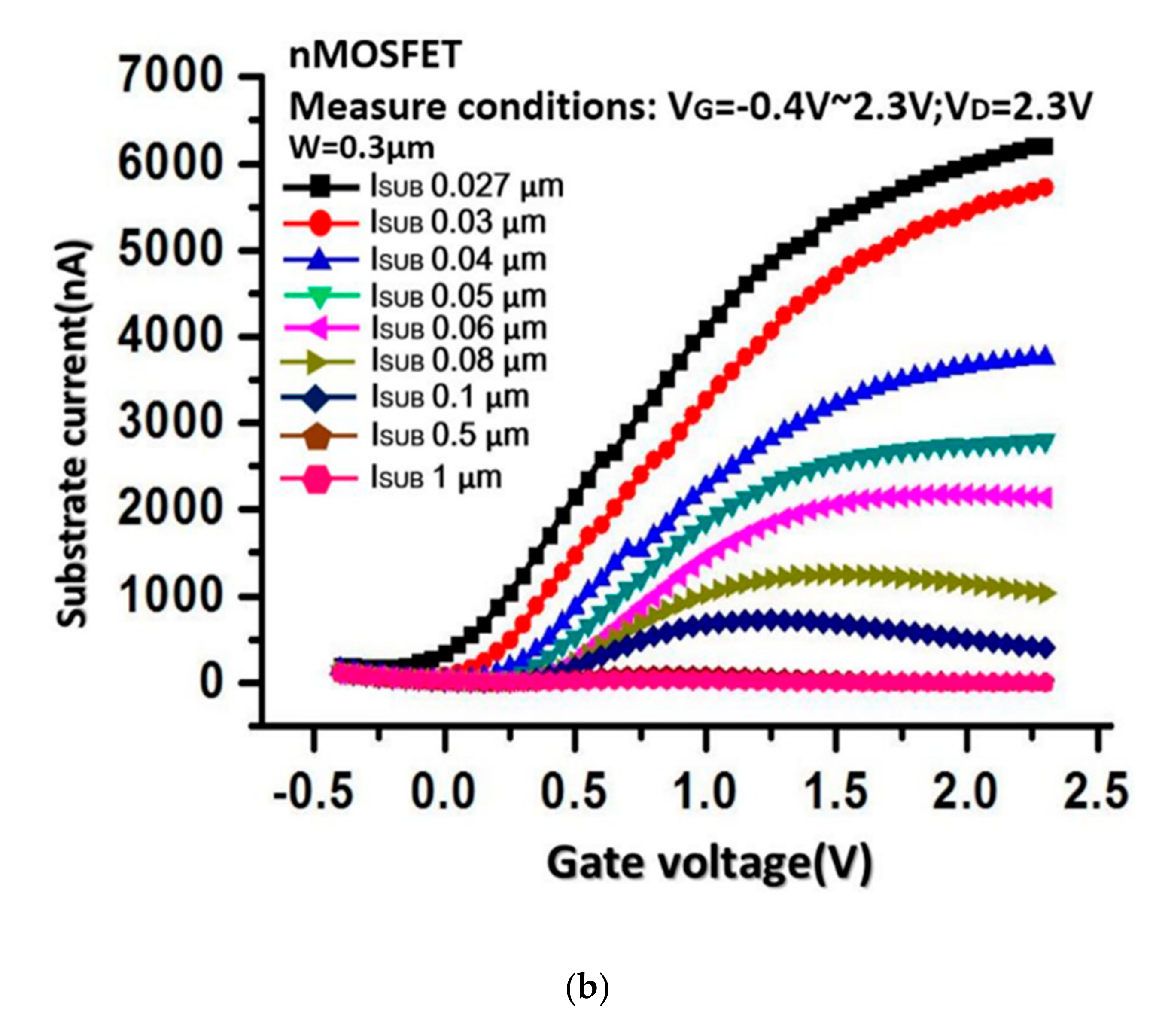

3.1. The Relationship between the Channel Length and ISUB

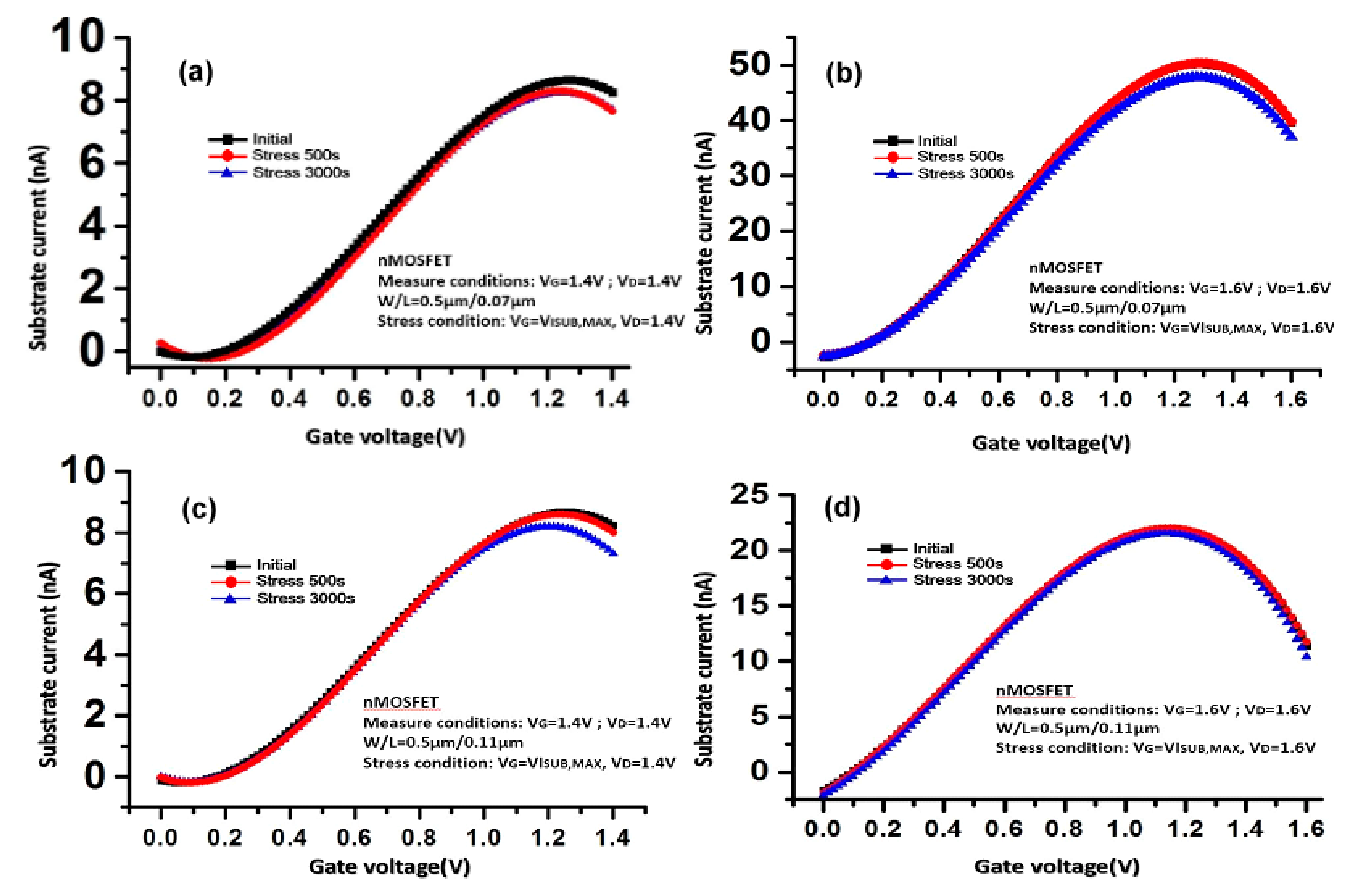

3.2. ISUB and VT Degradation after HC Stresses

3.3. HC Lifetime Model for n-MOSFETs

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Abbreviations

| Tox | Thickness of oxide |

| CADDET | Computer-Aided Device Design in Two Dimensions |

| R-D | Recombination-Diffusion |

| SDE | Source/Drain Extension |

| LEM | Lucky Electron Model |

| BTI | Bias Temperature Instability |

| EOT | Equivalent Oxide Thickness |

References

- Taur, Y.; Ning, T.H. CMOS Performance Factors. In Fundamentals of Modern VLSI Devices; University Press: Cambridge, UK, 2018; pp. 256–317. [Google Scholar]

- Pearce, C.W.; Yaney, D.S. Short-channel effects in MOSFET’s. IEEE Electron Dev. Lett. 1985, 6, 326–328. [Google Scholar] [CrossRef]

- Childs, P.; Leung, C. New mechanism of hot carrier generation in very short channel MOSFETs. Electron. Lett. 1995, 31, 139–141. [Google Scholar] [CrossRef]

- Joly, Y.; Lopez, L.; Portal, J.M.; Aziza, H.; Ogier, J.L.; Bert, Y.; Julien, F.; Fornara, P. Matching degradation of threshold voltage and gate voltage of NMOSFET after Hot Carrier Injection stress. Microelectron. Reliab. 2011, 51, 1561–1563. [Google Scholar] [CrossRef]

- Tam, S.; Ko, P.K.; Hu, C. Lucky-electron model of channel hot-electron injection in MOSFET’s. IEEE Trans. Electron Dev. 1984, 31, 1116–1125. [Google Scholar]

- Takeda, E. Hot-carrier effects in scaled MOS devices. Microelectron. Reliab. 1993, 33, 1687–1711. [Google Scholar] [CrossRef]

- Yu, B.; Wann, C.H.J.; Nowak, E.D.; Noda, K.; Hu, C. Short-channel effect improved by lateral channel-engineering in deep-submicronmeter MOSFET’s. IEEE Trans. Electron Dev. 1997, 44, 627–634. [Google Scholar]

- Takeda, E.; Nakagome, Y.; Kume, H.; Asai, S. New hot-carrier injection and device degradation in submicron MOSFETs. IEEE Proc. I Solid State Electron Devices 1983, 130, 144. [Google Scholar] [CrossRef]

- Abramo, A.; Fiegna, C.; Venturi, F. Hot Carrier Effects in Short MOSFETs at Low Applied Voltages; Institute of Electrical and Electronics Engineers (IEEE): Piscataway, NJ, USA, 2002. [Google Scholar]

- la Rosa, G.; Rauch, S.E. Channel hot carrier effects in n-MOSFET devices of advanced submicron CMOS technologies. Microelectron. Reliab. 2007, 47, 552–558. [Google Scholar] [CrossRef]

- Mahapatra, S.; Sharma, U. A Review of Hot Carrier Degradation in n-Channel MOSFETs—Part I: Physical Mechanism. IEEE Trans. Electron Devices 2020, 67, 2660–2671. [Google Scholar] [CrossRef]

- Mahapatra, S.; Sharma, U. A Review of Hot Carrier Degradation in n-Channel MOSFETs—Part II: Technology Scaling. IEEE Trans. Electron Devices 2020, 67, 2672–2681. [Google Scholar] [CrossRef]

- Amat, E.; Kauerauf, T.; Degraeve, R.; de Keersgieter, A.; Rodriguez, R.; Nafria, M.; Aymerich, X.; Groeseneken, G. Channel Hot-Carrier Degradation in Short-Channel Transistors With High- kk/Metal Gate Stacks. IEEE Trans. Device Mater. Reliab. 2009, 9, 425–430. [Google Scholar] [CrossRef]

- Pagey, M.P. Hot-carrier reliability simulation in aggressively scaled MOS transistors. Ph.D. Thesis, Vanderbilt University, Nashville, TN, USA, 2003. [Google Scholar]

- Hofmann, K.R.; Werner, C.; Weber, W.; Dorda, G. Hot-electron and hole-emission effects in short n-channel MOSFET’s. IEEE Trans. Electron Dev. 1985, 32, 691–699. [Google Scholar] [CrossRef]

- Koike, N.; Tatsuuma, K. A Drain Avalanche Hot Carrier Lifetime Model for n- and p-Channel MOSFETs. IEEE Trans. Device Mater. Reliab. 2004, 4, 457–466. [Google Scholar] [CrossRef]

- Acovic, A.; la Rosa, G.; Sun, Y.C. A review of hot-carrier degradation mechanisms in MOSFETs. Microelectron. Reliab. 1996, 36, 845–869. [Google Scholar] [CrossRef]

- Kim, H.D.; Roh, Y.; Lee, J.E. Characteristics of high-k gate dielectric formed by the oxidation of sputtered Hf/Zr/Hf thin films on the Si substrate. J. Vac. Sci. Tech. 2004, 22, 1342–1346. [Google Scholar] [CrossRef]

- Wong, H. The Current Conduction Issues in High-k Gate Dielectrics; Institute of Electrical and Electronics Engineers (IEEE): Piscataway, NJ, USA, 2007; pp. 31–36. [Google Scholar]

- Wong, H.; Iwai, H. On the scaling issues and high-k replacement of ultrathin gate dielectrics for nanoscale MOS transistors. Microelectron Eng. 2006, 83, 1867–1904. [Google Scholar] [CrossRef]

- Wang, S.J.; Sung, S.P.; Wang, M.C.; Huang, H.S.; Chen, S.Y.; Fan, S.K.; Wang, S.J.; Sung, S.P.; Wang, M.C.; Huang, H.S.; et al. Electrical stress probing recovery efficiency of 28 nm HK/MG nMOSFETs using decoupled plasma nitridation treatment. Vacuum 2018, 153, 117–121. [Google Scholar] [CrossRef]

- Amat, E.; Kauerauf, T.; Rodriguez, R.; Nafria, M.; Aymerich, X.; Degraeve, R.; Groeseneken, G. A comprehensive study of channel hot-carrier degradation in short channel MOSFETs with high-k dielectrics. Microelectron. Eng. 2013, 103, 144–149. [Google Scholar] [CrossRef]

- Pfäffli, P.; Tikhomirov, P.; Xu, X.; Avci, I.; Oh, Y.S.; Balasingam, P.; Krishnamoorthy, S.; Ma, T.; Avcı, I. TCAD for reliability. Microelectron. Reliab. 2012, 52, 1761–1768. [Google Scholar] [CrossRef]

- Macaleoni, A.; Villa, C.M.; Medda, M. Emerging challenges for a built-in reliability in innovative Automotive ICs. In Proceedings of the ESREF 2018, Aalborg, Denmark, 1–5 October 2018. [Google Scholar]

- Han, C.; Shi, X.; Huang, Q. Optimization of short channel effect and external resistance on small size FinFET for different threshold voltage flavors and supply voltages. Microelectron. J. 2019, 85, 1–5. [Google Scholar] [CrossRef]

- Tsai, C.H.; Yang, C.W.; Hsu, C.H.; Lai, C.M.; Lo, K.Y.; Chen, C.G.; Huang, R.M.; Tsai, C.T.; Hung, L.S.; You, J.W.; et al. Characteristics of HfZrOx Gate Stack Engineering forR Improvement on 28nm HK/MG CMOS Technology; Institute of Electrical and Electronics Engineers (IEEE): Piscataway, NJ, USA, 2012; pp. 1–2. [Google Scholar]

- Hegde, R.I.; Triyoso, D.H.; Samavedam, S.B.; White, B.E. Hafnium zirconate gate dielectric for advanced gate stack applications. J. Appl. Phys. 2007, 101, 74113. [Google Scholar] [CrossRef]

- Chung, S.; Yeh, C.H.; Feng, H.J.; Lai, C.S.; Yang, J.J.; Chen, C.C.; Jin, Y.; Chen, S.; Liang, M.-S. Impact of STI on the Reliability of Narrow-Width pMOSFETs With Advanced ALD N/O Gate Stack. IEEE Trans. Device Mater. Reliab. 2006, 6, 95–101. [Google Scholar] [CrossRef]

- Chiang, C.K.; Chang, J.C.; Liu, W.H.; Liu, C.C.; Lin, J.F.; Yang, C.L.; Wu, J.Y.; Wang, S.J. Investigation of the Structural and Electrical Characterization on ZrO2 Addition for ALD HfO2 with La2O3 Capping Layer Integrated Metal-oxide Semiconductor Capacitors; Institute of Electrical and Electronics Engineers (IEEE): Piscataway, NJ, USA, 2011; pp. 1–4. [Google Scholar]

- Cartier, E.; Ando, T.; Hopstaken, M.; Narayanan, V.; Krishnan, R.; Shepard, J.F.; Sullivan, M.D.; Krishnan, S.; Chudzik, M.P.; De, S.; et al. Characterization and Optimization of Charge Trapping in High-k Dielectrics; Institute of Electrical and Electronics Engineers (IEEE): Piscataway, NJ, USA, 2013; pp. 5A.2.1–5A.2.7. [Google Scholar]

- Zhao, L.; Su, J.C.; Zhang, X.B.; Pan, Y.F.; Wang, L.M.; Sun, X.; Li, R. Research on Reliability and Lifetime of Solid Insulation Structures in Pulsed Power Systems. IEEE Trans. Plasma Sci. 2012, 41, 165–172. [Google Scholar] [CrossRef]

- Tu, C.H.; Chen, S.Y.; Lin, M.H.; Wang, M.C.; Wu, S.H.; Chou, S.; Ko, J.; Huang, H.S. The switch of the worst case on NBTI and hot-carrier reliability for 0.13μm pMOSFETs. Appl. Surf. Sci. 2008, 254, 6186–6189. [Google Scholar] [CrossRef]

- Auth, C.; Cappellani, A.; Chun, J.S.; Dalis, A. 45nm High-k + metal gate strain-enhanced transistors. In Proceedings of the VLSI Technology Symposium, Honolulu, HI, USA, 17–19 June 2008. [Google Scholar]

- Kim, N.; Lee, S.; Kim, C.; Lee, C.; Park, J.; Kang, B. Enhanced degradation of n-MOSFETs with high-k/metal gate stacks under channel hot-carrier/gate-induced drain leakage alternating stress. Microelectron. Reliab. 2012, 52, 1901–1904. [Google Scholar] [CrossRef]

- Chung, J.; Moon, J.; Ko, P.K.; Hu, C.; Jeng, M.C. Low-voltage hot-electron currents and degradation in deep-submicrometer MOSFETs. IEEE Trans. Electron Devices 1990, 37, 1651–1657. [Google Scholar] [CrossRef] [Green Version]

- Tam, S.; Hsu, F.C.; Hu, C.; Muller, R.S. Hot-electron currents in very short channel MOSFET’s. IEEE Electron Dev. Lett. 1983, 4, 249–251. [Google Scholar] [CrossRef]

- Huang, H.S.; Wang, W.L.; Wang, M.C.; Chao, Y.H.; Wang, S.J.; Chen, S.Y. I-V model of nano nMOSFETs incorporating drift and diffusion current. Vacuum 2018, 155, 76–82. [Google Scholar] [CrossRef]

- Robertson, J. Electronic Structure and Band Offsets of High-Dielectric-Constant Gate Oxides. MRS Bull. 2002, 27, 217–221. [Google Scholar] [CrossRef]

- Wang, S.J.; Wang, M.C.; Der Lee, W.; Chen, W.S.; Huang, H.S.; Chen, S.-Y.; Huang, L.; Liu, C.H. Kink effect for 28 nm n-channel field-effect transistors after decoupled plasma nitridation treatment with annealing temperatures. Int. J. Nanotechnol. 2015, 12, 59. [Google Scholar] [CrossRef]

- Chou, C.C.; Shen, T.S.; Chen, J.M.; Chang, C.H.T.; Wang, S.J.; Lan, W.H.; Wang, M.C. Uniformity of Gate Dielectric for I/O and Core HK/MG pMOSFETs with Nitridation Treatments. J. Electron. Mater. 2020, 49, 1–12. [Google Scholar] [CrossRef]

- Sangiorgi, E.; Ricco, B.; Olivo, P. Hot electrons and holes in MOSFET’s biased below the Si-SiO2 interfacial barrier. IEEE Electron Dev. Lett. 1985, 6, 513–515. [Google Scholar] [CrossRef]

- Bude, J.; Iizuka, T.; Kamakura, Y. Determination of Threshold Energy for Hot Electron Interface State Generation; Institute of Electrical and Electronics Engineers (IEEE): Piscataway, NJ, USA, 2002; pp. 865–868. [Google Scholar]

- Duhan, P.; Rao, V.R.; Mohapatra, N.R. Effect of Device Dimensions, Layout and Pre-Gate Carbon Implant on Hot Carrier Induced Degradation in HKMG nMOS Transistors. IEEE Trans. Device Mater. Reliab. 2020, 20, 555–561. [Google Scholar] [CrossRef]

- Choudhury, N.; Parihar, N.; Mahapatra, S. Analysis of The Hole Trapping Detrapping Component of NBTI over Extended Temperature Range; Institute of Electrical and Electronics Engineers (IEEE): Piscataway, NJ, USA, 2020; pp. 1–5. [Google Scholar]

| Reference | Purpose | Stress Method | Specifications |

|---|---|---|---|

| Takeda et al. [7] | Probing the DAHC injection and the substrate current-induced hot-electron injection (SCHE) under submicron process with gate dioxide. | DAHC and SCHE |

|

| Abramo et al. [8] | Using a Monte Carlo simulator to quantify the electron energy distribution in Si devices at low applied voltages involving the process of carrier heating. | DAHC |

|

| Yu et al. [9] | Exposing the hot-carrier effect related to the channel implantation process influencing the normal and reverse short-channel effect LDD MOSFETs down to 0.1 μm. | CHC |

|

| La Rosa et al. [10] | Reviewing the CHC mechanism and its effects on n-MOSFETs of deep submicron CMOS bulk technologies guided into the carrier dominant energy. | CHC |

|

| Mahapatra et al. [11] | Reviewing the physical mechanisms of transistor parameter shift due to hot-carrier degradation (HCD) in n-MOSFETs. | CHC and DAHC |

|

| Mahapatra et al. [12] | Reviewing the technology scaling including the stress temperature and performing the comparison of dc and ac stress | CHC under dc and ac stress |

|

| Acovic et al. [17] | Reviewing the hot-carrier effects and reliability problem in MOSFET | DAHC and ac stress |

|

| Amat et al. [22] | Presenting a comprehensive study on CHC degradation in short-channel MOSFETs with high-k dielectric | CHC and ac stress |

|

| This work | Studying the degradation mechanisms of substrate current for high-k MOSFETs after HC stresses and exposing the change mechanisms of values of the acceleration factor in lifetime calculation | CHC and DAHC |

|

| Variable | Parameters Setup |

|---|---|

| Device width (µm) | 0.3 |

| Vcc (V) | 0.8 |

| Dimension (µm) | 0.027, 0.03, 0.04, 0.05, 0.06, 0.08, 0.1, 0.5, 1 |

| Stress conditions | VGS = −0.4 – 2.3 V; VDS = 2.3 V |

| Temperature (°C) | 25 |

| Variable | Parameters Setup | |

|---|---|---|

| Device width (µm) | 0.5 | |

| Vcc (V) | 0.8 | |

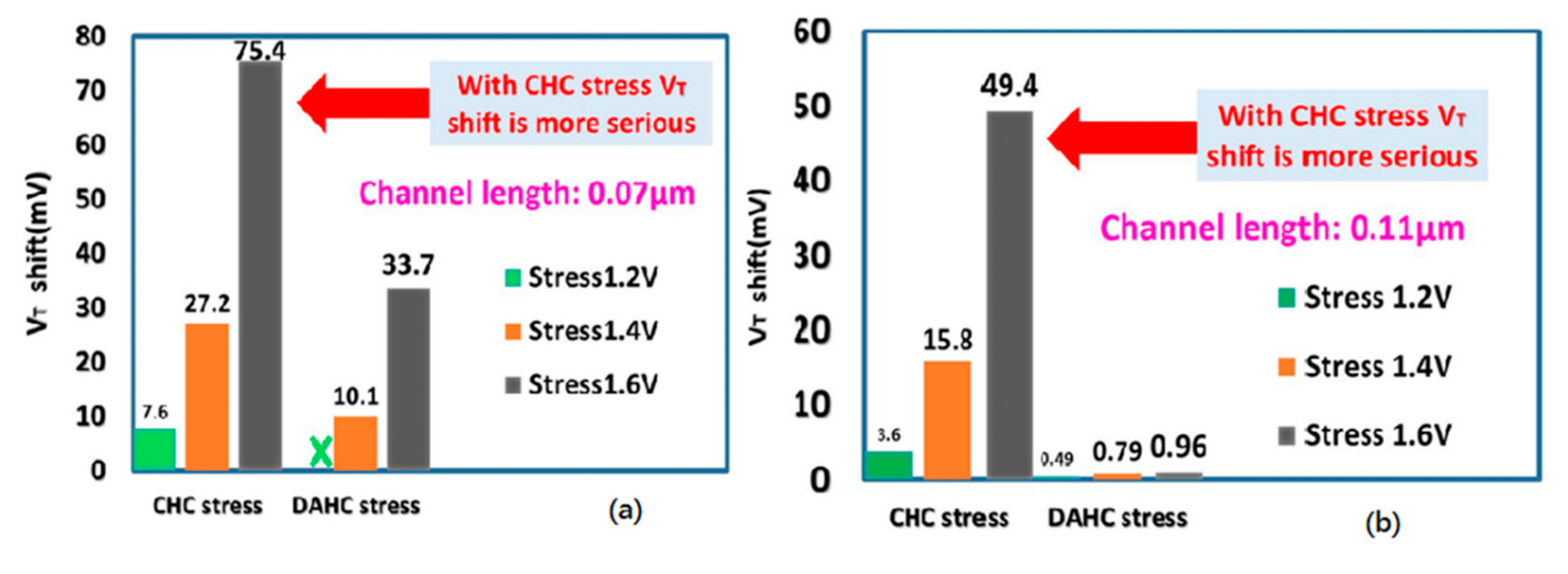

| Stress mode | CHC | DAHC |

| Dimension (µm) | 0.03, 0.07, 0.11 | |

| Vstress | VGS = VDS = 1.2 V, 1.4 V, 1.6 V | VGS at ISUB, max; VDS = 1.2, 1.4, 1.6 V |

| Temperature (°C) | 25 | |

| Threshold Voltage (VT) | Constant current method to extract VT values, VT, lin = VGS at IDS = 300 nA × W/L, VDS = 0.1 V, VB = VS = 0 V | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, C.-W.; Wang, M.-C.; Chang, C.-H.-T.; Chu, W.-L.; Sung, S.-P.; Lan, W.-H. Hot Carrier Stress Sensing Bulk Current for 28 nm Stacked High-k nMOSFETs. Electronics 2020, 9, 2095. https://doi.org/10.3390/electronics9122095

Chen C-W, Wang M-C, Chang C-H-T, Chu W-L, Sung S-P, Lan W-H. Hot Carrier Stress Sensing Bulk Current for 28 nm Stacked High-k nMOSFETs. Electronics. 2020; 9(12):2095. https://doi.org/10.3390/electronics9122095

Chicago/Turabian StyleChen, Chii-Wen, Mu-Chun Wang, Cheng-Hsun-Tony Chang, Wei-Lun Chu, Shun-Ping Sung, and Wen-How Lan. 2020. "Hot Carrier Stress Sensing Bulk Current for 28 nm Stacked High-k nMOSFETs" Electronics 9, no. 12: 2095. https://doi.org/10.3390/electronics9122095