Low Voltage Time-Based Matrix Multiplier-and-Accumulator for Neural Computing System

Abstract

:1. Introduction

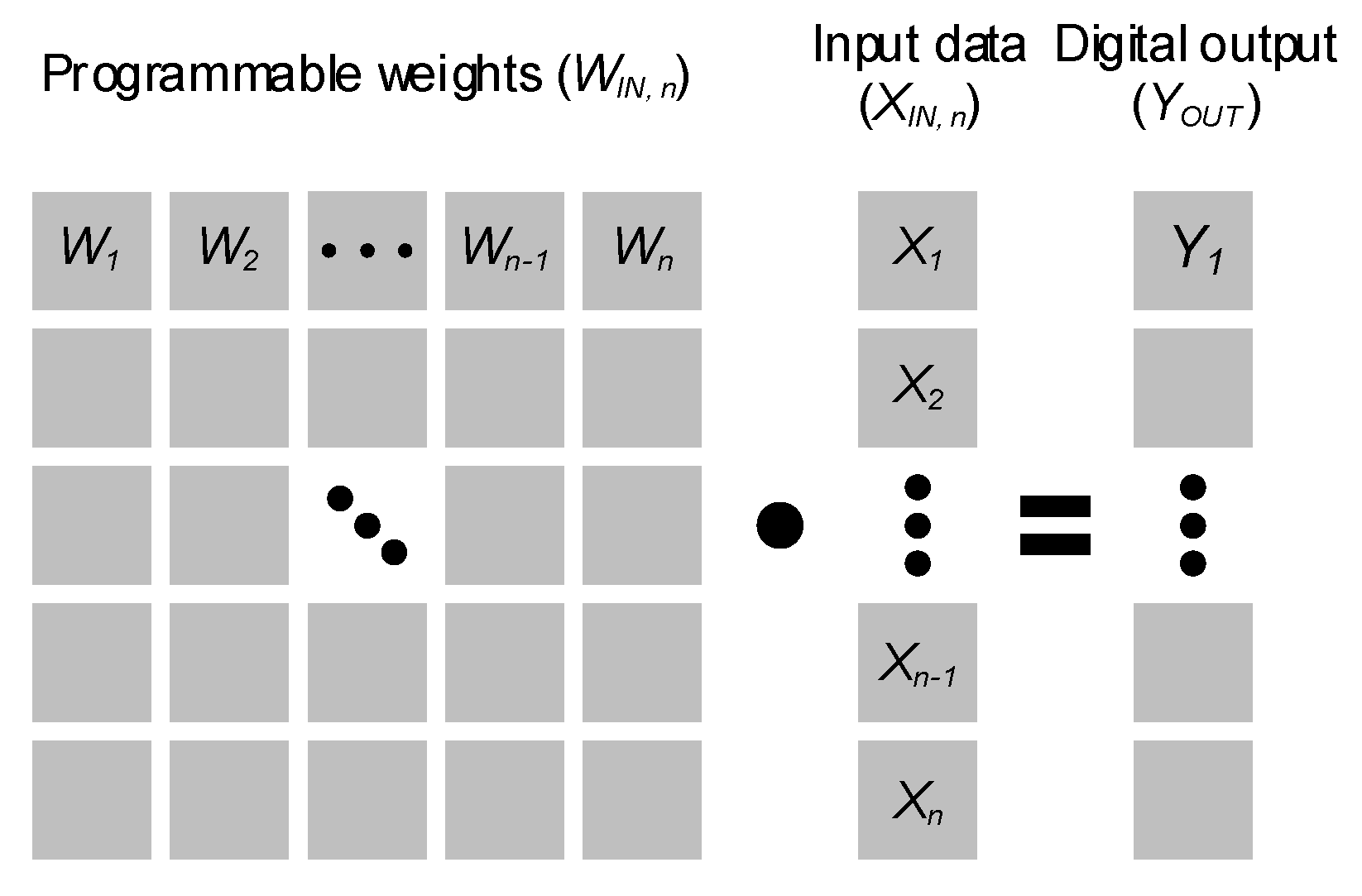

2. Time-Based Analog Multiplier

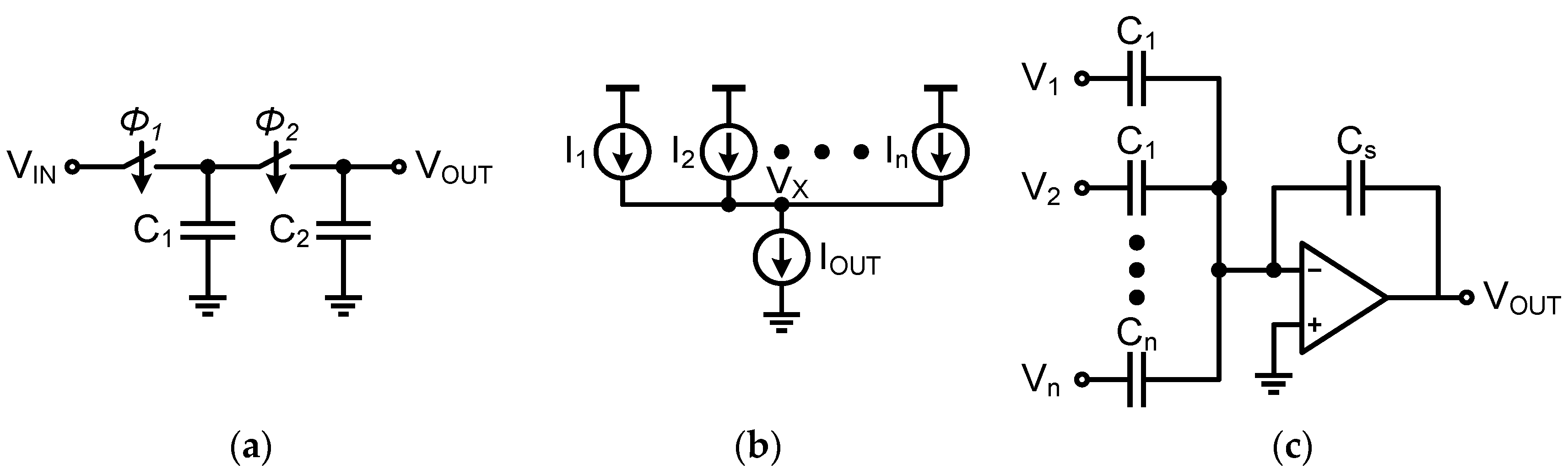

2.1. Conventional Analog Implementation

2.2. Proposed Time-Based Implementation

3. Circuit Implementation

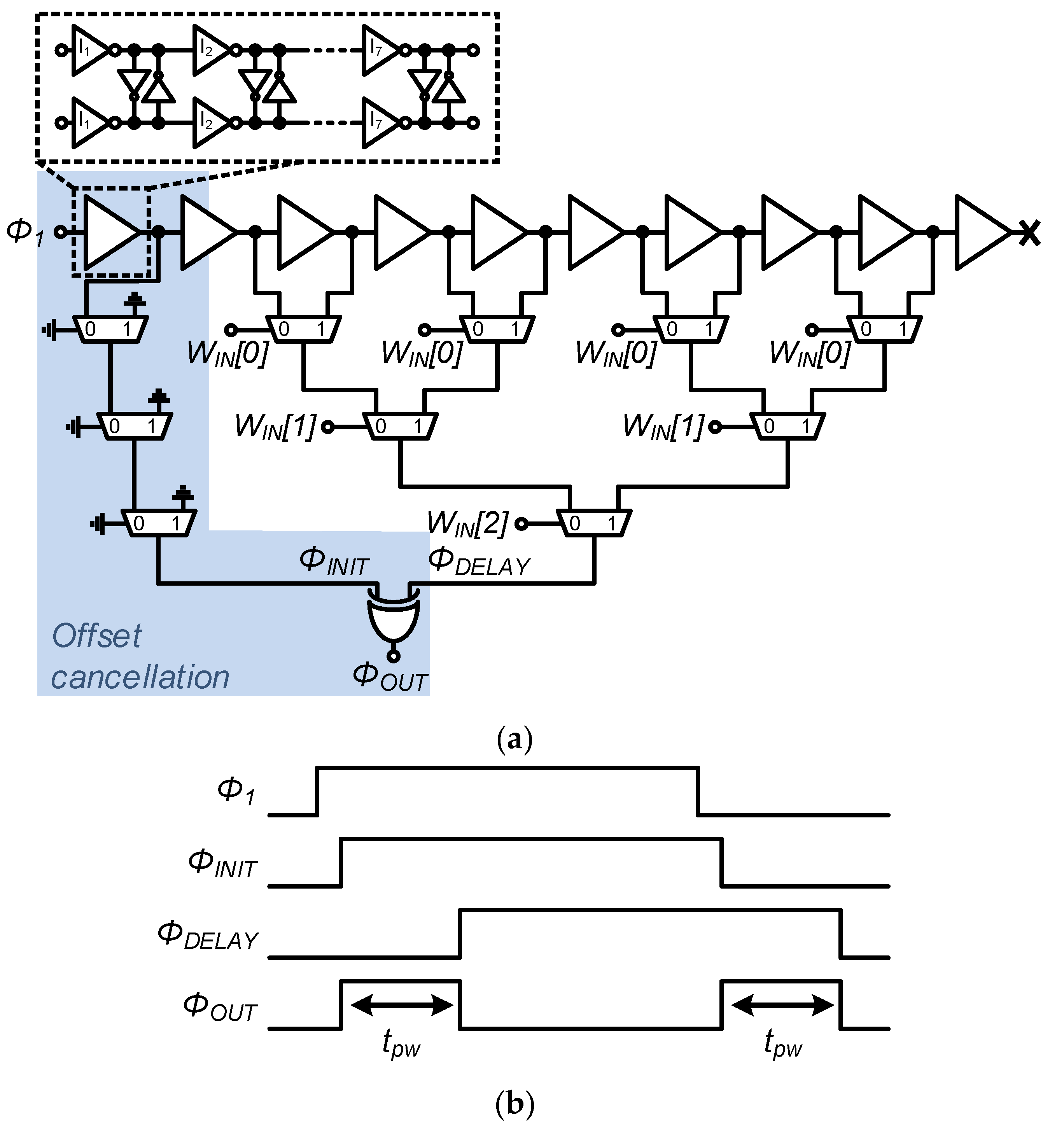

3.1. Proposed Offset-Free Pulse-Width Modulator

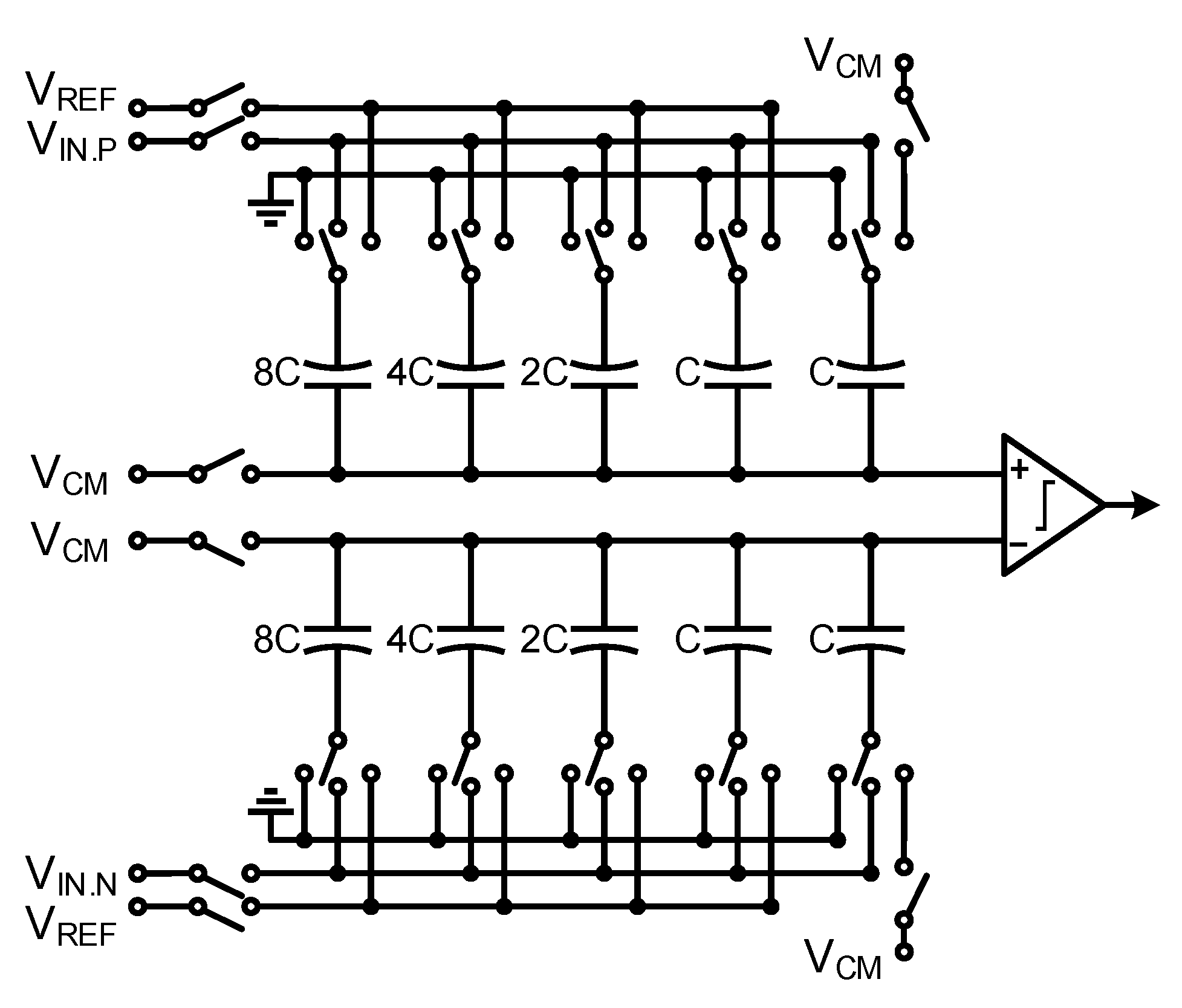

3.2. SAR ADC

3.3. Input Current DAC

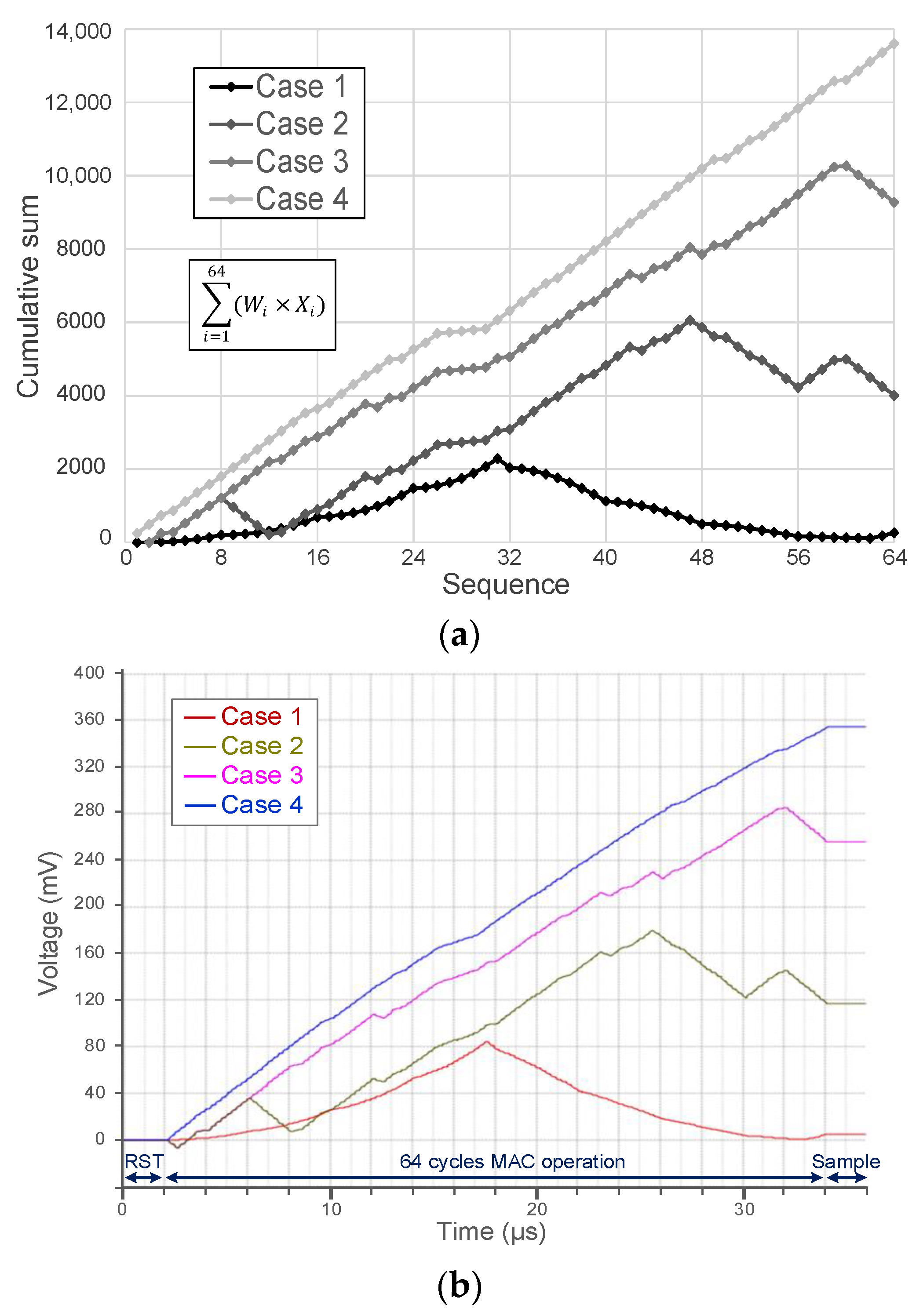

4. Simulation Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Sze, V.; Chen, Y.-H.; Emer, J.; Suleiman, A.; Zhang, Z. Hardware for machine learning: Challenges and opportunities. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 30 April–3 May 2017; pp. 1–8. [Google Scholar]

- Vanhoucke, V.; Senior, A.; Mao, M.Z. Improving the speed of neural networks on CPUs. In Proceedings of the Deep Learning and Unsupervised Feature Learning Workshop, NIPS, Granada, Spain, 16 December 2011. [Google Scholar]

- Lu, J.; Young, S.; Arel, I.; Holleman, J. A 1 TOPS/W Analog Deep Machine-Learning Engine With Floating-Gate Storage in 0.13 µm CMOS. IEEE J. Solid-State Circuits 2015, 50, 270–281. [Google Scholar] [CrossRef]

- Cisco Visual Networking Index (VNI) Complete Forecast Update. Available online: https://www.cisco.com (accessed on 1 January 2016).

- Woodhouse, J. Big, Big, Big Data: Higher and Higher Resolution Video Surveillance. Available online: http://technology.ihs.com (accessed on 1 January 2016).

- Szeliski, R. Computer Vision: Algorithms and Applications; Springer: London, UK, 2010. [Google Scholar]

- Seo, J.-S.; Brezzo, B.; Liu, Y.; Parker, B.D.; Esser, S.K.; Montoye, R.K.; Rajendran, B.; Tierno, J.A.; Chang, L.; Modha, D.S.; et al. A 45nm CMOS neuromorphic chip with a scalable architecture for learning in networks of spiking neurons. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 18–21 September 2011; pp. 1–4. [Google Scholar]

- Merolla, P.A.; Arthur, J.V.; Alvarez-Icaza, R.; Cassidy, A.S.; Sawada, J.; Akopyan, F.; Jackson, B.L.; Imam, N.; Guo, C.; Nakamura, Y.; et al. A million spiking-neuron integrated circuit with a scalable communication network and interface. Science 2014, 345, 668–673. [Google Scholar] [CrossRef] [PubMed]

- Zhang, J.; Wang, Z.; Verma, N. A matrix-multiplying ADC implementing a machine-learning classifier directly with data conversion. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 332–333. [Google Scholar]

- Lee, E.H.; Wong, S.S. Analysis and Design of a Passive Switched-Capacitor Matrix Multiplier for Approximate Computing. IEEE J. Solid-State Circuits 2016, 52, 261–271. [Google Scholar] [CrossRef]

- Rieutort-Louis, W.; Moy, T.; Wang, Z.; Wagner, S.; Sturm, J.C.; Verma, N. A Large-Area Image Sensing and Detection System Based on Embedded Thin-Film Classifiers. IEEE J. Solid-State Circuits 2015, 51, 281–290. [Google Scholar] [CrossRef]

- Wang, Z.; Zhang, J.; Verma, N. Realizing Low-Energy Classification Systems by Implementing Matrix Multiplication Directly Within an ADC. IEEE Trans. Biomed. Circuits Syst. 2015, 9, 1. [Google Scholar] [CrossRef] [PubMed]

- Price, M.; Glass, J.; Chandrakasan, A.P. A 6 mW, 5,000-Word Real-Time Speech Recognizer Using WFST Models. IEEE J. Solid-State Circuits 2014, 50, 102–112. [Google Scholar] [CrossRef]

- Yazdani, R.; Segura, A.; Arnau, J.-M.; Gonzalez, A. An ultra low-power hardware accelerator for automatic speech recognition. In Proceedings of the IEEE/ACM International Symposium on Microarchitecture (MICRO), Taipei, Taiwan, 15–19 October 2016; pp. 1–12. [Google Scholar]

- Verma, N.; Shoeb, A.; Guttag, J.V.; Chandrakasan, A.P. A micro-power EEG acquisition SoC with integrated seizure detection processor for continuous patient monitoring. In Proceedings of the IEEE Symposium on VLSI Circuits, Kyoto, Japan, 16–18 June 2009; pp. 62–63. [Google Scholar]

- Chen, T.-C.; Lee, T.-H.; Chen, Y.-H.; Ma, T.-C.; Chuang, T.-D.; Chou, C.-J.; Yang, C.-H.; Lin, T.-H.; Chen, L.-G. 1.4µW/channel 16-channel EEG/ECoG processor for smart brain sensor SoC. In Proceedings of the IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 16–18 June 2010; pp. 21–22. [Google Scholar]

- Lee, K.H.; Verma, N. A Low-Power Processor with Configurable Embedded Machine-Learning Accelerators for High-Order and Adaptive Analysis of Medical-Sensor Signals. IEEE J. Solid-State Circuits 2013, 48, 1625–1637. [Google Scholar] [CrossRef]

- Bin, A.M.; Yoo, J. A 1.83 μJ/classification, 8-channel, patient-specific epileptic seizure classification SoC using a non-linear support vector machine. IEEE Trans. Biomed. Circuits Syst. 2016, 10, 49–60. [Google Scholar]

- Ebong, I.E.; Mazumder, P. CMOS and Memristor-Based Neural Network Design for Position Detection. Proc. IEEE 2011, 100, 2050–2060. [Google Scholar] [CrossRef]

- Skrzyniarz, S.; Fick, L.; Shah, J.; Kim, Y.; Sylvester, D.; Blaauw, D.; Fick, D.; Henry, M.B. A 36.8 2b-TOPS/W self-calibrating GPS accelerator implemented using analog calculation in 65nm LP CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 420–422. [Google Scholar]

- Bankman, D.; Murmann, B. Passive charge redistribution digital-to-analogue multiplier. Electron. Lett. 2015, 51, 386–388. [Google Scholar] [CrossRef]

- Joshi, S.; Kim, C.; Ha, S.; Chi, Y.M.; Cauwenberghs, G. 2pJ/MAC 14b 8×8 linear transform mixed-signal spatial filter in 65nm CMOS with 84dB interference suppression. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 364–365. [Google Scholar]

- Miyashita, D.; Kousai, S.; Suzuki, T.; Deguchi, J. A Neuromorphic Chip Optimized for Deep Learning and CMOS Technology With Time-Domain Analog and Digital Mixed-Signal Processing. IEEE J. Solid-State Circuits 2017, 52, 2679–2689. [Google Scholar] [CrossRef]

- Everson, L.; Liu, M.; Pande, N.; Kim, C.H. An Energy-Efficient One-Shot Time-Based Neural Network Accelerator Employing Dynamic Threshold Error Correction in 65 nm. IEEE J. Solid-State Circuits 2019, 54, 2777–2785. [Google Scholar] [CrossRef]

- Gilbert, B. Translinear circuits: An historical overview. Analog. Integr. Circuits Signal Process. 1996, 9, 95–118. [Google Scholar] [CrossRef]

- Vittoz, E.; Fellrath, J. CMOS analog integrated circuits based on weak inversion operations. IEEE J. Solid-State Circuits 1977, 12, 224–231. [Google Scholar] [CrossRef] [Green Version]

| Expected Scaled Output | ADC Output | Error | |

|---|---|---|---|

| Case 1 | 0.39 | 0 | +0.39 |

| Case 2 | 5.94 | 7 | −1.06 |

| Case 3 | 13.74 | 15 | −1.26 |

| Case 4 | 20.16 | 21 | −0.84 |

| Process | Domain | Supply Voltage | Weighted Multiplier | Accumulator | |

|---|---|---|---|---|---|

| [10] | 40 nm | Analog | 1.1 V | Switched-capacitor multiplier with variable capacitor ratio | Charge accumulation |

| [9] | 130 nm | Analog | 1.2 V | Multiplying ADC with variable capacitor ratio | Digital adder by S/W |

| [22] | 65 nm | Analog | 1.2 V | Multiplying DAC with variable capacitor ratio | Digitally controlled VGA |

| [23] | 65 nm | Time | 1 V | Variable delay cell | Sequentially added multiplier units |

| [24] | 65 nm | Time | 0.7–1.4 V | Variable delay cell with calibration | Sequentially added multiplier units |

| This work | 32 nm | Time | 0.5 V | Variable delay cell with offset-free structure | Charge accumulation |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hong, S.; Kang, H.; Kim, J.; Cho, K. Low Voltage Time-Based Matrix Multiplier-and-Accumulator for Neural Computing System. Electronics 2020, 9, 2138. https://doi.org/10.3390/electronics9122138

Hong S, Kang H, Kim J, Cho K. Low Voltage Time-Based Matrix Multiplier-and-Accumulator for Neural Computing System. Electronics. 2020; 9(12):2138. https://doi.org/10.3390/electronics9122138

Chicago/Turabian StyleHong, Sungjin, Heechai Kang, Jusung Kim, and Kunhee Cho. 2020. "Low Voltage Time-Based Matrix Multiplier-and-Accumulator for Neural Computing System" Electronics 9, no. 12: 2138. https://doi.org/10.3390/electronics9122138