A Novel General Purpose Combined DFVF/VCII Based Biomedical Amplifier

Abstract

:1. Introduction

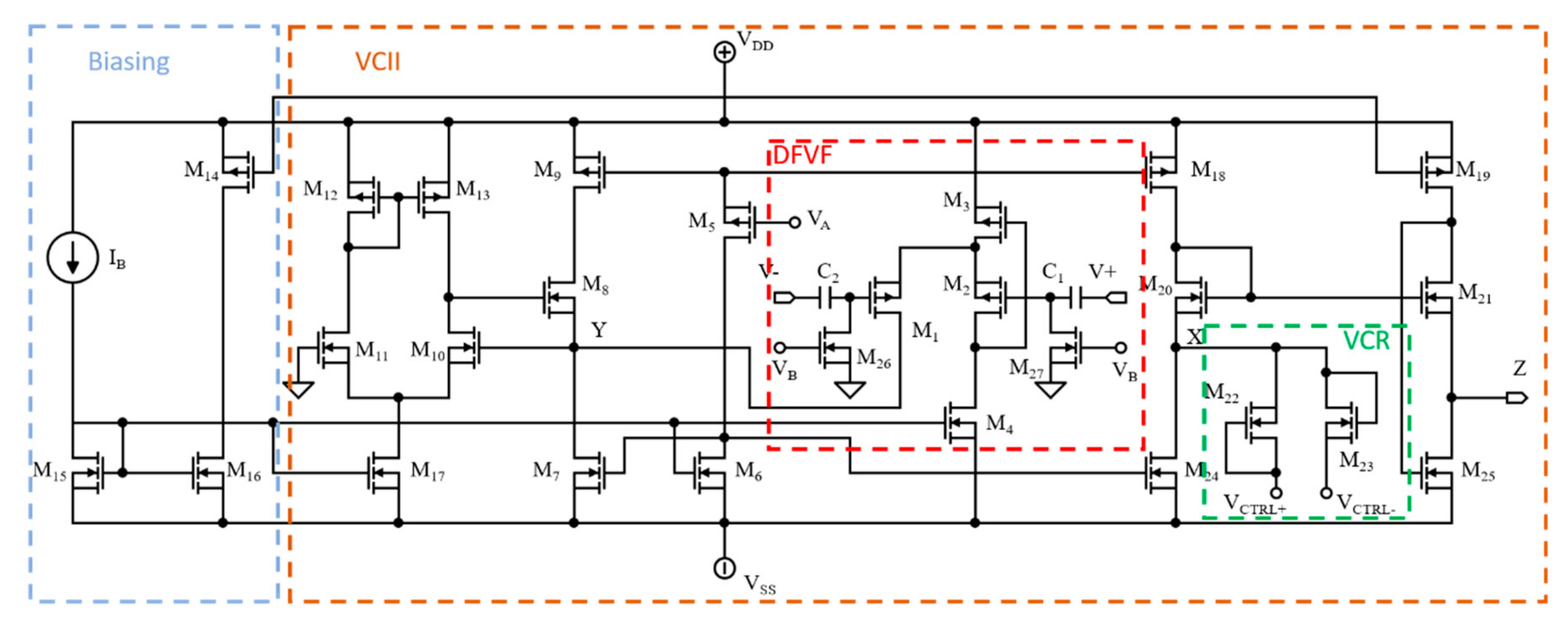

2. Flipped Voltage Follower and Second-Generation Voltage Conveyor Short Overview

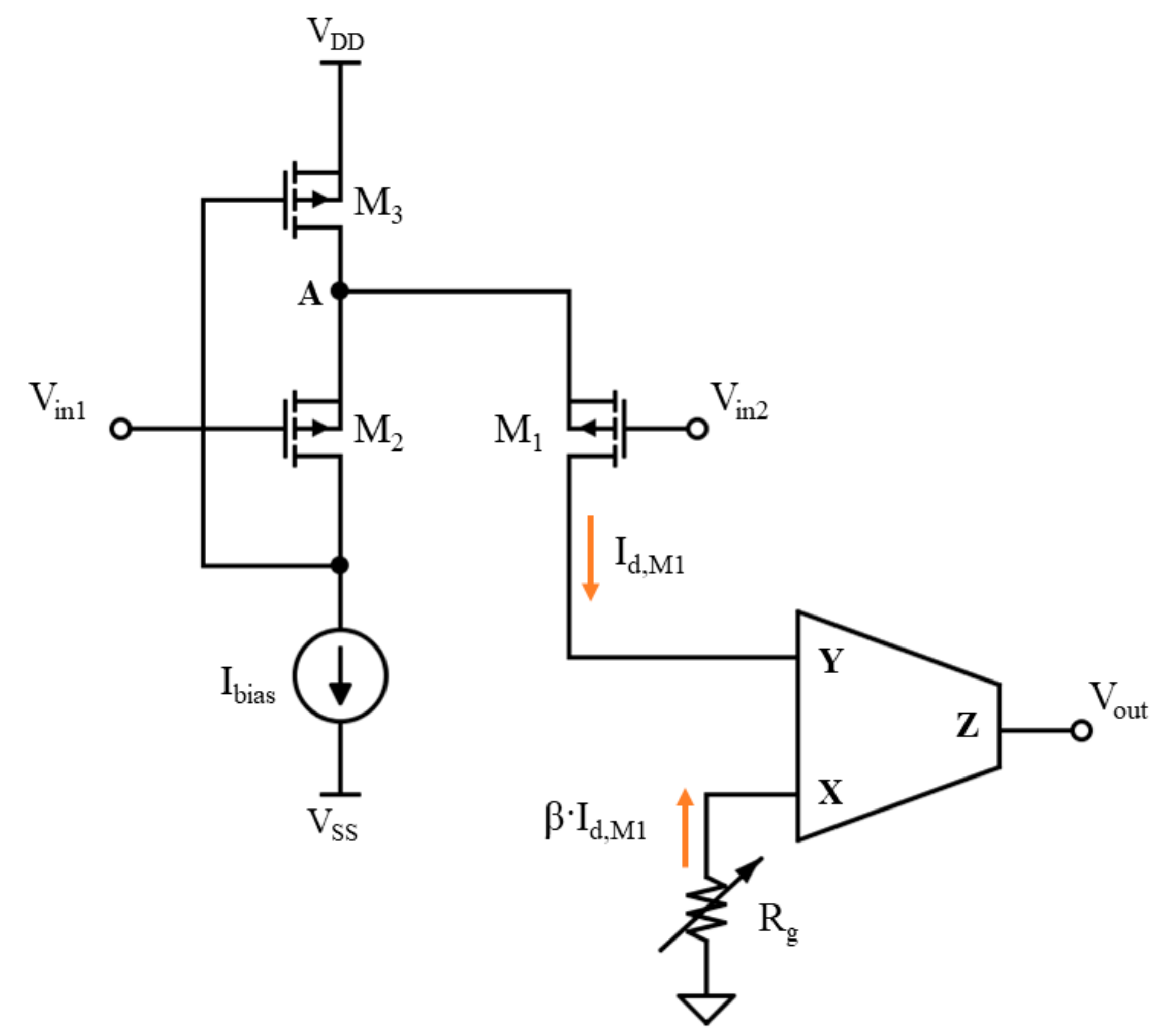

2.1. The Flipped Voltage Follower

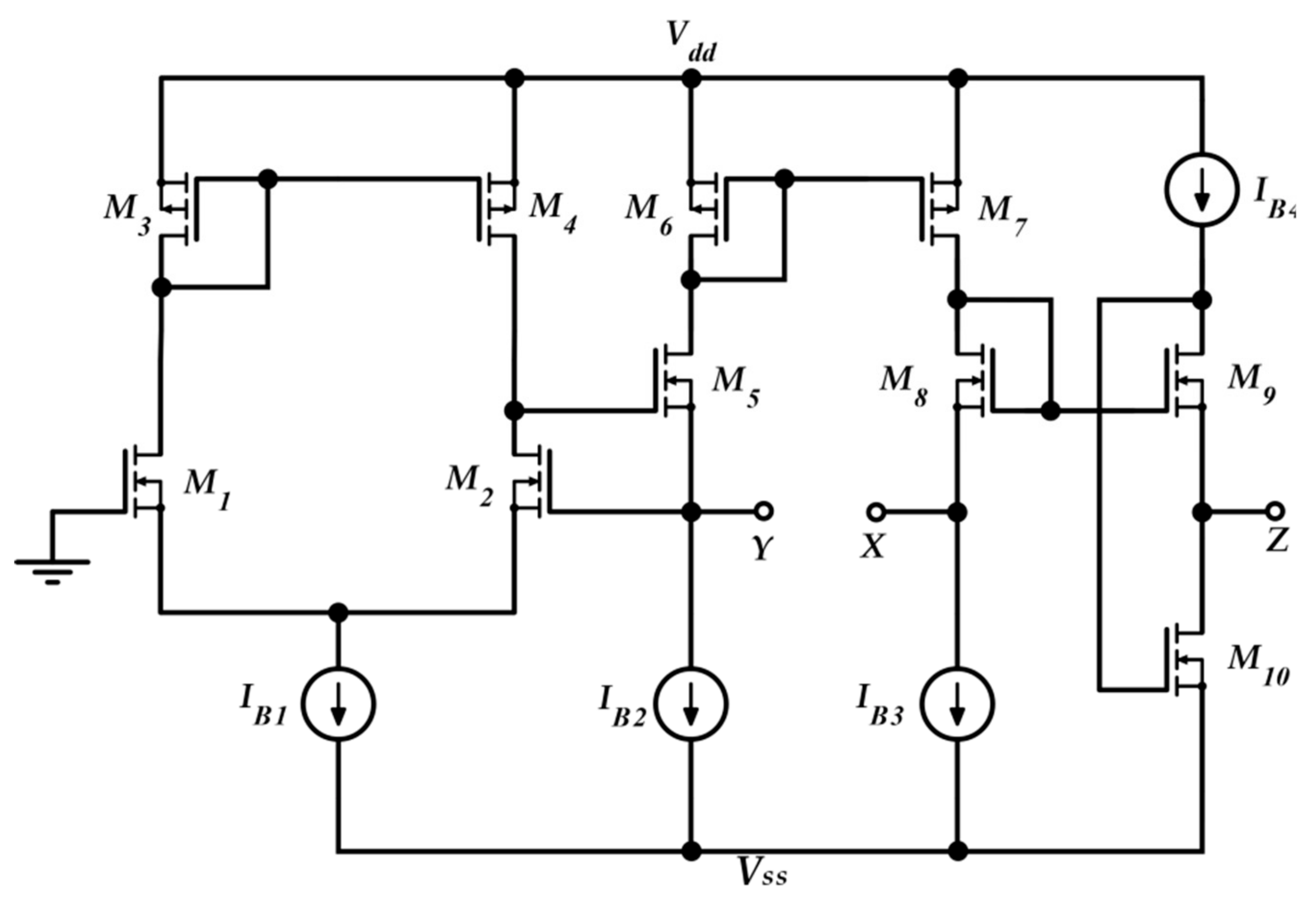

2.2. The Second-Generation Voltage Conveyor

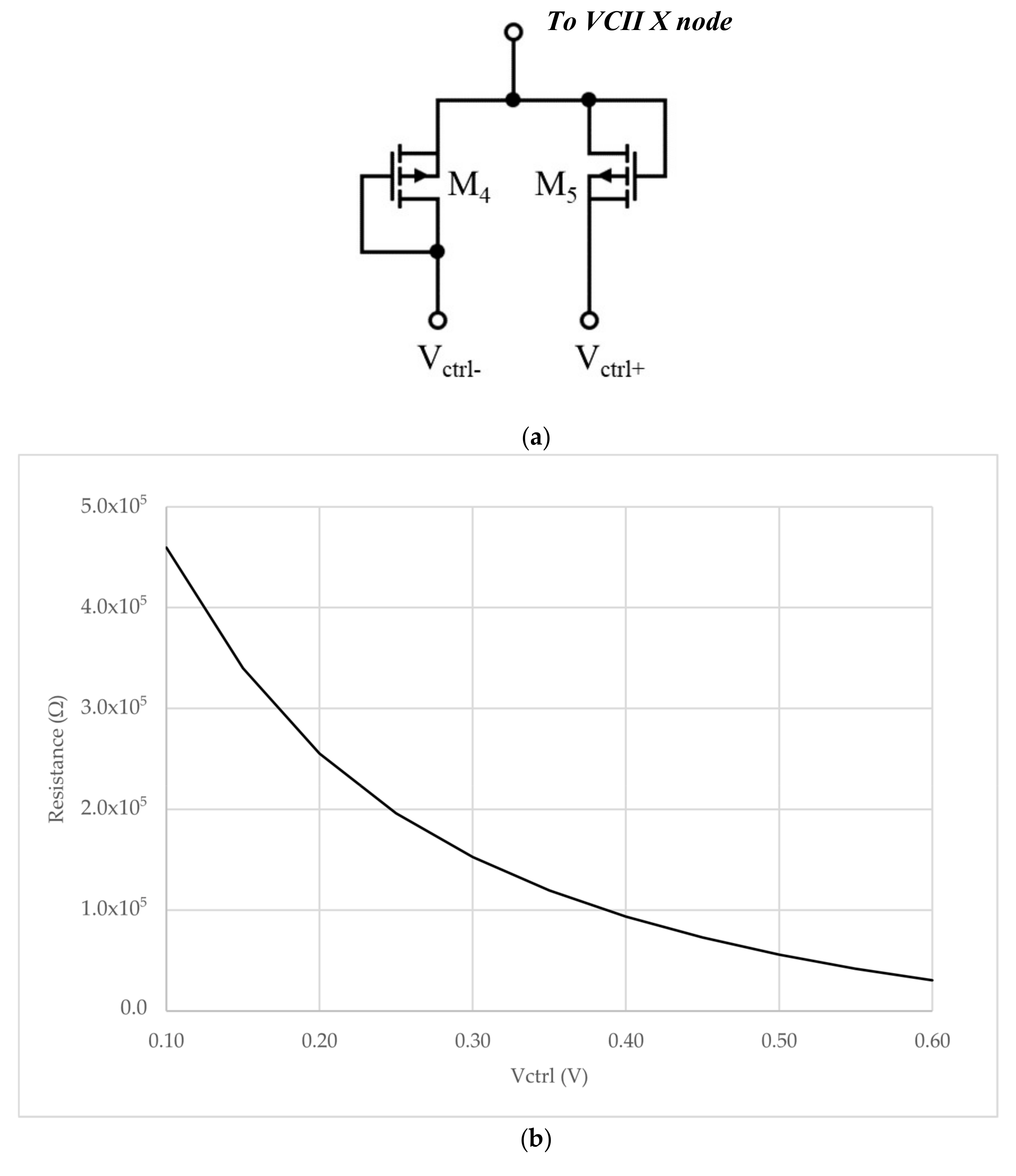

3. The Proposed Combined Architecture

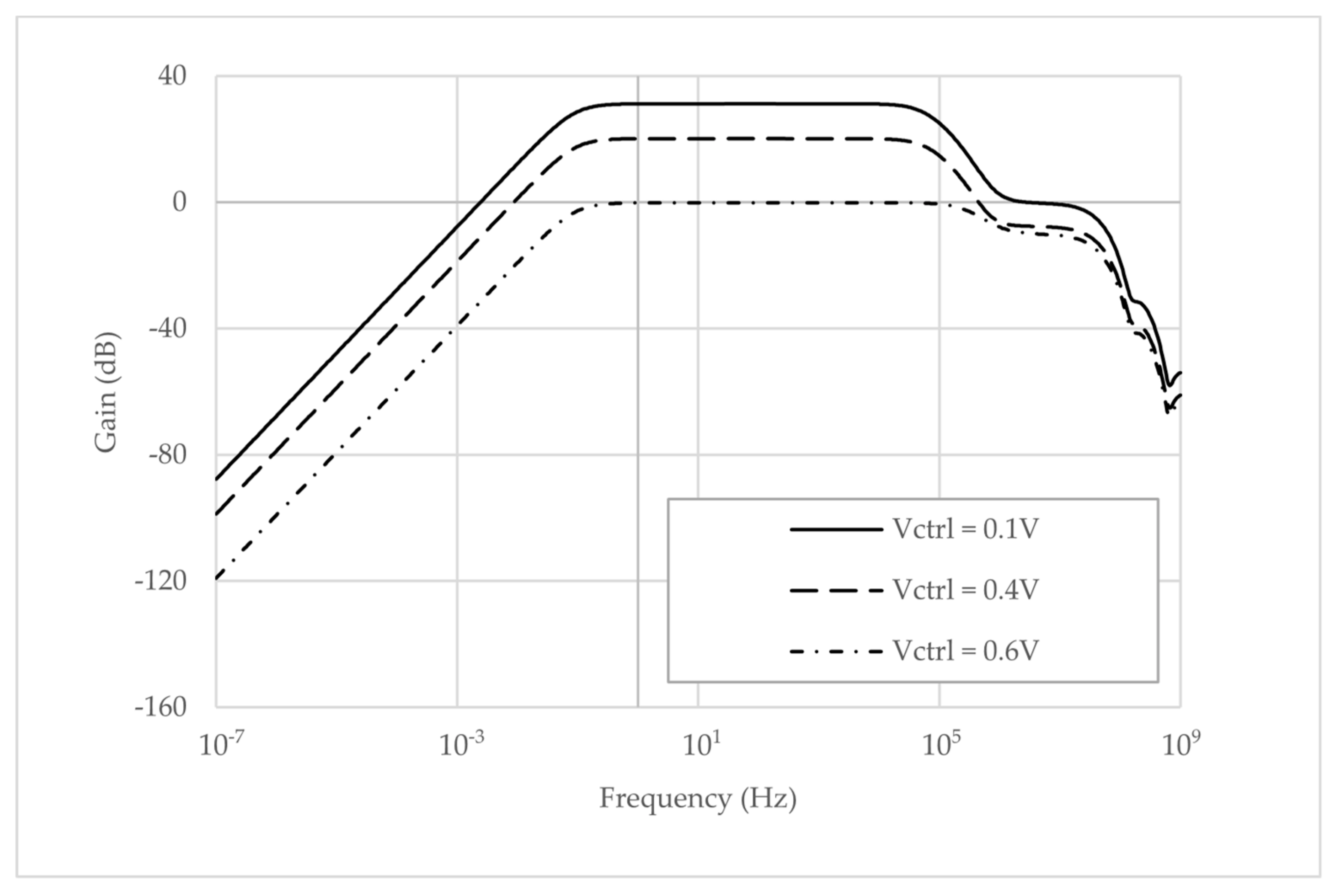

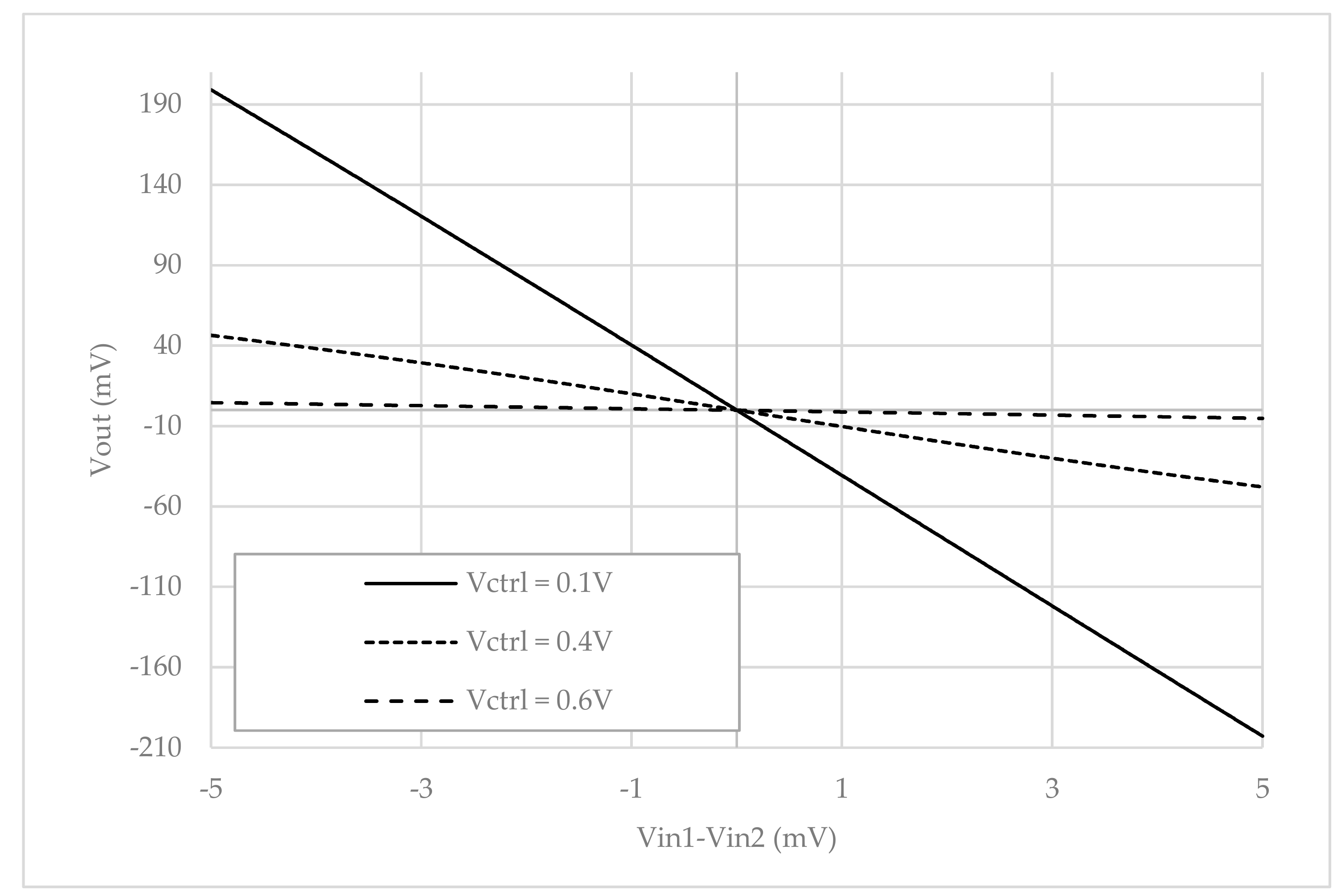

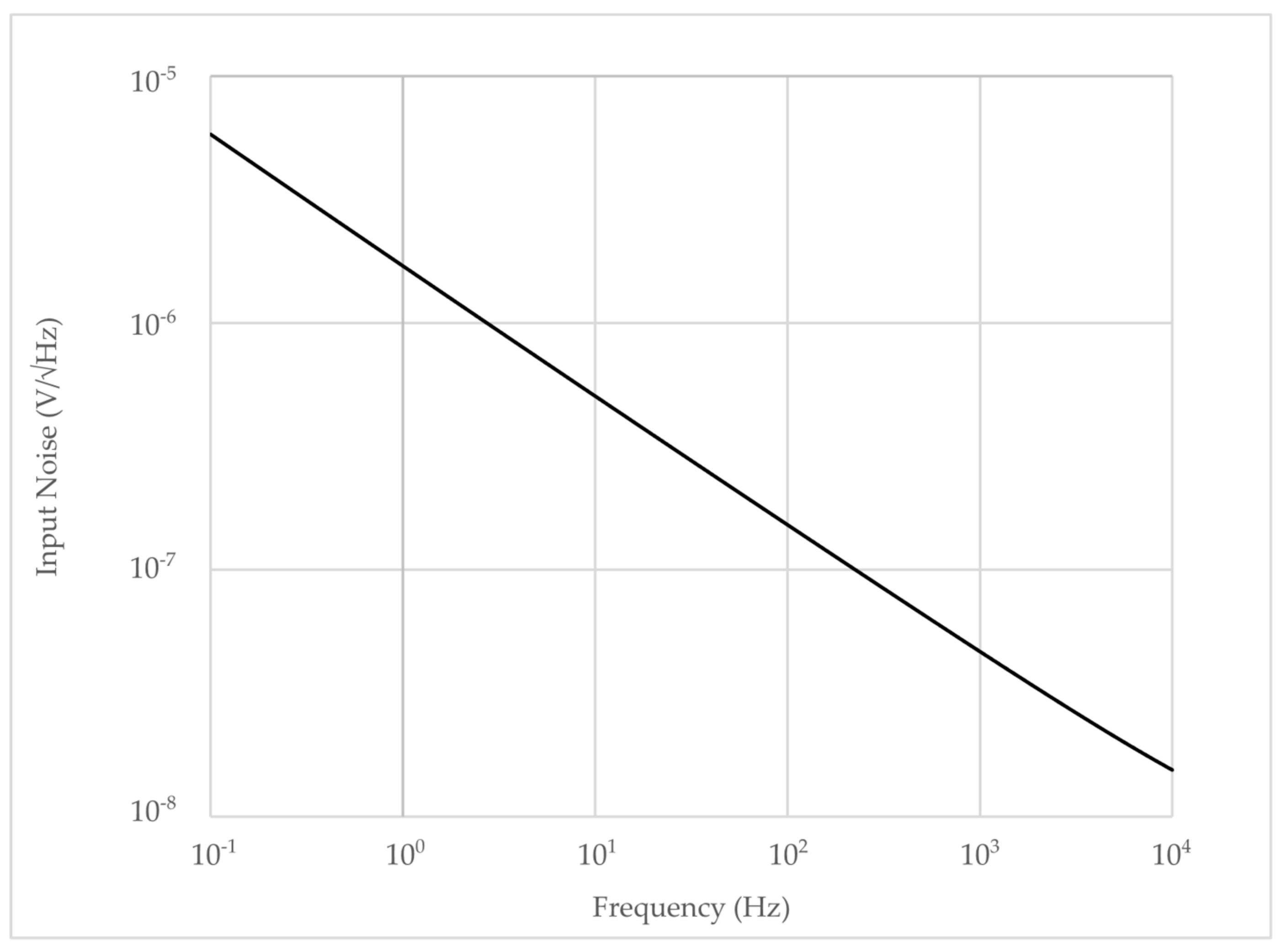

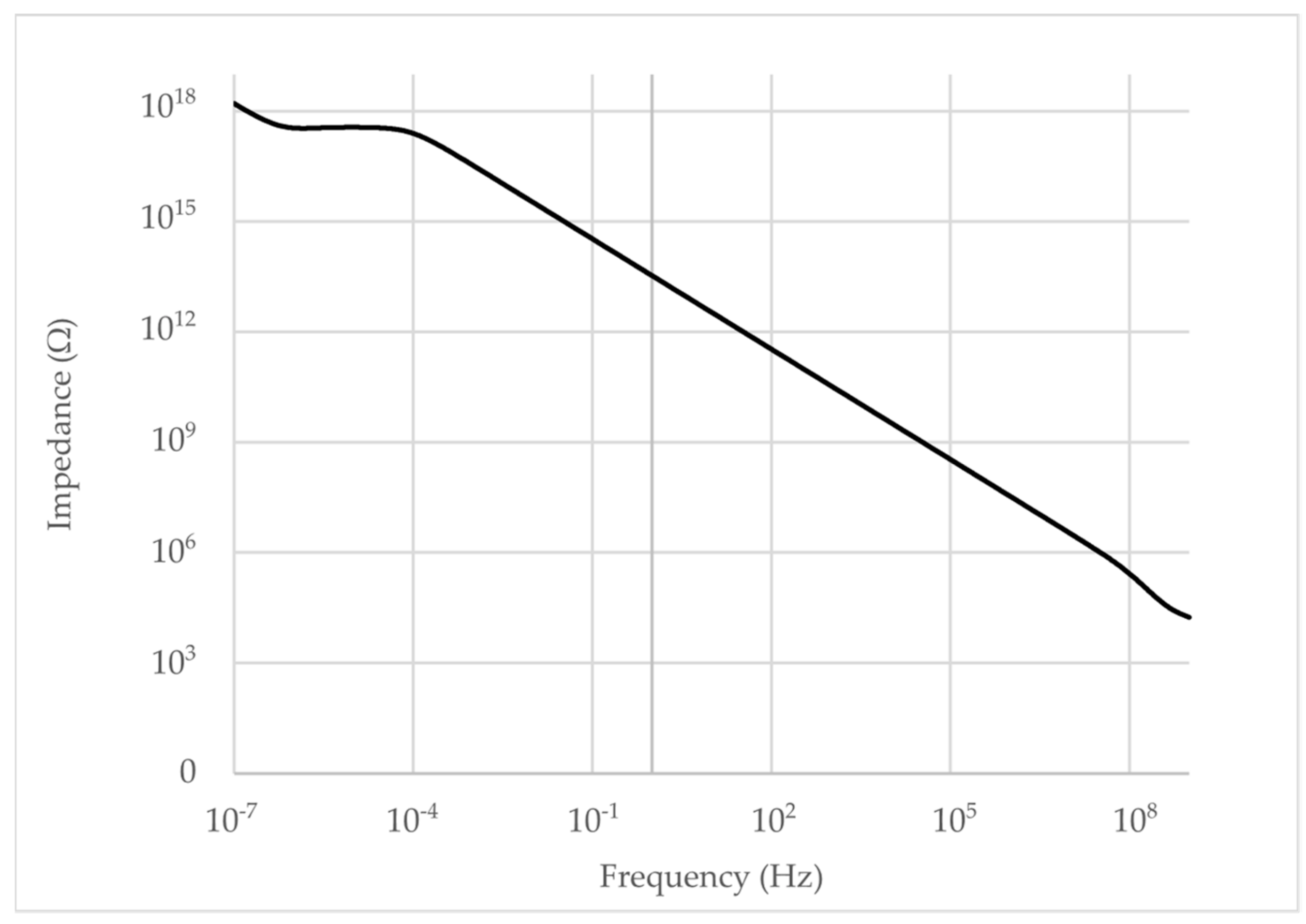

4. Simulation Results and Comparisons

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Du, J.; Blanche, T.; Harrison, R.; Lester, H.; Masmanidis, S. Multiplexed, High Density Electrophysiology with Nanofabricated Neural Probes. PLoS ONE 2011, 6, e26204. [Google Scholar] [CrossRef] [PubMed]

- Yazicioglu, F.; Lopez, C.M.; Mitra, S.; Raducanu, B.; Musa, S. Ultra-High-Density In-Vivo Neural Probes. In Proceedings of the 36th Annual International Conference of the IEEE Engineering in Medicince and Biology Society, Chicago, IL, USA, 26–30 August 2014; pp. 2032–2035. [Google Scholar]

- Scholvin, J.; Kinney, J.; Bernstein, J.; Moore-Kochlacs, C.; Kopell, N.; Fonstad, C.; Boyden, E. Close-Packed Silicon Microelectrodes for Scalable Spatially Oversampled Neural Recording. IEEE Trans. Biomed. Eng. 2016, 63, 120–130. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Dimitriadis, G.; Neto, J.; Kampff, A. t-SNE Visualization of Large-Scale Neural Recordings. Neural Comput. 2018, 30, 1750–1774. [Google Scholar] [CrossRef] [PubMed]

- Santhanam, G.; Linderman, M.; Gilja, V.; Afshar, A.; Ryu, S.; Meng, T.; Shenoy, K. HermesB: A Continuous Neural Recording System for Freely Behaving Primates. IEEE Trans. Biomed. Eng. 2007, 54, 2037–2050. [Google Scholar] [CrossRef] [Green Version]

- Angotzi, G.N.; Berdondini, L. A low-power, low-area modular architecture for high density neural probes. In Proceedings of the 2015 7th International IEEE/EMBS Conference on Neural Engineering (NER), Paris, France, 22–24 April 2015; pp. 521–524. [Google Scholar]

- Ludwig, K.; Miriani, R.; Langhals, N.; Joseph, M.; Anderson, D.; Kipke, D. Using a Common Average Reference to Improve Cortical Neuron Recordings from Microelectrode Arrays. J. Neurophysiol. 2009, 101, 1679–1689. [Google Scholar] [CrossRef]

- Buzsáki, G.; Stark, E.; Berényi, A.; Khodagholy, D.; Kipke, D.; Yoon, E.; Wise, K. Tools for Probing Local Circuits: High-Density Silicon Probes Combined with Optogenetics. Neuron 2015, 86, 92–105. [Google Scholar] [CrossRef] [Green Version]

- Olsson, R.; Wise, K. A three-dimensional neural recording microsystem with implantable data compression circuitry. IEEE J. Solid-State Circuits 2005, 40, 2796–2804. [Google Scholar] [CrossRef]

- Neto, J.; Lopes, G.; Frazão, J.; Nogueira, J.; Lacerda, P.; Baião, P.; Aarts, A.; Andrei, A.; Musa, S.; Fortunato, E.; et al. Validating silicon polytrodes with paired juxtacellular recordings: Method and dataset. J. Neurophysiol. 2016, 116, 892–903. [Google Scholar] [CrossRef] [Green Version]

- Peter, S.; Pratap Reddy, B.; Momtaz, F.; Givargis, T. Design of Secure ECG-Based Biometric Authentication in Body Area Sensor Networks. Sensors 2016, 16, 570. [Google Scholar] [CrossRef] [Green Version]

- Wu, Y.; Jiang, D.; Bardill, A.; Bayford, R.; Demosthenous, A. A 122 fps, 1 MHz Bandwidth Multi-Frequency Wearable EIT Belt Featuring Novel Active Electrode Architecture for Neonatal Thorax Vital Sign Monitoring. IEEE Trans. Biomed. Circuits Syst. 2019, 13, 927–937. [Google Scholar] [CrossRef] [Green Version]

- Xu, X.; Sun, L.; Cannata, J.; Yen, J.; Shung, K. High-Frequency Ultrasound Doppler System for Biomedical Applications with a 30-MHz Linear Array. Ultrasound Med. Biol. 2008, 34, 638–646. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Szuts, T.; Fadeyev, V.; Kachiguine, S.; Sher, A.; Grivich, M.; Agrochão, M.; Hottowy, P.; Dabrowski, W.; Lubenov, E.; Siapas, A.; et al. A wireless multi-channel neural amplifier for freely moving animals. Nat. Neurosci. 2011, 14, 263–269. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Herbawi, A.S.; Larramendy, F.; Galchev, T.; Holzhammer, T.; Mildenberger, B.; Paul, O.; Ruther, P. CMOS-based neural probe with enhanced electronic depth control. In Proceedings of the 2015 Transducers—2015 18th International Conference on Solid-State Sensors, Actuators and Microsystems (TRANSDUCERS), Anchorage, AK, USA, 21–25 June 2015; pp. 1723–1726. [Google Scholar]

- Shandhi, M.M.H.; Leber, M.; Hogan, A.; Bhandari, R.; Negi, S. A novel method of fabricating high channel density neural array for large neuronal mapping. In Proceedings of the 2015 Transducers—2015 18th International Conference on Solid-State Sensors, Actuators and Microsystems (TRANSDUCERS), Anchorage, AK, USA, 21–25 June 2015; pp. 1759–1762. [Google Scholar]

- Harrison, R.R. A Versatile Integrated Circuit for the Acquisition of Biopotentials. In Proceedings of the IEEE 2007 Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 16–19 September 2007; pp. 115–122. [Google Scholar]

- Berényi, A.; Somogyvári, Z.; Nagy, A.; Roux, L.; Long, J.; Fujisawa, S.; Stark, E.; Leonardo, A.; Harris, T.; Buzsáki, G. Large-scale, high-density (up to 512 channels) recording of local circuits in behaving animals. J. Neurophysiol. 2014, 111, 1132–1149. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Han, D.; Zheng, Y.; Rajkumar, R.; Dawe, G.S.; Je, M. A 0.45 V 100-Channel Neural-Recording IC With Sub-μW/Channel Consumption in 0.18 μm CMOS. IEEE Trans. Biomed. Circuits Syst 2013, 7, 735–746. [Google Scholar]

- Parente, F.; Di Giovanni, S.; Ferri, G.; Stornelli, V.; Pennazza, G.; Santonico, M. An Analog Bootstrapped Biosignal Read-Out Circuit with Common-Mode Impedance Two-Electrode Compensation. IEEE Sens. J. 2018, 18, 2861–2869. [Google Scholar] [CrossRef]

- Baluch, F.; Itti, L. A portable system for recording neural activity in indoor and outdoor environments. In Proceedings of the 2012 Annual International Conference of the IEEE Engineering in Medicine and Biology Society, San Diego, CA, USA, 28 August–1 September 2012; pp. 2388–2391. [Google Scholar] [CrossRef]

- Leoni, A.; Ulisse, I.; Pantoli, L.; Errico, V.; Ricci, M.; Orengo, G.; Giannini, F.; Saggio, G. Energy harvesting optimization for built-in power replacement of electronic multisensory architecture. AEU-Int. J. Electron. Commun. 2019, 107, 170–176. [Google Scholar] [CrossRef]

- Piscitelli, G.; Errico, V.; Ricci, M.; Giannini, F.; Saggio, G.; Leoni, A.; Stornelli, V.; Ferri, G.; Pantoli, L.; Ulisse, I. A low-cost energy-harvesting sensory headwear useful for tetraplegic people to drive home automation. AEU-Int. J. Electron. Commun. 2019, 107, 9–14. [Google Scholar] [CrossRef]

- Stornelli, V.; Leoni, A.; Ferri, G.; Errico, V.; Ricci, M.; Pallotti, A.; Saggio, G. A Multi-Source Energy Harvesting Sensory Glove Electronic Architecture. In Proceedings of the 2018 3rd International Conference on Smart and Sustainable Technologies (SpliTech), Split, Croatia, 26–29 June 2018; pp. 1–4. [Google Scholar]

- Leoni, A.; Stornelli, V.; Ferri, G.; Errico, V.; Ricci, M.; Pallotti, A.; Saggio, G. A human body powered sensory glove system based on multisource energy harvester. In Proceedings of the 2018 14th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Prague, Czech Republic, 2–5 July 2018; pp. 113–116. [Google Scholar] [CrossRef]

- Di Marco, P.; Leoni, A.; Pantoli, L.; Stornelli, V.; Ferri, G. Remote sensor networks with efficient energy harvesting architecture. In Proceedings of the 2016 12th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Lisbon, Portugal, 27–30 June 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Lopez, C.; Andrei, A.; Mitra, S.; Welkenhuysen, M.; Eberle, W.; Bartic, C.; Puers, R.; Yazicioglu, R.; Gielen, G. An Implantable 455-Active-Electrode 52-Channel CMOS Neural Probe. IEEE J. Solid-State Circuits 2014, 49, 248–261. [Google Scholar] [CrossRef]

- Raducanu, B.C.; Yazicioglu, R.F.; Lopez, C.M.; Ballini, M.; Putzeys, J.; Wang, S.; Andrei, A.; Welkenhuysen, M.; Van Helleputte, N.; Musa, S.; et al. Time multiplexed active neural probe with 678 parallel recording sites. In Proceedings of the 2016 46th European Solid-State Device Research Conference (ESSDERC), Lausanne, Switzerland, 12–15 September 2016; pp. 385–388. [Google Scholar] [CrossRef] [Green Version]

- Huang, Y.C.; Huang, P.T.; Wu, S.L.; Hu, Y.C.; You, Y.H.; Chen, M.; Huang, Y.Y.; Chang, H.C.; Lin, Y.H.; Duann, J.R.; et al. An ultra-high-density 256-channel/25mm2 neural sensing microsystem using TSV-embedded neural probes. In Proceedings of the 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, Canada, 22–25 May 2016; pp. 1302–1305. [Google Scholar] [CrossRef]

- Sayed Herbawi, A.; Kießner, L.; Paul, O.R.P. High-density CMOS neural probe implementing a hierarchical addressing scheme for 1600 recording sites and 32 output channels. In Proceedings of the IEEE Transducers 2017, Kaohsiung, Taiwan, 18–22 June 2017. [Google Scholar] [CrossRef]

- Gao, H.; Walker, R.M.; Nuyujukian, P.; Makinwa, K.A.A.; Shenoy, K.V.; Murmann, B.; Meng, T.H.; Hermes, E.A. 96-channel full data rate di‘rect neural interface in 0.13 μm CMOS. IEEE J. Solid-State Circuits 2012, 47, 1043–1055. [Google Scholar] [CrossRef]

- Harrison, R.; Charles, C. A low-power low-noise cmos for amplifier neural recording applications. IEEE J. Solid-State Circuits 2003, 38, 958–965. [Google Scholar] [CrossRef]

- Mora Lopez, C.; Putzeys, J.; Raducanu, B.; Ballini, M.; Wang, S.; Andrei, A.; Rochus, V.; Vandebriel, R.; Severi, S.; Van Hoof, C.; et al. A Neural Probe With Up to 966 Electrodes and Up to 384 Configurable Channels in 0.13 µm SOI CMOS. IEEE Trans. Biomed. Circuits Syst. 2017, 11, 510–522. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Carvajal, R.G.; Ramírez-Angulo, J.; López-Martin, A.; Torralba, A.; Galán, J.; Carlosena, A.; Muñoz, F. The Flipped voltage follower: A useful cell for low-voltage low-power circuit design. In Proceedings of the 2002 IEEE International Symposium on Circuits and Systems, Phoenix-Scottsdale, AZ, USA, 26–29 May 2002. [Google Scholar] [CrossRef]

- Gupta, S.; Padilla, I.; Ramirez-Angulo, J.; Torralba, A.; Jimenez, M.; Munoz, F. Comparison of conventional and new flipped voltage structures with increased input/output signal swing and current sourcing/sinking capabilities. In Proceedings of the IEEE Midwest Symposium on Circuits and Systems, Covington, KY, USA, 7–10 August 2005; pp. 1151–1154. [Google Scholar] [CrossRef]

- Gray, P.R.; Hurst, P.J.; Lewis, H.; Meyer, R.G. Analysis and Design of Analog Integrated Circuits, 4th ed.; John Wiley and Sons: New York, NY, USA, 2001. [Google Scholar]

- Centurelli, F.; Monsurrò, P.; Trifiletti, A.; Barile, G.; Ferri, G.; Pantoli, L.; Stornelli, V. Class-AB Current Conveyors based on the FVF. In Proceedings of the 2017 European Conference on Circuit Theory and Design (ECCTD), Catania, Italy, 4–6 September 2017. [Google Scholar] [CrossRef]

- Centurelli, F.; Monsurrò, P.; Trifiletti, A. A Class-AB Flipped Voltage Follower Output Stage. In Proceedings of the 2011 20th European Conference on Circuit Theory and Design (ECCTD), Linkoping, Sweden, 29–31 August 2011; pp. 757–760. [Google Scholar] [CrossRef]

- Centurelli, F.; Monsurrò, P.; Ruscio, D.; Trifiletti, A. A New Class-AB Flipped Voltage Follower Using a Common-gate Auxiliary Amplifier. In Proceedings of the 2016 MIXDES—23rd International Conference Mixed Design of Integrated Circuits and Systems, Lodz, Poland, 23–25 June 2018; pp. 143–146. [Google Scholar] [CrossRef]

- Barile, G.; Ferri, G.; Safari, L.; Stornelli, V. A New High Drive Class-AB FVF Based Second Generation Voltage Conveyor. IEEE Trans. Circuits Syst. Ii: Express Briefs 2019. [Google Scholar] [CrossRef]

- Carvajal, R.; Ramirez-Angulo, J.; Lopez-Martin, A.; Torralba, A.; Galan, J.; Carlosena, A.; Chavero, F. The flipped voltage follower: A useful cell for low-voltage low-power circuit design. IEEE Trans. Circuits Syst. I Regul. Pap. 2005, 52, 1276–1291. [Google Scholar] [CrossRef]

- Stornelli, V.; Ferri, G.; Pantoli, L.; Barile, G.; Pennisi, S. A rail-to-rail constant-g m CCII for Instrumentation Amplifier applications. AEU-Int. J. Electron. Commun. 2018, 91, 103–109. [Google Scholar] [CrossRef]

- Khateb, F.; Kulej, T.; Kumngern, M. 0.3V Bulk-Driven Current Conveyor. IEEE Access 2019, 7, 65122–65128. [Google Scholar] [CrossRef]

- Stornelli, V.; Ferri, G. A single current conveyor-based low voltage low power bootstrap circuit for ElectroCardioGraphy and ElectroEncephaloGraphy acquisition systems. Analog Integr. Circuits Signal Process. 2014, 79, 171–175. [Google Scholar] [CrossRef]

- Barile, G.; Leoni, A.; Pantoli, L.; Safari, L.; Stornelli, V. A New VCII Based Low-Power Low-Voltage Front-end for Silicon Photomultipliers. In Proceedings of the 3rd International Conference on Smart and Sustainable Technologies (SpliTech), Split, Croatia, 26–29 June 2018. [Google Scholar]

- Pantoli, L.; Barile, G.; Leoni, A.; Muttillo, M.; Stornelli, V. A Novel Electronic Interface for Micromachined Si-Based Photomultipliers. Micromachines 2018, 9, 507. [Google Scholar] [CrossRef] [Green Version]

- Safari, L.; Barile, G.; Ferri, G.; Stornelli, V. High performance voltage output filter realizations using second generation voltage conveyor. Int. J. Rf Microw. Comput.-Aided Eng. 2018, 28, e21534. [Google Scholar] [CrossRef]

- Safari, L.; Barile, G.; Ferri, G.; Stornelli, V. Traditional Op-Amp and new VCII: A comparison on analog circuits applications. AEU-Int. J. Electron. Commun. 2019, 110, 152845. [Google Scholar] [CrossRef]

- Wang, Z. Reply: 2-MOSFET transresistor with extremely low distortion for output reaching supply voltages. Electron. Lett. 1990, 26, 951–952. [Google Scholar] [CrossRef]

- Song, S.; Rooijakkers, M.; Harpe, P.; Rabotti, C.; Mischi, M.; van Roermund, A.; Cantatore, E. A Noise Reconfigurable Current-Reuse Resistive Feedback Amplifier with Signal Dependent Power Consumption for Fetal ECG Monitoring. IEEE Sens. J. 2016, 16, 8304–8313. [Google Scholar] [CrossRef] [Green Version]

- Shen, L.; Lu, N.; Sun, N. A 1-V 0.25-µW Inverter Stacking Amplifier with 1.07 Noise Efficiency Factor. IEEE J. Solid-State Circuits 2018, 53, 896–905. [Google Scholar] [CrossRef]

- Franks, W.; Schenker, I.; Schmutz, P.; Hierlemann, A. Impedance characterization and modeling of electrodes for biomedical applications. IEEE Trans. Biomed. Eng. 2005, 52, 1295–1302. [Google Scholar] [CrossRef] [PubMed]

- Dong, S.; Tong, X.; Liu, L.; Yang, A.; Li, R. A Gain & Bandwidth Reprogrammable Neural Recording Amplifier with Leakage Reduction Switches. In Proceedings of the IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Xi’an, China, 12–14 June 2019; pp. 1–3. [Google Scholar] [CrossRef]

- Liu, L.; Zhuang, Y.; Zhang, L.; Jing, K.; Dong, S.; Chen, Y. A Reconfigurable Low Noise Amplifier with Sub-amplifier Compensation for Wearable Wireless Neural Recording System. In Proceedings of the IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Xi’an, China, 12–14 June 2019; pp. 1–3. [Google Scholar] [CrossRef]

- Oreggioni, J.; Caputi, A.A.; Silveira, F. Current-Efficient Preamplifier Architecture for CMRR Sensitive Neural Recording Applications. IEEE Trans. Biomed. Circuits Syst 2018, 12, 689–699. [Google Scholar] [CrossRef] [PubMed]

| Transistor | Dimensions (W, L) |

|---|---|

| M1,2 | 5.55 µm, 0.3 µm |

| M3 | 1.05 µm, 0.3 µm |

| M4–6–15–16–17 | 1.8 µm, 1.5 µm |

| M5–9–18 | 11.85 µm, 0.3 µm |

| M8 | 60 µm, 0.15 µm |

| M10–11 | 55.95 µm, 0.15 µm |

| M12–13 | 1.95 µm, 0.15 µm |

| M14 | 7.95 µm, 1.5 µm |

| M7–24 | 3.6 µm, 1.5 µm |

| M19 | 16.05 µm, 1.5 µm |

| M20–21 | 70.05 µm, 0.3 µm |

| M22–23 | 55.05 µm, 18 µm |

| M25 | 1.8 µm, 45.9 µm |

| Parameter | Value |

| IB | 2 µA |

| VA | −290 mV |

| C1, C2 | 1 pF |

| VB | 50 mV |

| Parameter | This work | 2016 [50] | 2018 [51] | 2019 [53] | 2019 [54] | 2018 [55] |

|---|---|---|---|---|---|---|

| CMOS Technology | LFoundry 150 nm | 180 nm | 180 nm | 180 nm | 180 nm | 500 nm |

| Supply voltage | ±0.6 V | 1.2 V | 1 V | 1.2 V | 1.2 V | 3.3 V |

| Static power consumption | 20 µW | 0.9 µW | 0.25 µW | 8.1 µW | 2.48/5.46 µW (AP/LFP) | 28.05 µW |

| Amplifier Gain (dB) | 0~33 (continuous Tuning) | 30/50 | 25.6 | 26/32/35.6 (Selectable) | 40/20 (AP/LFP) | 49.5 (Untunable) |

| fHPF (Hz) | 10-5 | 6.3 | 4 | 0.025/0.25/0.5/1.5/32/65/125/260 | - | 13 |

| fLPF (kHz) | 174~3980 | 0.175 | 10 | 1/11.4/125 | 100/1000 (LFP/AP) | 9.8 |

| Zin | 3.2 GΩ (@10 kHz) | 20 MΩ | 200 MΩ @100 Hz | - | - | - |

| Zout | 1.2 kΩ (@10 kHz) | - | - | - | - | - |

| THD @frequency reference | 1.02% (−39.8 dB) @Vin = 2mVpp, Vctrl = 0 V, 10 kHz) | 0.4%@1mVpp 10 Hz | - | - | - | 1% @ 0.7 mVpp, 10 kHz |

| Noise Voltage (input referred) | 5.4 µVRMS (0.1 Hz ~ 10 kHz) | 2.6 µVRMS (0.5 Hz ~ 400 Hz) | 3.32 µVRMS (250 Hz ~ 10 kHz) | 6.75 µVRMS (0.5~11.4 k, 40 dB) | AP: 3.44 (0.25 k~10 k) LFP: 6.88 (0.025~600) | 1.88 µVRMS (0.03 Hz~11 kHz) |

| NEF | 8.3 | 6.6 | 1.07 | 7.29 | NA | 2.3 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Stornelli, V.; Barile, G.; Leoni, A. A Novel General Purpose Combined DFVF/VCII Based Biomedical Amplifier. Electronics 2020, 9, 331. https://doi.org/10.3390/electronics9020331

Stornelli V, Barile G, Leoni A. A Novel General Purpose Combined DFVF/VCII Based Biomedical Amplifier. Electronics. 2020; 9(2):331. https://doi.org/10.3390/electronics9020331

Chicago/Turabian StyleStornelli, Vincenzo, Gianluca Barile, and Alfiero Leoni. 2020. "A Novel General Purpose Combined DFVF/VCII Based Biomedical Amplifier" Electronics 9, no. 2: 331. https://doi.org/10.3390/electronics9020331