A Self-Powered VDJT AC–DC Conversion Circuit for Piezoelectric Energy Harvesting Systems

Abstract

:1. Introduction

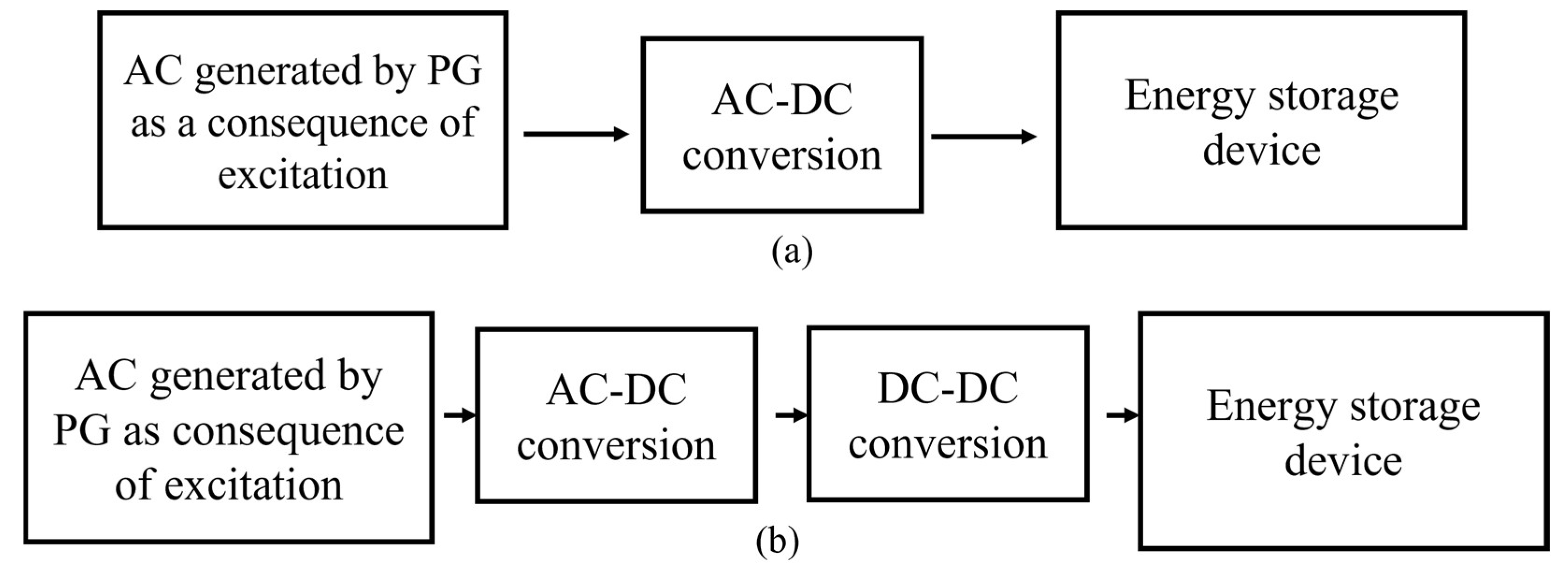

2. PG Internal Characteristics and Power Conversion Circuits

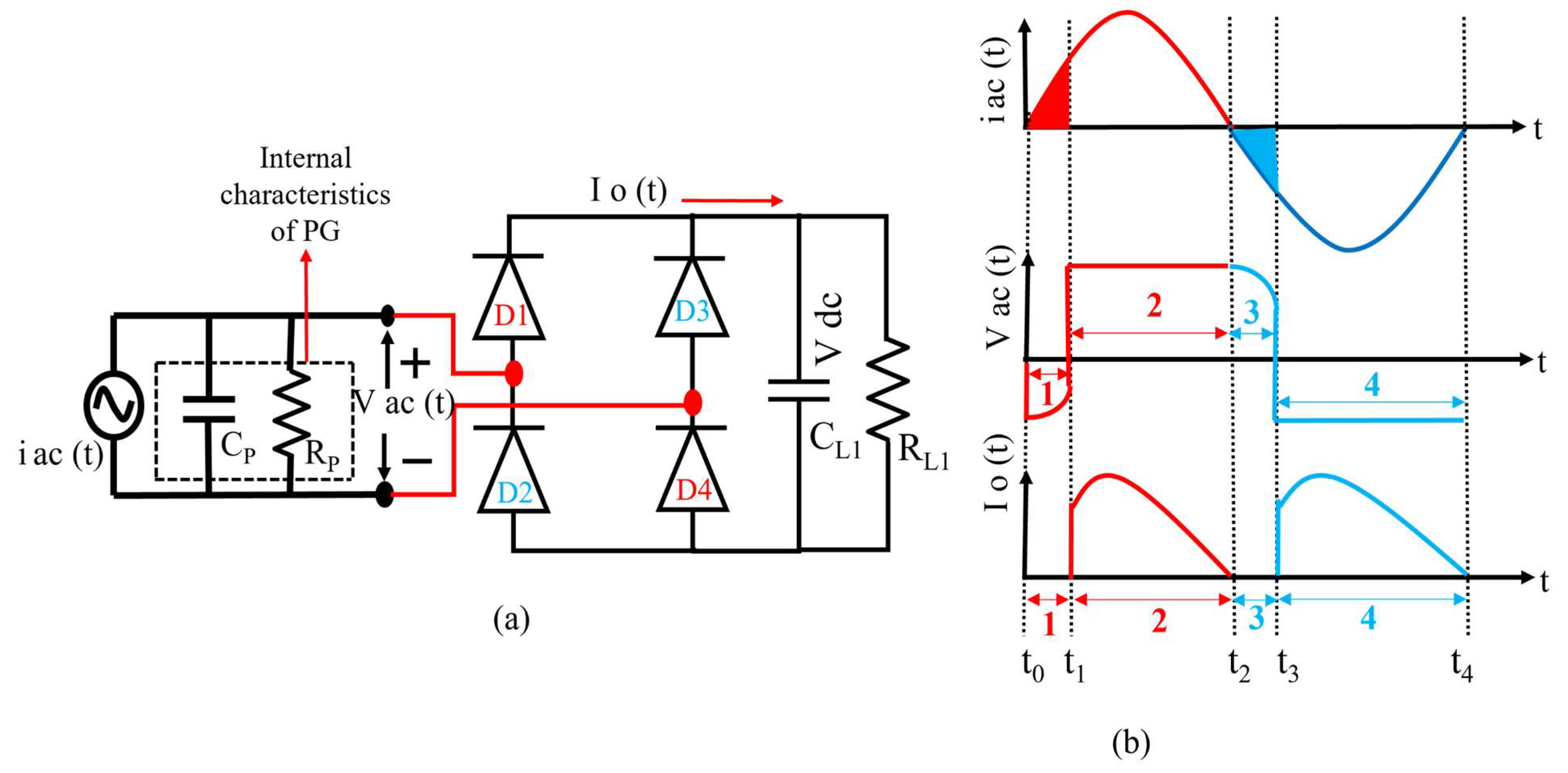

2.1. PG Circuit Model

2.2. VD Circuit

- Mode 1: Positive half cycle

- -

- No output

- -

- D1: OFF

- -

- D1: ON

- -

- V ac = V dc (C1: Charged)

- Mode 2: Negative half cycle

- -

- No output

- -

- D2: OFF

- -

- D2: ON

- -

- V ac = V dc (C2: Charged)

2.3. VDJT Circuit

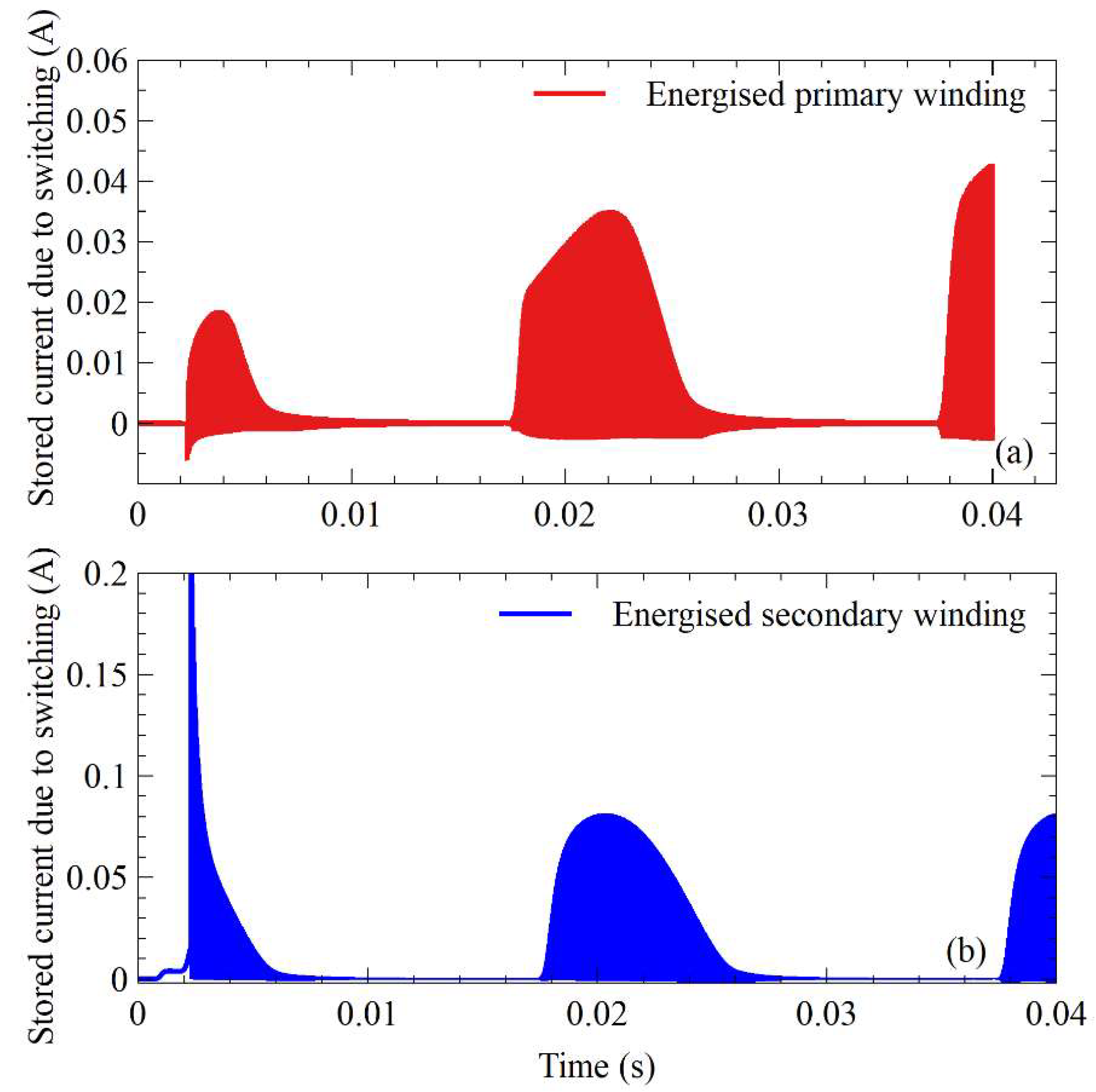

3. Simulation Results

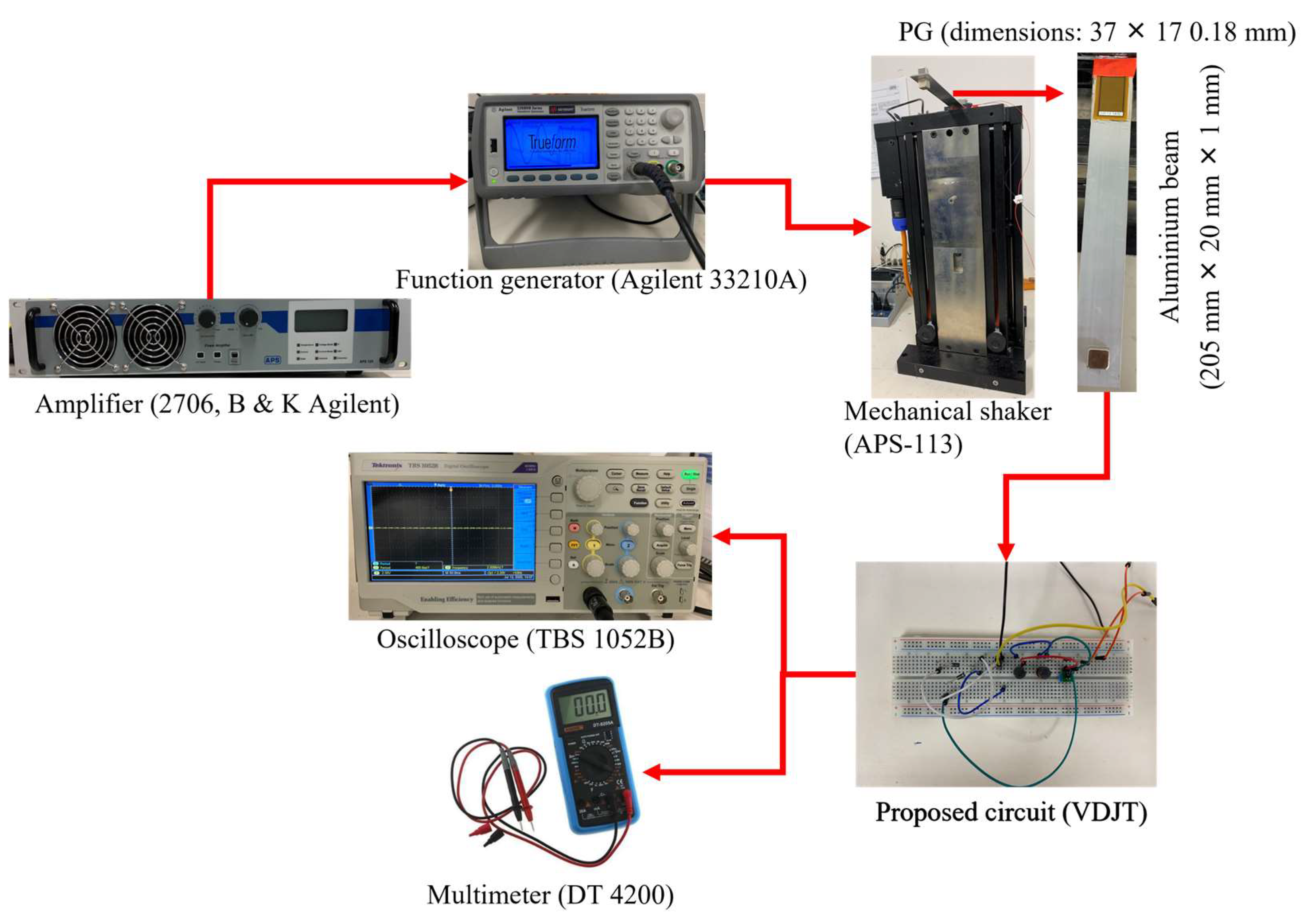

4. Experimental Results

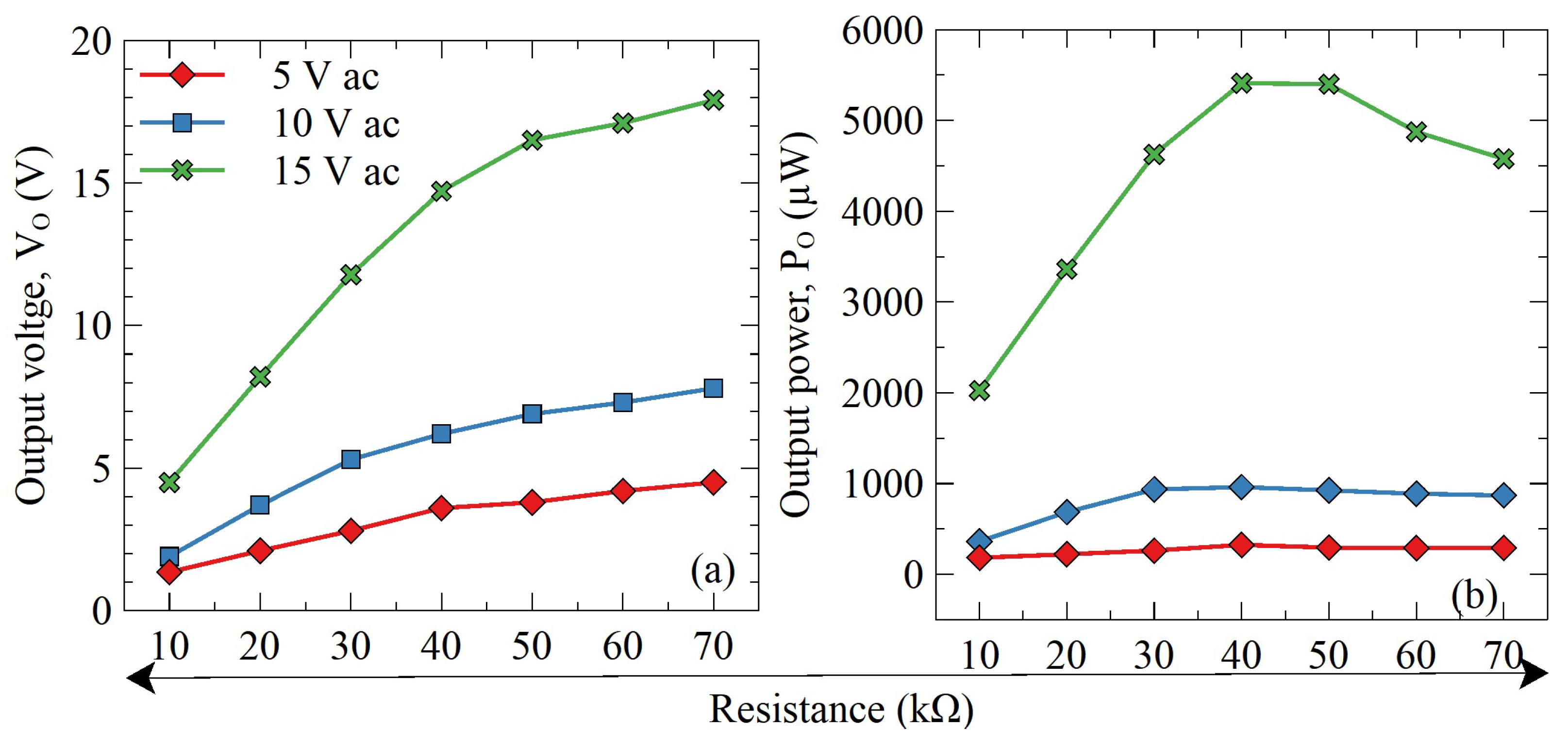

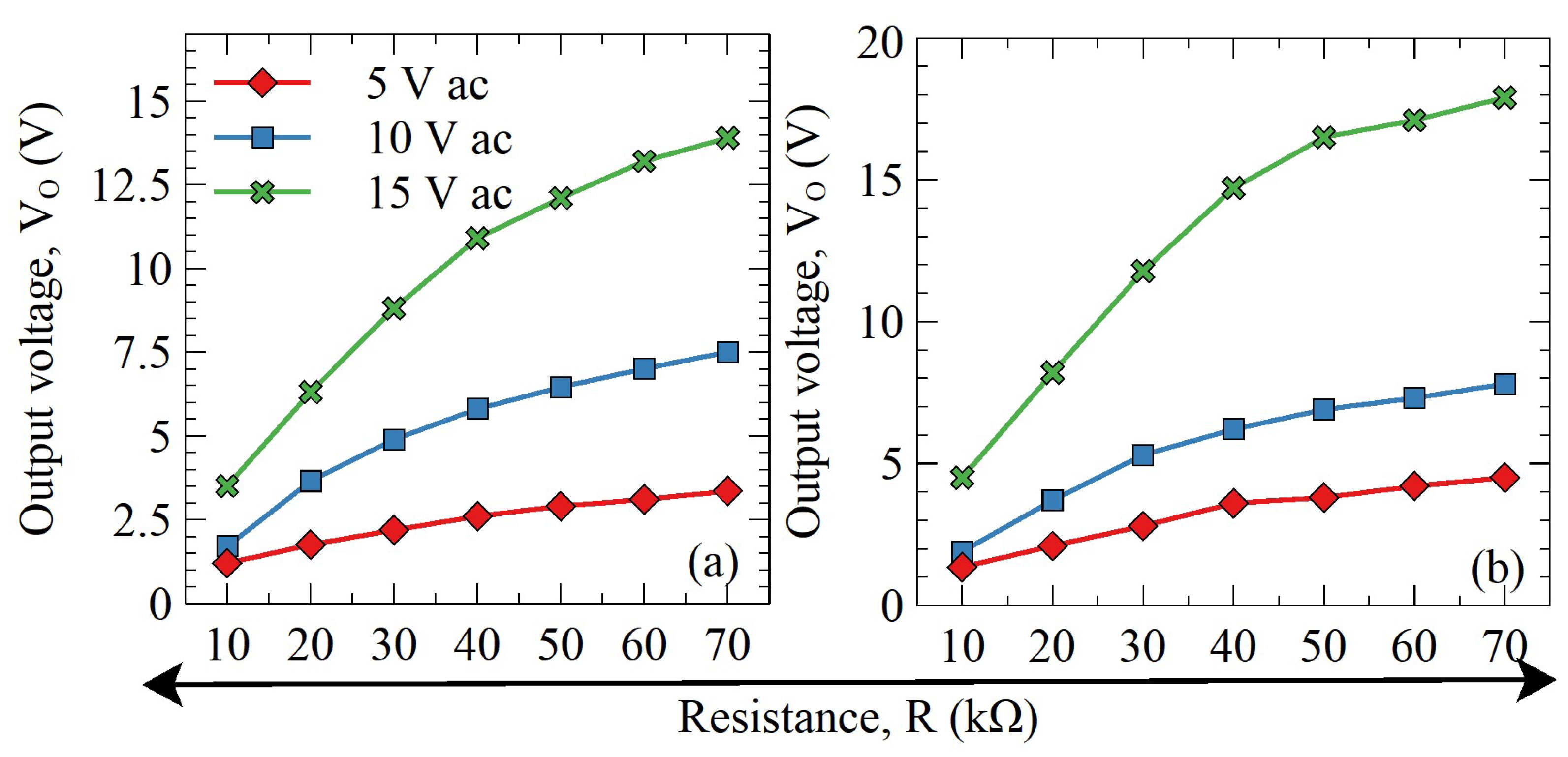

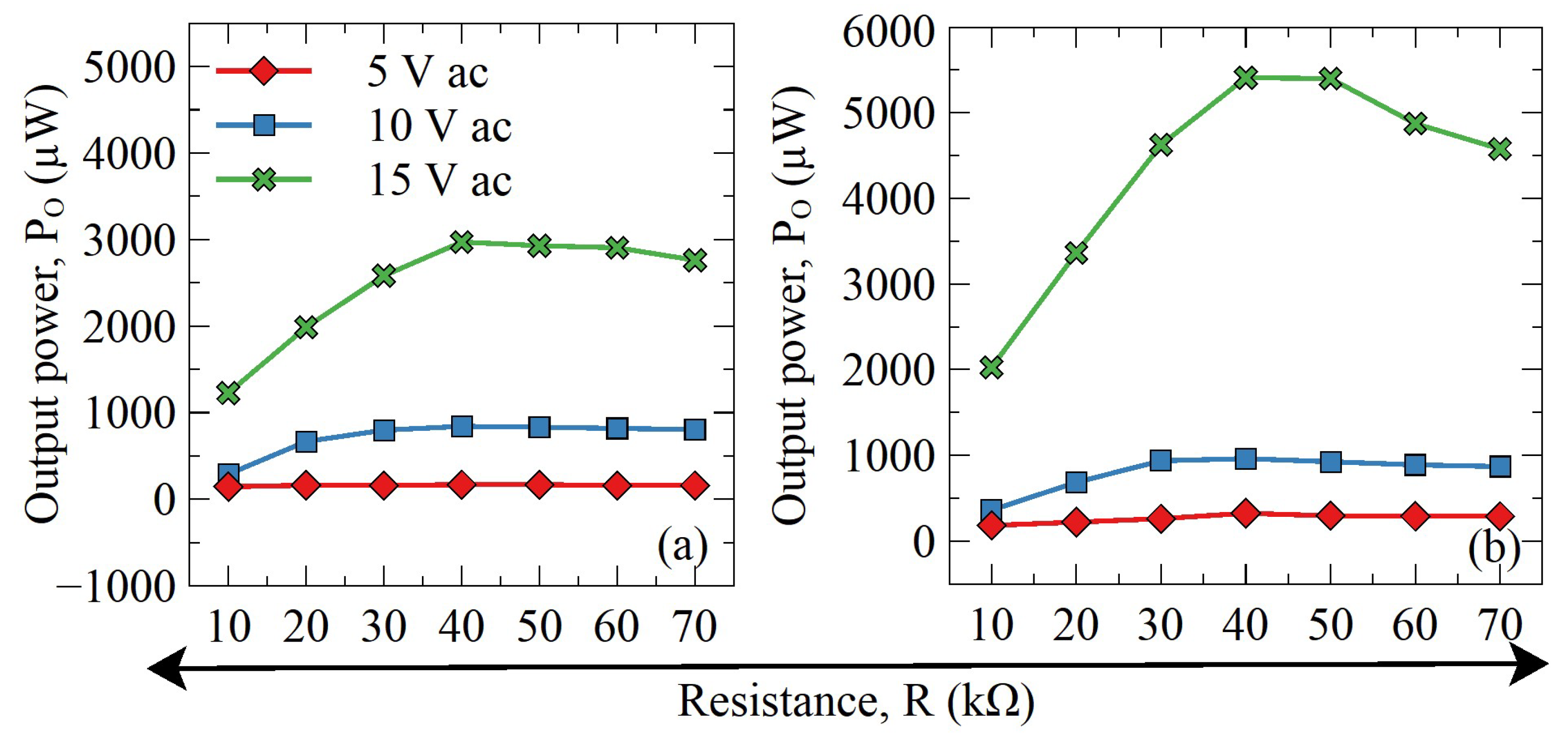

4.1. Test 1: Varying Input Voltage at a Constant Frequency

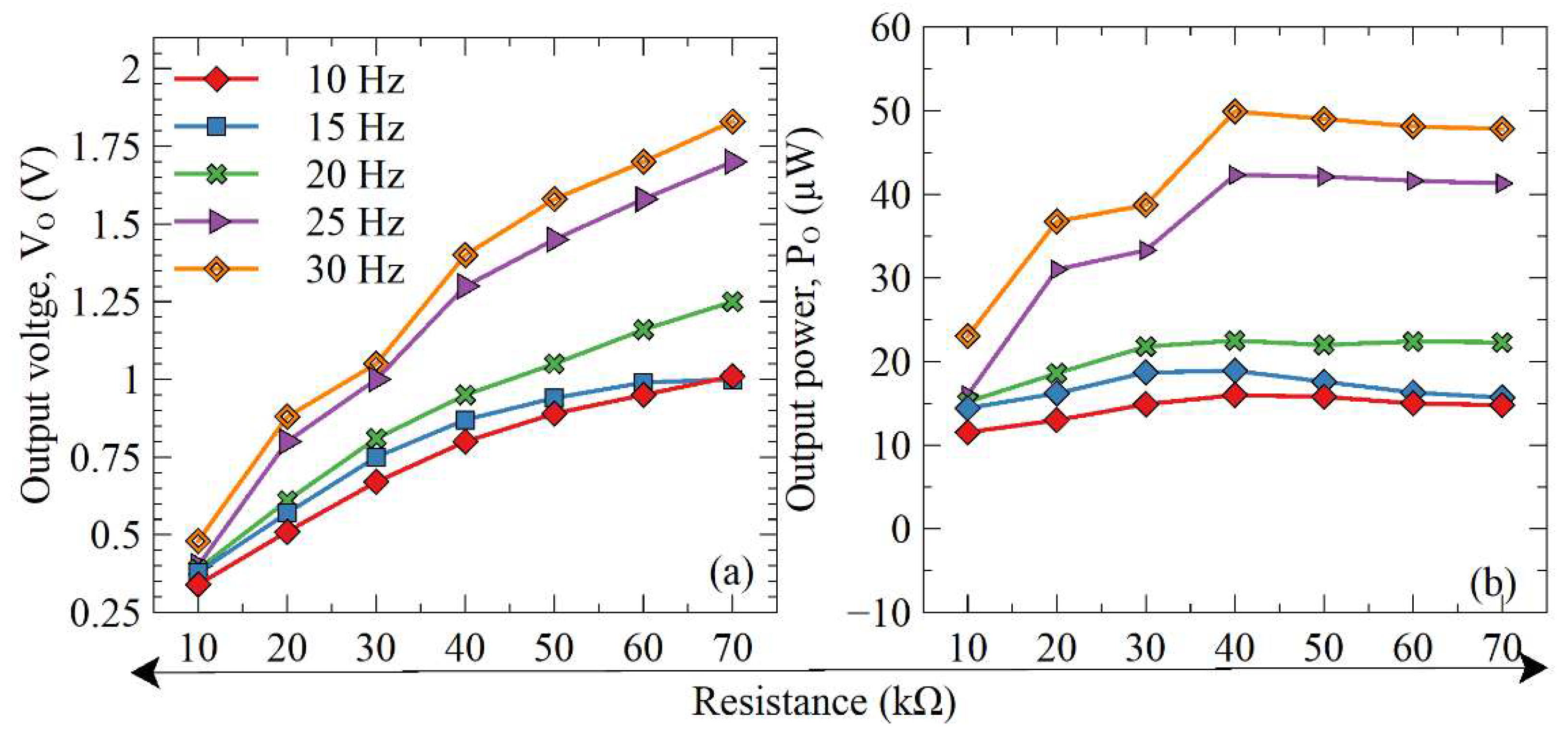

- While the frequency incremented, PG generated more current due to a decrease in capacitive reactance.

- When the PG current was increased, its output power was also increased, resulting in higher output power of the VDJT circuit.

4.2. Test 2: Constant Input Voltage by Varying Frequencies

4.3. Comparison of VDJT Circuit with the Literature Circuits

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Erturk, A.; Inman, D.J. Piezoelectric Energy Harvesting; John Wiley & Sons: Hoboken, NJ, USA, 2011. [Google Scholar]

- Lefeuvre, E.; Badel, A.; Richard, C.; Guyomar, D. Piezoelectric energy harvesting device optimization by synchronous electric charge extraction. J. Intell. Mater. Syst. Struct. 2005, 16, 865–876. [Google Scholar] [CrossRef]

- Liu, H.; Zhong, J.; Lee, C.; Lee, S.-W.; Lin, L. A comprehensive review on piezoelectric energy harvesting technology: Materials, mechanisms, and applications. Appl. Phys. Rev. 2018, 5, 041306. [Google Scholar] [CrossRef] [Green Version]

- Lee, M.; Yang, J.; Park, M.; Jung, S.; Kim, J. Design and Analysis of Energy-Efficient Single-Pulse Piezoelectric Energy Harvester and Power Management IC for Battery-Free Wireless Remote Switch Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 366–379. [Google Scholar] [CrossRef]

- Edla, M.; Mikio, D.; Izadgoshasb, I.; Mahmud, M.P.; Kouzani, A.Z. Self-powered boost-converter for power optimisation and piezo garden lights. Smart Mater. Struct. 2022, 31, 045021. [Google Scholar] [CrossRef]

- Edla, M.; Lim, Y.Y.; Mikio, D.; Padilla, R.V. Non-Linear Switching Circuit for Active Voltage Rectification and Ripples Reduction of Piezoelectric Energy Harvesters. Energies 2022, 15, 709. [Google Scholar] [CrossRef]

- Muhammad, K.; Edla, M.; Thabet, A.M.; Haseeb, A.; Deguchi, M.; Bui, V. A Self-Powered AC-DC Conversion Circuit for Piezoelectric Energy Harvesting Systems. Energies 2023, 16, 1734. [Google Scholar] [CrossRef]

- Abdul, H.; Edla, M.; Ahmed Mostafa, T.; Deguchi, M.; Kamran, M. A Self-Powered Dual-Stage Boost Converter Circuit for Piezoelectric Energy Harvesting Systems. Energies 2023, 16, 2490. [Google Scholar]

- Abdul, H.; Edla, M.; Mustafa, U.; Fendy, S.; Deguchi, M. A Voltage Doubler Boost Converter Circuit for Piezoelectric Energy Harvesting Systems. Energies 2023, 16, 1631. [Google Scholar]

- Yuan, M.; Cao, Z.; Luo, J. Characterization the influences of diodes to piezoelectric energy harvester. Int. J. Smart Nano Mater. 2018, 9, 151–166. [Google Scholar] [CrossRef]

- Edla, M.; Lim, Y.Y.; Deguchi, M.; Padilla, R.V.; Izadgoshasb, I. An Improved Self-Powered H-Bridge Circuit for Voltage Rectification of Piezoelectric Energy Harvesting System. IEEE J. Electron Devices Soc. 2020, 8, 1050–1062. [Google Scholar] [CrossRef]

- Wen, N.; Fan, Z.; Yang, S.; Zhao, Y.; Cong, T.; Xu, S.; Zhang, H.; Wang, J.; Huang, H.; Li, C. Highly conductive, ultra-flexible and continuously processable PEDOT: PSS fibers with high thermoelectric properties for wearable energy harvesting. Nano Energy 2020, 78, 105361. [Google Scholar] [CrossRef]

- Naderipour, A.; Saboori, H.; Mehrjerdi, H.; Jadid, S.; Abdul-Malek, Z. Sustainable and reliable hybrid AC/DC microgrid planning considering technology choice of equipment. Sustain. Energy Grids Netw. 2020, 23, 100386. [Google Scholar] [CrossRef]

- Sedighi, M.; Padilla, R.V.; Alamdari, P.; Lake, M.; Rose, A.; Izadgoshasb, I.; Taylor, R.A. A novel high-temperature (>700 °C), volumetric receiver with a packed bed of transparent and absorbing spheres. Appl. Energy 2020, 264, 114705. [Google Scholar] [CrossRef]

- Shi, H.; Liu, Z.; Mei, X. Overview of Human Walking Induced Energy Harvesting Technologies and Its Possibility for Walking Robotics. Energies 2020, 13, 86. [Google Scholar] [CrossRef] [Green Version]

- Sharma, S.; Kiran, R.; Azad, P.; Vaish, R. A review of piezoelectric energy harvesting tiles: Available designs and future perspective. Energy Convers. Manag. 2022, 254, 115272. [Google Scholar] [CrossRef]

- Edla, M.; Lim, Y.Y.; Vasquez Padilla, R.; Deguchi, M. An Improved Rectifier Circuit for Piezoelectric Energy Harvesting from Human Motion. Appl. Sci. 2021, 11, 2008. [Google Scholar] [CrossRef]

- Arul, A.; Clarence, A.; Samuel, E.R. Efficiency Evaluation of a MOSFET bridge rectifier for Powering LEDs using Piezo-electric Energy Harvesting Systems. Automatika 2017, 57, 329–336. [Google Scholar]

- Maiorca, F.; Giusa, F.; Trigona, C.; Andò, B.; Bulsara, A.R.; Baglio, S. Diode-less mechanical H-bridge rectifier for “zero threshold” vibration energy harvesters. Sens. Actuators A Phys. 2013, 201, 246–253. [Google Scholar] [CrossRef]

- Edla, M.; Lim, Y.Y.; Padilla, R.V.; Mikio, D. Design and Application of a Self-Powered Dual-Stage Circuit for Piezoelectric Energy Harvesting Systems. IEEE Access 2021, 9, 86954–86965. [Google Scholar] [CrossRef]

- Salauddin, M.; Rana, S.S.; Sharifuzzaman, M.; Rahman, M.T.; Park, C.; Cho, H.; Maharjan, P.; Bhatta, T.; Park, J.Y. A Novel MXene/Ecoflex Nanocomposite-Coated Fabric as a Highly Negative and Stable Friction Layer for High-Output Triboelectric Nanogenerators. Adv. Energy Mater. 2021, 11, 2002832. [Google Scholar] [CrossRef]

- Shareef, A.; Goh, W.L.; Narasimalu, S.; Gao, Y. A rectifier-less ac–dc interface circuit for ambient energy harvesting from low-voltage piezoelectric transducer array. IEEE Trans. Power Electron. 2018, 34, 1446–1457. [Google Scholar] [CrossRef]

- Edla, M.; Lim, Y.Y.; Mikio, D.; Padilla, R.V. A Single-Stage Rectifier-Less Boost Converter Circuit for Piezoelectric Energy Harvesting Systems. IEEE Trans. Energy Convers. 2022, 37, 505–514. [Google Scholar] [CrossRef]

- Lefeuvre, E.; Audigier, D.; Richard, C.; Guyomar, D. Buck-Boost Converter for Sensorless Power Optimization of Piezoelectric Energy Harvester. IEEE Trans. Power Electron. 2007, 22, 2018–2025. [Google Scholar] [CrossRef]

- Azad, P. Design and analysis of a synchronized interface circuit for triboelectric energy harvesting. J. Electron. Mater. 2020, 49, 2491–2501. [Google Scholar]

- Eltamaly, A.M.; Addoweesh, K.E. A novel self-power SSHI circuit for piezoelectric energy harvester. IEEE Trans. Power Electron. 2017, 32, 7663–7673. [Google Scholar] [CrossRef]

- Lu, S.; Boussaid, F. A highly efficient P-SSHI rectifier for piezoelectric energy harvesting. IEEE Trans. Power Electron. 2015, 30, 5364–5369. [Google Scholar] [CrossRef] [Green Version]

- Dini, M.; Romani, A.; Filippi, M.; Tartagni, M. A nanopower synchronous charge extractor IC for low-voltage piezoelectric energy harvesting with residual charge inversion. IEEE Trans. Power Electron. 2015, 31, 1263–1274. [Google Scholar] [CrossRef]

- Xia, H.; Xia, Y.; Ye, Y.; Qian, L.; Shi, G.; Chen, R. Analysis and simulation of synchronous electric charge partial extraction technique for efficient piezoelectric energy harvesting. IEEE Sens. J. 2018, 18, 6235–6244. [Google Scholar] [CrossRef]

- Rashid, M.H. Power Electronics Handbook; Butterworth-Heinemann: Oxford, UK, 2017. [Google Scholar]

- Bimbhra, P.; Kaur, S. Power Electronics; Khanna Publishers: Delhi, India, 2012. [Google Scholar]

- Xia, H.; Xia, Y.; Shi, G.; Ye, Y.; Wang, X.; Chen, Z.; Jiang, Q. A Self-Powered S-SSHI and SECE Hybrid Rectifier for PE Energy Harvesters: Analysis and Experiment. IEEE Trans. Power Electron. 2020, 36, 1680–1692. [Google Scholar] [CrossRef]

- Tabesh, A.; Frechette, L.G. A Low-Power Stand-Alone Adaptive Circuit for Harvesting Energy From a Piezoelectric Micropower Generator. IEEE Trans. Ind. Electron. 2010, 57, 840–849. [Google Scholar] [CrossRef] [Green Version]

- Edla, M.; Lim, Y.Y.; Deguchi, M.; Padilla, R.V. A Novel Discontinuous Mode Piezoelectric Energy Harvesting Circuit for Low-Voltage Applications. In Proceedings of the 2021 31st Australasian Universities Power Engineering Conference (AUPEC), Perth, Australia, 26–30 September 2021; pp. 1–5. [Google Scholar]

- Yu, L.; Wang, H.; Khaligh, A. A discontinuous conduction mode single-stage step-up rectifier for low-voltage energy harvesting applications. IEEE Trans. Power Electron. 2016, 32, 6161–6169. [Google Scholar] [CrossRef]

- Ottman, G.K.; Hofmann, H.F.; Bhatt, A.C.; Lesieutre, G.A. Adaptive piezoelectric energy harvesting circuit for wireless remote power supply. IEEE Trans. Power Electron. 2002, 17, 669–676. [Google Scholar] [CrossRef] [Green Version]

- Chew, Z.J.; Zhu, M. Adaptive Maximum Power Point Finding Using Direct VOC/2 Tracking Method with Microwatt Power Consumption for Energy Harvesting. IEEE Trans. Power Electron. 2018, 33, 8164–8173. [Google Scholar] [CrossRef] [Green Version]

- Edla, M.; Deguchi, M.; Lim, Y.Y. A Self-Powered H-Bridge Joule Theory Circuit for Piezoelectric Energy Harvesting Systems. Power Electron. Devices Compon. 2022, 3, 100015. [Google Scholar] [CrossRef]

- Edla, M.; Lim, Y.Y. An Improved Piezoelectric Energy Harvesting Circuit for Reducing the Internal Loss. In Proceedings of the 83rd Researchfora International Conference, New Delhi, India, 29–30 January 2020. [Google Scholar]

- Edla, M.; Lim, Y.Y.; Mikio, D.; Ricardo Vasquez, P. Development of High-Efficiency Rectifier Circuits for Piezoelectric Energy Harvesting Systems. Ph.D. Thesis, Southern Cross University, Faculty of Science and Engineering, Lismore, Australia, 2022. [Google Scholar]

- Lee, H.-M.; Ghovanloo, M. An adaptive reconfigurable active voltage doubler/rectifier for extended-range inductive power transmission. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 481–485. [Google Scholar]

- Chen, Y.; Wang, C.; Guo, J. A Highly Adaptive and Flipping-Time Optimized Piezoelectric Energy Harvesting Interface IC with Synchronized Triple Bias-Flip. IEEE Trans. Power Electron. 2022, 37, 14981–14992. [Google Scholar] [CrossRef]

- Gao, L.; Teng, L.; Fu, M.; Wang, H.; Liang, J. A Switched-mode Self-sensing Solution for Piezoelectric Synchronous Electric Charge Extraction (SECE). IEEE Trans. Ind. Electron. 2022, 70, 7457–7466. [Google Scholar] [CrossRef]

- Qi, N.; Dai, K.; Wang, X.; You, Z. Adaptive Capacitor Charging Circuit with Simplified Configuration for Efficient Piezoelectric Energy Harvesting. IEEE Trans. Power Electron. 2022, 37, 10267–10280. [Google Scholar] [CrossRef]

- De Pasquale, G.; Fraccarollo, F.; Somà, A. Performances evaluation of an autonomous sensing network node for rail vehicles supplied by a piezoelectric energy harvester. In Proceedings of the 10th International Workshop on Micro and Nanotechnology for Power Generation and Energy Conversion Applications, Leuven, Belgium, 30 November–3 December 2010; pp. 73–76. [Google Scholar]

- Liu, M.; Shen, H.; Luan, H. A new multi-piezoelectric input synchronized switch harvesting on inductor circuit. Ferroelectrics 2023, 606, 13–22. [Google Scholar] [CrossRef]

- Ben Ammar, M.; Sahnoun, S.; Fakhfakh, A.; Viehweger, C.; Kanoun, O. Self-Powered Synchronized Switching Interface Circuit for Piezoelectric Footstep Energy Harvesting. Sensors 2023, 23, 1830. [Google Scholar] [CrossRef]

- Zeng, W.; Shi, G.; Hu, X.; Shi, Z.; Pan, J.; Sun, Q.; Jia, S.; Han, J. A self-powered P–SSHI and boost hybrid interface circuit for Multi-PZTs and low voltage electromagnetic energy extraction. Microelectron. J. 2023, 135, 105745. [Google Scholar] [CrossRef]

- Mair, D.; Ferdik, M.; Happ, C.; Renzler, M.; Ussmueller, T. Numerical Optimization of a Fully Cross-Coupled Rectifier Circuit for Wireless Passive Ultra Low Power Sensor Nodes. Sensors 2019, 19, 4527. [Google Scholar] [CrossRef] [PubMed] [Green Version]

| Similar Circuits | Components–Quantity | |||||||

|---|---|---|---|---|---|---|---|---|

| Diodes | MOSFETs | Switch Drivers | Additional ICs | Inductors | Load Capacitors | Load Resistors | Auxiliary Circuits | |

| FBR [32] | 4 (0.67 Vf) | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| Dual-stage buck-boost converter [25] | 5 | 1 | 1 | 1 | 1 | 3 | 1 | 0 |

| SSRBC [24] | 3 | 4 | 2 | 0 | 2 | 1 | 1 | 1 |

| Hybrid rectifier [33] | 3 | 4 | 1 | 0 | 2 | 1 | 1 | 0 |

| Proposed VDJT | 2 | 1 | 0 | 0 | 2 | 1 | 1 | 0 |

| Scenarios | Frequency (Hz) | Input Voltage V ac (V) | Load Capacitor (µF) | Load Resistor (kΩ) |

|---|---|---|---|---|

| Test 1 | 2, 5 | 5, 10, 15 | 10 | 10–70 |

| Test 2 | 10, 15, 20, 25, 30 | 1 |

| Literature Circuits | No. of PGs | Acceleration (g: m/s2) | Input Voltage (V) | Input Power (µW) | Output Power (µW) |

|---|---|---|---|---|---|

| [34] | 1 | - | 8 | 480 | 800 |

| [25] (similar circuit) | 1 | 1.5 | Frequency | 1100 | |

| 66 (resonance) | Not mentioned | ||||

| [7] (similar circuit) | 1 | 1.5 | 10 (not resonance) | 4901 | 3410 |

| [39] (similar circuit) | 1 | - | 3 | 676 | 520 |

| [46] | 1 | - | 10 | 900 | 195 |

| [47] | 1 | - | 8.6 | 238 | 167.2 |

| [48] | 1 | - | 4.2 | 2905 | 2000 |

| [49] | 1 | - | 1.5 | 10,756 | 6800 |

| [21] | 1 | - | 10 | - | 84.2 |

| [39] | 1 | - | 3 | - | 510 |

| VDJT | 1 | - | 15 | 7600 | 5500 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kamran, M.; Edla, M.; Thabet, A.M.; Mikio, D.; Bui, V. A Self-Powered VDJT AC–DC Conversion Circuit for Piezoelectric Energy Harvesting Systems. Designs 2023, 7, 94. https://doi.org/10.3390/designs7040094

Kamran M, Edla M, Thabet AM, Mikio D, Bui V. A Self-Powered VDJT AC–DC Conversion Circuit for Piezoelectric Energy Harvesting Systems. Designs. 2023; 7(4):94. https://doi.org/10.3390/designs7040094

Chicago/Turabian StyleKamran, Muhammad, Mahesh Edla, Ahmed Mostafa Thabet, Deguchi Mikio, and Vinh Bui. 2023. "A Self-Powered VDJT AC–DC Conversion Circuit for Piezoelectric Energy Harvesting Systems" Designs 7, no. 4: 94. https://doi.org/10.3390/designs7040094