Area-Efficient Mixed-Signal Time-to-Digital Converter Integration for Time-Resolved Photon Counting

Abstract

:1. Introduction

2. Materials and Methods

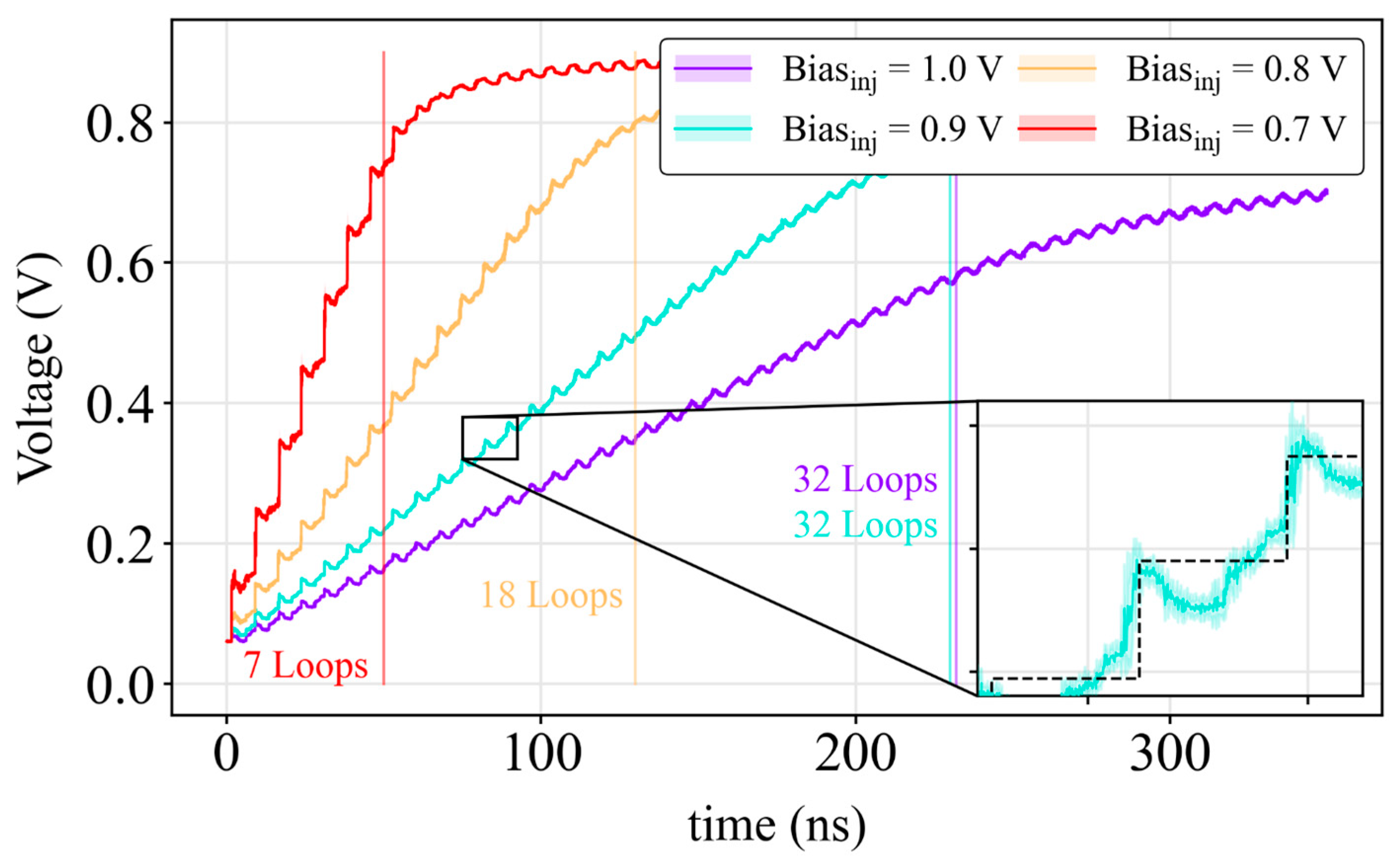

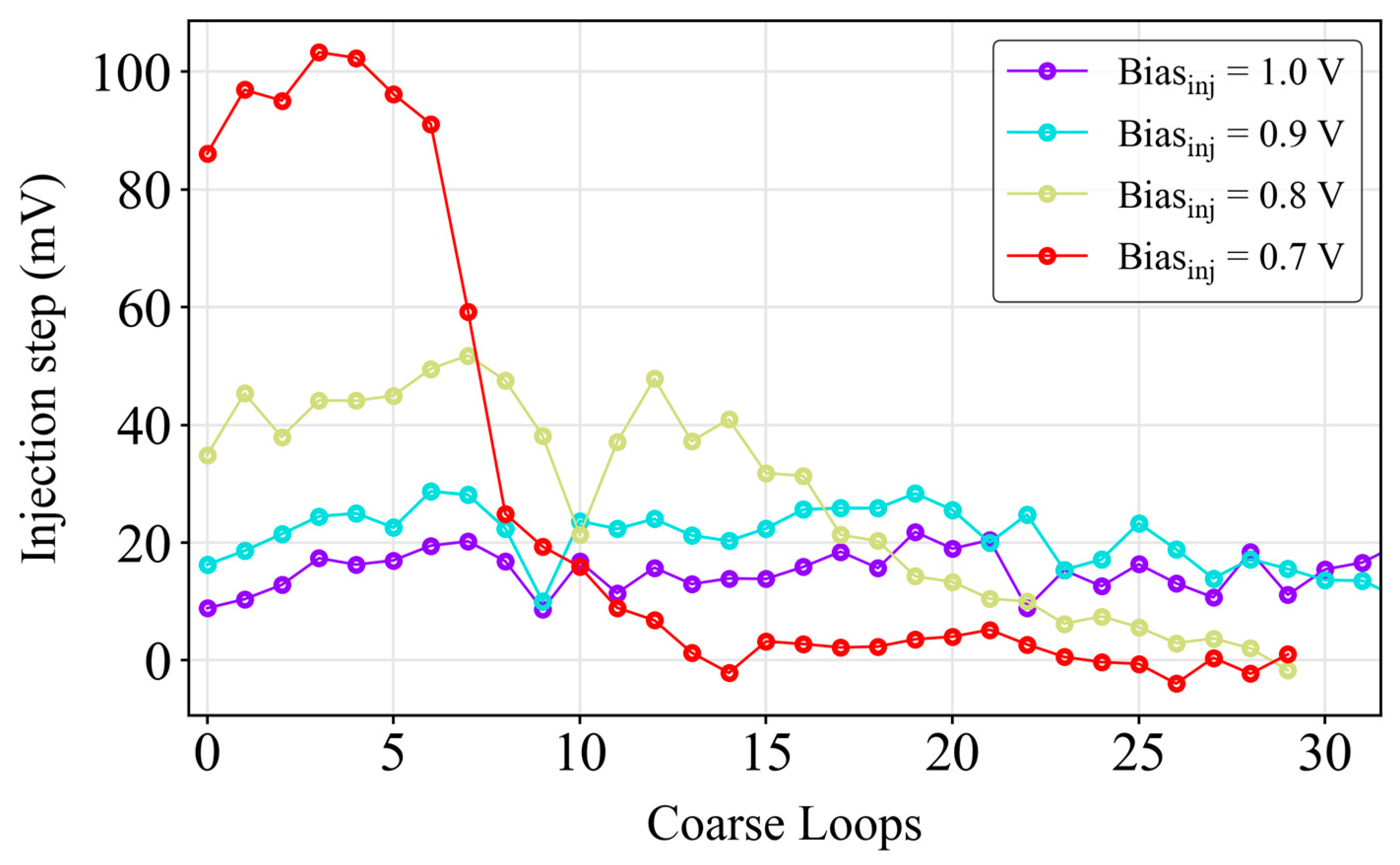

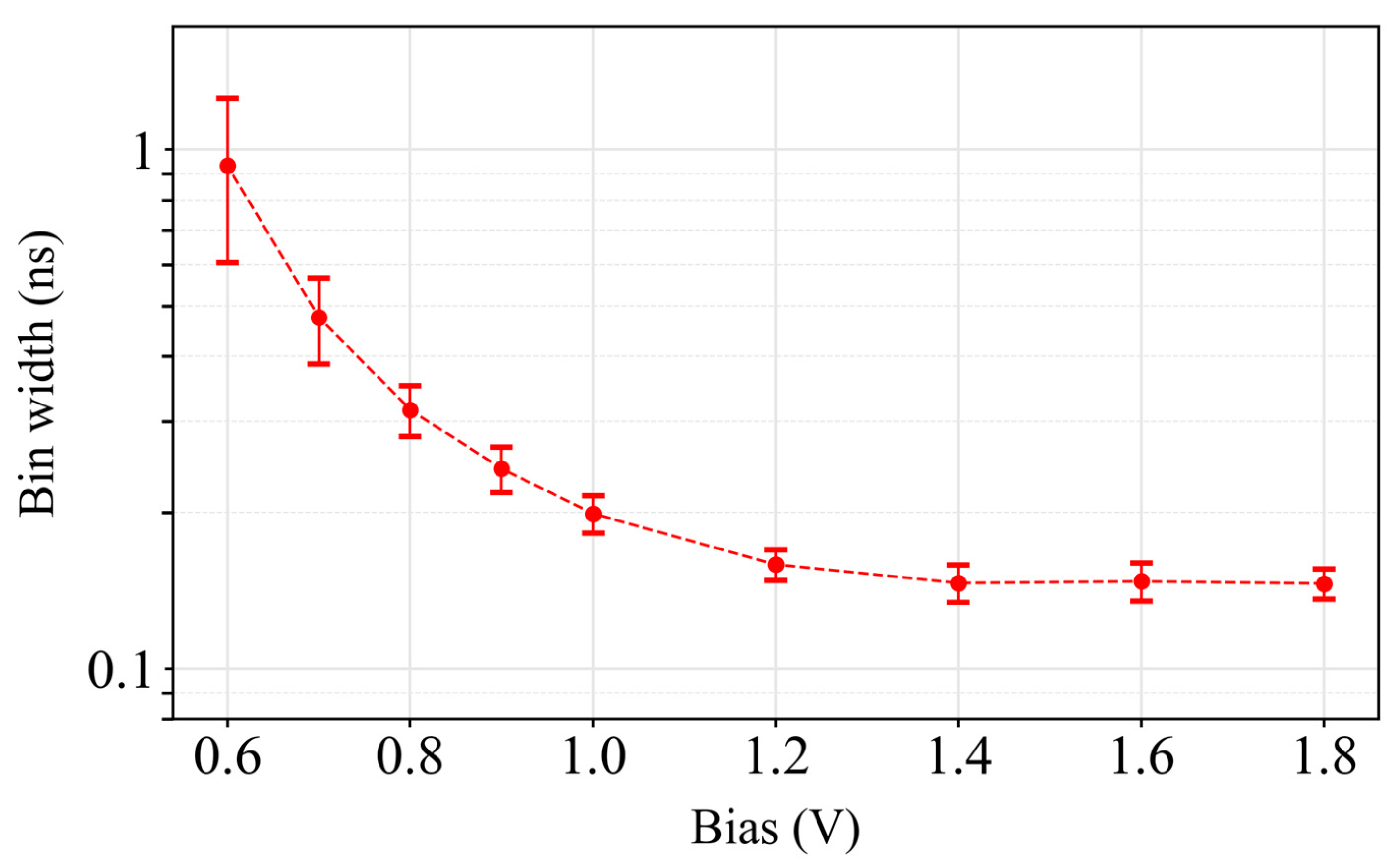

2.1. Design Description

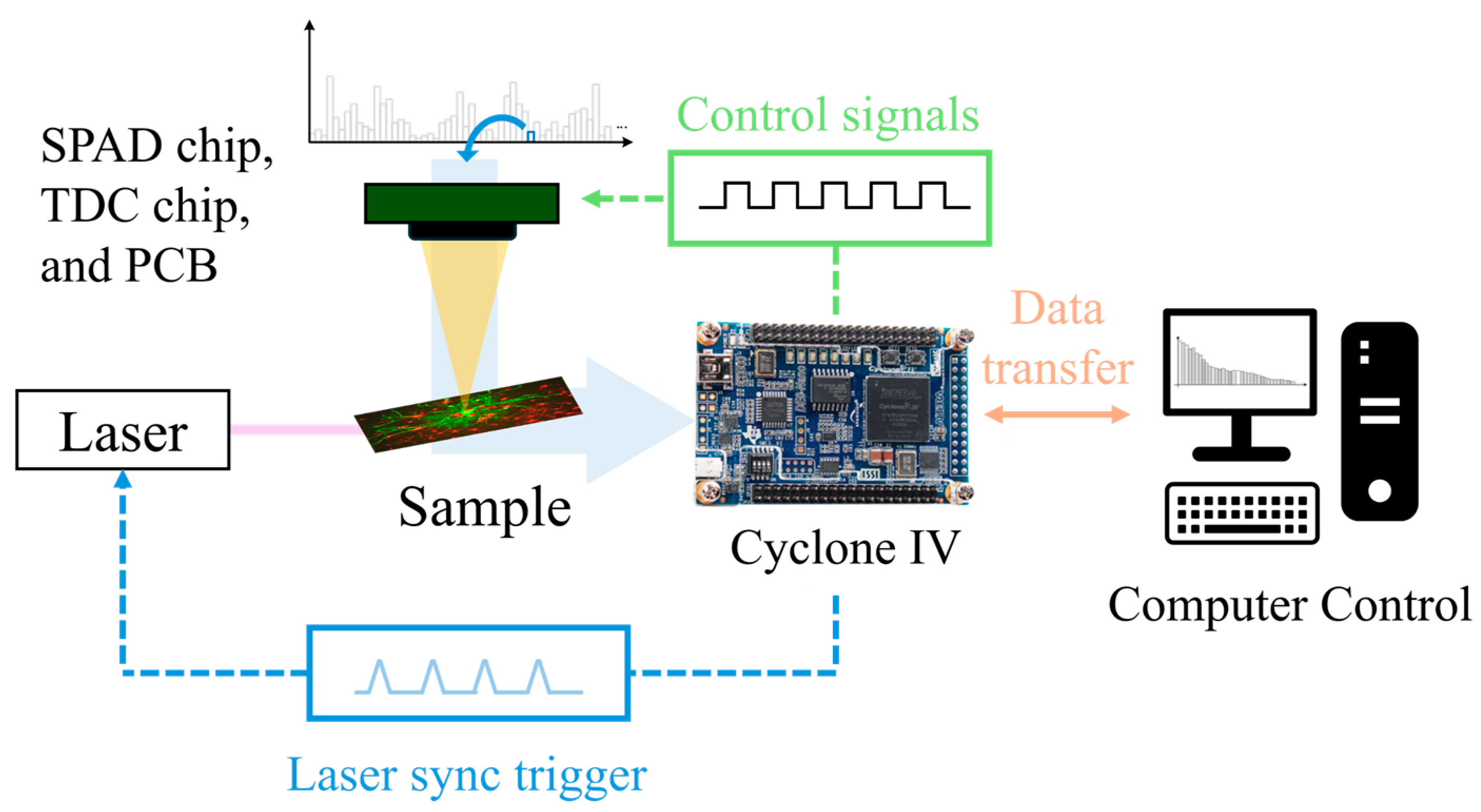

2.2. Experimental Characterization

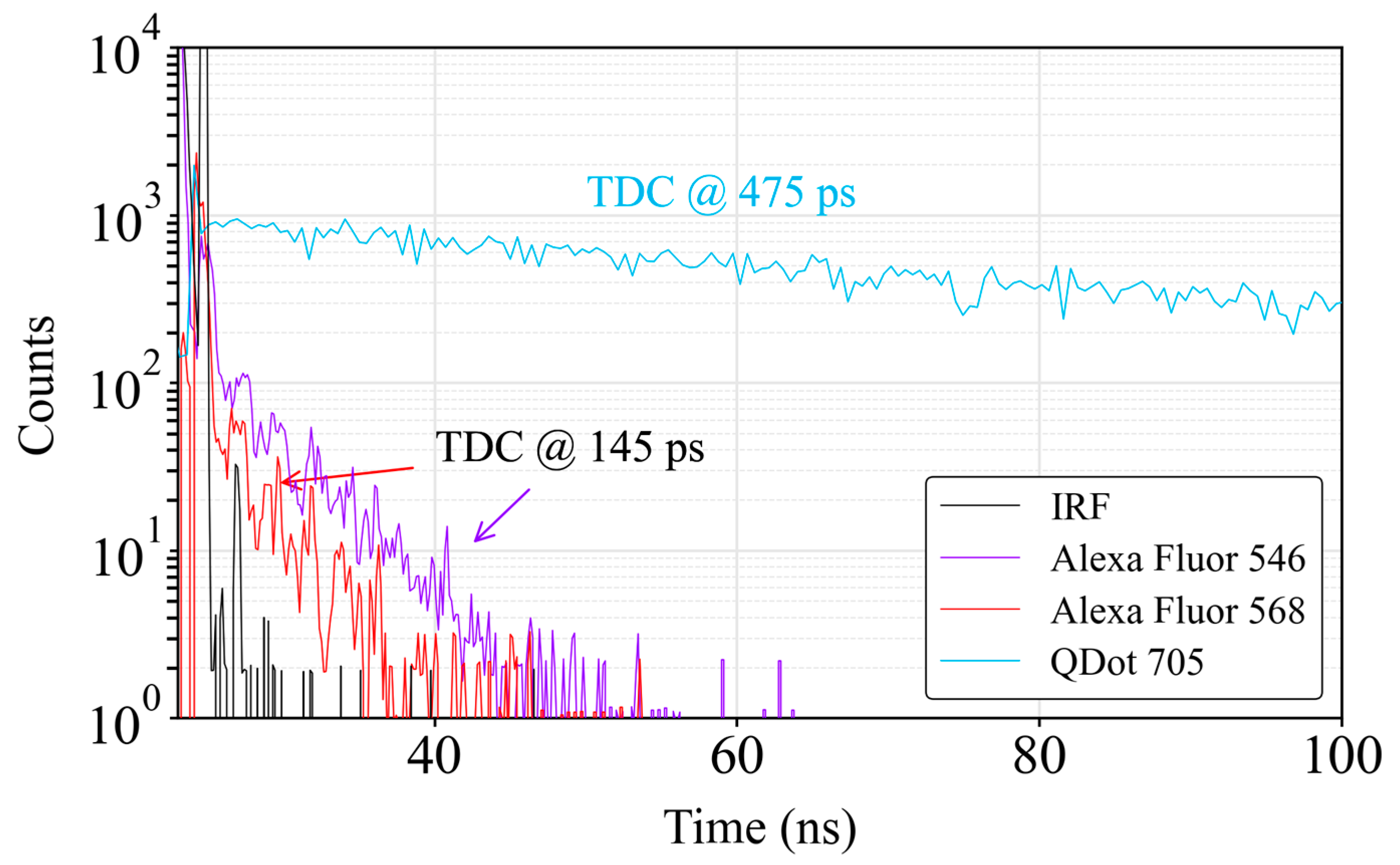

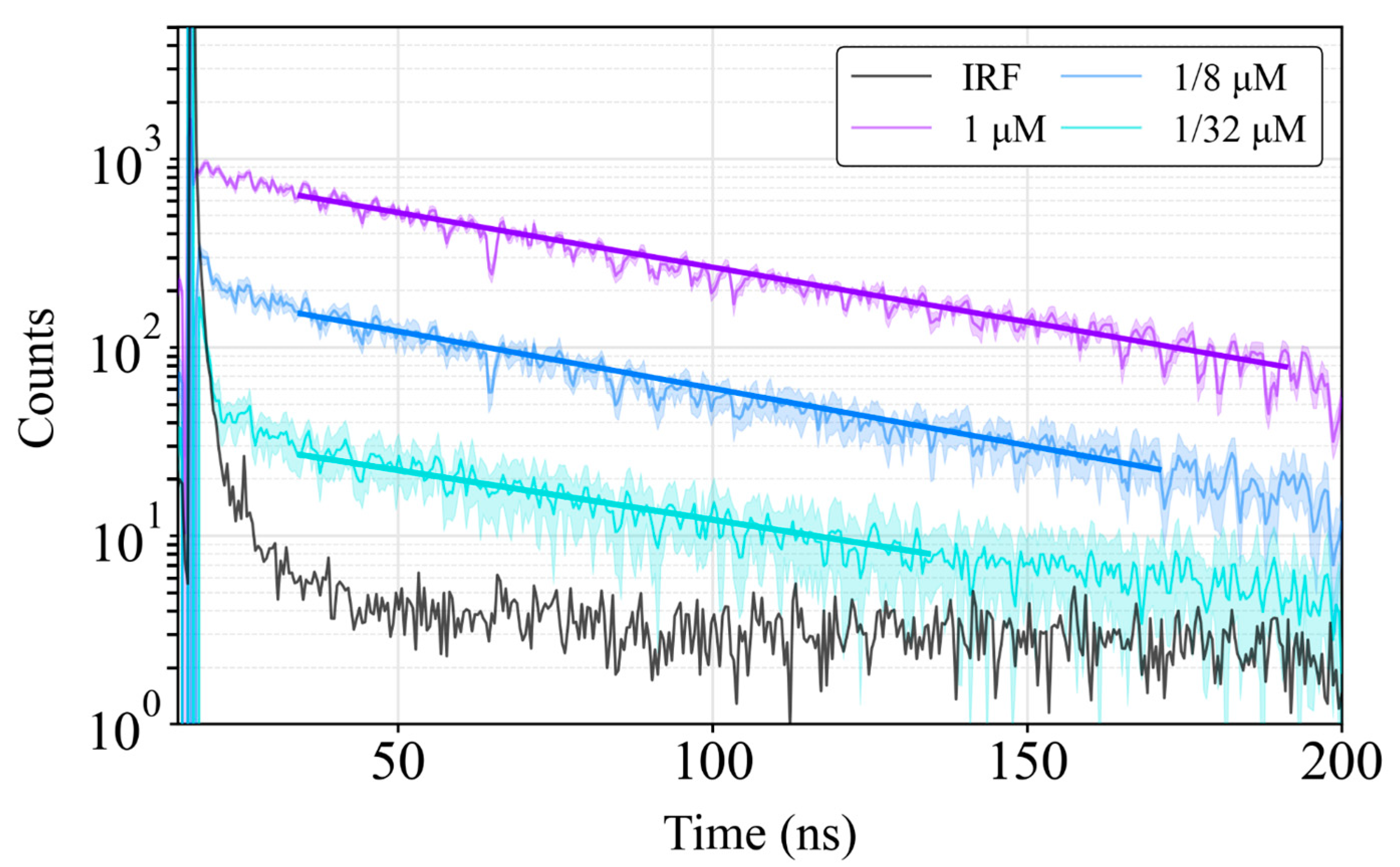

3. Results

Validation Experiments for a Fluorescence-Based Point-of-Care Device

4. Discussion

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Yokota, H.; Fukasawa, A.; Hirano, M.; Ide, T. Low-Light Photodetectors for Fluorescence Microscopy. Appl. Sci. 2021, 11, 2773. [Google Scholar] [CrossRef]

- Ghezzi, A.; Farina, A.; Bassi, A.; Valentini, G.; Labanca, I.; Acconcia, G.; Rech, I.; D’Andrea, C. Multispectral Compressive Fluorescence Lifetime Imaging Microscopy with a SPAD Array Detector. Opt. Lett. 2021, 46, 1353. [Google Scholar] [CrossRef] [PubMed]

- Zickus, V.; Wu, M.-L.; Morimoto, K.; Kapitany, V.; Fatima, A.; Turpin, A.; Insall, R.; Whitelaw, J.; Machesky, L.; Bruschini, C.; et al. Fluorescence Lifetime Imaging with a Megapixel SPAD Camera and Neural Network Lifetime Estimation. Sci. Rep. 2020, 10, 20986. [Google Scholar] [CrossRef] [PubMed]

- Smith, J.T.; Rudkouskaya, A.; Gao, S.; Gupta, J.M.; Ulku, A.; Bruschini, C.; Charbon, E.; Weiss, S.; Barroso, M.; Intes, X.; et al. In Vitro and In Vivo NIR Fluorescence Lifetime Imaging with a Time-Gated SPAD Camera. Optica 2022, 9, 532. [Google Scholar] [CrossRef]

- Xiao, D.; Zang, Z.; Wang, Q.; Jiao, Z.; Della Rocca, F.M.; Chen, Y.; Li, D.D.U. Smart Wide-Field Fluorescence Lifetime Imaging System with CMOS Single-Photon Avalanche Diode Arrays. In Proceedings of the 2022 44th Annual International Conference of the IEEE Engineering in Medicine & Biology Society (EMBC), Glasgow, Scotland, 11–15 September 2022; IEEE: Piscataway, NJ, USA, 2022; pp. 1887–1890. [Google Scholar]

- Erdogan, A.T.; Al Abbas, T.; Finlayson, N.; Hopkinson, C.; Gyongy, I.; Almer, O.; Dutton, N.A.W.; Henderson, R.K. A High Dynamic Range 128 × 120 3-D Stacked CMOS SPAD Image Sensor SoC for Fluorescence Microendoscopy. IEEE J. Solid-State Circuits 2022, 57, 1649–1660. [Google Scholar] [CrossRef]

- Talala, T.; Kaikkonen, V.A.; Keranen, P.; Nikkinen, J.; Harkonen, A.; Savitski, V.G.; Reilly, S.; Dziechciarczyk, U.; Kemp, A.J.; Guina, M.; et al. Time-Resolved Raman Spectrometer With High Fluorescence Rejection Based on a CMOS SPAD Line Sensor and a 573-Nm Pulsed Laser. IEEE Trans. Instrum. Meas. 2021, 70, 6004110. [Google Scholar] [CrossRef]

- Talala, T.; Parkkinen, E.; Nissinen, I. CMOS SPAD Line Sensor With Fine-Tunable Parallel Connected Time-to-Digital Converters for Raman Spectroscopy. IEEE J. Solid-State Circuits 2023, 58, 1350–1361. [Google Scholar] [CrossRef]

- Bruschini, C.E.; Charbon, E. A Review of Recent Developments on CMOS Single-Photon Avalanche Diode-Based Cameras for Biomedical Time-Resolved Applications. In Proceedings of the Reporters, Markers, Dyes, Nanoparticles, and Molecular Probes for Biomedical Applications XV, San Francisco, CA, USA, 30–31 January 2024; Raghavachari, R., Berezin, M.Y., Eds.; SPIE: Bellingham, WA, USA, 2024; p. 25. [Google Scholar]

- Dalla Mora, A.; Tosi, A.; Zappa, F.; Cova, S.; Contini, D.; Pifferi, A.; Spinelli, L.; Torricelli, A.; Cubeddu, R. Fast-Gated Single-Photon Avalanche Diode for Wide Dynamic Range Near Infrared Spectroscopy. IEEE J. Sel. Top. Quantum Electron. 2010, 16, 1023–1030. [Google Scholar] [CrossRef]

- Bruschini, C.; Homulle, H.; Antolovic, I.M.; Burri, S.; Charbon, E. Single-Photon Avalanche Diode Imagers in Biophotonics: Review and Outlook. Light. Sci. Appl. 2019, 8, 87. [Google Scholar] [CrossRef]

- Palubiak, D.; El-Desouki, M.M.; Marinov, O.; Deen, M.J.; Fang, Q. High-Speed, Single-Photon Avalanche-Photodiode Imager for Biomedical Applications. IEEE Sens. J. 2011, 11, 2401–2412. [Google Scholar] [CrossRef]

- Hirvonen, L.M.; Suhling, K. Wide-Field TCSPC: Methods and Applications. Meas. Sci. Technol. 2017, 28, 012003. [Google Scholar] [CrossRef]

- Wang, Z.; Huang, C.; Wu, J. A review of cmos time-to-digital converter. J. Circuits Syst. Comput. 2014, 23, 1430001. [Google Scholar] [CrossRef]

- Villa, F.; Lussana, R.; Bronzi, D.; Tisa, S.; Tosi, A.; Zappa, F.; Dalla Mora, A.; Contini, D.; Durini, D.; Weyers, S.; et al. CMOS Imager with 1024 SPADs and TDCs for Single-Photon Timing and 3-D Time-of-Flight. IEEE J. Sel. Top. Quantum Electron. 2014, 20, 364–373. [Google Scholar] [CrossRef]

- Niclass, C.; Favi, C.; Kluter, T.; Gersbach, M.; Charbon, E. A 128 × 128 Single-Photon Image Sensor With Column-Level 10-Bit Time-to-Digital Converter Array. IEEE J. Solid-State Circuits 2008, 43, 2977–2989. [Google Scholar] [CrossRef]

- Tancock, S.; Arabul, E.; Dahnoun, N. A Review of New Time-to-Digital Conversion Techniques. IEEE Trans. Instrum. Meas. 2019, 68, 3406–3417. [Google Scholar] [CrossRef]

- Mattada, M.P.; Guhilot, H. Time-to-digital Converters—A Comprehensive Review. Int. J. Circuit Theory Appl. 2021, 49, 778–800. [Google Scholar] [CrossRef]

- Machado, R.; Cabral, J.; Alves, F.S. Recent Developments and Challenges in FPGA-Based Time-to-Digital Converters. IEEE Trans. Instrum. Meas. 2019, 68, 4205–4221. [Google Scholar] [CrossRef]

- Zhang, C.; Lindner, S.; Antolovic, I.M.; Mata Pavia, J.; Wolf, M.; Charbon, E. A 30-Frames/s, 252 × 144 SPAD Flash LiDAR With 1728 Dual-Clock 48.8-Ps TDCs, and Pixel-Wise Integrated Histogramming. IEEE J. Solid-State Circuits 2019, 54, 1137–1151. [Google Scholar] [CrossRef]

- Arvani, F.; Carusone, T.C.; Rogers, E.S. TDC Sharing in SPAD-Based Direct Time-of-Flight 3D Imaging Applications. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; IEEE: Piscataway, NJ, USA, 2019; pp. 1–5. [Google Scholar]

- Field, R.M.; Realov, S.; Shepard, K.L. A 100 Fps, Time-Correlated Single-Photon-Counting-Based Fluorescence-Lifetime Imager in 130 Nm CMOS. IEEE J. Solid-State Circuits 2014, 49, 867–880. [Google Scholar] [CrossRef]

- Villa, F.; Markovic, B.; Bellisai, S.; Bronzi, D.; Tosi, A.; Zappa, F.; Tisa, S.; Durini, D.; Weyers, S.; Paschen, U.; et al. SPAD Smart Pixel for Time-of-Flight and Time-Correlated Single-Photon Counting Measurements. IEEE Photonics J. 2012, 4, 795–804. [Google Scholar] [CrossRef]

- Perenzoni, M.; Massari, N.; Gasparini, L.; Garcia, M.M.; Perenzoni, D.; Stoppa, D. A Fast 50 × 40-Pixels Single-Point DTOF SPAD Sensor With Photon Counting and Programmable ROI TDCs, With σ < 4 Mm at 3 m up to 18 Klux of Background Light. IEEE Solid-State Circuits Lett. 2020, 3, 86–89. [Google Scholar] [CrossRef]

- Henderson, R.K.; Johnston, N.; Chen, H.; Li, D.D.-U.; Hungerford, G.; Hirsch, R.; McLoskey, D.; Yip, P.; Birch, D.J.S. A 192 × 128 Time Correlated Single Photon Counting Imager in 40 nm CMOS Technology. In Proceedings of the ESSCIRC 2018—IEEE 44th European Solid State Circuits Conference (ESSCIRC), Dresden, Germany, 3–6 September 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 54–57. [Google Scholar]

- Erdogan, A.T.; Walker, R.; Finlayson, N.; Krstajic, N.; Williams, G.; Girkin, J.; Henderson, R. A CMOS SPAD Line Sensor With Per-Pixel Histogramming TDC for Time-Resolved Multispectral Imaging. IEEE J. Solid-State Circuits 2019, 54, 1705–1719. [Google Scholar] [CrossRef]

- Panina, E.; Pancheri, L.; Dalla Betta, G.-F.; Massari, N.; Stoppa, D. Compact CMOS Analog Counter for SPAD Pixel Arrays. IEEE Trans. Circuits Syst. II Express Briefs 2014, 61, 214–218. [Google Scholar] [CrossRef]

- Dieguez, A.; Canals, J.; Franch, N.; Dieguez, J.; Alonso, O.; Vila, A. A Compact Analog Histogramming SPAD-Based CMOS Chip for Time-Resolved Fluorescence. IEEE Trans. Biomed. Circuits Syst. 2019, 13, 343–351. [Google Scholar] [CrossRef] [PubMed]

- Pancheri, L.; Massari, N.; Stoppa, D. SPAD Image Sensor With Analog Counting Pixel for Time-Resolved Fluorescence Detection. IEEE Trans. Electron Devices 2013, 60, 3442–3449. [Google Scholar] [CrossRef]

- Rajalingam, P.; Jayakumar, S.; Routray, S. Design and Analysis of Low Power and High Frequency Current Starved Sleep Voltage Controlled Oscillator for Phase Locked Loop Application. Silicon 2021, 13, 2715–2726. [Google Scholar] [CrossRef]

- AD7274. Available online: https://www.mouser.es/ProductDetail/Analog-Devices/AD7274?qs=%252BEew9%252B0nqrDFn8D0j2eBuw%3D%3D (accessed on 23 July 2024).

- DE0-Nano Development and Education Board. Available online: https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&No=593 (accessed on 23 July 2024).

- Sui, T.; Zhao, Z.; Xie, S.; Xie, Y.; Zhao, Y.; Huang, Q.; Xu, J.; Peng, Q. A 2.3-Ps RMS Resolution Time-to-Digital Converter Implemented in a Low-Cost Cyclone V FPGA. IEEE Trans. Instrum. Meas. 2019, 68, 3647–3660. [Google Scholar] [CrossRef]

- Tian, Y.; Yan, W.; Wei, L.; Ho, D. Low Detection Limit Time-Correlated Single Photon Counting Lifetime Analytical System for Point-of-Care Applications. IEEE Access 2019, 7, 18256–18266. [Google Scholar] [CrossRef]

- Thapa, P.; Singh, V.; Gupta, K.; Shrivastava, A.; Kumar, V.; Kataria, K.; Mishra, P.R.; Mehta, D.S. Point-of-care Devices Based on Fluorescence Imaging and Spectroscopy for Tumor Margin Detection during Breast Cancer Surgery: Towards Breast Conservation Treatment. Lasers Surg. Med. 2023, 55, 423–436. [Google Scholar] [CrossRef]

- Franch Masdeu, N. Development of a Nano-Illumination Microscope. Ph.D. Thesis, Universitat de Barcelona, Barcelona, Spain, 2022. [Google Scholar]

- Canals, J.; Franch, N.; Alonso, O.; Vilà, A.; Diéguez, A. A Point-of-Care Device for Molecular Diagnosis Based on CMOS SPAD Detectors with Integrated Microfluidics. Sensors 2019, 19, 445. [Google Scholar] [CrossRef]

- Laser Diodes Green Laser Diode 520 nm, 30 mW. Available online: https://eu.mouser.com/ProductDetail/ams-OSRAM/PL-520_B1_2?qs=P%252BGkiCIryJuOxJrFamAdJQ%3D%3D (accessed on 10 May 2024).

- Μ-Slide I Luer Glass Bottom. Available online: https://ibidi.com/channel-slides/244-4645--slide-i-luer-glass-bottom.html#/29-surface_modification-15h_170_%C2%B5m_5_%C2%B5m_d_263_m_schott_glass_sterilized/33-pcs_box-15_individually_packed/318-channel_version_channel_height-02_channel_height_250_%C2%B5m (accessed on 10 May 2024).

- Streptavidin, Alexa FluorTM 546 Conjugate. Available online: https://www.thermofisher.com/order/catalog/product/S11225?SID=srch-srp-S11225 (accessed on 10 May 2024).

- Streptavidin, Alexa FluorTM 568 Conjugate. Available online: https://www.thermofisher.com/order/catalog/product/es/en/S11226 (accessed on 31 August 2024).

- QdotTM 705 ITKTM Amino (PEG) Quantum Dots. Available online: https://www.thermofisher.com/order/catalog/product/Q21561MP?SID=srch-srp-Q21561MP (accessed on 19 March 2024).

- Fluorescence Quantum Yields (QY) and Lifetimes (τ) for Alexa Fluor Dyes. Available online: https://www.thermofisher.com/es/en/home/references/molecular-probes-the-handbook/tables/fluorescence-quantum-yields-and-lifetimes-for-alexa-fluor-dyes.html (accessed on 16 May 2024).

- Holton, M.D.; Silvestre, O.F.; Errington, R.J.; Smith, P.J.; Rees, P.; Summers, H.D. Fluorescence Lifetime Based Contrast Imaging Using Variable Period Excitation Pulse Trains. In Proceedings of the Multiphoton Microscopy in the Biomedical Sciences IX, San Jose, CA, USA, 24–29 January 2009; Periasamy, A., So, P.T.C., Eds.; SPIE: Bellingham, WA, USA, 2009; p. 718321. [Google Scholar]

- Resch-Genger, U.; Grabolle, M.; Cavaliere-Jaricot, S.; Nitschke, R.; Nann, T. Quantum Dots versus Organic Dyes as Fluorescent Labels. Nat. Methods 2008, 5, 763–775. [Google Scholar] [CrossRef]

- Veerappan, C.; Richardson, J.; Walker, R.; Li, D.-U.; W Fishburn, M.; Maruyama, Y.; Stoppa, D.; Borghetti, F.; Gersbach, M.; K Henderson, R.; et al. A 160×128 Single-Photon Image Sensor with on-Pixel 55ps 10b Time-to-Digital Converter. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011; IEEE: Piscataway, NJ, USA, 2011; pp. 312–314. [Google Scholar]

- Gersbach, M.; Maruyama, Y.; Trimananda, R.; Fishburn, M.W.; Stoppa, D.; Richardson, J.A.; Walker, R.; Henderson, R.; Charbon, E. A Time-Resolved, Low-Noise Single-Photon Image Sensor Fabricated in Deep-Submicron CMOS Technology. IEEE J. Solid-State Circuits 2012, 47, 1394–1407. [Google Scholar] [CrossRef]

- Seo, H.; Choi, J. Histogram-based Mixed-signal Time-to-digital-converter Array for Direct Time-of-flight Depth Sensors. Electron. Lett. 2019, 55, 310–312. [Google Scholar] [CrossRef]

- Zarghami, M.; Gasparini, L.; Parmesan, L.; Moreno-Garcia, M.; Stefanov, A.; Bessire, B.; Unternahrer, M.; Perenzoni, M. A 32 × 32-Pixel CMOS Imager for Quantum Optics with Per-SPAD TDC, 19.48% Fill-Factor in a 44.64-Μm Pitch Reaching 1-MHz Observation Rate. IEEE J. Solid-State Circuits 2020, 55, 2819–2830. [Google Scholar] [CrossRef]

- Gao, L.; Ma, Y.; Huang, L.; Sen, C.; Burri, S.; Polytechnique, E.; De Lausanne, F.; Bruschini, C.; Yang, X.; Cameron, R.; et al. Light-Eld Tomographic Uorescence Lifetime Imaging Microscopy. Res. Sq. 2023. [Google Scholar] [CrossRef]

- Bronzi, D.; Villa, F.; Tisa, S.; Tosi, A.; Zappa, F. SPAD Figures of Merit for Photon-Counting, Photon-Timing, and Imaging Applications: A Review. IEEE Sens. J. 2016, 16, 3–12. [Google Scholar] [CrossRef]

| Reference | [46] | [47] | [48] | [49] | This Work |

|---|---|---|---|---|---|

| CMOS Technology (nm) | 130 | 130 | 180 | 150 | 150 |

| Year | 2011 | 2012 | 2019 | 2020 | 2024 |

| Area (µm2) | 2244 | 2000 | 6000 | 402.7 | 699.9 a |

| Norm. for Process (a.u.) b | 132.8 k | 118.3 k | 185.2 k | 17.9 k | 31.1 k |

| DNLp-p (LSB) | 0.6 | 0.4 | 1.26 | 1.28 | 0.37 |

| INLp-p (LSB) | 4 | 1.2 | 1.23 | 1.92 | 0.54 |

| Resolution (ps) | 55 | 119 | 417 | 210 | 145–931 |

| Depth (bits) | 7 (coarse) 3 (fine) | 6 (coarse) 4 (fine) | 9 (coarse) 3 (fine) | 6 (coarse) 2 (fine) | 5 (coarse) 4 (fine) |

| Range (ns) | 55 | 100 | - | 53 | 74–477 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Moreno, S.; Moro, V.; Canals, J.; Diéguez, A. Area-Efficient Mixed-Signal Time-to-Digital Converter Integration for Time-Resolved Photon Counting. Sensors 2024, 24, 5763. https://doi.org/10.3390/s24175763

Moreno S, Moro V, Canals J, Diéguez A. Area-Efficient Mixed-Signal Time-to-Digital Converter Integration for Time-Resolved Photon Counting. Sensors. 2024; 24(17):5763. https://doi.org/10.3390/s24175763

Chicago/Turabian StyleMoreno, Sergio, Victor Moro, Joan Canals, and Angel Diéguez. 2024. "Area-Efficient Mixed-Signal Time-to-Digital Converter Integration for Time-Resolved Photon Counting" Sensors 24, no. 17: 5763. https://doi.org/10.3390/s24175763