A Fabrication Method for Realizing Vertically Aligned Silicon Nanowires Featuring Precise Dimension Control

Abstract

1. Introduction

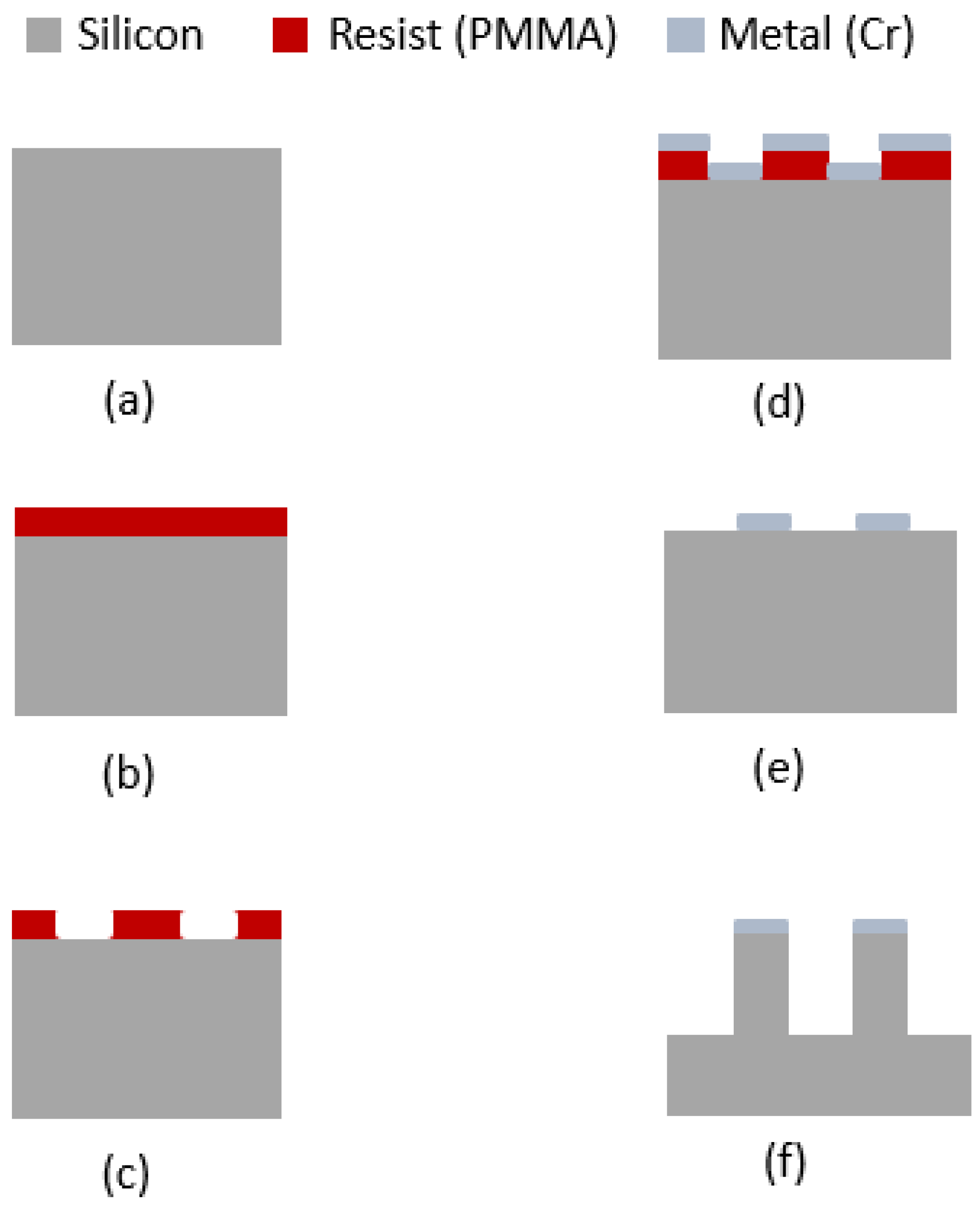

2. Materials and Methods

- (a)

- Group 1: Matrix of 200 nm diameter circles with 200 nm inter-nanowire spacing.

- (b)

- Group 2: Matrix of 400 nm diameter circles with 400 nm inter-nanowire spacing.

- (c)

- Group 3: Matrix of 600 nm diameter circles with 600 nm inter-nanowire spacing.

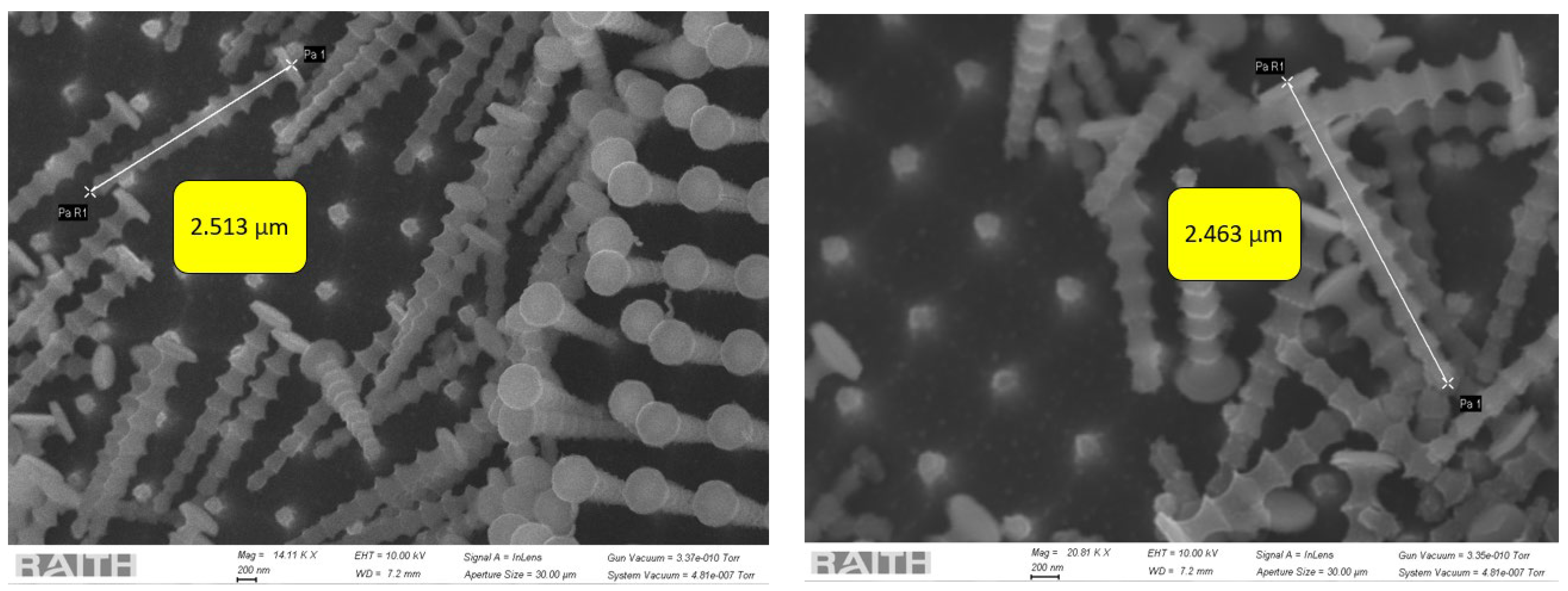

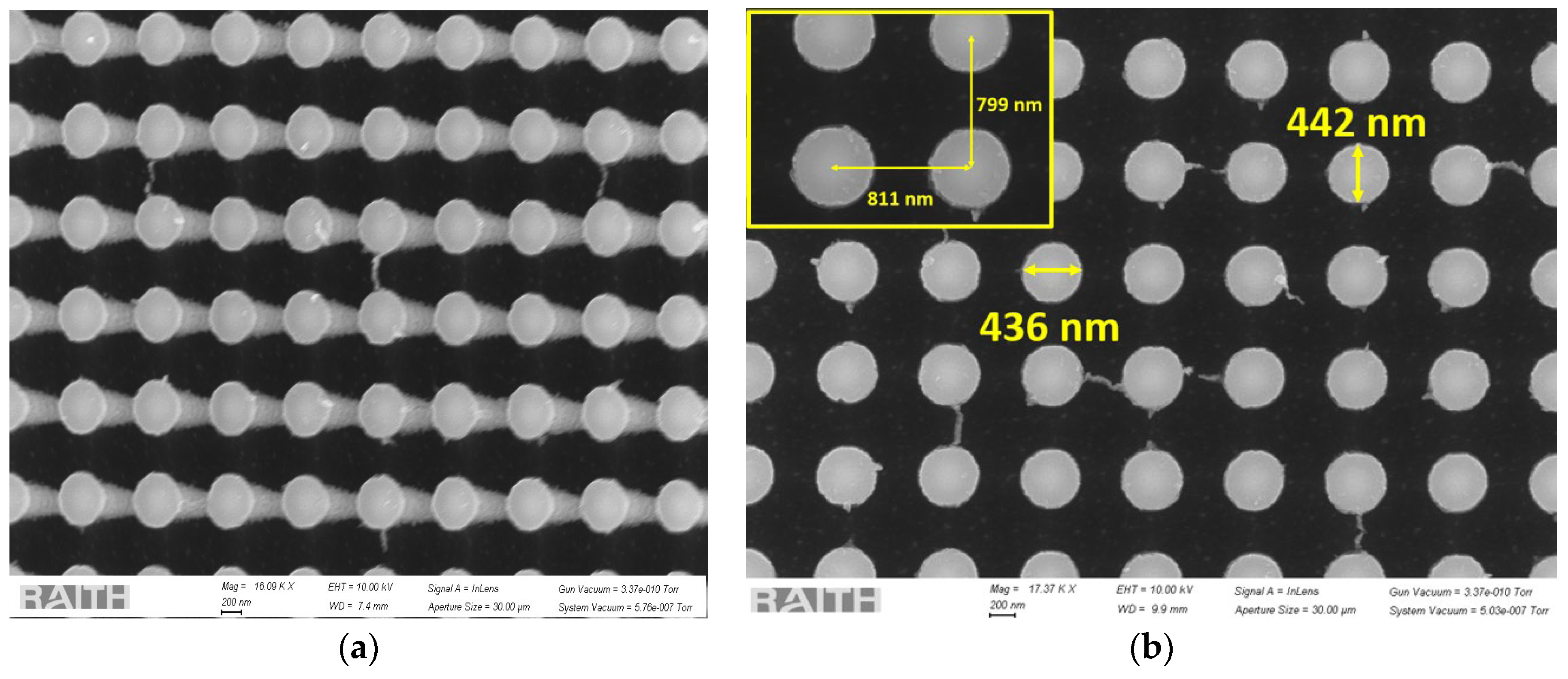

3. Characterization and Results

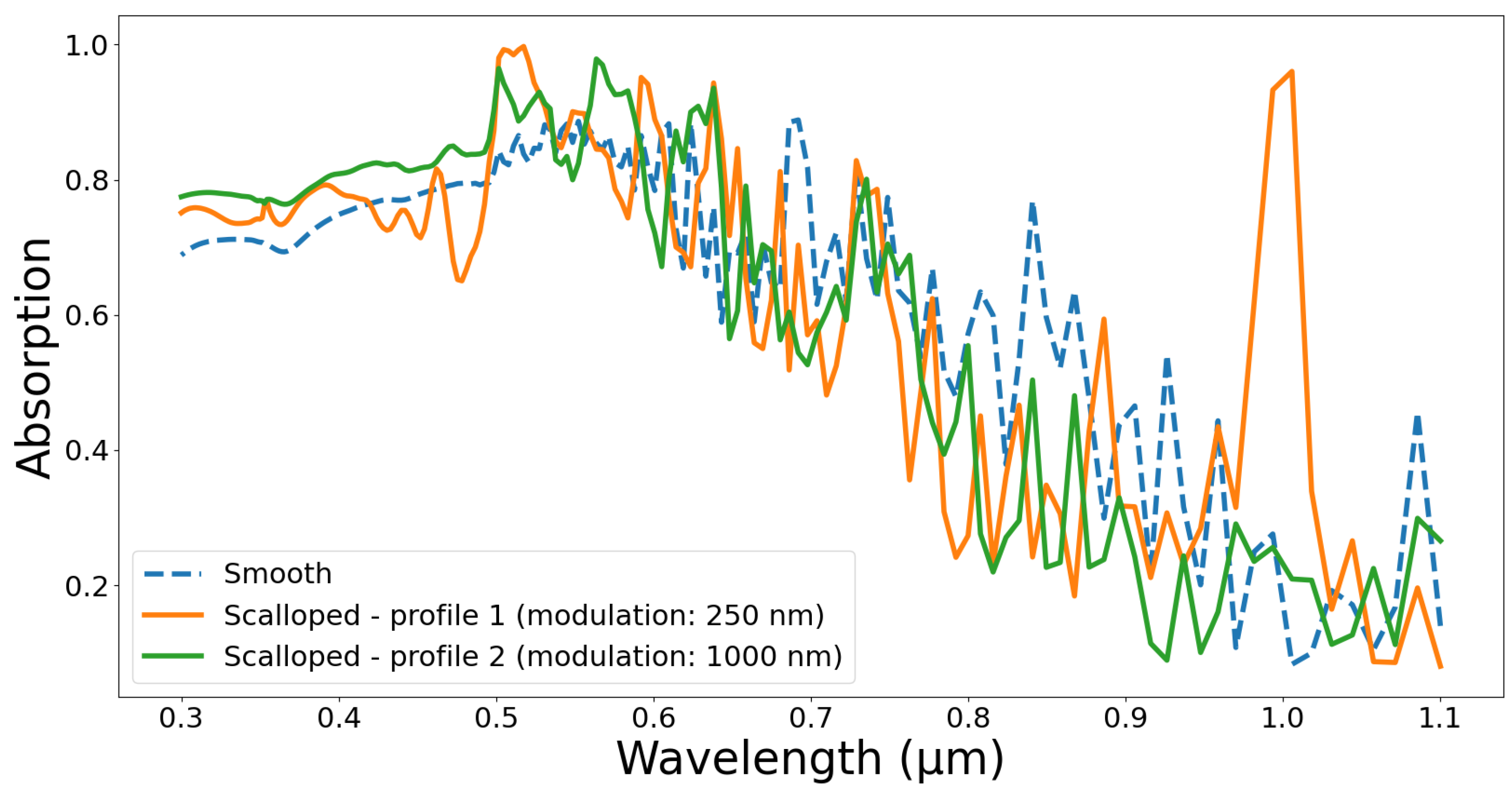

4. Analysis

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Zheng, G.; Lu, W.; Jin, S.; Lieber, C.M. Synthesis and Fabrication of High-Performance n-Type Silicon Nanowire Transistors. Adv. Mater. 2004, 16, 1890–1893. [Google Scholar] [CrossRef]

- Song, X.; Zhang, T.; Wu, L.; Hu, R.; Qian, W.; Liu, Z.; Wang, J.; Shi, Y.; Xu, J.; Chen, K.; et al. Highly Stretchable High-Performance Silicon Nanowire Field Effect Transistors Integrated on Elastomer Substrates. Adv. Sci. 2022, 9, 2105623. [Google Scholar] [CrossRef]

- Cui, Y.; Zhong, Z.; Wang, D.; Wang, W.U.; Lieber, C.M. High Performance Silicon Nanowire Field Effect Transistors. Nano Lett. 2003, 3, 149–152. [Google Scholar] [CrossRef]

- Huang, Y.; Duan, X.; Cui, Y.; Lauhon, L.J.; Kim, K.-H.; Lieber, C.M. Logic Gates and Computation from Assembled Nanowire Building Blocks. Science 2001, 294, 1313–1317. [Google Scholar] [CrossRef]

- Garnett, E.; Yang, P. Light Trapping in Silicon Nanowire Solar Cells. Nano Lett. 2010, 10, 1082–1087. [Google Scholar] [CrossRef] [PubMed]

- Zhang, Y.; Liu, H. Nanowires for High-Efficiency, Low-Cost Solar Photovoltaics. Crystals 2019, 9, 87. [Google Scholar] [CrossRef]

- Yun, J.; Ahn, J.-H.; Moon, D.-I.; Choi, Y.-K.; Park, I. Joule-Heated and Suspended Silicon Nanowire Based Sensor for Low-Power and Stable Hydrogen Detection. ACS Appl. Mater. Interfaces 2019, 11, 42349–42357. [Google Scholar] [CrossRef]

- Chen, W.; Yao, H.; Tzang, C.H.; Zhu, J.; Yang, M.; Lee, S.-T. Silicon Nanowires for High-Sensitivity Glucose Detection. Appl. Phys. Lett. 2006, 88, 213104. [Google Scholar] [CrossRef]

- Mohammad, N.S. Understanding Quantum Confinement in Nanowires: Basics, Applications and Possible Laws. J. Phys. Condens. Matter 2014, 26, 423202. [Google Scholar] [CrossRef]

- Amprius Technologies. The All-New Amprius 500 Wh/Kg Battery Platform Is Here. Available online: https://amprius.com/the-all-new-amprius-500-wh-kg-battery-platform-is-here/ (accessed on 3 September 2024).

- Chang, S.; Lee, G.; Song, Y. Recent Advances in Vertically Aligned Nanowires for Photonics Applications. Micromachines 2020, 11, 726. [Google Scholar] [CrossRef] [PubMed]

- Puglisi, R.A.; Bongiorno, C.; Caccamo, S.; Fazio, E.; Mannino, G.; Neri, F.; Scalese, S.; Spucches, D.; La Magna, A. Chemical Vapor Deposition Growth of Silicon Nanowires with Diameter Smaller Than 5 nm. ACS Omega 2019, 4, 17967–17971. [Google Scholar] [CrossRef]

- Acharya, S.; Kottantharayil, A. VLS Growth of Silicon Nanowires in Cold Wall Cat-CVD Chamber. In Proceedings of the 2014 IEEE 2nd International Conference on Emerging Electronics (ICEE), Bengaluru, India, 3–6 December 2014; IEEE: Bengaluru, India, 2014; pp. 1–4. [Google Scholar]

- Sivakov, V.; Heyroth, F.; Falk, F.; Andrä, G.; Christiansen, S. Silicon Nanowire Growth by Electron Beam Evaporation: Kinetic and Energetic Contributions to the Growth Morphology. J. Cryst. Growth 2007, 300, 288–293. [Google Scholar] [CrossRef]

- Peng, K.-Q.; Yan, Y.-J.; Gao, S.-P.; Zhu, J. Synthesis of Large-Area Silicon Nanowire Arrays via Self-Assembling Nanoelectrochemistry. Adv. Mater. 2002, 14, 1164. [Google Scholar] [CrossRef]

- Jana, S.; Mondal, S.; Bhattacharyya, S.R. Wetting and Surface Energy of Vertically Aligned Silicon Nanowires. J. Nanosci. Nanotechnol. 2013, 13, 3983–3989. [Google Scholar] [CrossRef] [PubMed]

- Wendisch, F.J.; Rey, M.; Vogel, N.; Bourret, G.R. Large-Scale Synthesis of Highly Uniform Silicon Nanowire Arrays Using Metal-Assisted Chemical Etching. Chem. Mater. 2020, 32, 9425–9434. [Google Scholar] [CrossRef] [PubMed]

- Huang, Z.; Fang, H.; Zhu, J. Fabrication of Silicon Nanowire Arrays with Controlled Diameter, Length, and Density. Adv. Mater. 2007, 19, 744–748. [Google Scholar] [CrossRef]

- Chen, C.-Y.; Liu, Y.-R. Exploring the Kinetics of Ordered Silicon Nanowires with the Formation of Nanogaps Using Metal-Assisted Chemical Etching. Phys. Chem. Chem. Phys. 2014, 16, 26711–26714. [Google Scholar] [CrossRef]

- Nor, M.N.M.; Hashim, U.; Halim, N.H.A.; Hamat, N.H.N.; Rusop, M.; Subban, R.Y.; Kamarulzaman, N.; Wui, W.T. Top-down approach: Fabrication of silicon nanowires using scanning electron microscope based electron beam lithography method and inductively coupled plasma-reactive ion etching. AIP Conf. Proc. 2010, 1217, 272–278. [Google Scholar]

- Sun, M.-C.; Kim, G.; Lee, J.H.; Kim, H.; Kim, S.W.; Kim, H.W.; Lee, J.-H.; Shin, H.; Park, B.-G. Patterning of Si Nanowire Array with Electron Beam Lithography for Sub-22nm Si Nanoelectronics Technology. Microelectron. Eng. 2013, 110, 141–146. [Google Scholar] [CrossRef]

- Fischer, P.B.; Chou, S.Y. RIE of Sub-50 Nm High Aspect-Ratio Pillars, Ridges, and Trenches in Silicon and Silicon-Germanium. Microelectron. Eng. 1993, 21, 311–314. [Google Scholar] [CrossRef]

- Henry, M.D.; Walavalkar, S.; Homyk, A.; Scherer, A. Alumina Etch Masks for Fabrication of High-Aspect-Ratio Silicon Micropillars and Nanopillars. Nanotechnology 2009, 20, 255305. [Google Scholar] [CrossRef] [PubMed]

- Xu, J.; Refino, A.D.; Delvallée, A.; Seibert, S.; Schwalb, C.; Hansen, P.E.; Foldyna, M.; Siaudinyte, L.; Hamdana, G.; Wasisto, H.S.; et al. Deep-Reactive Ion Etching of Silicon Nanowire Arrays at Cryogenic Temperatures. Appl. Phys. Rev. 2024, 11, 021411. [Google Scholar] [CrossRef]

- Liu, J.; Zhang, X.; Ashmkhan, M.; Dong, G.; Liao, Y.; Wang, B.; Zhang, T.; Yi, F. Fabrication and Photovoltaic Properties of Silicon Solar Cells with Different Diameters and Heights of Nanopillars. Energy Tech. 2013, 1, 139–143. [Google Scholar] [CrossRef]

- Thalluri, S.M.; Borme, J.; Xiong, D.; Xu, J.; Li, W.; Amorim, I.; Alpuim, P.; Gaspar, J.; Fonseca, H.; Qiao, L.; et al. Highly-Ordered Silicon Nanowire Arrays for Photoelectrochemical Hydrogen Evolution: An Investigation on the Effect of Wire Diameter, Length and Inter-Wire Spacing. Sustain. Energy Fuels 2018, 2, 978–982. [Google Scholar] [CrossRef]

- Lee, S.; Yoo, H.; Won, W.-Y.; Cho, H.; Seo, M.; Kong, B.D.; Meyyappan, M.; Baek, C.-K. Thermal Conductivity Reduction by Scallop Shaped Surface Modulation in Silicon Nanowires. Appl. Phys. Lett. 2020, 116, 203901. [Google Scholar] [CrossRef]

- Ko, M.; Baek, S.; Song, B.; Kang, J.; Kim, S.; Cho, C. Periodically Diameter-Modulated Semiconductor Nanowires for Enhanced Optical Absorption. Adv. Mater. 2016, 28, 2504–2510. [Google Scholar] [CrossRef] [PubMed]

- Wang, B.; Dong, X.-S.; Wang, Z.; Wang, Y.-F.; Hou, Z.-Y. MEMS-Based Ionization Gas Sensors for VOCs with Array of Nanostructured Silicon Needles. ACS Sens. 2020, 5, 994–1001. [Google Scholar] [CrossRef]

- Kim, G.-H.; Lee, B.-H.; Im, H.; Jeon, S.-B.; Kim, D.; Seol, M.-L.; Hwang, H.; Choi, Y.-K. Controlled Anisotropic Wetting of Scalloped Silicon Nanogroove. RSC Adv. 2016, 6, 41914–41918. [Google Scholar] [CrossRef]

- Syed Mohammed, Z.A.; Olimpo, M.A.S.; Poenar, D.P.; Aditya, S. Smoothening of Scalloped DRIE Trench Walls. Mater. Sci. Semicond. Process. 2017, 63, 83–89. [Google Scholar] [CrossRef]

- Dey, R.K.; Ekinci, H.; Cui, B. Effects of Mask Material Conductivity on Lateral Undercut Etching in Silicon Nano-Pillar Fabrication. J. Vac. Sci. Technol. B Nanotechnol. Microelectron. Mater. Process. Meas. Phenom. 2020, 38, 012207. [Google Scholar] [CrossRef]

- Herth, E.; Edmond, S.; Bouville, D.; Cercus, J.L.; Bayle, F.; Cambril, E. Micro-/Nanopillars for Micro- and Nanotechnologies Using Inductively Coupled Plasmas. Phys. Status Solidi 2019, 216, 1900324. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| Spread | 500 rpm, 5 s |

| Acceleration | 1305 rpm/s |

| Spin | 5000 rpm, 30 s |

| Deceleration | 5 s |

| Parameter | Value |

|---|---|

| Nanopatterns | Circles |

| Acceleration voltage | 10 kV |

| Dose | 100 µC/cm2 |

| Aperture | 30 µm |

| Working distance | 10 mm |

| Process Parameters | Passivation Step | Transition (Buffer) Step | Etching Step |

|---|---|---|---|

| C4F8 flow rate (sccm) | 65 | 15 | 15 |

| SF6 flow rate (sccm) | 1 | 65 | 65 |

| Chamber pressure (mTorr) | 20 | 20 | 20 |

| Stage temperature () | 20 | 20 | 20 |

| ICP power (W) | 450 | 0 | 450 |

| CCP power (W) | 10 | 0 | 25 |

| He cooling (Torr) | 11 | 11 | 11 |

| Time (s) | 3 | 2 | 7 |

| Parameters | Group 1 | Group 2 | Group 3 |

|---|---|---|---|

| Diameter (mask) | 200 nm | 400 nm | 600 nm |

| Average diameter (fabricated) | 251.6 nm | 445 nm | 623.9 nm |

| Average diameter (error) | ~25.8% | ~11.25% | ~4% |

| Average pitch (mask) | 400 nm | 800 nm | 1200 nm |

| Average pitch (fabricated) | 403.1 nm | 816 nm | 1221.7 nm |

| Average pitch (error) | ~0.77% | ~2% | ~1.8% |

| Metric | Our Method (EBL + Bosch DRIE) | Photolithography + Bosch DRIE [28] | EBL + Cryogenic DRIE [24] | EBL + Pseudo-Bosch DRIE [32,33] |

|---|---|---|---|---|

| Pitch control | Very high | - | - | - |

| Diameter control | High | Moderate | High | Moderate |

| Additional treatment | No | Yes (thermal oxidation and oxide etching) | No | No |

| Sidewall tunability | Very high | Very high | Low | Low |

| Cooling requirement | Low—Standard temperature conditions required | Low—Standard temperature conditions required | Very high—Cryogenic cooling is required | Moderate—Requires some cooling but less stringent than cryo-DRIE |

| Target applications | Thermoelectric devices, IGS, solar cells, etc. | Solar cells, photodetectors, etc. | High-end electronics, optoelectronics, sensors requiring smooth surfaces | MEMS, high aspect ratio structures |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mukherjee, S.; Elsayed, M.Y.; Tawfik, H.H.; El-Gamal, M.N. A Fabrication Method for Realizing Vertically Aligned Silicon Nanowires Featuring Precise Dimension Control. Sensors 2024, 24, 7144. https://doi.org/10.3390/s24227144

Mukherjee S, Elsayed MY, Tawfik HH, El-Gamal MN. A Fabrication Method for Realizing Vertically Aligned Silicon Nanowires Featuring Precise Dimension Control. Sensors. 2024; 24(22):7144. https://doi.org/10.3390/s24227144

Chicago/Turabian StyleMukherjee, Sourav, Mohannad Y. Elsayed, Hani H. Tawfik, and Mourad N. El-Gamal. 2024. "A Fabrication Method for Realizing Vertically Aligned Silicon Nanowires Featuring Precise Dimension Control" Sensors 24, no. 22: 7144. https://doi.org/10.3390/s24227144

APA StyleMukherjee, S., Elsayed, M. Y., Tawfik, H. H., & El-Gamal, M. N. (2024). A Fabrication Method for Realizing Vertically Aligned Silicon Nanowires Featuring Precise Dimension Control. Sensors, 24(22), 7144. https://doi.org/10.3390/s24227144