A Dynamic Multi-Cell FCL to Improve the Fault Ride through Capability of DFIG-Based Wind Farms

Abstract

:1. Introduction

- A multi-cell FCL that has a resistor in each cell and is directly connected to the power grid without using the series transformer, thus reducing the volume and cost of the MCFCL.

- A FCL topology that puts the suitable number of cells in the fault path in accordance with the voltage sag level, thus providing an adaptive voltage sag compensation mechanism.

- A design that is able to effectively mitigate voltage sag conditions ranging from low to severe and prevent the occurrence of over-voltages in the WF terminals.

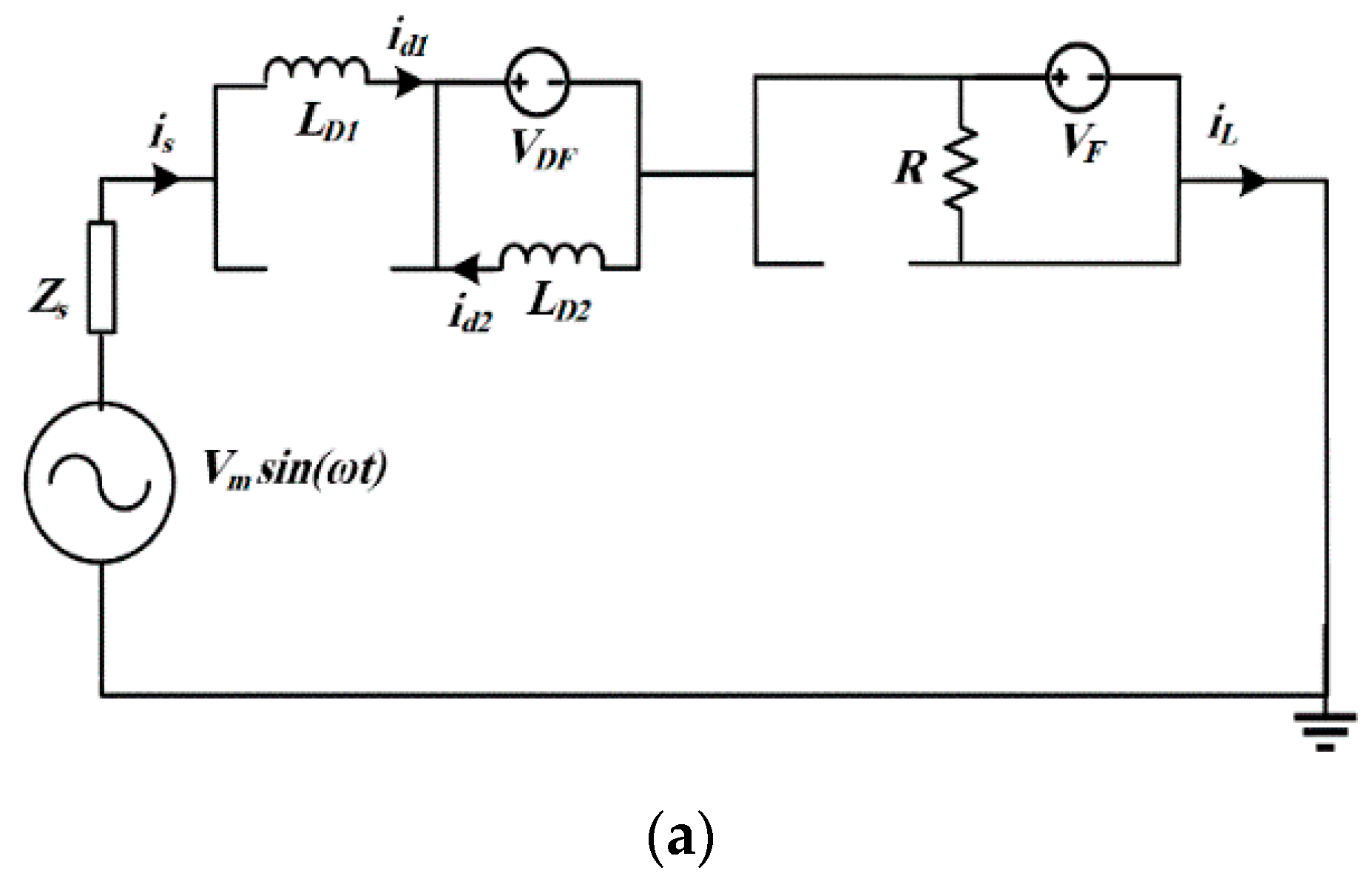

2. Proposed Multi-Cell Fault Current Limiter (MCFCL) Topology

2.1. MCFCL Operation

2.2. MCFCL Control System

2.3. Procedure to Determine the Number of MCFCL Cells

3. Analytical Study of the Proposed MCFCL Topology

4. Implementation to a DFIG-Based WF

4.1. DFIG-Based Wind Turbine Model

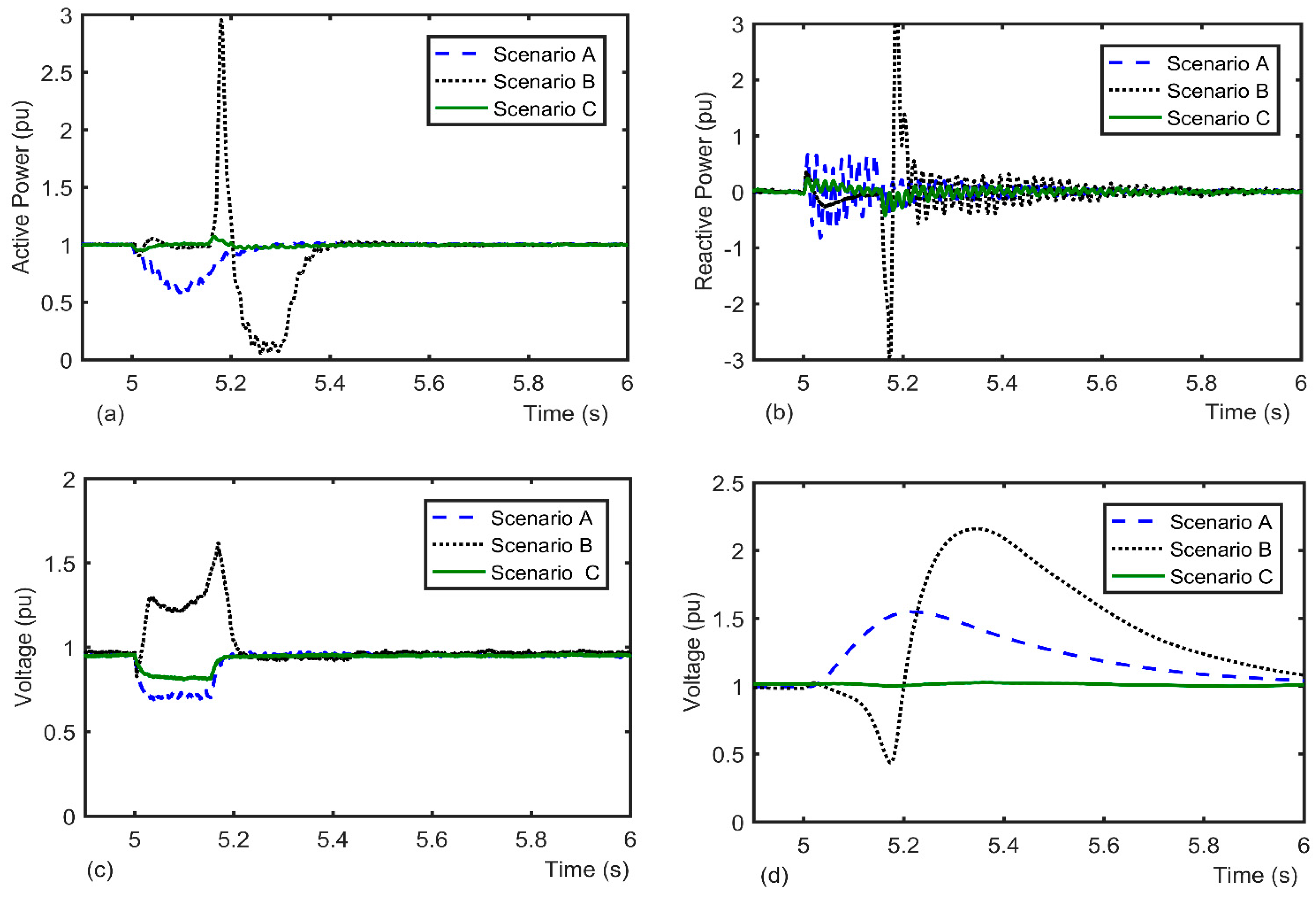

4.2. Simulation Results

- - Scenario A: No FRT devices.

- - Scenario B: Using the SBFCL.

- - Scenario C: Using the MCFCL.

4.2.1. Low Voltage Sag Condition

4.2.2. Medium Voltage Sag Condition

4.2.3. Severe Voltage Sag Condition

- Using the SBFCL produces high transient over voltage under low and medium voltage sag conditions, which is harmful for the DFIG under short circuit fault current.

- The proposed MCFCL scheme is able to properly mitigate a wide range of voltage sag levels without producing any transient over voltage.

- The MCFCL outperforms the SBFCL in terms of FRT performance and transient over-voltage under medium and low voltage sag levels.

- Response and performance of both SBFCL and MCFCL are the same under severe voltage sag levels.

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Tong, N.; Lin, X.; Li, Z.; Fang, J.; Zhuo, Y.; Sui, Q.; Jin, N.; Chen, Z.; Muradov, N. Coordinated Sequential Control of Individual Generators for Large-Scale DFIG-Based Wind Farms. IEEE Trans. Sustain. Energy 2019, 11, 1679–1692. [Google Scholar] [CrossRef]

- Tsili, M.; Papathanassiou, S. A review of grid code technical requirements for wind farms. IET Renew. Power Gener. 2009, 3, 308. [Google Scholar] [CrossRef]

- Firouzi, M.; Gharehpetian, G.B. LVRT Performance Enhancement of DFIG-Based Wind Farms by Capacitive Bridge-Type Fault Current Limiter. IEEE Trans. Sustain. Energy 2018, 9, 1118–1125. [Google Scholar] [CrossRef]

- Ali, M.A.S.; Mehmood, K.K.; Baloch, S.; Kim, C.-H. Modified rotor-side converter control design for improving the LVRT capability of a DFIG-based WECS. Electr. Power Syst. Res. 2020, 186, 106403. [Google Scholar] [CrossRef]

- Xiao, S.; Yang, G.; Zhou, H.; Geng, H. Analysis of the control limit for rotor-side converter of doubly fed induction generator-based wind energy conversion system under various voltage dips. IET Renew. Power Gener. 2013, 7, 71–81. [Google Scholar] [CrossRef]

- Morshed, M.J.; Fekih, A. A new fault ride-through control for DFIG-based wind energy systems. Electr. Power Syst. Res. 2017, 146, 258–269. [Google Scholar] [CrossRef]

- Wang, L.; Truong, D.-N. Stability Enhancement of DFIG-Based Offshore Wind Farm Fed to a Multi-Machine System Using a STATCOM. IEEE Trans. Power Syst. 2013, 28, 2882–2889. [Google Scholar] [CrossRef]

- Amalorpavaraj, R.J.; Kaliannan, P.; Padmanaban, S.; Subramaniam, U.; Ramachandaramurthy, V.K. Improved Fault Ride Through Capability in DFIG Based Wind Turbines Using Dynamic Voltage Restorer With Combined Feed-Forward and Feed-Back Control. IEEE Access 2017, 5, 20494–20503. [Google Scholar] [CrossRef]

- Firouzi, M.; Gharehpetian, G.B.; Mozafari, B. Power flow control and short circuit current limitation of wind farms using unified inter-phase power controller. IEEE Trans. Power Deliv. 2017, 32, 62–71. [Google Scholar] [CrossRef]

- Dong, H.; Wu, H.; Pan, J.; Chen, Y.; Xu, B. Research on Double-Fed Induction Generator Low Voltage Ride Through Based on Double Braking Resistors Using Fuzzy Control. Energies 2018, 11, 1155. [Google Scholar] [CrossRef] [Green Version]

- Jiang, H.; Zhang, C. A Method of Boosting Transient Stability of Wind Farm Connected Power System Using S Magnetic Energy Storage Unit. IEEE Trans. Appl. Supercond. 2019, 29, 1–5. [Google Scholar] [CrossRef]

- Chen, L.; Zheng, F.; Deng, C.; Li, Z.; Guo, F. Fault Ride-Through Capability Improvement of DFIG-Based Wind Turbine by Employing a Voltage-Compensation-Type Active SFCL. Can. J. Electr. Comput. Eng. 2015, 38, 132–142. [Google Scholar] [CrossRef]

- Zou, Z.-C.; Xiao, X.-Y.; Liu, Y.-F.; Zhang, Y.; Wang, Y.-H. Integrated Protection of DFIG-Based Wind Turbine with a Resistive-Type SFCL under Symmetrical and Asymmetrical Faults. IEEE Trans. Appl. Supercond. 2016, 26, 1–5. [Google Scholar] [CrossRef]

- Firouzi, M.; Gharehpetian, G.B. Improving Fault Ride-Through Capability of Fixed-Speed Wind Turbine by Using Bridge-Type Fault Current Limiter. IEEE Trans. Energy Convers. 2013, 28, 361–369. [Google Scholar] [CrossRef]

- Firouzi, M.; Nasiri, M.; Mobayen, S.; Gharehpetian, G.B. Sliding Mode Controller-Based BFCL for Fault Ride-Through Performance Enhancement of DFIG-Based Wind Turbines. Complexity 2020, 2020, 1–12. [Google Scholar] [CrossRef]

- Firouzi, M.; Shafiee, M.R.; Gharehpetian, G.B. Multi-Resistor Bridge-Type FCL for FRT Capability Improvement of DFIG-based Wind Farm. IET Energy Syst. Integr. 2020. [Google Scholar] [CrossRef]

- Rashid, G.; Ali, M.H. A modified bridge-type fault current limiter for fault ride-through capacity enhancement of fixed speed wind generator. IEEE Trans. Energy Convers. 2015, 29, 527–534. [Google Scholar]

- Hossain, E. Performance analysis of diode-bridge-type non-superconducting fault current limiter in improving transient stability of DFIG based variable speed wind generator. Electr. Power Syst. Res. 2017, 143, 782–793. [Google Scholar] [CrossRef]

- Firouzi, M. A modified capacitive bridge-type fault current limiter (CBFCL) for LVRT performance enhancement of wind power plants. Int. Trans. Electr. Energy Syst. 2017, 28, e2505. [Google Scholar] [CrossRef]

- Kartijkolaie, H.S.; Radmehr, M.; Firouzi, M. LVRT capability enhancement of DFIG-based wind farms by using capacitive DC reactor-type fault current limiter. Int. J. Electr. Power Energy Syst. 2018, 102, 287–295. [Google Scholar] [CrossRef]

- Mei, F.; Pal, B.C. Modeling of Doubly Fed Induction Generator for Power System Stability Study. In Proceedings of the IEEE Power and Energy Society General Meeting-Conversion and Delivery of Electrical Energy in the 21st Century, Pittsburgh, PA, USA, 20–24 July 2008; pp. 1–8. [Google Scholar]

- Li, H.; Yang, C.; Zhao, B.; Wang, H.S.; Chen, Z. Aggregated models and transient performances of a mixed wind farm with different wind turbine generator systems. Electr. Power Syst. Res. 2012, 92, 1–10. [Google Scholar] [CrossRef]

| Switching Sequence | Cell Resistance | Voltage Range (pu) | |||

|---|---|---|---|---|---|

| S1 | S2 | Sn-1 | Sn | ||

| 0 | 0 | 0 | 0 | ||

| 1 | 0 | 0 | 0 | R | |

| 1 | 1 | 0 | 0 | ||

| 1 | 1 | 1 | 1 | ||

| Parameters | Value | |

|---|---|---|

| Grid | Rated voltage | 20 kV |

| Frequency | 50 Hz | |

| DFIG | Nominal power | 2 MW |

| Nominal voltage | 690 V | |

| Nominal frequency | 50 Hz | |

| Inertia constant | 1 s | |

| Stator resistance | 0.0057 Ω | |

| Stator leakage reactance | 0.078 Ω | |

| Rotor resistance | 0.0159 Ω | |

| Rotor leakage reactance | 0.1022 Ω | |

| Mutual reactance | 2.434 Ω | |

| MCFCL | TLR inductance | 0.01 H |

| Resistance of each RC | 10 Ω |

| States | Cell Resistance | Voltage Sag Range (pu) | ||

|---|---|---|---|---|

| S1 | S2 | S3 | ||

| ON | ON | ON | 0 | 0.9 pu |

| OFF | ON | ON | 0.6 pu 0.9 pu | |

| OFF | OFF | ON | 0.3 pu 0.6 pu | |

| OFF | OFF | OFF | 0 0.3 pu | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shafiee, M.R.; Kartijkolaie, H.S.; Firouzi, M.; Mobayen, S.; Fekih, A. A Dynamic Multi-Cell FCL to Improve the Fault Ride through Capability of DFIG-Based Wind Farms. Energies 2020, 13, 6071. https://doi.org/10.3390/en13226071

Shafiee MR, Kartijkolaie HS, Firouzi M, Mobayen S, Fekih A. A Dynamic Multi-Cell FCL to Improve the Fault Ride through Capability of DFIG-Based Wind Farms. Energies. 2020; 13(22):6071. https://doi.org/10.3390/en13226071

Chicago/Turabian StyleShafiee, M. R., H. Shahbabaei Kartijkolaie, M. Firouzi, S. Mobayen, and A. Fekih. 2020. "A Dynamic Multi-Cell FCL to Improve the Fault Ride through Capability of DFIG-Based Wind Farms" Energies 13, no. 22: 6071. https://doi.org/10.3390/en13226071